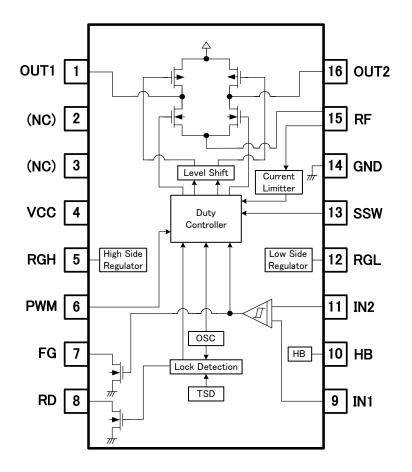

**Block Diagram**

# Specifications

Absolute maximum rating at Ta=25°C

| Parameter           | Symbol  | Conditions            | Ratings     | Unit |

|---------------------|---------|-----------------------|-------------|------|

| Maximum supply      | VCC     |                       | 36          | V    |

| voltage             | max     |                       |             |      |

| OUT pin output      | IOUT    |                       | 0.7         | А    |

| current             | max     |                       |             |      |

| RD/FG output pin    | VRD/FG  |                       | 36          | V    |

| withstand           | max     |                       |             |      |

| RD/FG output        | IRD/FG  |                       | 10          | mA   |

| maximum current     | max     |                       |             |      |

| RGL output maximum  | IRGL    |                       | 5           | mA   |

| current             | max     |                       |             |      |

| HB output maximum   | IHB max |                       | 10          | mA   |

| current             |         |                       |             |      |

| PWM input pin       | VPWM    |                       | 6           | V    |

| withstand           | max     |                       |             |      |

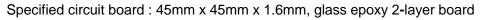

| Allowable power     | Pd max  | *On a specified board | 0.8         | W    |

| dissipation         |         |                       |             |      |

| Operating           | Topr    |                       | -40 to +95  | °C   |

| temperature         |         |                       |             |      |

| Storage temperature | Tstg    |                       | -55 to +150 | °C   |

\*Specified board: 114.3mm×76.1mm×1.6mm, fiberglass epoxy printed circuit board

Caution 1) Absolute maximum ratings represent the values which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

### Recommended Operating Conditions at Ta=25°C

| Parameter                                      | Symbol                                                 | Conditions                   |        | Ratings             | Unit |

|------------------------------------------------|--------------------------------------------------------|------------------------------|--------|---------------------|------|

| Operating supply voltage range                 | ply voltage range VCC op1 Recommended su voltage range |                              | supply | 7 to 34             | V    |

|                                                | VCC op2                                                | Boot guarantee voltage range | supply | 6 to 34             | V    |

| Hall input common phase input<br>voltage range | VICM                                                   |                              |        | 0.3 to VRGL-2.<br>0 | V    |

| SSW pin input voltage range                    | SSW                                                    |                              |        | 1.0 to 3.0          | V    |

| Input PWM frequency range                      | PWMF                                                   |                              |        | 20 to 50            | kHz  |

# LV8860V

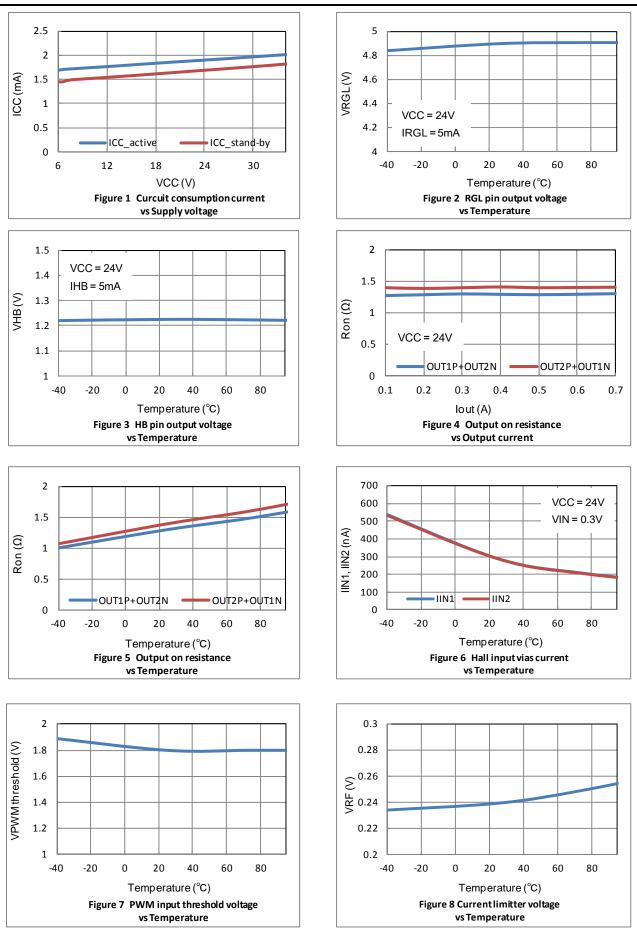

| Electrical Characteristics at Ta=25°C, V <sub>CC</sub> =24V |               |                     |        |        |        |      |  |  |  |

|-------------------------------------------------------------|---------------|---------------------|--------|--------|--------|------|--|--|--|

| Parameter                                                   | Symbol        | Conditions          |        | Uni    |        |      |  |  |  |

|                                                             | -             | Conditions          | min    | typ    | max    | t    |  |  |  |

| Circuit consumption current                                 | ICC           | Active              |        | 2.2    | 3.5    | mA   |  |  |  |

|                                                             | ICCo          | Stand-by            |        | 1.7    | 2.7    | mA   |  |  |  |

| RGL pin output voltage                                      | VRGL          |                     | 4.7    | 5.0    | 5.3    | V    |  |  |  |

| RGH pin output voltage                                      | VRGH          |                     | VCC-4. | VCC-4. | VCC-5. | V    |  |  |  |

|                                                             |               |                     | 3      | 8      | 3      |      |  |  |  |

| HB pin output voltage                                       | VHB           | IHB=5mA             | 1.16   | 1.25   | 1.28   | V    |  |  |  |

| Output ON resistance                                        | Ron           | Io=0.3A, upper and  |        | 1.4    | 2.0    | Ω    |  |  |  |

|                                                             |               | lower ON resistance |        |        |        |      |  |  |  |

| Hall input bias current                                     | IHIN          |                     |        |        | 1.0    | uA   |  |  |  |

| Current limiter                                             | VRF           |                     | 200    | 225    | 250    | mV   |  |  |  |

| PWM pin input Low level                                     | VPWM          |                     | 0      |        | 1.0    | V    |  |  |  |

|                                                             | L             |                     |        |        |        |      |  |  |  |

| PWM pin input High level                                    | VPWM          |                     | 2.5    |        | VRGL   | V    |  |  |  |

|                                                             | Н             |                     |        |        |        |      |  |  |  |

| PWM input minimum pulse                                     | TPWM          |                     |        | 2      |        | uSec |  |  |  |

| width                                                       |               |                     |        |        |        |      |  |  |  |

| RD/FG output pin Low                                        | VRD/F         | IRD/FG=3mA          |        | 0.22   | 0.30   | V    |  |  |  |

| voltage                                                     | G             |                     |        |        |        |      |  |  |  |

| FG output leakage current                                   | IRDL/F        | VRD/FG=24V          |        |        | 10     | uA   |  |  |  |

|                                                             | GL            |                     |        |        |        |      |  |  |  |

| FG comparator hysteresis                                    | $\Delta VHYS$ | including offset    | ±5     | ±12    | ±18    | mV   |  |  |  |

| width                                                       |               |                     |        |        |        |      |  |  |  |

| Output ON time in                                           | TACT          |                     | 0.74   | 0.95   | 1.16   | Sec  |  |  |  |

| Lock-detection                                              |               |                     |        |        |        |      |  |  |  |

| Output OFF time in                                          | TDET          |                     | 7.0    | 9.0    | 11.0   | Sec  |  |  |  |

| Lock-detection<br>Output ON/OFF ratio in                    | TRTO          | TRTO=TDET/TACT      | 7.5    | 9.0    | 11.0   |      |  |  |  |

| Lock-detection                                              | IRIU          | INTO-IDEI/IAGI      | 6.1    | 9.0    | 11.0   |      |  |  |  |

| Thermal shutdown operating                                  | TSD           | *Design querentes   |        | 180    |        | °C   |  |  |  |

| temperature                                                 |               | *Design guarantee   |        |        |        |      |  |  |  |

| Thermal shutdown                                            | $\Delta TSD$  | *Design guarantee   |        | 40     |        | °C   |  |  |  |

| hysteresis width                                            |               |                     |        |        |        |      |  |  |  |

\* Design guarantee value and no measurement is performed.

|    | uit board , | $\stackrel{\wedge}{\vdash}$ means VCC , $\stackrel{\wedge}{\top}$ means                                                                                                               | PCI                                                   |

|----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|    | Pin name    | incane ree, incane                                                                                                                                                                    | Equivalent circuit                                    |

| 1  | OUT1        | Output pin for motor driver<br>The motor coil is connected between<br>OUT1 (pin1) and OUT2 (16pin).                                                                                   |                                                       |

| 16 | OUT2        |                                                                                                                                                                                       |                                                       |

| 2  | NC          | NC pin                                                                                                                                                                                |                                                       |

| 3  | NC          | NC pin                                                                                                                                                                                |                                                       |

| 4  | VCC         | Power supply pin<br>VCC voltage is impressed. The<br>operation voltage range is from 7.0 to<br>34.0(V). The capacitor is connected to<br>GND pin (14pin) for stabilization.           |                                                       |

| 5  | RGH         | Regulator voltage output pin for the<br>upper output Tr driver<br>The capacitor is connected to VCC pin<br>(3pin) for stabilization.                                                  | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 6  | PWM         | Input pin for PWM control<br>The PWM signal is supplied for speed<br>control.<br>*OPEN: pull up to High<br>* When input is High → output is High<br>When input is Low → output is Low |                                                       |

| 7  | FG          | FG(rotation detection) pulse output pin<br>The resistor is connected to VCC pin<br>(3pin) for detection signal.                                                                       |                                                       |

| 8  | RD          | RD(lock detection) signal output pin<br>*During rotation → output is Low<br>During lock→ output is High<br>The resistor is connected to VCC pin<br>(3pin) for detection signal.       |                                                       |

To the next page

**Pin Functions**

| Pin No. | Pin name | Description                                                                                                                                                                                                                                                                                | Equivalent circuit         |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 9       | IN1      | Hall input + pin                                                                                                                                                                                                                                                                           |                            |

|         |          | Hall input - pin                                                                                                                                                                                                                                                                           |                            |

|         |          | The Hall device outputs are connected.                                                                                                                                                                                                                                                     |                            |

|         |          | If hall signal is affected by noise, the                                                                                                                                                                                                                                                   |                            |

| 11      | IN2      | capacitor should be connected between                                                                                                                                                                                                                                                      |                            |

|         |          | IN1 pin (9pin) and IN2 pin (11pin).                                                                                                                                                                                                                                                        |                            |

|         |          |                                                                                                                                                                                                                                                                                            |                            |

| 10      | HB       | Hall bias output pin<br>The voltage supply pin of Hall device is<br>connected.                                                                                                                                                                                                             |                            |

| 12      | RGL      | Regulator voltage output pin for internal<br>circuit and lower output Tr driver<br>The capacitor is connected to GND pin<br>(14pin) for stabilization.                                                                                                                                     |                            |

| 13      | SSW      | Voltage input pin for control between soft<br>switches<br>The resistor is connected to for RGL or<br>GND pin (14pin) for adjusting soft switch<br>width.<br>*OPEN: pin voltage is 2V<br>*Soft switch zone is changed by<br>connecting a resistance to RGL or GND to<br>adjust pin voltage. | 90kΩ<br>90kΩ<br>13<br>60kΩ |

| 14      | GND      | Ground pin                                                                                                                                                                                                                                                                                 |                            |

| 15      | RF       | Resistive connection pin for current limiter<br>The resistor is connected to GND (14pin)<br>for detection of current value.                                                                                                                                                                |                            |

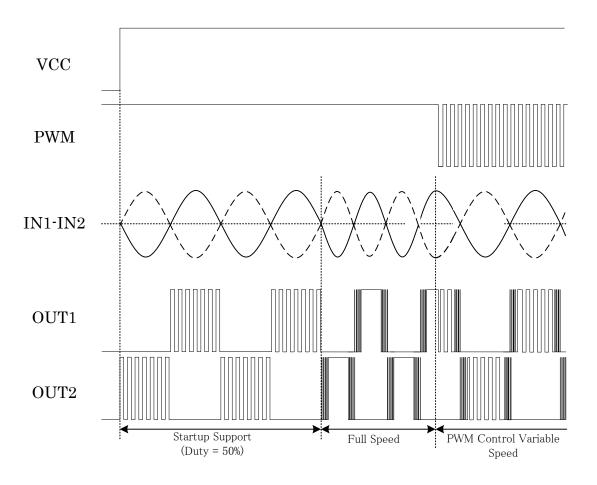

### **Operational Description**

#### 1. Operation Overview

LV8860V is a driver with single phase full wave drive mode which outputs the voltage to a coil based on the position signal from a Hall device. By supplying power, the IC is turned on. As a result, the output voltage is impressed to the coil.

FG signal is outputted according to phase switch of the coil, and RD signal is output when a motor is locked. LV8860V incorporates speed control function with direct PWM input method. The output mode is switched according to the signal input into a PWM pin and speed control is performed.

• When PWM input duty is 100% (DC input) or PWM pin is open, a fan rotates at full speed.

• Rotation speed is controllable because when a duty signal is input to PWM input, coil is energized by the same duty.

• When PWM input duty is 0% or the PWM pin is shorted to GND, IC is set to standby mode, where power supply to coil is stopped and a fan stops.

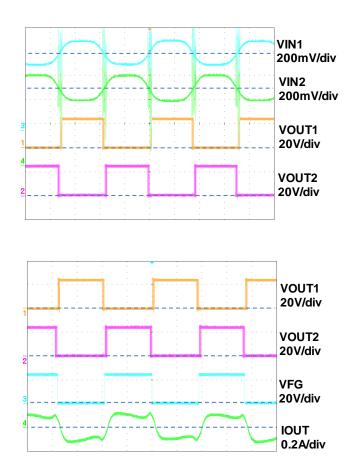

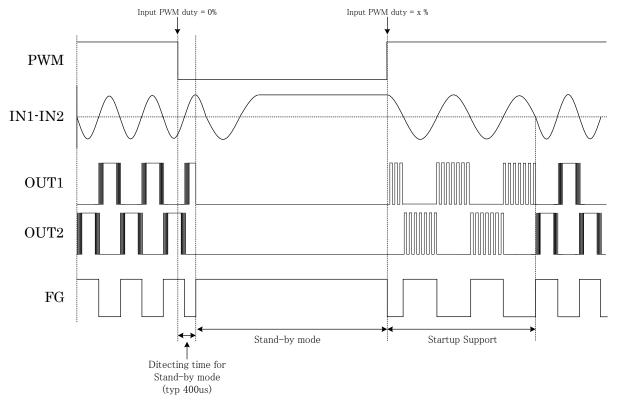

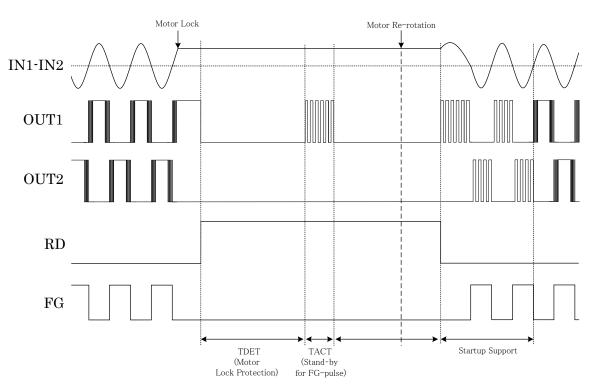

Fig.13 Operation Waveform

| Input-Output Logic           |     |     |    |      |      |     |     |

|------------------------------|-----|-----|----|------|------|-----|-----|

| Operating state              | IN1 | IN2 | PW | OUT1 | OUT2 | FG  | RD  |

|                              |     |     | М  |      |      |     |     |

| Rotation - drive mode        | Н   | L   | н  | Н    | L    | L   | L   |

| Rotation - drive mode        | L   | Н   |    | L    | Н    | OFF | L   |

| Potation regeneration mode   | Н   | L   |    | L    | L    | L   | L   |

| Rotation – regeneration mode | L   | Н   | L  | L    | L    | OFF | L   |

| Stand-by mode                | -   | -   | L  | L    | OFF  | OFF | L   |

| Look protostor               | Н   | L   |    | OFF  | L    | L   | OFF |

| Lock protector               | L   | Н   | -  | L    | OFF  | OFF | OFF |

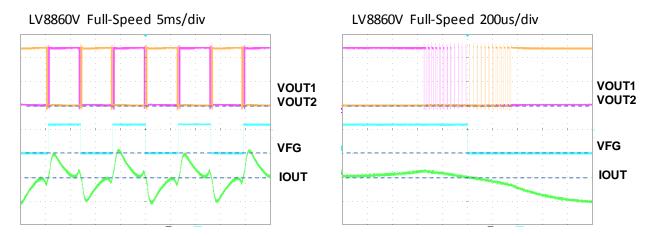

Example Wave Form (VCC = 24V , □80 single phase fan motor is used)

Explanation of each wave VIN1, VIN2 : input signal from Hall device VOUT1 : output signal from OUT1 pin(1pin) VOUT2 : output signal from OUT2 pin(16pin) VFG : output signal from FG pin(7pin), FG pin is pulled up with VCC pin IOUT : Coil Current

Fig.14 Operation Waveform

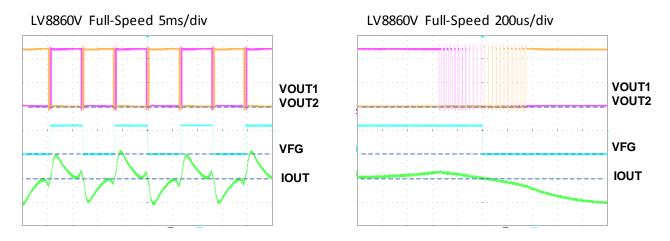

### 1-1. Full-Speed drive

When PWM pin is open or input PWM signal duty is 100%, the output of LV8860V is considered "full speed drive".

LV8860V has adopted a new soft-switching method, with which output waveform before and after the phase switch is obtained as shown in the following figure, where the duty changes gradually.

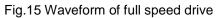

# 1-2. Speed control by PWM input

The rotation speed is controllable by PWM input into PWM pin (No.6pin) .

- /PWM input voltage is " Low " => Drive OFF PWM input voltage is " High " => Drive ON

- /When PWM pin is open, IC drives Duty = 100%.

/Input PWM frequency range is 20kHz - 50kHz , and Input PWM amplitude is 0V - 5V .

# LV8860V

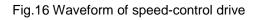

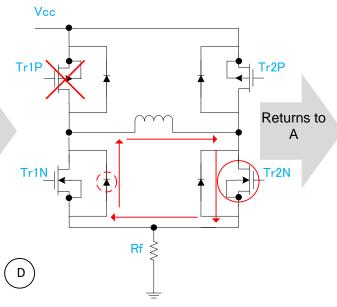

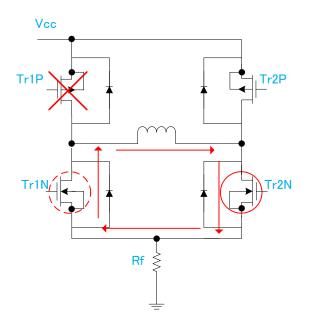

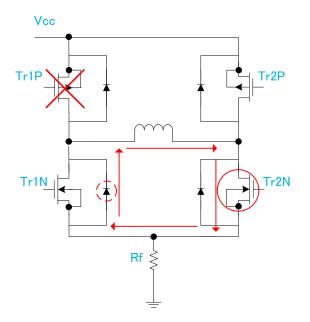

1-2-Appendix1. Description of synchronous rectification

The synchronous rectification is one method for current regeneration in PWM speed control, which realizes high efficiency and low heat generation compared to the conventional diode rectification. The following figure explains operation of the output when synchronous rectification is performed. The alphabet at the left lower of each figure corresponds to figure 16 of the previous section.

When 2 transistors, Tr 1P and Tr2N are ON, coil current flows through the coil. At that time, output voltages are OUT1: Vcc – Vsat1P OUT2: 0V + I × Rf + Vsat2N

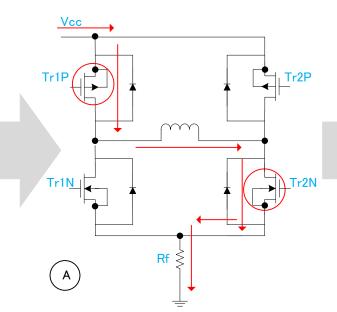

When PWM signal turns to Low, Tr 1P turns OFF to prevent penetration current. Coil current flows through the parasite Diode of Tr1N. At that time, output voltages are

OUT1: 0V – VF (negative potential) OUT2: 0V + Vsat2N

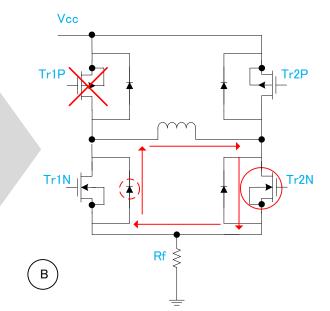

Next, Tr1N turns ON, Coil current flows through the Tr1N, coil, and Tr2N. (This method is "synchronous rectification") At that time, output voltages are OUT1: 0V – Vsat1N (negative potential) OUT2: 0V + Vsat2N

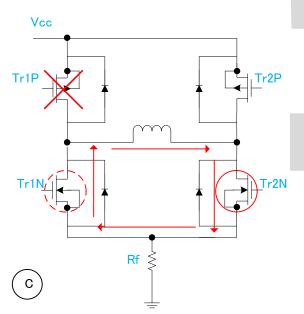

4) When PWM signal turns to High, Tr1N turns OFF.

Coil current flows through the parasite Diode of Tr1N.

At that time, output voltages are OUT1: 0V – VF (negative potential) OUT2: 0V + Vsat2N

### LV8860V

1-2-Appendix2.Merit of synchronous rectification compared to the conventional diode rectification.

In this case, output voltages are OUT1: 0V – Vsat1N (negative potential) OUT2: 0V + Vsat2N In this case, output voltages are OUT1: 0V – VF (negative potential) OUT2: 0V + Vsat2N

When the ON resistance of the transistor used for regeneration (Tr1N) is low and Vsat1N (Tr1N \* regenerated current) is lower than VF of the diode used for diode regeneration, the power dissipation for regeneration is small. Hence, efficiency becomes high and low heat generation is realized. Example: Compare the power dissipation in Tr1N during regeneration where lout = 0.3A, Ron =  $0.5\Omega$ , VF = 0.7V:

Synchronous rectification  $Ptr1n = lout \times Vosat1N = 0.3 \times (0.3 \times 0.5) = 0.045(W)$ Diode regeneration  $Ptr1n = lout \times VF = 0.3 \times 0.7 = 0.21(W)$

Heat generation of synchronous rectification is about 20% of that of diode regeneration at Tr1N.

### 1-3. Stand-by mode

When PWM input duty is 0% or PWM pin is connected to GND, the IC runs stand-by mode.

The low signal detection time of stand-by mode is about 400us.

In stand-by mode, motor is stopped. The motor starts rotation again as soon as PWM-High signal is detected.

Fig.17 Operation Waveform of Stand-by mode

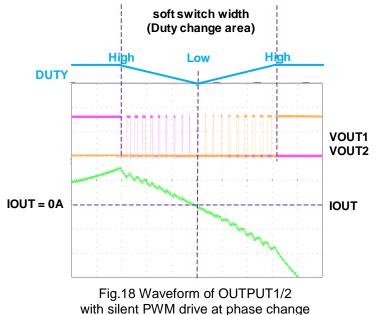

# 2. Switching method

Outline

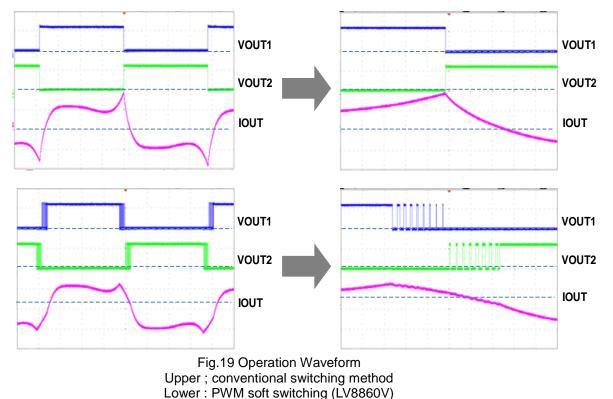

LV8860V has silent PWM drive new switching method which realizes high efficiency and silent drive. The characteristic waveform in silent PWM mode at phase switch is shown in figure 18.

Compared to the conventional switching method, current switch is smooth; therefore, the operation is silent and efficient.

The soft switch width before and after phase change is adjustable. As the following figure18 shows, by adjusting soft switch width, current change is optimized. As a result, we can get the following merits.

- 1. Small kickback waveform

- 2. Silent drive

- 3. Higher driving efficiency

Comparison of silent PWM soft switching with conventional switching method

Downloaded from Arrow.com.

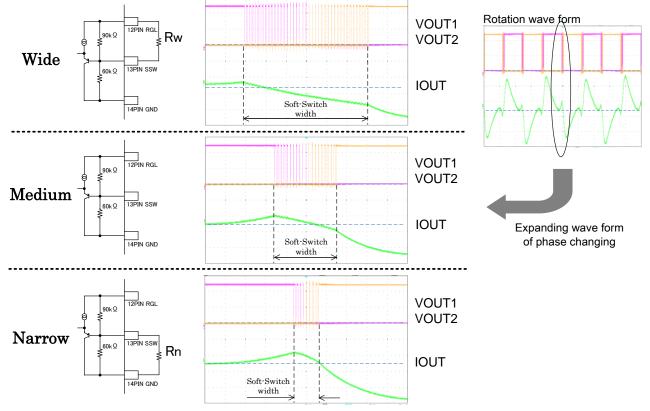

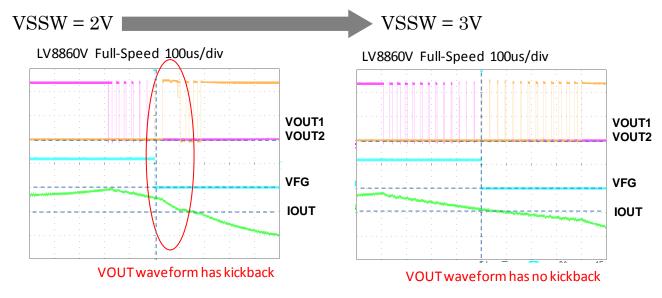

### 2-1 How to set soft-switch pin

The width of soft switch before and after switching is controlled by SSW (No.13pin) voltage. Timing of current changes at phase change is controllable by adjusting soft-switch width. This way, reactive current is reduced and motor is driven efficiently.

Fig.20 How to change soft-switch width

The width of soft-switch before and after switching is controlled by SSW. Therefore, it is adjustable by connecting an external resistance to SSW. Adjustable voltage range is between 1V and 3V. Input SSW voltage range is 1V to 3V.

When SSW voltage is High, soft-switch width is wide.

When SSW voltage is Low, soft-switch width is narrow.

\*The evaluation board is open .

< Configuration of SSW Voltage >

A . \*Without adjustment (SSW is open \* this is a reference width of soft switch) with IC's internal resistance:

$VSSW = 5 \times 60k / (90k + 60k) = 2V$

B . \*To widen width of soft switch (connect Rw (resistance) between RGL and SSW.) VSSW = 5 × 60k / { 60k + 1 / ( 1/Rw + 1/90k ) }

(ex.) Connect Rw = 75kΩ VSSW = 5 × 60k / { 60k + 1 / ( 1/75k + 1/90k ) } = 2.97V

C . \*To narrow soft switch width (connect Rn (resistance) between SSW and GND.) VSSW = 5 × [ { 1 / ( 1/Rn + 1/60k ) } / { 90k + 1 / ( 1/Rn + 1/60k ) } ]

(ex.) Connect Rn = 39kΩ VSSW = 5 × [{ 1 / (1/39k + 1/60k)} / { 90k + 1 / (1/39k + 1/60k )}] = 1.04V

#### 2-2. Effect of soft switching width adjustment

\* Because the output current at phase switch is smooth, the operation is efficient. If current switch is not smooth when SSW pin is open, connect a resistor to SSW pin to adjust SSW voltage for an optimum current waveform.

Example: If the direction of coil current has not been changed at phase switch

Fig.21 Efficiency of adjusting soft-switch width

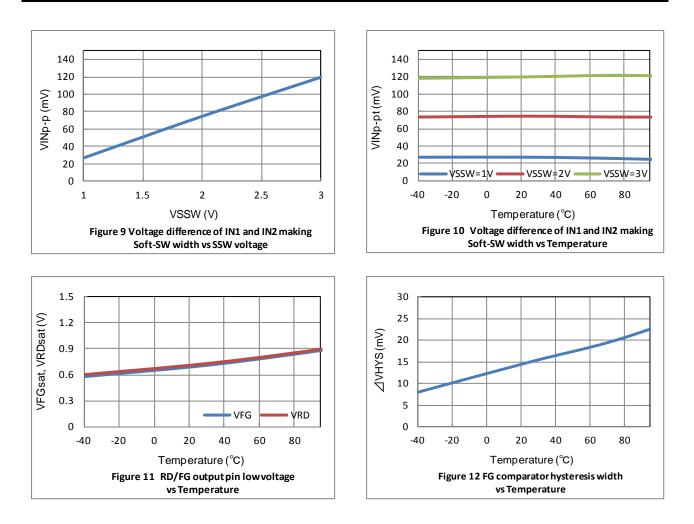

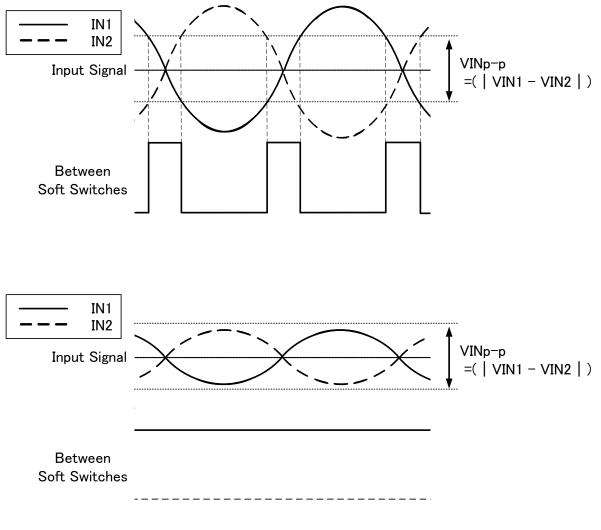

2-3. Reference amplitude of input signal

The width of soft switch in LV8860V is controlled by input signal, IN1/IN2. The external SSW voltage (VSSW) adjusts the difference of input voltage (VINp-p) that creates width of soft switch. The range of SSW input voltage is between 1V and 3V.

Referential difference of input signal amplitude in VSSW range: \*When VSSW = 1V (min), VINp-p = 30 mV --> make sure to input Hall signal with amplitude difference greater than 30mV. \*When VSSW = 2V (open), VINp-p = 90 mV --> make sure to input Hall signal with amplitude difference greater than 90mV. \*When VSSW = 3V (max), VINp-p = 150 mV --> make sure to input Hall signal with amplitude difference greater than 150mV.

When input signal amplitude is greater than VINp-p (as shown in Fig. A below) Width of soft switch is defined as shown in Fig. A.

When input signal amplitude is less than VINp-p. (as shown in Fig. B below). Since input signal is within the range of VINp-p in all rotations, the entire zone is the soft switch zone. Consequently, IC does not operate properly.

For such reason, make sure to input Hall signal with enough amplitude difference to SSW setting value so that IC operates properly.

# 3. Protective Function

# Outline

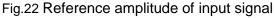

3-1. Current limiter

\*The current limiter is activated when the current detection resistor voltage exceeds 225mV between RF (No.15pin) and GND (No.14pin).

When the current limiter is active, LV8860V turns to current regeneration mode and consumes the redundant current; hence, coil current does not flow any higher than the set value. After operating current regeneration for twice the inner clock (typ20us at normal temperature), LV8860V returns to normal operation mode.

The waveform during current limiter operation is as follows. Only the Rf resistor value has been changed.

<Calculating equation>

#### lolim = Vlim / Rf

Iolim : setting limiter value Vlim : setup voltage (TYP 225mV) Rf : resistance value between RF and GND

Where Rf=0.5 $\Omega$ , current limiter is activated at Iolim=450mA (Iolim = 225mV / 0.5 $\Omega$  = 450mA ).

Fig.23 Current Limiter operation waveform

3-2. Lock protector circuit and automatic recovery circuit

This IC incorporates lock protector circuit and automatic recovery circuit.

If a motor is locked, lock protector function is turned on to prevent motor from destruction.

The lock protector repeats conduction mode for approximately 0.95sec and non-conduction mode for approximately 9.0sec at normal temperature.

If the lock protector is active during conduction, the IC is set to non-conduction mode again.

The above operations are repeated until lock protector is cancelled.

When the lock protector is active, RD signal level is High.

Fig.24 Lock protector operation waveform

3-3. Thermal shutdown function

This IC includes thermal shutdown circuit.

The thermal shutdown circuit is incorporated and the output is turned off when junction temperature Tj exceeds 180°C. As the temperature falls by hysteresis, the output turned on again (automatic restoration).

The thermal shutdown circuit does not guarantee the protection of the final product because it operates when the temperature exceed the junction temperature of Tjmax =  $150^{\circ}$ C. Thermal shutdown temperature =  $180^{\circ}$ C (typ)

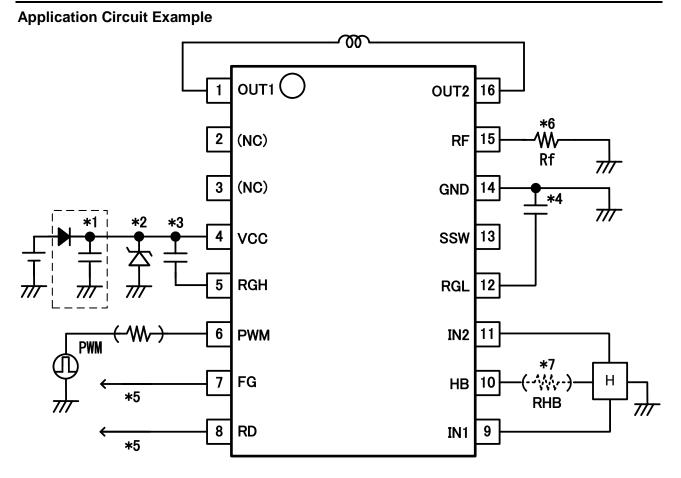

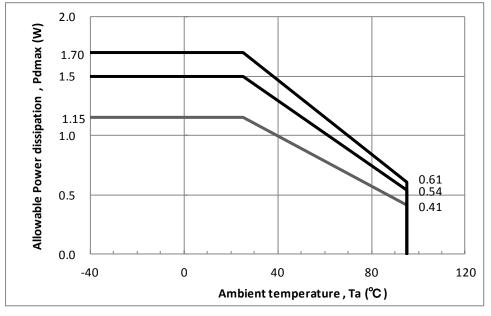

Figure 25. Sample Application Circuit

- \*1 When diode Di is used to prevent destruction of IC from reverse connection, make sure to implement capacitor Cr to secure regenerative current route.

- \*2 If kickback at a phase change is greater, insert zener diode between GND and VCC or implement the larger capacitor between GND and VCC mentioned in \*1.

- \*3 Make sure to implement enough capacitance 0.1uF or greater between RGH pin and VCC pin for stable performance.

- \*4 Make sure to implement enough capacitance 0.1uF or higher between RGL pin and GND pin for stable performance.

- \*5 FG pin and RD pin are open drain output. Keep the pins open when unused.

- \*6 The current limiter is activated when the current detection resistor voltage exceeds 225mV between RF and GND.

Where RL=0.5 $\Omega$ , current limiter is activated at Io=450mA. Setting is made using Rf resistance.

\*7 Hall element outputs stable hall signal with good temperature characteristic when it is biased with constant voltage from HB pin. If you wish to alleviate heating of IC, do not use HB pin. When you do not use this Pin (Pin HB), pull down with resistor of around 10kΩ(recommended).

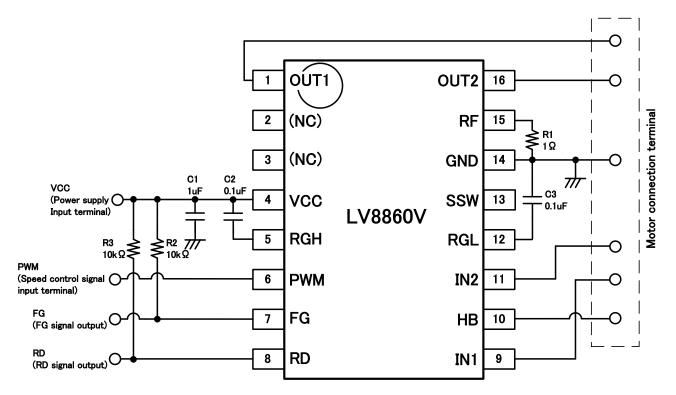

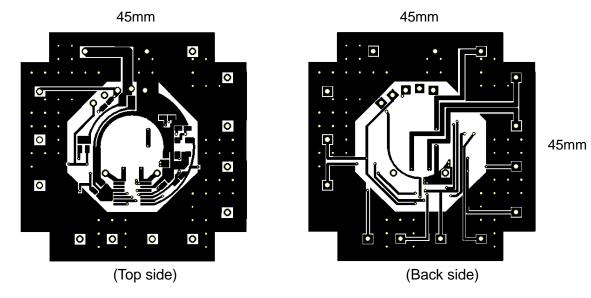

# **Evaluation Board Manual**

# 1. Evaluation Board circuit diagram

# Bill of Materials for LV8860V Evaluation Board

| Designator   | Qty | Description               | Value | Tol      | Footprint          | Manufacturer               | Manufacturer<br>Part Number | Substitution<br>Allowed | Lead<br>Free |

|--------------|-----|---------------------------|-------|----------|--------------------|----------------------------|-----------------------------|-------------------------|--------------|

|              |     |                           |       |          |                    |                            |                             |                         |              |

| IC1          | 1   | Motor<br>Driver           |       |          | SSOP16<br>(225mil) | SANYO<br>semicondu<br>ctor | LV8860V                     | No                      | Yes          |

| C1           | 1   | VM<br>Bypass<br>capacitor | 1µF   | ±10<br>% | 0805               | Murata                     | GRM21BR<br>71H105KA         | Yes                     | Yes          |

| C2,C3        | 2   | capacitor                 | 0.1uF | ±10<br>% | 1608               | Murata                     | GRM188B<br>31H104KA<br>92   | Yes                     | Yes          |

| R1           | 1   | resistor                  | 1Ω    | ±5%      | 0603               | KOA                        | RK73B1JT<br>TD1R0J          | Yes                     | Yes          |

| R2,R3        | 2   | resistor                  | 10kΩ  | ±5%      | 1608               | KOA                        | RK73B1JT<br>103             | Yes                     | Yes          |

| TP1-TP1<br>2 | 8   | Test<br>points            |       |          |                    | MAC8                       | ST-1-3                      | Yes                     | Yes          |

### LV8860V

# Allowable power dissipation

### 2. Motor drive

- 1. Connect a motor to OUT1, OUT2, IN1, IN2, HB and GND.

- 2. Connect the motor power supply to VCC, and connect the GND line to GND.

- 3. Connect the PWM signal supply to PWM if speed control is needed.

- 4. Drive motor to supply voltage to VCC.

- 5. Motor speed is controllable by adjusting duty of PWM signal.

# Caution for layout

- Power supply connection terminal [VCC]

- $\cdot$  VCC is the only power supply.

- The regulator voltage RGL (typ 5V) is the internally generated control power supply.

- Make sure that supply voltage does not exceed the absolute maximum rating under no circumstance. Noncompliance can ve the cause of IC destruction and degradation.

- Caution is required for VCC supply voltage because this IC performs switching.

The bypass capacitor of the VCC power supply should be close to the IC as much as possible to stabilize voltage. Also if you intend to use large current or back EMF is high, please augment enough capacitance.

- GND terminal [GND]

GND terminal is 0V, hence pattern layout should be in low impedance. Since high current flows into GND, GND terminal should be connected independently.

- Internal power supply regulator terminal [RGL, RGH]

- RGL is the control power supply for logic. (typ 5V). RGH is the gate voltage power supply for output Pch-Tr (typ VCC-4.5V).

- $\boldsymbol{\cdot}$  When VCC is energized, the voltage is impressed to RGL and RGH.

- Connect a capacitor to RGL and RGH respectively to stabilize internal power supply. (Recommended value: 0.1uF or higher)

- <u>PWM signal input terminal [PWM]</u>

- PWM signal input could be the cause of noise. Hence, caution is required for pattern layout.

- OUT terminal [OUT1, OUT2]

- During PWM operation, VOUT terminal could be the cause of noise. Hence, caution is required for pattern layout.

- · Since motor current flows into OUT terminals, they should be connected at low impedance.

- Output voltage may boost due to back EMF. Make sure that the voltage does not exceed the absolute MAX ratings under no circumstance. Noncompliance can be the cause of IC destruction and degradation.

- <u>Current sense resistor connection terminal [RF]</u>

- Since motor current flows from RF to GND line, it should be connected independently at low impedance.

- <u>NC terminal</u>

- $\cdot$  NC terminal is not connected to the internal circuit of the IC.

- Use NC terminal to keep the layout for power supply line and GND line as fat and short as possible.

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of June, 2011. Specifications and information herein are subject to change without notice.