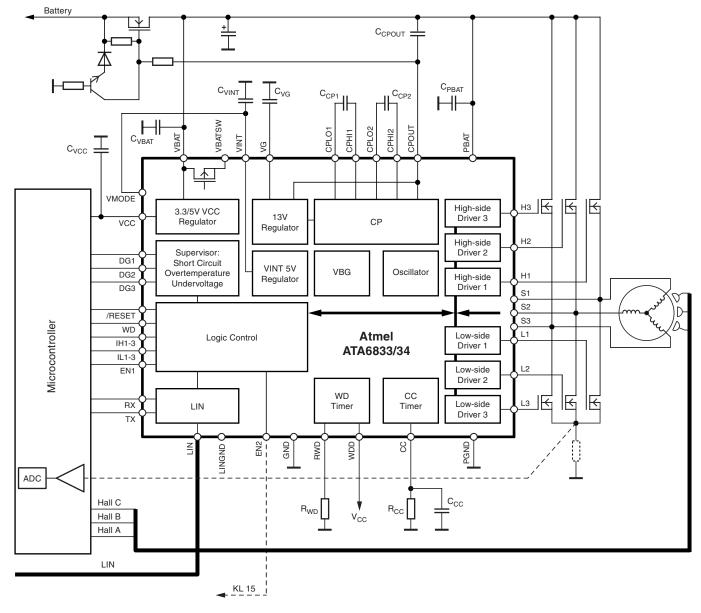

### 1. Description

The Atmel<sup>®</sup> ATA6833C and Atmel ATA6834C are system basis chips for three-phase brushless DC motor controllers designed in Atmel's state-of-the-art 0.8µm SOI technology SMART-I.S.<sup>™</sup>1. In combination with a microcontroller and six discrete power MOSFETs, the system basis chip forms a BLDC motor control unit for automotive applications. In addition, the circuits provide a 3.3V/5V linear regulator and a window watchdog.

The circuit includes various control and protection functions like overvoltage and overtemperature protection, short circuit detection, and undervoltage management. Thanks to these function blocks, the driver fulfils a maximum of safety requirements and offers a high integration level to save cost and space in various applications. The target applications are most suitable for the automotive market due to the robust technology and the high qualification level. Atmel ATA6834C, in particular, is designed for applications in a high-temperature environment.

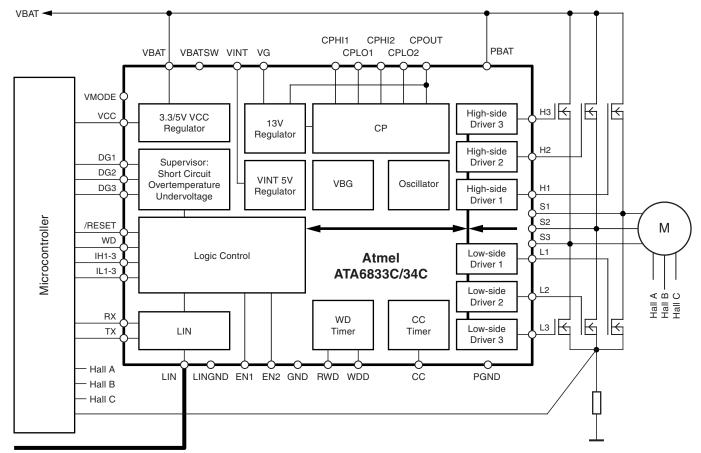

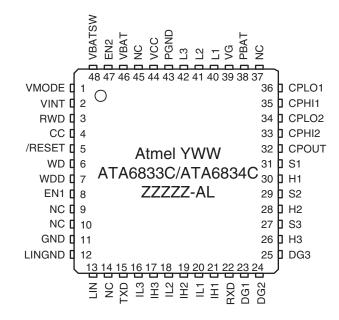

## 2. Pin Configuration

Figure 2-1. Pinning QFN48

Note:

YWWDate code (Y = Year - above 2000, WW = week number)ATA683xProduct name

ZZZZZ Wafer lot number

AL Assembly sub-lot number

#### Table 2-1. Pin Description

|     | in Description |     |                                                         |

|-----|----------------|-----|---------------------------------------------------------|

| Pin | Symbol         | I/O | Function                                                |

| 1   | VMODE          | I   | Selector for $V_{CC}$ and interface logic voltage level |

| 2   | VINT           | I/O | Blocking capacitor                                      |

| 3   | RWD            | I   | Resistor defining the watchdog interval                 |

| 4   | CC             | I/O | RC combination to adjust cross conduction time          |

| 5   | /RESET         | 0   | Reset signal for microcontroller                        |

| 6   | WD             | I   | Watchdog trigger signal                                 |

| 7   | WDD            | I   | Enable and disable the watchdog                         |

| 8   | EN1            | I   | Microcontroller output to switch system in Sleep Mode   |

| 9   | N.C.           |     | Connect to GND                                          |

| 10  | N.C.           |     | Connect to GND                                          |

| 11  | GND            | I   | Ground                                                  |

| 12  | LINGND         |     | Ground for LIN connected to GND                         |

| 13  | LIN            | I/O | LIN-bus terminal                                        |

| 14  | NC             |     | Connect to GND                                          |

| 15  | TXD            | I   | Transmit signal to LIN bus from microcontroller         |

| 16  | IL3            | I   | Control Input for output L3                             |

| 17  | IH3            | I   | Control Input for output H3                             |

|     |                |     |                                                         |

| Table 2-1. | Pin Description |     |                                                                          |

|------------|-----------------|-----|--------------------------------------------------------------------------|

| Pin        | Symbol          | I/O | Function                                                                 |

| 18         | IL2             | I   | Control Input for output L2                                              |

| 19         | IH2             | Ι   | Control Input for output H2                                              |

| 20         | IL1             | I   | Control Input for output L1                                              |

| 21         | IH1             | I   | Control Input for output H1                                              |

| 22         | RXD             | 0   | Receive signal from LIN bus for microcontroller                          |

| 23         | DG1             | 0   | Diagnostic output 1                                                      |

| 24         | DG2             | 0   | Diagnostic output 2                                                      |

| 25         | DG3             | 0   | Diagnostic output 3                                                      |

| 26         | H3              | 0   | Gate voltage high-side 3                                                 |

| 27         | S3              | I/O | Voltage at half bridge 3                                                 |

| 28         | H2              | 0   | Gate voltage high-side 2                                                 |

| 29         | S2              | I/O | Voltage at half bridge 2                                                 |

| 30         | H1              | 0   | Gate voltage high-side 1                                                 |

| 31         | S1              | I/O | Voltage at half bridge 1                                                 |

| 32         | CPOUT           | I/O | Charge pump output capacitor                                             |

| 33         | CPHI2           | I   | Charge pump capacitor 2                                                  |

| 34         | CPLO2           | 0   | Charge pump capacitor 2                                                  |

| 35         | CPHI1           | I   | Charge pump capacitor 1                                                  |

| 36         | CPLO1           | 0   | Charge pump capacitor 1                                                  |

| 37         | NC              |     | Connect to GND                                                           |

| 38         | PBAT            | I   | Power supply (after reverse protection) for charge pump and gate drivers |

| 39         | VG              | I/O | Blocking capacitor                                                       |

| 40         | L1              | 0   | Gate voltage H-bridge, low-side 1                                        |

| 41         | L2              | 0   | Gate voltage H-bridge, low-side 2                                        |

| 42         | L3              | 0   | Gate voltage H-bridge, low-side 3                                        |

| 43         | PGND            | I   | Power ground for H-bridge and charge pump                                |

| 44         | VCC             | 0   | 5V/100mA supply for microcontroller                                      |

| 45         | NC              |     | Connect to GND                                                           |

| 46         | VBAT            | I   | Supply voltage for IC core (after reverse protection)                    |

| 47         | EN2             | I   | High voltage enable input                                                |

| 48         | VBATSW          | 0   | 100 $\Omega$ PMOS switch from V <sub>BAT</sub>                           |

|            |                 |     |                                                                          |

Table 2-1. Pin Description

### 3. Functional Description

### 3.1 Power Supply Unit with Supervisor Functions

#### 3.1.1 Power Supply

The IC has to be supplied by a reverse-protected battery voltage. To prevent damage to the IC, proper external protection circuitry has to be added. It is recommended to use at least one capacitor combination of storage and RF capacitors behind the reverse protection circuitry, which is connected close to the VBAT and GND pins of the IC.

A fully integrated low-power and low-drop regulator (VINT regulator), stabilized by an external blocking capacitor, provides the necessary low-voltage supply needed for the wake-up process. A trimmed low-power band gap is used as reference for the VINT regulator as well as for the VCC regulator. All internal blocks are supplied by VINT regulator. VINT regulator must not be used for any external supply purposes.

Nothing inside the IC except the logic interface to the external microcontroller is supplied by the 5V/3.3V VCC regulator.

Both voltage regulators are checked by a "power-good comparator", which keeps the whole chip in reset as long as the internal supply voltage (VINT regulator output) is too low and generates a reset for the external microcontroller if the output voltage of the VCC regulator is not sufficient.

### 3.1.2 VBatt Switch

This high-voltage switch provides the battery voltage at pin VBATSW for various purposes. It is switched ON after power on reset when the IC transits to Active Mode and it will only turn OFF when the IC changes to Sleep Mode. Watchdog resets do not have an effect on the switch. The switch can be used for measuring purposes as well as to switch on external voltage regulators.

#### 3.1.3 Voltage Supervisor

This function is implemented to protect the IC and the external power MOS transistors from damage due to overvoltage on PBAT input. In the event of overvoltage ( $V_{THOV}$ ) or undervoltage ( $V_{THUV}$ ), the external NMOS motor driver transistors will be switched off. The failure state will be flagged on DG2 pin. It is recommended to block PBAT with an external RF capacitor to suppress high frequency disturbances.

#### 3.1.4 Temperature Supervisor

An integrated temperature sensor prevents the IC from overheating. If the temperature is above the overtemperature prewarning threshold  $T_{JPW set}$ , the diagnostic pin DG3 will be switched to HIGH to signal this event to the external microcontroller. The microcontroller should take actions to reduce the power dissipation in the IC. If the temperature rises above the overtemperature shutdown threshold  $T_{J switch off}$ , the VCC regulator and all output drivers together with the LIN transceiver will be switched OFF immediately and the /RESET signal will go LOW. Both thresholds have a built-in hysteresis to avoid oscillations. The IC will return to normal operation (Active Mode) when it has cooled down below the shutdown threshold. When the junction temperature drops below the pre-warning threshold, bit DG3 will be switched LOW.

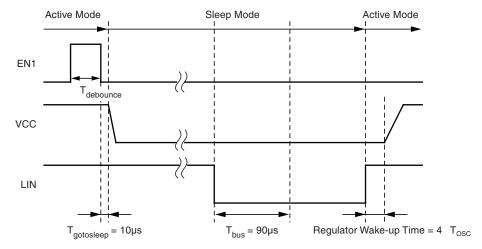

### 3.2 Active Mode and Sleep Mode

The IC has two modes: Sleep Mode and Active Mode. Switching between the modes is described below. By default the IC starts in Active Mode (which means normal operation) after power-on. A *Go to Sleep* procedure switches the IC from Active Mode to Sleep Mode (standby). A *Go to Active* procedure brings the IC back from Sleep Mode to Active Mode. When in Sleep Mode the internal 5V supply (VINT regulator), the EN2 pin input structure, and a certain part of the LIN receiver remain active to ensure a proper startup of the system. The VCC regulator is turned off.

The Go to Sleep and Go to Active procedures are implemented as follows:

#### Go to Sleep

Pin EN1 is a low-voltage input supplied by the VCC regulator. It is ESD protected by diodes against VCC and GND. Thus the input voltage at pin EN1 must not go below GND or exceed the output voltage of the VCC regulator. A transition from HIGH to LOW followed by a permanent LOW signal for a minimum time period  $t_{gotosleep}$  (typical 10µs) at pin EN1 switches the IC to Sleep Mode as the EN1 is edge triggered. V<sub>CC</sub> is switched off in Sleep Mode. It is recommended to keep EN1 LOW during normal operation.

#### Go to Active Using Pin EN2

Pin EN2 is a high-voltage input for external wake-up signals. Its input structure consists of a comparator with a built-in hysteresis. It is ESD-protected by diodes against GND and  $V_{BAT}$ , B, and for this reason the applied input voltage must not go below GND or exceed  $V_{BAT}$ . Pulling EN2 up to  $V_{BAT}$  switches the IC to Active Mode. EN2 is debounced and edge triggered.

#### Go to Active Using the LIN Interface

Using the LIN interface provides a second possibility to wake-up the IC (see Figure 3-1). A falling edge at pin LIN followed by a dominant bus level maintained for a minimum time period ( $T_{bus}$ ) and ending with a rising edge leads to a remote wake-up request. The device switches from Sleep Mode to Active Mode. The VCC regulator is activated and the internal LIN slave termination resistor is switched on.

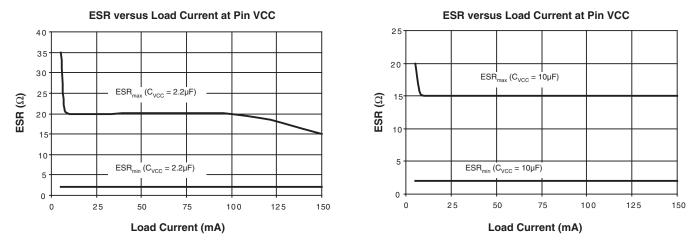

### 3.3 5V/3.3V VCC Regulator

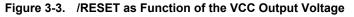

The 5V/3.3V regulator is fully integrated. It requires an external electrolytic capacitor in the range of 2.2 $\mu$ F up to 10 $\mu$ F and with an ESR in the range from 2 $\Omega$  to 15 $\Omega$  for stability (see Figure 3-2). The output voltage can be configured as either 5V or 3.3V by connecting pin VMODE to either pin VINT or GND. Since the regulator is not designed to be switched between both output voltages during operation, it is advisable to hard-wire VMODE pin. The logic levels of the microcontroller interface are adapted to the VCC regulator output voltage. The maximum output current (I<sub>OS1</sub>) of the regulator is 100mA. For T<sub>J</sub> > 150°C the I<sub>OS1</sub> of Atmel<sup>®</sup> ATA6834C is reduced to 80mA. The VCC regulator has a built-in short circuit protection. A comparator checks the output voltage of the VCC regulator and keeps the external microcontroller in reset as long as the voltage is below the lower operation minimum (shown in Figure 3-3).

Figure 3-2. ESR versus Load Current for External Capacitors with Different Values

7

### 3.4 Reset and Watchdog Management

The watchdog timing is based on the trimmed internal watchdog oscillator. Its period time  $T_{OSC}$  is determined by the external resistor  $R_{WD}$ . A HIGH signal on WDD pin enables the watchdog function; a LOW signal disables it. Since WDD pin is equipped with an internal pull-up resistor the watchdog is enabled by default. In order to keep the current consumption as low as possible the watchdog is switched off during Sleep Mode.

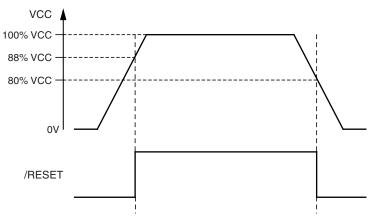

The timing diagram in Figure 3-4 shows the watchdog and external reset timing.

Figure 3-4. Timing Diagram of the Watchdog in Conjunction with the /RESET Signal

After power-up of the VCC regulator (VCC output exceeds 88% of its nominal value) /RESET output stays LOW for the timeout period t<sub>res</sub> (typical 10ms). Subsequently /RESET output switches to HIGH. During the following time t<sub>d</sub> (typical 500ms) a rising edge at the input WD is expected otherwise another external reset will be triggered.

When the watchdog has been correctly triggered for the first time, normal watch-dog operation begins. A normal watchdog cycle consists of two time sections  $t_1$  and  $t_2$  followed by a short pulse for the time  $t_{resshort}$  at /RESET if no valid trigger has been applied at pin WD during  $t_2$ . Rising edges on WD pin during  $t_1$  also cause a short pulse on /RESET. Start for such a cycle is always the time of the last rising edge either on WD pin or on /RESET pin.

If the watchdog is disabled (WDD = LOW), only the initial reset for the time  $t_{res}$  after power-up will be generated.

Additional resets will be generated if the VCC output voltage drops below 80% of its nominal value.

The following example demonstrates how to calculate the timing scheme for valid watchdog trigger pulses, which the external microcontroller has to provide in order to prevent undesired resets.

#### Example:

Using an external resistor  $R_{WD}$  = 33 k $\Omega \pm 1\%$  results in typical parameters as follows:

$$\begin{split} T_{OSC} &= 12.4 \mu s \\ t_1 &= 980 \times T_{OSC} = 12.1 ms \pm 10\% \\ t_2 &= 780 \times T_{OSC} = 9.6 ms \pm 10\% \end{split}$$

$$t_1 + t_2 = 21.7 \text{ms} \pm 10\%$$

Hence, the minimum time the external microcontroller has to wait before pin WD can be triggered is in worst case  $t_{min} = 1.1 \times t_1 = 13.3$ ms. The maximum time for the watchdog trigger on WD pin is  $t_{max} = 0.9 \times (t_1 + t_2) = 19.5$ ms. Thus watchdog trigger input must remain within  $t_{max} - t_{min} = 6.2$ ms.

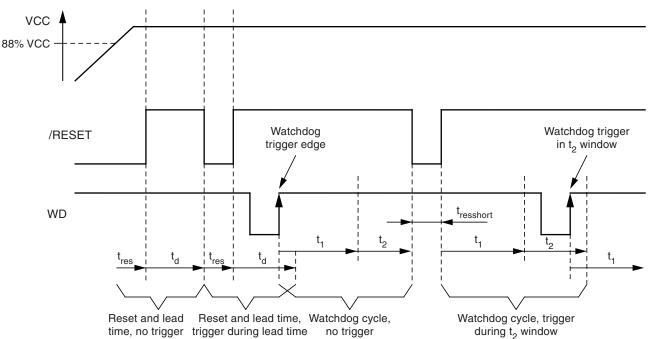

Other values can be set up by picking a different resistor value for  $R_{WD}$ . The dependency of  $T_{OSC}$  on the value of  $R_{WD}$  is shown in Figure 3-5.

Figure 3-5. T<sub>OSC</sub> versus R<sub>WD</sub>

The tolerance of  $T_{OSC}$  is ±10% for resistors  $R_{WD}$  with maximum ±1% in tolerance.

#### 3.5 Charge Pump

A charge pump has been implemented in order to provide sufficient voltage to operate the external high-side power-NMOS transistors and the VG regulator, which drives the low-side Power-NMOS transistors. The charge pump output voltage at CPOUT pin is controlled to settle typically about 15V above the voltage at pin PBAT. A built-in supervisor circuit checks if the output voltage is sufficient to operate the VG regulator and external Power-NMOS transistors. The output voltage is accepted as good when it rises above VCP<sub>CPGOOD</sub>. A charge pump failure is flagged at DG2 if this minimum can not be reached or if the output voltage drops below the lower threshold of VCP<sub>CPGOOD</sub> due to overloading.

The two shuffle capacitors should have the same value. The value of the reservoir capacitor should be at least twice the value of one shuffle capacitor. Two external shuffle capacitors and an external reservoir capacitor have to be provided. The typical values for the two shuffle capacitor is 100nF, and for the reservoir capacitor is 470nF. All capacitors should be ceramic. It is advisable to pick a reservoir capacitor with twice or three-times the size of the two equally-sized shuffle capacitors. The greater the capacitors, the greater the output current capability.

### 3.6 VG Regulator

The VG regulator provides a stable voltage to supply the low-side gate drivers and to deliver sufficient voltage for the external low-side Power-NMOS transistors. Typically the output voltage is 12V. In order to guarantee reliable operation even with a low battery voltage, the VG regulator is supplied by the charge pump output. For stability, an external ceramic capacitor of typically 470nF has to be provided. There is no internal supervision of the VG output voltage.

### 3.7 Output Drivers and Control Inputs IL1-IL3, IH1-IH3

This IC offers six push-pull output drivers for the external low-side and high-side power-NMOS transistors. To guarantee reliable operation, the low-side drivers are supplied by the VG regulator while the high-side drivers are supplied directly by the charge pump. All drivers are designed to operate at switching frequencies in the range of DC up to 50kHz. The maximum gate charge that can be delivered to each external Power-NMOS transistor at 50kHz is 100nC.

The output drivers are directly controlled by the digital input pins IL1 to IL3 and IH1 to IH3 (see Table 3-1). All pins are equipped with an internal pull-down resistor. To operate the output drivers properly the following requirements have to be fulfilled:

- 1. Device is in Active Mode.

- 2. In case of watchdog is enabled, at least one valid watchdog trigger has been accepted.

- 3. The voltage at pin PBAT lies within its operation range. Neither undervoltage nor overvoltage is present.

- 4. The charge pump output voltage has been accepted as good, thus it exceeded VCP<sub>CPGOOD</sub>.

- 5. No overtemperature shutdown has occurred.

If a short circuit is detected by one of the sense inputs S1 to S3, the output drivers will be switched off after a debounce time of 6 µs and the output DG1 will be flagged (see also Section 3.8 "Short Circuit Detection" on page 10). The output drivers will be enabled again and DG1 will be cleared with a rising edge at one of the control inputs (IL1 to IL3, IH1 to IH3).

Additional logic prevents short circuits due to switching on one power-NMOS transistor while the opposite one in the same branch is switched on already.

|        |                          | -                        | -                                                      |                          |

|--------|--------------------------|--------------------------|--------------------------------------------------------|--------------------------|

| Mode   | Control Inputs<br>IL(13) | Control Inputs<br>IH(13) | Driver Stage for External<br>Power MOS<br>L(13), H(13) | Comments                 |

| Sleep  | Х                        | Х                        | OFF                                                    | Sleep Mode               |

| Active | 0                        | 0                        | OFF                                                    |                          |

| Active | 1                        | 0                        | L(13) ON, H(13) OFF                                    |                          |

| Active | 0                        | 1                        | H(13) ON, L(13) OFF                                    |                          |

| Active | 1                        | 1                        | OFF                                                    | Shoot-through protection |

| Table 3-1. | Status of the Output Drivers Depending on the Control Inputs |

|------------|--------------------------------------------------------------|

|            | etatae et ale eupar entre e epenang en ale eentre inpate     |

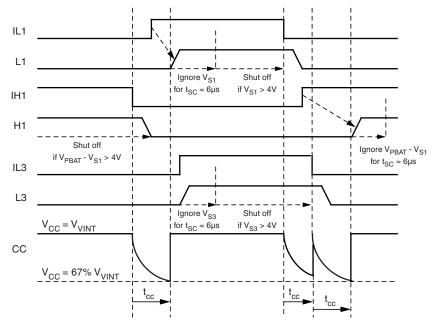

### 3.8 Short Circuit Detection

Short circuits in the motor bridge circuitry are sensed by S1 to S3 inputs. Internal comparators monitor the voltage differences between the drain and the source terminals of the external power-NMOS transistors. If one transistor switches on and its drain-source voltage exceeds  $V_{SC}$  threshold (typically 4V) after a blanking time  $t_{SC}$  (typically 6µs, see Figure 3-6), a short circuit in this branch will be detected. In this case, all output drivers will be switched off immediately and pin DG1 will be set to HIGH. With a rising edge at any of the pins IL1 to IL3 or IH1 to IH3, the diagnostic output DG1will be reset and the drivers can be switched on again.

### 3.9 Cross Conduction Timer

In order to prevent damage of the motor bridge due to peak currents a non-overlapping phase for switching the power-NMOS transistors is mandatory. Therefore, a cross conduction timer has been implemented to prevent switching on any output driver for a time  $t_{CC}$  after any other driver has been switched off. This also accounts for toggling any other driver after a short circuit was detected. An external RC parallel combination defines the value for  $t_{CC}$  and can be estimated as follows:

$t_{cc} = K_{cc} \times R_{cc} (k\Omega) \times C_{cc} (nF), K_{cc}$  is specified in Section 8. "Electrical Characteristics" on page 15.

The RC combination is connected between CC and GND pins. When one of the drivers has been switched off the RC combination is charged to 5V (VINT) and discharged with its time constant. Any low to high transition at the control inputs will be masked out at the driver outputs until the voltage at CC pin drops below 67% of its initial value (VINT). The timer will be re-triggered at any time by any falling edge at the control inputs. This is shown in the following figure.

At least  $5k\Omega$  minimum and 5nF at maximum should be used as values for the RC combination.  $10k\Omega$  is recommended. If the non-overlapping phase is controlled by the external microcontroller, it is possible to do without the external capacitor. The minimum time  $t_{CC}$  is defined by the parasitic capacitance at CC pin.

### 3.10 Diagnostic Outputs D1 - D3

As mentioned in the sections above, the diagnostic outputs DG1 to DG3 are used to signal failures. This is summarized in the following table.

Note: This is only valid for VCC > V<sub>tHRESHLow</sub>. Otherwise all diagnostic outputs will be tristated.

| Device Status |                         |                                                                                                                              |                                                                                                                                                                                           | Diagnostic Outputs                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OT1           | ov                      | UV                                                                                                                           | SC                                                                                                                                                                                        | DG1                                                                                                                                                                                                                                                    | DG2                                                                                                                                                                                                                                                 | DG3                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Х             | Х                       | Х                                                                                                                            | Х                                                                                                                                                                                         | -                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                  | Charge pump failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1             | Х                       | Х                                                                                                                            | Х                                                                                                                                                                                         | -                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                  | Overtemperature prewarning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Х             | 1                       | Х                                                                                                                            | Х                                                                                                                                                                                         | -                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                  | Overvoltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Х             | Х                       | 1                                                                                                                            | Х                                                                                                                                                                                         | -                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                  | Undervoltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Х             | Х                       | Х                                                                                                                            | 1                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                  | Short circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | OT1<br>X<br>1<br>X<br>X | OT1         OV           X         X           1         X           X         1           X         1           X         X | OT1         OV         UV           X         X         X           1         X         X           X         1         X           X         1         X           X         1         X | OT1         OV         UV         SC           X         X         X         X           1         X         X         X           X         1         X         X           X         1         X         X           X         1         X         X | OT1         OV         UV         SC         DG1           X         X         X         X            1         X         X         X            X         1         X         X            X         1         X             X         1         X | OT1         OV         UV         SC         DG1         DG2           X         X         X         X         -         1           1         X         X         X         -         -           X         1         X         X         -         1           X         1         X         X         -         1           X         1         X         X         -         1 | OT1         OV         UV         SC         DG1         DG2         DG3           X         X         X         X         -         1         -           1         X         X         X         -         1         -           X         1         X         X         -         1         -           X         1         X         X         -         1         -           X         1         X         X         -         1         -           X         X         1         X         -         1         - |

#### Table 3-2. Status of the Diagnostic Outputs (Normal Operation)

Note: X represents: no effect)

OT1: overtemperature warning OV: overvoltage of PBAT UV: undervoltage of PBAT SC: short circuit CPOK: charge pump OK

In order to differentiate between LIN and EN2 wake-up, DG1 output will be set to LOW or HIGH respectively. LOW indicates wake-up by LIN, HIGH indicates wake-up by EN2. DG1 output will be cleared by the first valid watchdog trigger after wake-up or by the first rising edge at one of the control inputs (IL1 to IL3 and IH1 toIH3) if the watchdog is disabled.

#### Table 3-3. Indicating Wake-up Source

| Diagnostic Outputs |     |     |                |

|--------------------|-----|-----|----------------|

| DG1                | DG2 | DG3 | Wake-up Source |

| 1                  | -   | -   | EN2            |

| 0                  | -   | -   | LIN            |

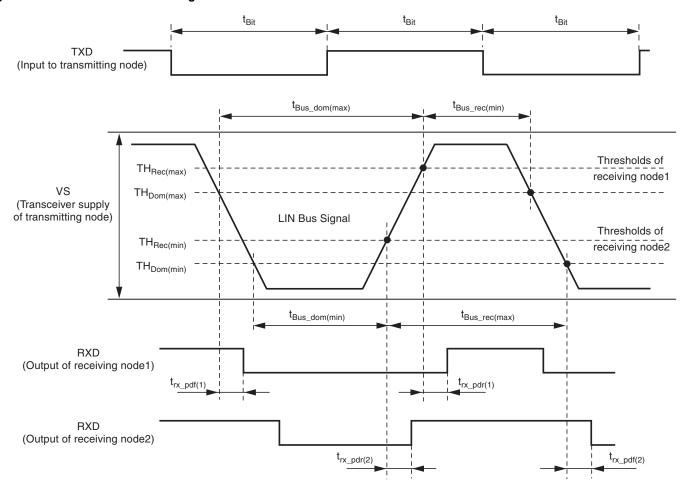

#### 3.11 LIN Transceiver

Atmel<sup>®</sup> ATA6833C and Atmel ATA6834C include a fully integrated LIN transceiver complying with LIN specification 2.1 and SAEJ2602 2. The transceiver consists of a low-side driver with slew rate control, wave shaping, current limiting, and a high voltage comparator followed by a debouncing unit in the receiver.

During transmission, the data applied at pin TXD will be transferred to the bus driver to generate a bus signal on LIN pin. TXD input has an internal pull-up resistor.

To minimize the electromagnetic emission of the bus line, the bus driver has a built-in slew rate control and wave-shaping unit. The transmission will be aborted by a thermal shutdown or by a transition to Sleep Mode.

Figure 3-7. Definition of Bus Timing Parameters

The recessive BUS level is generated from the integrated  $30k\Omega$  pull-up resistor in series with an active diode. This diode protects against reverse currents on the bus line in case of a voltage difference between the bus line and VSUP (V<sub>BUS</sub> > V<sub>SUP</sub>). No additional termination resistor is necessary to use the IC as a LIN slave. If this IC is used as a LIN master, the LIN pin is terminated by an external  $1k\Omega$  resistor in series with a diode to VBAT.

As PWM communication directly over the LIN transceiver in both directions is possible, there is no TXD timeout feature implemented in the LIN transceiver.

## 4. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters             | Pin                                | Symbol                                                                                                              | Min.                     | Max.                      | Unit |

|------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|------|

| Input voltage          | PGND                               | V <sub>PGND</sub>                                                                                                   | -0.3                     | +0.3                      | V    |

| Negative input current | VBAT                               | IVBAT                                                                                                               | -15                      |                           | mA   |

| Negative input current | PBAT                               | IPBAT                                                                                                               | -20                      |                           | mA   |

| Supply voltage         | VBAT                               | V <sub>VBAT</sub>                                                                                                   |                          | +40                       | V    |

| Supply voltage         | PBAT                               | V <sub>PBAT</sub>                                                                                                   |                          | +40                       | V    |

| Logic output voltage   | /RESET, DG1, DG2,<br>DG3, RXD      | $\begin{array}{c} V_{\text{/RESET}}, V_{\text{DG1}}, V_{\text{DG2}}, \\ V_{\text{DG3}}, V_{\text{RXD}} \end{array}$ | -0.3                     | V <sub>VCC</sub> + 0.3    | V    |

| Logic input voltage    | IL1-3, IH1-3, WD,<br>WDD, EN1, TXD | $\begin{array}{c} V_{IL1-3}, V_{IH1-3}, V_{WD}, V_{EN1}, \\ V_{TXD} \end{array}$                                    | -0.3                     | V <sub>VCC</sub> + 0.3    | V    |

| Output voltage         | VINT, VCC                          | $V_{INT}$ , $V_{VVCC}$                                                                                              | -0.3                     | +5.5                      | V    |

| Analog input voltage   | RWD, CC                            | V <sub>RWD</sub>                                                                                                    | -0.3                     | V <sub>VCC</sub> + 0.3    | V    |

| Digital input voltage  | EN2                                | V <sub>EN2</sub>                                                                                                    | -0.3                     | V <sub>VBAT</sub> + 0.3   | V    |

| Digital input voltage  | VMODE                              | V <sub>VMODE</sub>                                                                                                  | -0.3                     | V <sub>VINT</sub> + 0.3   | V    |

| Output voltage         | VG                                 | V <sub>VG</sub>                                                                                                     |                          | +16                       | V    |

| Input voltage          | LIN                                | V <sub>VLIN</sub>                                                                                                   | -27                      | V <sub>VBAT</sub> + 2     | V    |

| Output voltage         | S1, S2, S3                         | $V_{S1}, V_{S2}, V_{S3}$                                                                                            | (6)                      | +30                       | V    |

| Output voltage         | L1, L2, L3                         | $V_{L1}, V_{L2}, V_{L3}$                                                                                            | $V_{PGND} - 0.3$         | V <sub>VG</sub> + 0.3     | V    |

| Output voltage         | H1, H2, L3                         | V <sub>H1</sub> , V <sub>H2</sub> , V <sub>H3</sub>                                                                 | V <sub>S1, 2, 3</sub> -1 | V <sub>S1, 2, 3</sub> +16 | V    |

| Charge pump            | CPLO1, 2                           | $V_{CPLO1}, V_{CPLO2}$                                                                                              |                          | V <sub>PBAT</sub> + 0.3   | V    |

| Charge pump            | CPHI1, 2                           | $V_{CPHO1}, V_{CPHO2}$                                                                                              |                          | V <sub>CPOUT</sub> + 0.3  | V    |

| Output voltage         | CPOUT                              | V <sub>CPOUT</sub>                                                                                                  |                          | +40                       | V    |

| Output voltage         | VBATSW                             | V <sub>VBATSW</sub>                                                                                                 | -0.3                     | V <sub>VBAT</sub> + 0.3   | V    |

| Storage temperature    |                                    | T <sub>Storage</sub>                                                                                                | -55                      | +150                      | °C   |

| Reverse current        | CPLOx, CPHIx, VG,<br>CPOUT, Sx     | I <sub>CPLOX_R</sub> , I <sub>CPHIX_R</sub> , I <sub>VG_R</sub> ,<br>I <sub>CPOUT_R</sub> , I <sub>SX_R</sub>       | -2                       |                           | mA   |

|                        | Lx, Hx                             | I <sub>Lx_R</sub> , I <sub>Hx_R</sub>                                                                               | -1                       |                           | mA   |

All voltages are referenced to pin GND. (xxx) Values for the Atmel® ATA6834C.

Note: Estimated values take  $T_J > 150^{\circ}C$  into account.

### 5. Thermal Resistance

| Parameters                                                               | Symbol            | Value | Unit |

|--------------------------------------------------------------------------|-------------------|-------|------|

| Thermal resistance junction to heat slug                                 | R <sub>thjc</sub> | < 5   | K/W  |

| Thermal resistance junction to ambient when heat slug is soldered to PCB | R <sub>thja</sub> | 25    | K/W  |

# 6. Operating Range

The operating conditions define the limits for functional operation and parametric characteristics of the device. Functionality outside these limits is not implied unless otherwise stated explicitly. (xxx) Values for the Atmel<sup>®</sup> ATA6834C

| Parameters                              | Symbol            | Min               | Max                              | Unit |

|-----------------------------------------|-------------------|-------------------|----------------------------------|------|

| Operating supply voltage <sup>(1)</sup> | V <sub>VBAT</sub> | 5.5               | V <sub>THOV</sub> <sup>(4)</sup> | V    |

| Operating supply voltage <sup>(2)</sup> | V <sub>VBAT</sub> | 4.3               | 5.5                              | V    |

| Operating supply voltage <sup>(3)</sup> | V <sub>VBAT</sub> | V <sub>THOV</sub> | 40                               | V    |

| Ambient temperature range               | T <sub>A</sub>    | -40               | +150                             | °C   |

| Junction temperature range              | Τ <sub>J</sub>    | -40               | +150 (200)                       | °C   |

Notes: 1. Full functionality

- 2. Output drivers are switched off, extended range for parameters for voltage regulators

- 3. Output drivers and charge pump are switched off

## 7. Noise and Surge Immunity, ESD and Latch-up

| Parameters                                                                                 | Standard and Test Conditions                                                          | Value                  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|

| Conducted interferences                                                                    | ISO 7637-1                                                                            | Level 4 <sup>(1)</sup> |

| Conducted disturbances                                                                     | CISP25                                                                                | Level 5                |

| ESD according to IBEE LIN EMC<br>- Pins LIN, PBAT, VBAT<br>- Pin EN2 (33kΩserial resistor) | Test specification 1.0 following IEC 61000-4-2                                        | ±6 kV<br>±5 kV         |

| ESD HBM with 1.5kΩ/100pF                                                                   | ESD- STM5.1-2001<br>JESD22-A114E 2007<br>CEI/IEC 60749-26: 2006<br>AEC-Q100-002-Ref_D | ±2 kV                  |

| ESD HBM with 1.5kΩ/100pF<br>Pins EN2, LIN, PBAT, VBAT against GND                          | ESD- STM5.1-2001<br>JESD22-A114E 2007<br>CEI/IEC 60749-26: 2006<br>AEC-Q100-002-Ref_D | ±8 kV                  |

| ESD CDM (field induced method)                                                             | ESD STM5.3.1 - 1999                                                                   | ±500V                  |

| Note: 1. Test pulse 5: V <sub>bat max</sub> = 40V                                          |                                                                                       |                        |

- Static latch-up tested according to AEC-Q100-004 and JESD78.

- 3 to 6 samples, 0 failures

- Electrical post-stress testing at room temperature

In test, the voltage at the pins VBAT, LIN, CP, VBATSW, Hx, and Sx must not exceed 45V when not able to drive the specified current.

## 8. Electrical Characteristics

All parameters given are valid for  $5.5V \le V_{VBAT} \le 18V$  and for  $-40^{\circ}C \le T_{J} \le 150^{\circ}C$  (200°C) unless stated otherwise. All values refer to PIN GND. (xxx) Values for the Atmel<sup>®</sup> ATA6834C.

| No.  | Parameters                                               | Test Conditions                                                                                                                                                                                                                                                      | Pin             | Symbol                                               | Min.         | Тур.         | Max.         | Unit | Type* |

|------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------|--------------|--------------|--------------|------|-------|

| 1    | Power Supply and Supervis                                | or Functions                                                                                                                                                                                                                                                         |                 |                                                      |              |              |              |      |       |

| 1.1  | Current consumption $V_{VBAT}$                           | V <sub>VBAT</sub> = 13.5V <sup>(1)</sup>                                                                                                                                                                                                                             | VBAT            | I <sub>VBAT</sub>                                    |              |              | 7            | mA   | А     |

| 1.3  | Current consumption $V_{\text{VBAT}}$ in Standby Mode    |                                                                                                                                                                                                                                                                      | VBAT            | I <sub>VBAT</sub>                                    |              |              | 65           | μA   | А     |

| 1.4  | Current consumption $V_{\text{VBAT}}$ in Standby Mode    | V <sub>PBAT</sub> = 13.5V                                                                                                                                                                                                                                            | PBAT            | I <sub>VPBAT</sub>                                   | 9.0          |              | 20.0         | μA   | А     |

| 1.5  | Internal power supply                                    | V <sub>VBAT</sub> > 7V                                                                                                                                                                                                                                               | VINT            | V <sub>VINT</sub>                                    | 4.7          | 5.0          | 5.3          | V    | А     |

| 1.6  | Overvoltage lock-out threshold                           |                                                                                                                                                                                                                                                                      | PBAT            | V <sub>THOVLO</sub>                                  | 20.0         |              | 23.0         | V    | А     |

| 1.7  | Overvoltage hysteresis                                   |                                                                                                                                                                                                                                                                      | PBAT            | V <sub>TOVhys</sub>                                  | 1.0          |              | 1.5          | V    | А     |

| 1.8  | Undervoltage lock-out threshold                          |                                                                                                                                                                                                                                                                      | PBAT            | V <sub>THUVRC</sub>                                  | 4.75         |              | 5.25         | V    | А     |

| 1.9  | Undervoltage threshold<br>hysteresis                     |                                                                                                                                                                                                                                                                      | PBAT            | V <sub>TUVhys</sub>                                  | 0.2          |              | 0.4          | V    | А     |

| 1.10 | R <sub>DSON</sub> VBAT-Switch switch                     | V <sub>VBAT</sub> = 13.5V,<br>I <sub>VBATSW</sub> = –15mA                                                                                                                                                                                                            | VBATSW          | R <sub>ON_VBATSW</sub>                               |              |              | 100          | Ω    | А     |

| 1.11 | Thermal prewarning set                                   |                                                                                                                                                                                                                                                                      |                 | T <sub>JPW set</sub>                                 | 120<br>(170) | 145<br>(195) | 170<br>(220) | °C   | В     |

| 1.12 | Thermal prewarning reset                                 |                                                                                                                                                                                                                                                                      |                 | T <sub>JPW reset</sub>                               | 105<br>(155) | 130<br>(180) | 155<br>(205) | °C   | В     |

| 1.13 | Thermal prewarning<br>hysteresis                         |                                                                                                                                                                                                                                                                      |                 | $\Delta T_{\text{JPW}}$                              |              | 15           |              | °C   | В     |

| 1.14 | Thermal shutdown off                                     |                                                                                                                                                                                                                                                                      |                 | T <sub>J switch off</sub>                            | 150<br>(200) | 175<br>(225) | 200<br>(250) | °C   | В     |

| 1.15 | Thermal shutdown on                                      |                                                                                                                                                                                                                                                                      |                 | T <sub>J switch on</sub>                             | 135<br>(185) | 160<br>(210) | 185<br>(235) | °C   | В     |

| 1.16 | Thermal shutdown<br>hysteresis                           |                                                                                                                                                                                                                                                                      |                 | $\Delta T_{\rm Jswitchoff}$                          |              | 15           |              | °C   | В     |

| 1.17 | Ratio thermal shutdown off/thermal prewarning set        |                                                                                                                                                                                                                                                                      |                 | T <sub>J switch off</sub> /<br>T <sub>JPW set</sub>  | 1.05         | 1.15         |              |      | В     |

| 1.18 | Ratio thermal shutdown<br>on/thermal prewarning<br>reset |                                                                                                                                                                                                                                                                      |                 | T <sub>J switch on</sub> /<br>T <sub>JPW reset</sub> | 1.05         | 1.15         |              |      | В     |

| 2    | 5V/3.3V Regulator                                        |                                                                                                                                                                                                                                                                      |                 |                                                      |              |              |              |      |       |

| 2.1  | Regulated output voltage                                 | $\label{eq:VMODE} \begin{split} V_{\text{MODE}} &= V_{\text{INT}},  7V < V_{\text{BAT}} < 40V \\ V_{\text{MODE}} &= \text{GND},  5.5V < V_{\text{BAT}} < 40V \\ I_{\text{Load}} &= 0 \text{ to } 100\text{mA} \end{split}$                                           | V <sub>CC</sub> | V <sub>VCC</sub>                                     | 4.85<br>3.20 |              | 5.15<br>3.40 | V    | A     |

| 2.2  | Regulated output voltage                                 | $\begin{split} V_{\text{MODE}} &= V_{\text{INT}},  7V < V_{\text{BAT}} < 40V \\ V_{\text{MODE}} &= \text{GND},  5.5V < V_{\text{BAT}} < 40V \\ I_{\text{Load}} &= 0 \text{ to } 80\text{mA} \\ 150^{\circ}\text{C} < T_{\text{J}} < 200^{\circ}\text{C} \end{split}$ | V <sub>CC</sub> | V <sub>VCC</sub>                                     | 4.85<br>3.20 |              | 5.15<br>3.40 | V    | A     |

| 2.3  | Regulated output voltage                                 | $\label{eq:VMODE} \begin{split} V_{\text{MODE}} &= V_{\text{INT}}, \ 5.5V < V_{\text{BAT}} < 7V \\ V_{\text{MODE}} &= \text{GND}, \ 5V < V_{\text{BAT}} < 5.5V \\ I_{\text{Load}} &= 0 \ \text{to} \ 60\text{mA} \end{split}$                                        | V <sub>CC</sub> | V <sub>VCC</sub>                                     | 4.50<br>2.97 |              | 5.15<br>3.40 | V    | A     |

All parameters given are valid for  $5.5V \le V_{VBAT} \le 18V$  and for  $-40^{\circ}C \le T_{J} \le 150^{\circ}C$  (200°C) unless stated otherwise. All values refer to PIN GND. (xxx) Values for the Atmel<sup>®</sup> ATA6834C.

| No.  | Parameters                                                     | Test Conditions                                                                                                                                                                                                                                                                 | Pin             | Symbol                 | Min.         | Тур.                      | Max.         | Unit | Type*  |

|------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|--------------|---------------------------|--------------|------|--------|

| 2.4  | Regulated output voltage                                       | $\begin{split} V_{\text{MODE}} &= V_{\text{INT}}, \ 5.5V < V_{\text{BAT}} < 7V \\ V_{\text{MODE}} &= \text{GND}, \ 5V < V_{\text{BAT}} < 5.5V \\ I_{\text{Load}} &= 0 \ \text{to} \ 50\text{mA} \\ 150^{\circ}\text{C} < \text{T}_{\text{J}} < 200^{\circ}\text{C} \end{split}$ | V <sub>cc</sub> | V <sub>VCC</sub>       | 4.50<br>2.97 |                           | 5.15<br>3.40 | V    | A      |

| 2.5  | Line regulation                                                | $ \begin{split} V_{\text{MODE}} &= V_{\text{INT}},  7V < V_{\text{BAT}} < 40V \\ V_{\text{MODE}} &= \text{GND},  5.5V < V_{\text{BAT}} < 40V \\ I_{\text{Load}} &= 50\text{mA},  -40^\circ\text{C} < \text{T}_{\text{J}} < 150^\circ\text{C} \end{split} $                      | V <sub>CC</sub> |                        |              |                           | 50<br>50     | mV   | A      |

| 2.6  | Load regulation                                                | $V_{MODE} = V_{INT}, V_{BAT} > 7V$ $V_{MODE} = GND, V_{BAT} > 5.5V$ $I_{Load} = 0 \text{ to } 100\text{mA}$ $I_{Load} = 0 \text{ to } 80\text{mA},$ $150^{\circ}\text{C} < T_{J} < 200^{\circ}\text{C}$                                                                         | V <sub>cc</sub> |                        |              |                           | 50<br>50     | mV   | A      |

| 2.7  | Output current limit                                           | $V_{MODE} = V_{INT}, V_{BAT} > 7V$<br>$V_{MODE} = GND, V_{BAT} > 5.5V$<br>$I_{Load}$ @ RESET                                                                                                                                                                                    | $V_{CC}$        | I <sub>OS1</sub>       | 100<br>100   |                           | 360<br>360   | mA   | A      |

| 2.8  | Output current limit                                           | $V_{MODE} = V_{INT}, V_{BAT} > 7V$ $V_{MODE} = GND, V_{BAT} > 5.5V$ $I_{Load} @ RESET,$ $150^{\circ}C < T_{J} < 200^{\circ}C$                                                                                                                                                   | VCC             | I <sub>OS1</sub>       | 70<br>70     |                           | 360<br>360   | mA   | С      |

| 2.12 | HIGH threshold VMODE                                           |                                                                                                                                                                                                                                                                                 |                 | $V_{VMODE H}$          |              |                           | 4.0          | V    | А      |

| 2.13 | LOW threshold VMODE                                            |                                                                                                                                                                                                                                                                                 |                 | V <sub>VMODE L</sub>   | 0.7          |                           |              | V    | А      |

| 3    | Reset and Watchdog                                             |                                                                                                                                                                                                                                                                                 |                 |                        |              |                           |              |      |        |

| 3.1  | $V_{\text{CC}}$ threshold voltage level for /RESET             | VMODE = VINT<br>(VMODE = GND)                                                                                                                                                                                                                                                   |                 | V <sub>tHRESHLow</sub> | 3.8<br>2.5   |                           | 4.2<br>2.8   | V    | A<br>B |

| 3.2  | Hysteresis                                                     | VMODE = VINT<br>(VMODE = GND)                                                                                                                                                                                                                                                   |                 | HYS <sub>RESth</sub>   | 0.2<br>0.13  |                           | 0.6<br>0.4   | V    | A<br>B |

| 3.3  | Length of pulse at /RESET                                      |                                                                                                                                                                                                                                                                                 |                 | t <sub>res</sub>       | 8            |                           | 12           | ms   | А      |

| 3.4  | Length of short pulse at<br>/RESET                             |                                                                                                                                                                                                                                                                                 |                 | t <sub>resshort</sub>  | 1.6          |                           | 2.4          | ms   | А      |

| 3.5  | Wait for the first WD trigger                                  |                                                                                                                                                                                                                                                                                 |                 | t <sub>d</sub>         | 400          |                           | 600          | ms   | А      |

| 3.6  | Time for VCC < V <sub>tHRESL</sub><br>before activating /RESET |                                                                                                                                                                                                                                                                                 |                 | t <sub>delayRESL</sub> |              |                           | 2            | μs   | С      |

| 3.8  | Watchdog oscillator period                                     | $R_{RWD}$ = 33k $\Omega$ ±1%                                                                                                                                                                                                                                                    |                 | T <sub>OSC</sub>       | 11.09        |                           | 13.55        | μs   | А      |

| 3.12 | Close window                                                   |                                                                                                                                                                                                                                                                                 |                 | t1                     |              | $980 \times T_{OSC}$      |              |      | А      |

| 3.13 | Open window                                                    |                                                                                                                                                                                                                                                                                 |                 | t2                     |              | 780 ×<br>T <sub>OSC</sub> |              |      | А      |

| 3.14 | Output low-level at pin<br>/RESET                              | I <sub>OLRES</sub> = 1mA                                                                                                                                                                                                                                                        |                 | V <sub>OLRES</sub>     |              |                           | 0.4          | V    | А      |

| 3.15 | Internal pull-up resistor at<br>pin /RESET                     |                                                                                                                                                                                                                                                                                 |                 | R <sub>PURES</sub>     | 5            | 10                        | 15           | kΩ   | D      |

All parameters given are valid for  $5.5V \le V_{VBAT} \le 18V$  and for  $-40^{\circ}C \le T_{J} \le 150^{\circ}C$  (200°C) unless stated otherwise. All values refer to PIN GND. (xxx) Values for the Atmel<sup>®</sup> ATA6834C.

|      | Parameters                                                                                                                                                        | Test Conditions                                                                   | Pin | Symbol                   | Min.                                                    | Тур.                        | Max.                                                    | Unit | Туре |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|--------------------------|---------------------------------------------------------|-----------------------------|---------------------------------------------------------|------|------|

| 4    | LIN Transceiver                                                                                                                                                   |                                                                                   |     |                          |                                                         |                             |                                                         |      |      |

| 4.1  | Low-level output current                                                                                                                                          | Normal mode;<br>V <sub>LIN</sub> = 0V, V <sub>RXD</sub> = 0.4V                    |     | IL <sub>RXD</sub>        | 2                                                       |                             |                                                         | mA   | D    |

| 4.2  | High-level output current                                                                                                                                         | Normal mode; $V_{LIN} = V_{BAT}$<br>$V_{RXD} = V_{CC} - 0.4V$                     |     | IH <sub>RXD</sub>        |                                                         |                             | -2                                                      | mA   | D    |

| 4.3  | Driver recessive output voltage                                                                                                                                   | $V_{TXD} = V_{CC}; I_{LIN} = 0mA$                                                 |     | V <sub>BUSrec</sub>      | $0.9 \times $ VBAT                                      |                             |                                                         | V    | А    |

| 4.4  | Driver dominant voltage<br>V <sub>BUSdom_DRV_LoSUP</sub>                                                                                                          | $V_{VBAT} = 7.3V$<br>$R_{load} = 500\Omega$                                       |     | V_LoSUP                  |                                                         |                             | 1.2                                                     | V    | А    |

| 4.5  | Driver dominant voltage<br>V <sub>BUSdom_DRV_HiSUP</sub>                                                                                                          | $V_{VBAT}$ = 18V<br>$R_{load}$ = 500 $\Omega$                                     |     | $V_{HiSUP}$              |                                                         |                             | 2                                                       | V    | А    |

| 4.6  | Driver dominant voltage<br>V <sub>BUSdom_DRV_LoSUP</sub>                                                                                                          | $V_{VBAT}$ = 7.3V<br>R <sub>load</sub> = 1000\Omega                               |     | V_LoSUP_1k               | 0.6                                                     |                             |                                                         | V    | А    |

| 4.7  | Driver dominant voltage<br>V <sub>BUSdom_DRV_HiSUP</sub>                                                                                                          | $V_{VBAT}$ = 18V<br>R <sub>load</sub> = 1000 $\Omega$                             |     | $V_{HiSUP_{1k_{}}}$      | 0.8                                                     |                             |                                                         | V    | А    |