### **SPECIFICATIONS**

$V_{DD} = 7.5 \text{ V to } 30 \text{ V}, V_{SS} = 0 \text{ V}, D_{VCC} = A_{VCC} = V_{REG}, V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}, \quad T_A = -40 ^{\circ}\text{C} \text{ to } 105 ^{\circ}\text{C}, \text{ unless otherwise noted } 105 ^{\circ}\text{C}, \text{ and } 105 ^{\circ}\text{C}, \text$

Table 1.

| Parameter <sup>1</sup>                                           | Min                                | Тур                                           | Max                              | Unit   | Test Conditions/Comments     |

|------------------------------------------------------------------|------------------------------------|-----------------------------------------------|----------------------------------|--------|------------------------------|

| DC ACCURACY [Vin(0) to Vin(6)] <sup>2</sup>                      |                                    |                                               |                                  |        |                              |

| Resolution                                                       | 12                                 |                                               |                                  | Bits   | No Missing Codes             |

| Integral Nonlinearity                                            |                                    |                                               | ±1                               | LSB    |                              |

| Differential Nonlinearity                                        |                                    |                                               | ±1                               | LSB    |                              |

| Offset Error                                                     |                                    | 1                                             |                                  | LSB    |                              |

| Offset Error Drift                                               |                                    | 3                                             |                                  | ppm/°C |                              |

| Offset Error Match                                               |                                    | 1                                             |                                  | LSB    |                              |

| Gain Error                                                       |                                    | 1                                             |                                  | LSB    |                              |

| Gain Error Drift                                                 |                                    | 2                                             |                                  | ppm/°C |                              |

| Gain Error Match                                                 |                                    | 1                                             |                                  | LSB    |                              |

| ADC Unadjusted Error <sup>3,4</sup>                              |                                    | 0.05                                          | 0.1                              | %      | -40°C to 85°C                |

|                                                                  |                                    | 0.08                                          | 0.3                              | %      | -40°C to 105°C               |

| Total Unadjusted Error <sup>5,6</sup>                            |                                    | 0.07                                          | 0.2                              | %      | -40°C to 85°C                |

| Total ondajasted Error                                           |                                    | 0.1                                           | 0.5                              | %      | -40°C to 105°C               |

| ANALOG INPUTS [Vin(0) to<br>Vin(6)]<br>Pseudo Differential Input |                                    |                                               |                                  | ,,     |                              |

| Voltage                                                          |                                    |                                               |                                  |        |                              |

| Vin(n) – Vin(n-1)                                                | 1V                                 |                                               | $2V_{REF}$                       | V      |                              |

| Absolute Input Voltage                                           | V <sub>CM</sub> - V <sub>REF</sub> |                                               | $V_{\text{CM}} + V_{\text{REF}}$ | V      |                              |

| Common Mode Input Voltage                                        | 0.5                                |                                               | 27.5                             | V      |                              |

| DC Leakage Current                                               |                                    | ±70                                           |                                  | nA     | CNVST pulse every 100ms      |

| Input Capacitance                                                |                                    | 15                                            |                                  | pF     | When in track                |

|                                                                  |                                    | 3                                             |                                  | pF     | When in hold                 |

| DC ACCURACY [VT1 to VT6] <sup>2</sup>                            |                                    |                                               |                                  |        |                              |

| Resolution                                                       | 12                                 |                                               |                                  | Bits   | No Missing Codes             |

| Integral Nonlinearity                                            |                                    |                                               | ±1                               | LSB    |                              |

| Differential Nonlinearity                                        |                                    |                                               | ±1                               | LSB    |                              |

| Offset Error                                                     |                                    | 2                                             |                                  | LSB    |                              |

| Offset Error Drift                                               |                                    | 2                                             |                                  | ppm/°C |                              |

| Offset Error Match                                               |                                    | 2                                             |                                  | LSB    |                              |

| Gain Error                                                       |                                    | 2                                             |                                  | LSB    |                              |

| Gain Error Drift                                                 |                                    | 1.2                                           |                                  | ppm/°C |                              |

| Gain Error Match                                                 |                                    | 2                                             |                                  | LSB    |                              |

| ADC Unadjusted Error <sup>7</sup>                                |                                    | 0.1                                           | 0.2                              | %      | -40°C to 85°C                |

| ,                                                                |                                    | 0.16                                          | 0.6                              | %      | -40°C to 105°C               |

| Total Unadjusted Error <sup>8</sup>                              |                                    | 0.15                                          | 0.4                              | %      | -40°C to 85°C                |

|                                                                  |                                    | 0.2                                           | 1                                | %      | -40°C to 105°C               |

| ANALOG INPUTS (VT1 to VT6)                                       |                                    | <u> </u>                                      |                                  |        |                              |

| Input Voltage Range                                              | 0                                  |                                               | $2V_{REF}$                       | V      |                              |

| Leakage Current                                                  |                                    | ±70                                           |                                  | nA     | CNVST pulse every 100ms      |

| Input Capacitance                                                |                                    | 15                                            |                                  | pF     | When in track                |

| input cupacitatice                                               |                                    | 3                                             |                                  | pF     | When in hold                 |

| DYNAMIC PERFORMANCE                                              |                                    | <u>,                                     </u> |                                  | Ρι     | When it floid                |

| Common Mode Rejection Ratio [CMRR]                               |                                    | -75                                           |                                  | dB     | Up to 10kHz ripple frequency |

| Parameter <sup>1</sup>                      | Min                                             | Тур        | Max              | Unit              | Test Conditions/Comments                           |

|---------------------------------------------|-------------------------------------------------|------------|------------------|-------------------|----------------------------------------------------|

| REFERENCE                                   |                                                 |            |                  |                   |                                                    |

| Reference Voltage                           | 2.495                                           | 2.5        | 2.505            | V                 | V <sub>REF</sub> @ 25°C                            |

| Reference Temperature<br>Coefficient        |                                                 | ±3         | ±15              | ppm/°C            | -40 °C to +85 °C                                   |

| Output Voltage Hysteresis                   | tput Voltage Hysteresis 50 ppm -40 °C to +85 °C |            | -40 °C to +85 °C |                   |                                                    |

| Long Term Drift                             |                                                 | 100        |                  | ppm/1000<br>Hours |                                                    |

| Line Regulation                             |                                                 | ±15        |                  | ppm/V             | AVDD =7.5V                                         |

| Turn-On Settling Time                       |                                                 | 10         |                  | ms                | V <sub>REF</sub> = 10uF , C <sub>REF</sub> = 100nF |

| REGULATOR OUTPUT                            |                                                 |            |                  |                   |                                                    |

| Input Voltage Range                         | 7.5                                             |            | 30               | V                 |                                                    |

| Output Voltage V <sub>REG</sub>             | 4.75                                            | 5          | 5.25             | V                 |                                                    |

| Output Current <sup>9</sup>                 | 5                                               |            |                  | mA                |                                                    |

| Line Regulation                             |                                                 | 0.4        |                  | mV/V              |                                                    |

| Load Regulation                             |                                                 | 2.5        |                  | mV/mA             |                                                    |

| Output Noise Voltage                        |                                                 | 700        |                  | uV                |                                                    |

| Internal Short Protection Limit             |                                                 | 20         |                  | mA                | For a 10 Ohm short                                 |

| CELL BALANCING OUTPUTS <sup>10</sup>        |                                                 |            |                  |                   |                                                    |

| Output High Voltage, V <sub>OH</sub>        | 4                                               | 5          | 5.25             | V                 | For a 80pF load, I <sub>SOURCE</sub> = 40 nA       |

| Output Low Voltage, Vol                     | 0                                               |            |                  | V                 | Service 12 min                                     |

| CB1 Output ramp up time <sup>11</sup>       |                                                 | 5          |                  | us                | For a 80pF load                                    |

| CB1 Output ramp down time <sup>12</sup>     |                                                 | 50         |                  | ns                | For a 80pF load                                    |

| CB2-CB6 Output ramp up time <sup>11</sup>   |                                                 | 350        |                  | us                | For a 80pF load                                    |

| CB2-CB6 Output ramp down time <sup>12</sup> |                                                 | 10         |                  | us                | For a 80pF load                                    |

| LOGIC INPUTS                                |                                                 |            |                  |                   |                                                    |

| Input High Voltage, V <sub>INH</sub>        | 2.4                                             |            |                  | V                 |                                                    |

| Input Low Voltage, V <sub>INL</sub>         |                                                 |            | 0.4              | V                 |                                                    |

| Input Current, I <sub>IN</sub>              |                                                 |            | ±1               | μΑ                |                                                    |

| Input Capacitance, C <sub>IN</sub>          |                                                 | 10         |                  | pF                |                                                    |

| LOGIC OUTPUTS                               |                                                 |            |                  |                   |                                                    |

| Output High Voltage, V <sub>OH</sub>        | V <sub>DRIVE</sub> * 0.9                        |            |                  | V                 | $I_{SOURCE} = 200 \mu\text{A}$                     |

| Output Low Voltage, Vol                     |                                                 |            | 0.4              | V                 | I <sub>SINK</sub> = 200 μA                         |

| Floating-State Leakage                      |                                                 |            | ±1               | μA                |                                                    |

| Current                                     |                                                 |            |                  | •                 |                                                    |

| Floating-State Output<br>Capacitance        |                                                 | 5          |                  | pF                |                                                    |

| Output Coding                               | Strai                                           | ght natura | al binary        |                   |                                                    |

| POWER REQUIREMENTS                          |                                                 |            |                  |                   |                                                    |

| $V_{DD}$                                    | 7.5                                             |            | 30               | V                 |                                                    |

| I <sub>DD</sub> During Conversion           |                                                 | 7          | 10               | mA                | V <sub>DD</sub> = 30 V                             |

| IDD During Data Readback                    |                                                 | 5          | 8                | mA                | V <sub>DD</sub> = 30 V                             |

| IDD During Cell Balancing                   |                                                 | 4.5        | 6                | mA                | V <sub>DD</sub> = 30 V                             |

| I <sub>DD</sub> Software Powerdown          |                                                 | 1.8        | 2.5              | mA                | $V_{DD} = 30 \text{ V}$                            |

| I <sub>DD</sub> Full Powerdown Mode         |                                                 |            | 4                | μΑ                | V <sub>DD</sub> = 30 V                             |

| POWER DISSIPATION                           |                                                 |            |                  | -                 |                                                    |

| During Conversion                           |                                                 |            | 300              | mW                | $V_{DD} = 30 \text{ V}$                            |

| During Data Readback                        |                                                 |            | 240              | mW                | V <sub>DD</sub> = 30 V                             |

| During Cell Balancing                       |                                                 |            | 180              | mW                | V <sub>DD</sub> = 30 V                             |

| Software Powerdown                          |                                                 |            | 75               | mW                | V <sub>DD</sub> = 30 V                             |

| Full Powerdown Mode                         |                                                 |            | 120              | μW                | $V_{DD} = 30 \text{ V}$                            |

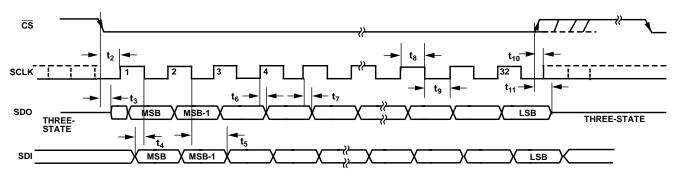

#### **TIMING SPECIFICATIONS**

$V_{DD} = 7.5 \ V \ to \ 30 \ V, \ V_{SS} = 0 \ V, \ D_{VCC} = A_{VCC} = V_{REG}, \ V_{DRIVE} = 2.7 \ V \ to \ 5.25 \ V, \ T_A = -40^{\circ}C \ to \ 105^{\circ}C, \ unless \ otherwise \ noted.^{1}$

Table 2.

|                             | Limit at                            | T <sub>MIN</sub> , T <sub>MAX</sub>  |         |                                                                                                |

|-----------------------------|-------------------------------------|--------------------------------------|---------|------------------------------------------------------------------------------------------------|

| Parameter                   | 2.7 V ≤ V <sub>DRIVE</sub> < 4.75 V | 4.75 V ≤ V <sub>DRIVE</sub> ≤ 5.25 V | Unit    | Test Conditions/Comments                                                                       |

| t <sub>CONV</sub>           | 610                                 | 610                                  | ns max  | ADC Conversion time                                                                            |

| t <sub>DELAY</sub>          | 200                                 | 200                                  | ns typ  | Propogation delay between adjacent parts on the Daisy                                          |

|                             | 250                                 | 250                                  | ns max  | Chain                                                                                          |

| twait                       | 5                                   | 5                                    | μs min  | Time required between the end of conversions and beginning to read back the conversion results |

| $f_{SCLK}$                  | 10                                  | 10                                   | kHz min | Frequency of serial read clock                                                                 |

|                             | 1                                   | 1                                    | MHz max |                                                                                                |

| t <sub>QUIET</sub>          | 200                                 | 200                                  | ns min  | Minimum quiet time required between the end of serial                                          |

|                             |                                     |                                      |         | read and the start of the next conversion                                                      |

| t <sub>1</sub>              | 400                                 | 400                                  | ns min  | Minimum CONVST low pulse                                                                       |

| $t_2$                       | 10                                  | 10                                   | ns min  | CS falling edge to SCLK rising edge                                                            |

| t <sub>3</sub>              | 10                                  | 10                                   | ns max  | Delay from CS falling edge until SDO is three-state disabled                                   |

| t <sub>4</sub>              | 5                                   | 5                                    | ns min  | SDI setup time prior to SCLK falling edge                                                      |

| <b>t</b> <sub>5</sub>       | 3                                   | 3                                    | ns min  | SDI hold time after SCLK falling edge                                                          |

| t <sub>6</sub> <sup>2</sup> | 20                                  | 14                                   | ns max  | Data access time after SCLK falling edge                                                       |

| <b>t</b> <sub>7</sub>       | 7                                   | 7                                    | ns min  | SCLK to data valid hold time                                                                   |

| t <sub>8</sub>              | $0.3 \times t_{SCLK}$               | $0.3 \times t_{SCLK}$                | ns min  | SCLK high pulse width                                                                          |

| <b>t</b> 9                  | $0.3 \times t_{SCLK}$               | 0.3 × t <sub>SCLK</sub>              | ns min  | SCLK low pulse width                                                                           |

| $t_{10}^{3}$                | 10                                  | 10                                   | ns min  | CS rising edge to SCLK rising edge                                                             |

| t <sub>11</sub>             | 10                                  | 10                                   | ns max  | CS rising edge to SDO high impedance                                                           |

Rev. PrF | Page 4 of 38

<sup>&</sup>lt;sup>1</sup> Temperature range is -40°C to +105°C.

<sup>&</sup>lt;sup>2</sup> For dc accuracy specifications, the LSB size for cell voltage measurements is (2V<sub>REF</sub>-1V)/4096, the LSB size for temperature measurements is 2V<sub>REF</sub>/4096.

<sup>&</sup>lt;sup>3</sup> ADC Unadjusted Error includes the INL of the ADC and the Gain and Offset Errors of the Vin0 to Vin6 input channels.

<sup>&</sup>lt;sup>4</sup> The conversion accuracy during Cell Balancing is decreased due to the activation of the Cell Balance circuitry. The ADC Unadjusted Error will increase from 0.1% to 0.4% within the -40°C to 85°C temperature range.

<sup>&</sup>lt;sup>5</sup> Total Unadjusted Error includes the INL of the ADC and the Gain and Offset Errors of the Vin0 to Vin6 input channels as well as the temperature coefficient of the 2.5V reference.

<sup>&</sup>lt;sup>6</sup> The conversion accuracy during Cell Balancing is decreased due to the activation of the Cell Balance circuitry. The Total Unadjusted Error will increase from 0.2% to 0.8% within the -40°C to 85°C temperature range.

<sup>&</sup>lt;sup>7</sup> ADC Unadjusted Error includes the INL of the ADC and the Gain and Offset Errors of the VT input channels.

<sup>8</sup> Total Unadjusted Error includes the INL of the ADC and the Gain and Offset Errors of the VT input channels as well as the temperature coefficient of the 2.5V reference.

<sup>&</sup>lt;sup>9</sup> This spec outlines the regulator output current which is available for external use, that is, it does not include the regulator current already being used by the AD7280.

<sup>&</sup>lt;sup>10</sup> CB output can be set to 0V or 5V with respect to negative terminal of cell being balanced.

<sup>11</sup> The CB1 to CB6 output ramp up times are defined from the rising edge of the CS command until the CB output exceeds 4V with respect to negative terminal of cell being balanced.

<sup>&</sup>lt;sup>12</sup> The CB1 to CB6 output ramp down times are defined from the rising edge of the CS command until the CB output falls below 50mV with respect to negative terminal of cell being balanced.

<sup>&</sup>lt;sup>1</sup> Sample tested during initial release to ensure compliance. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of  $V_{DRIVE}$ ) and timed from a voltage level of 1.6 V. All timing specifications given are with a 25 pF load capacitance.

<sup>&</sup>lt;sup>2</sup> The time required for the output to cross 0.4 V or 2.4 V.

<sup>&</sup>lt;sup>3</sup> t<sub>10</sub> applies when using a continuous SCLK.

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted

Table 3

| Table 3.                             |                                                      |

|--------------------------------------|------------------------------------------------------|

| Parameter                            | Rating                                               |

| V <sub>DD</sub> to AGND              | -0.3 V to +33 V                                      |

| V <sub>ss</sub> to AGND              | −0.3 V to +0.3 V                                     |

| Vin0 to Vin5 Voltage to AGND         | $V_{SS} - 0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ |

| Vin6 Voltage to AGND                 | $V_{DD}$ $-0.3$ V to $V_{DD}$ + 1 V                  |

| CB1 Output to AGND                   | $-0.3 \text{ V to DV}_{CC} + 0.3 \text{ V}$          |

| CB2 to CB6 Output to AGND            | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$           |

| VT1 to VT6 Voltage to AGND           | $-0.3 \text{ V to AV}_{CC} + 0.3 \text{ V}$          |

| AV <sub>cc</sub> to AGND, DGND       | −0.3 V to +7 V                                       |

| DV <sub>cc</sub> to AV <sub>cc</sub> | −0.3 V to +0.3 V                                     |

| DV <sub>cc</sub> to DGND             | −0.3 V to +7 V                                       |

| V <sub>DRIVE</sub> to AGND           | -0.3 V to DV <sub>CC</sub> +0.3 V                    |

| AGND to DGND                         | –0.3 V to +0.3 V                                     |

| Digital Input Voltage to DGND        | $-0.3 \text{ V to } V_{DRIVE} + 0.3 \text{ V}$       |

| Digital Output Voltage to GND        | $-0.3 \text{ V to } V_{DRIVE} + 0.3 \text{ V}$       |

| Operating Temperature Range          | -40°C to +105°C                                      |

| Storage Temperature Range            | −65°C to +150°C                                      |

| Junction Temperature                 | 150°C                                                |

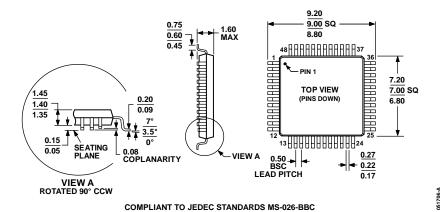

| LQFP Package                         |                                                      |

| $\theta_{JA}$ Thermal Impedance      | 76.2°C/W                                             |

| $\theta_{JC}$ Thermal Impedance      | 17°C/W                                               |

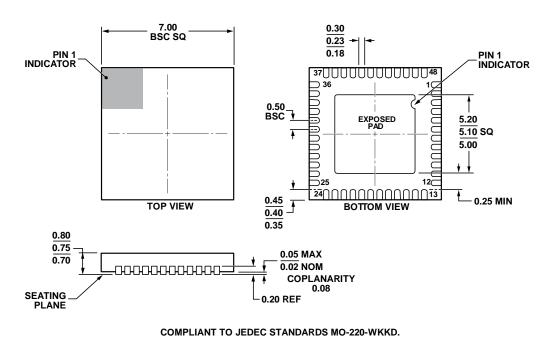

| LFCSP Package                        |                                                      |

| $\theta_{JA}$ Thermal Impedance      | 54°C/W                                               |

| $\theta_{JC}$ Thermal Impedance      | 15°C/W                                               |

| Pb-free Temperature, Soldering       |                                                      |

| Reflow                               | 260(+0)°C                                            |

| ESD                                  | 2kV                                                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

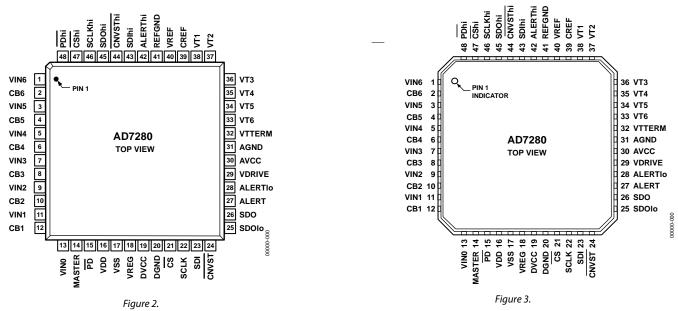

### PIN CONFIGURATIONS AND FUNCTIONAL DESCRIPTIONS

Table 4.

| Pin No.                  | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7,<br>9, 11, 13 | Vin6 to<br>Vin0  | Analog Input 0 to Analog Input 6. Analog input 0 should be connected to the base of the series connected battery cells. Analog Input 1 should be connected to the top of cell 1, Analog Input 2 should be connected to the top of cell 2, etc. The Analog Inputs are multiplexed into the on-chip track-and-hold allowing the potential across each cell to be measured.                                                                                                                                                                      |

| 2, 4, 6, 8,<br>10, 12    | CB6 to CB1       | Cell Balance Outputs. These provide a voltage output which can be used to supply the gate drives of a cell balancing transistor network. Each CB(n) output provides a 5V voltage output referenced to the absolute voltage of Cell(n-1).                                                                                                                                                                                                                                                                                                      |

| 14                       | MASTER           | Voltage Input. In an application with 2 or more AD7280s Daisy Chained the MASTER pin of the AD7280 connected directly to the DSP or uP should be connected to the $V_{DD}$ supply pin through a 10kOhm resistor. The MASTER pin on the remaining AD7280s in the application should be tied to their respective $V_{SS}$ supply pins through 10kOhm resistors.                                                                                                                                                                                 |

| 15                       | PD               | Power down Input. This input is used to power down the AD7280. When acting as master the PD input is supplied from the DSP/uP. When acting as a slave on the Daisy Chain the PD input should be connected to the PDhi output of the AD7280 immediately below it in potential in the Daisy Chain.                                                                                                                                                                                                                                              |

| 16                       | V <sub>DD</sub>  | Positive Power Supply Voltage. This is the positive supply voltage for the high voltage analog input structure AD7280. The supply must be greater than a minimum voltage of 7.5 V. In an application monitoring the cell voltages of up to 6 series connected battery cells the supply voltage may be supplied directly from the cell with the highest potential. The maximum voltage which can be applied between $V_{DD}$ and $V_{SS}$ is 30V. Place 10 $\mu$ F and 100 nF decoupling capacitors on the $V_{DD}$ pin.                       |

| 17                       | V <sub>SS</sub>  | Negative Power Supply Voltage. This is the negative supply voltage for the high voltage analog input structure of the AD7280. This input should be at the same potential as the AGND voltage.                                                                                                                                                                                                                                                                                                                                                 |

| 18                       | V <sub>REG</sub> | Analog Voltage output, 5V. The internally generated $V_{REG}$ voltage, which provides the supply voltage for the ADC core, is available on this pin for use external to the AD7280. Place 10 $\mu$ F and 100 nF decoupling capacitors on the $V_{REG}$ pin.                                                                                                                                                                                                                                                                                   |

| 19                       | DVcc             | Digital Supply Voltage, 4.75 V to 5.25 V. The DV <sub>CC</sub> and AV <sub>CC</sub> voltages should ideally be at the same potential. For best performance, it is recommended that the DV <sub>CC</sub> and AV <sub>CC</sub> pins be shorted together, to ensure that the voltage difference between them never exceeds 0.3 V even on a transient basis. This supply should be decoupled to DGND. Place 100 nF decoupling capacitors on the DV <sub>CC</sub> pin. The DV <sub>CC</sub> supply pin should be connected to the $V_{REG}$ output |

| 20                       | DGND             | Digital Ground. Ground reference point for all digital circuitry on the AD7280. The DGND and AGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                                                                                                          |

| 21       | CS                 | Chip select Input. When acting as a master, that is the Master pin of the AD7280 is connected to $V_{DD}$ , the $\overline{CS}$ input is used to frame the input and output data on the SPI. The $\overline{CS}$ input also frames the input and output data                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22       | SCLK               | on the Daisy Chain Interface when the MASTER input of the AD7280 is connected to Vss.  Serial Clock Input. When acting as master the SCLK input is supplied from the DSP/uP. When acting as a slave on the Daisy Chain this input should be connected to the SCLKhi output of the AD7280 immediately below it in potential in the Daisy Chain.                                                                                                                                                                                                                                                                                                                                                                       |

| 23       | SDI                | Serial Data Input. Data to be written to the on-chip registers is provided on this input and is clocked into the AD7280 on the falling edge of SCLK. When acting as master this is the data input of the SPI interface. When acting as a slave on the Daisy Chain this input acepts data from the SDOhi output of the AD7280 immediately below it in potential in the Daisy Chain.                                                                                                                                                                                                                                                                                                                                   |

| 24       | CNVST              | Convert Start Input. The conversion is initiated on the falling edge of CONVST. When acting as master the CNVST pulse is supplied from the DSP/uP. When acting as a slave on the Daisy Chain this input should be connected to the CNVSThi output of the AD7280 immediately below it in potential in the Daisy Chain. This                                                                                                                                                                                                                                                                                                                                                                                           |

| 25       | SDOlo              | input can also be tied to V <sub>CC</sub> and the conversion initiated through the serial interface.  Serial Data Output in Daisy Chain mode. When configured as a slave device this output should be connected to the SDIhi input of the AD7280 immediately below it in potential on the Daisy Chain. The data from each AD7280 in the Daisy Chain will be passed through the SDOIo outputs and SDIhi inputs of each AD7280 in the chain and supplied to the uP/DSP through the SDO output of the master AD7280. When configured as a master device it is recommended that this output, which is not required in slave mode, be connected to V <sub>SS</sub> either directly or through a pull-down 1kOhm resistor. |

| 26       | SDO                | Serial Data Output. The conversion output data or the register output data is supplied to this pin as a serial data stream. The bits are clocked out on the rising edge of the SCLK input, and 32 SCLKs are required to access the data. The data is provided MSB first. In a Daisy Chain application the SDO output of the master AD7280 should be connected to the uP/DSP. The SDO outputs of the remaining AD7280s in the chain should be terminated to                                                                                                                                                                                                                                                           |

|          |                    | $V_{SS}$ through a 1k $\Omega$ resistor. The data from each AD7280 in the Daisy Chain will be passed through the SDOlo outputs and SDIhi inputs of each AD7280 in the chain and supplied to the uP/DSP through the SDO output of the master AD7280. 32 SCLKs are required for each AD7280 in the chain to access the data.                                                                                                                                                                                                                                                                                                                                                                                           |

| 27       | ALERT              | Digital Output. Flag to indicate over voltage, under voltage, over temperature or under temperature. The ALERT output of the master AD7280 should be connected to the uP/DSP. The ALERT outputs of the remaining AD7280s in the chain should be be terminated to $V_{SS}$ through a $1k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 28       | ALERTIO            | Alert Output in Daisy Chain mode. The alert signal from each AD7280 in the Daisy Chain will be passed through the ALERTlo outputs and ALERThi inputs of each AD7280 in the chain and supplied to the uP/DSP through the ALERT output of the master AD7280. When configured as a slave device this output should be connected to the ALERThi input of the AD7280 immediately below it in potential on the Daisy Chain. When configured as a master device it is recommended that this output, which is not required in slave mode, be connected to Vss either directly or through a pull-down 1kOhm resistor.                                                                                                         |

| 29       | V <sub>DRIVE</sub> | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. This pin should be decoupled to DGND. The voltage range on this pin is 2.7 V to 5.25 V and may be different to the voltage at $AV_{CC}$ and $DV_{CC}$ , but should never exceed either by more than 0.3 V.                                                                                                                                                                                                                                                                                                                                                                                             |

| 30       | AV <sub>CC</sub>   | Analog Supply Voltage, 4.75 V to 5.25 V. This is the supply voltage for the ADC core. The $AV_{CC}$ and $DV_{CC}$ voltages should ideally be at the same potential. For best performance, it is recommended that the $DV_{CC}$ and $AV_{CC}$ pins be shorted together, to ensure that the voltage difference between them never exceeds 0.3 V even on a transient basis. This supply should be decoupled to AGND. Place 100 nF decoupling capacitors on the $AV_{CC}$ pin. The $AV_{CC}$ supply pin should be externally connected to the $V_{REG}$ output.                                                                                                                                                          |

| 31       | AGND               | Analog Ground. Ground reference point for all analog circuitry on the AD7280. This input should be at the same potential as the base of the series connected battery cells. The AGND and DGND voltages ideally should be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                                                                                                                                                                                     |

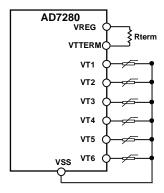

| 32       | VT <sub>TERM</sub> | Thermistor termination resistor input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 33 to 38 | VT6 to VT1         | Voltage temperature input from potential divider with thermistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 39       | C <sub>REF</sub>   | A 100 nF decoupling capacitor to REFGND should be placed on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 40       | V <sub>REF</sub>   | Reference Output. The on-chip reference is available on this pin for use external to the AD7280. The nominal internal reference voltage is 2.5V, which appears at the pin. A 10 $\mu$ F decoupling capacitor to REFGND is recommended on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 41       | REFGND             | Reference Ground. This is the ground reference point for the internal bandgap reference circuitry on the AD7280. The REFGND voltage should be at the same potential as the AGND voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 42       | ALERThi            | Alert Input in Daisy Chain mode. Flag to indicate over voltage, under voltage, over temperature or under temperature in Daisy Chain mode. The alert signal from each AD7280 in the Daisy Chain will be passed through the ALERTlo outputs and ALERThi inputs of each AD7280 in the chain and supplied to the uP/DSP through the ALERT output of the master AD7280. This input should be connected to the ALERTlo output of the AD7280 immediately above it in potential on the Daisy Chain. When this pin is unused, it is recommended that it is connected to VDD through a 1kOhm resistor.                                                                                                                         |

# **Preliminary Technical Data**

| 43 | SDIhi   | Serial Data Input in Daisy Chain mode. The data from each AD7280 in the Daisy Chain will be passed through                                                                                                             |

|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |         | the SDOlo outputs and SDIhi inputs of each AD7280 in the chain and supplied to the uP/DSP through the SDO output of the master AD7280. This input should be connected to the SDOlo output of the AD7280 immediately    |

|    |         | above it in potential on the Daisy Chain. When this pin is unused, it is recommended that it is connected to V <sub>DD</sub> through a 1kOhm resistor.                                                                 |

| 44 | CNVSThi | Conversion Start Output in Daisy Chain mode. The convert start signal from the uP/DSP supplied to the CNVST                                                                                                            |

|    |         | input of the Master AD7280 is passed through each AD7280 by means of the CNVST input and the CNVSThi output. This output should be connected to the CNVST pin of the AD7280 immediately above it in potential on       |

|    |         | the Daisy Chain. When this pin is unused, it is recommended that it is connected to V <sub>DD</sub> .                                                                                                                  |

| 45 | SDOhi   | Serial Data Output in Daisy Chain mode. The Serial Data input from the uP/DSP supplied to the SDI input of the Master AD7280 is passed through each AD7280 by means of the SDI input and the SDOhi output. This output |

|    |         | should be connected to the SDI input of the AD7280 immediately above it in potential on the Daisy Chain.                                                                                                               |

|    |         | When this pin is unused, it is recommended that it is connected to VDD.                                                                                                                                                |

| 46 | SCLKhi  | Serial Clock Output in Daisy Chain mode. The clock signal from the uP/DSP supplied to the SCLK input of the Master AD7280 is passed through each AD7280 by means of the SCLK input and the SCLKhi output. This output  |

|    |         | should be connected to the SCLK input of the AD7280 immediately above it in potential in the Daisy Chain.                                                                                                              |

|    |         | When this pin is unused, it is recommended that it is connected to VDD.                                                                                                                                                |

| 47 | CShi    | Chip select Output in Daisy Chain mode. The chip select signal from the uP/DSP supplied to the CS input of the                                                                                                         |

|    |         | Master AD7280 is passed through each AD7280 by means of the CS input and the CShi output. This output                                                                                                                  |

|    |         | should be connected to the $\overline{\text{CS}}$ input of the AD7280 immediately above it in potential on the Daisy Chain. When this pin is unused, it is recommended that it is connected to $V_{DD}$ .              |

| 48 | PDhi    | Power down Output in Daisy Chain mode. The power down signal from the uP/DSP supplied to the PD input of                                                                                                               |

| 40 | FUIII   | the Master AD7280 is passed through each AD7280 by means of the PD input and the PDhi output. This output                                                                                                              |

|    |         | should be connected to the PD pin of the AD7280 immediately above it in potential on the Daisy Chain. When                                                                                                             |

|    |         | this pin is unused, it is recommended that it is connected to V <sub>DD</sub> .                                                                                                                                        |

|    |         |                                                                                                                                                                                                                        |

### **TERMINOLOGY**

#### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Integral Nonlinearity**

This is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale (a point 1 LSB below the first code transition) and full scale (a point 1 LSB above the last code transition).

#### Offset Code Error

This applies to straight binary output coding. It is the deviation of the first code transition (00  $\dots$  000) to (00  $\dots$  001) from the ideal, that is, AGND +1 LSB for VT1 to VT6 and 1V + AGND +1 LSB for Vin0 to Vin6.

#### **Gain Error**

This applies to straight binary output coding. It is the deviation of the last code transition (111 ... 110) to (111 ... 111) from the ideal (that is  $2 \times V_{REF} - 1$  LSB) after adjusting for the offset error.

#### **ADC Unadjusted Error**

ADC Unadjusted Error includes integral nonlinearity errors, offset and gain errors of the ADC and measurement channel.

#### **Total Unadjusted Error (TUE)**

This is the maximum deviation of the output code from the ideal. Total Unadjusted Error includes integral nonlinearity errors, offset and gain errors and reference drift.

#### Offset Error Match

This is the difference in zero code error across all 6 channels.

#### **Gain Error Match**

The difference in gain error across all 6 channels.

#### **Track-and-Hold Acquisition Time**

The track-and-hold amplifier returns to track mode at the end of a conversion. Track-and-hold acquisition time is the time required for the output of the track-and-hold amplifier to reach its final value, within  $\pm \frac{1}{2}$  LSB.

#### **Common Mode Rejection Ration (CMRR)**

CMRR is defined as the ratio of the power in the ADC output at full-scale frequency, f, to the power of a 100 mV sine wave applied to the common-mode voltage of the Vin(n) and

Vin(n-1) frequency, fs, as

$$CMRR$$

(dB) =  $10 \log (Pf/Pf_S)$

where Pf is the power at frequency f in the ADC output, and  $Pf_S$  is the power at frequency  $f_S$  in the ADC output.

#### Power Supply Rejection Ration (PSRR)

Variations in power supply affect the full-scale transition but not the converter's linearity. PSRR is the maximum change in the full-scale transition point due to a change in power supply voltage from the nominal value.

#### Reference Voltage Temperature Coefficient

Reference voltage temperature coefficient is derived from the maximum and minimum reference output voltage ( $V_{REF}$ ) measured at  $T_{MIN}$ , T(25°C), and  $T_{MAX}$ . It is expressed in ppm/°C using the following equation:

$$TCV_{REF}(ppm/^{\circ}C) = \frac{V_{REF}(Max) - V_{REF}(Min)}{V_{REF}(25^{\circ}C) \times (T_{MAX} - T_{MIN})} \times 10^{6}$$

where:

$V_{REF}(Max) = Maximum V_{REF} \text{ at } T_{MIN}, T(25^{\circ}C), \text{ or } T_{MAX}$

$V_{REF}(Min) = Minimum V_{REF}$  at  $T_{MIN}$ ,  $T(25^{\circ}C)$ , or  $T_{MAX}$

$V_{REF}(25^{\circ}C) = V_{REF} \text{ at } +25^{\circ}C$

$T_{MAX} = +85$ °C

$T_{MIN} = -40$ °C

#### **Output Voltage Hysteresis**

Output voltage hysteresis, or thermal hysteresis, is defined as the absolute maximum change of reference output voltage after the device is cycled through temperature from either

$$T_HYS$$

+ = +25°C to  $T_{MAX}$  to +25°C

$T_HYS$ - = +25°C to  $T_{MIN}$  to +25°C

It is expressed in ppm using the following equation:

$$V_{HYS}(ppm) = \left| \frac{V_{REF}(25^{\circ}C) - V_{REF}(T_{HYS})}{V_{REF}(25^{\circ}C)} \right| \times 10^{6}$$

where:

$V_{REF}(25^{\circ}C) = V_{REF}$  at 25°C

$V_{REF}(T\_HYS)$  = Maximum change of  $V_{REF}$  at T\_HYS+ or T\_HYS-.

### THEORY OF OPERATION

#### **CIRCUIT INFORMATION**

The AD7280 is a Lithium Ion battery monitoring chip with the ability to monitor the voltage and temperature of 6 series connected battery cells. The AD7280 also provides an interface which can be used to control transistors for cell balancing.

The  $V_{\rm DD}$  and  $V_{\rm SS}$  supplies required by the AD7280 can be taken from the upper and lower voltages of the series connected battery cells. An internal  $V_{\rm REG}$  rail is generated from the supply voltage which provides power for the ADC and the internal interface circuitry. This  $V_{\rm REG}$  voltage is available on an output pin for use external to the AD7280.

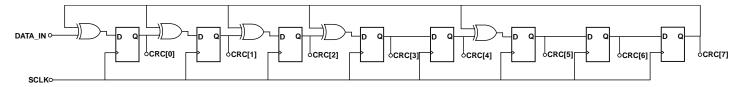

The AD7280 consists of a high voltage input multiplexer, a low voltage input multiplexer and a 12 bit ADC. The high voltage multiplexer allows up to 6 series connected Lithium Ion battery cells to be measured. The low voltage multiplexer allows the temperature of each cell to be measured. A single CNVST signal is required to initiate conversions on all 12 channels, that is 6 voltage and 6 temperature channels. Alternatively the conversion can be initiated through the rising edge of  $\overline{CS}$  on the SPI interface. Each conversion result is stored in a results register (See Register section). On power-up, the CNVST signal is the default option, this can be changed by writing to the CONTROL register. The default sequence of conversions completed following the CNVST signal, or software convert start, is all 6 voltage channels followed by all 6 temperature channels. Two further conversion sequences may be selected by the user, 6 voltage channels followed by 3 temperature channels or just 6 voltage channels. The conversion sequence may be selected by writing to the CONTROL register.

Each voltage and temperature measurement requires a minimum of 1us to acquire and complete a conversion. Depending on the external components connected to the analog inputs of the AD7280 additional acquisition time may be required. A higher acquisition time may be selected through the CONTROL register. For increased accuracy in a noisy environment the user may also select the averaging option through the CONTROL register. This option allows the user to complete 2, 4 or 8 averages on each cell voltage and cell temperature measurement. The averaged conversion results are stored in the results registers. On power-up the default combined acquisition and conversion time will be 1us, with the averaging register set to zero, that is, a single conversion per channel.

The results of the voltage and temperature conversions are read back via the 4 wire Serial Peripheral Interface. The SPI interface is also used to write to and read data from the internal registers.

The AD7280 features an ALERT function which is triggered if the voltage conversion results or the temperature conversion results exceed the maximum and minimum voltage thresholds selected by the user. The threshold levels are selected by writing to the internal registers.

The AD7280 provides 6 analog output voltages which can be used to control external transistors as part of a cell balancing circuit. Each Cell Balance output provides a 0V or 5V voltage, with respect to the potential on base of each individual cell, which can be applied to the gate of the external cell balancing transistors.

The AD7280 features a daisy chain interface. Individual AD7280s can monitor the cell voltages and temperatures of 6 cells, a chain of AD7280s can be used to monitor the cell voltages and temperatures of a larger number of cells. The conversion data from each AD7280 in the chain passes to the system controller via a single standard serial interface. Control data can similarly be passed via the standard serial interface up the chain to each individual AD7280s

The AD7280 includes an on-chip 2.5V reference. The reference voltage is available for use external to the AD7280.

#### **CONVERTER OPERATION**

The AD7280 consists of a high voltage input multiplexer, a low voltage input multiplexer and a 12 bit ADC.

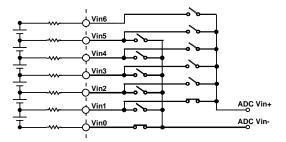

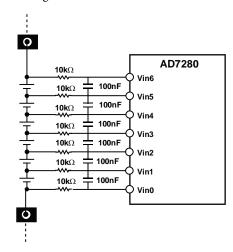

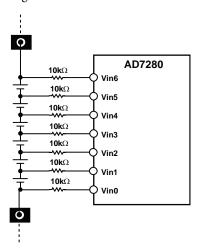

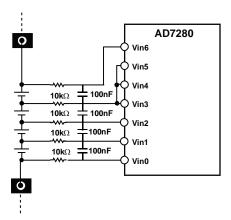

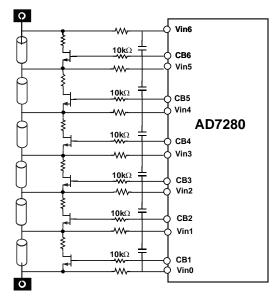

The high voltage multiplexer selects which pair of analog inputs, Vin0 to Vin6, are to be converted. The voltage of each individual cell is measured by converting the difference between adjacent analog inputs, that is, Vin1 – Vin0, Vin2 – Vin1, etc. This is illustrated in Figure 4 and Figure 5. The conversion results for each cell may be accessed after the programmed conversion sequence is complete.

The second multiplexer selects which voltage temperature input, VT1 to VT6, is to be converted. The conversion results for each cell may be accessed after the programmed conversion sequence is complete.

Figure 4. MUX Configuration During Vin1-Vin0 Sampling

Figure 5. MUX Configuration During Vin2-Vin1 Sampling

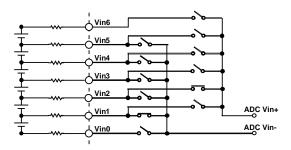

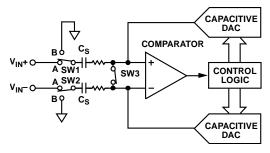

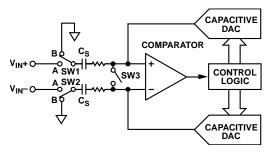

The ADC is a 12-bit successive approximation analog-to-digital converter. The converter is composed of a comparator, SAR, some control logic and 2 capacitive DACs. Figure 6 shows a simplified schematic of the converter. During the acquisition phase switches SW1, SW2 and SW3 are closed. The sampling capacitor array acquires the signal on the input during this phase.

Figure 6. ADC Configuration During Acquisition Phase

When the ADC starts a conversion (Figure 7), SW3 opens and SW1 and SW2 move to position B, causing the comparator to become unbalanced. The control logic and capacitive DACs are used to add and subtract fixed amounts of charge to bring the comparator back into a balanced condition. When the comparator is rebalanced, the conversion is complete. The control logic generates the ADC output code. This output code is then stored in the appropriate register for the input that has been converted.

Figure 7. ADC Configuration During Conversion Phase

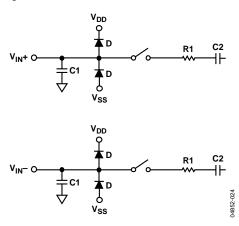

#### **ANALOG INPUT STRUCTURE**

Figure 8 shows the equivalent circuit of the analog input structure of the AD7280. The two diodes provide ESD protection. The resistors are lumped components made up of the on-resistance of the input multiplexer and the track-and-hold switch. The value of these resistors is typically about  $300\Omega$ . Capacitor C1 can primarily be attributed to pin capacitance while Capacitor C2 is the sampling capacitor of the ADC. The total lumped capacitance of C1 and C2 is approximately 13 pF.

Figure 8. Equivalent Analog Input Circuit

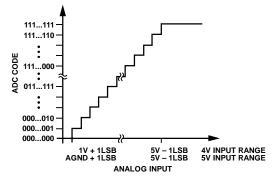

#### TRANSFER FUNCTION

The output coding of the AD7280 is straight binary. The designed code transitions occur at successive integer LSB values (that is, 1 LSB, 2 LSB, and so on). The LSB size is dependent on whether the voltage or temperature inputs are being measured. The analog input range of the voltage inputs is 1V to 5V, the analog input range of the temperature inputs is 0V to 5V. The ideal transfer characteristic is shown in Figure 9.

Table 5. LSB Sizes for Each Analog Input Range

| Selected inputs | Input<br>Range | Full-Scale<br>Range | LSB Size |

|-----------------|----------------|---------------------|----------|

| Voltage         | 1 V to 5 V     | 4 V/4096            | 976 μV   |

| Temperature     | 0 V to 5 V     | 5 V/4096            | 1.22 mV  |

Figure 9. Transfer Characteristic

#### **TYPICAL CONNECTION DIAGRAMS**

Rev. PrF | Page 11 of 38

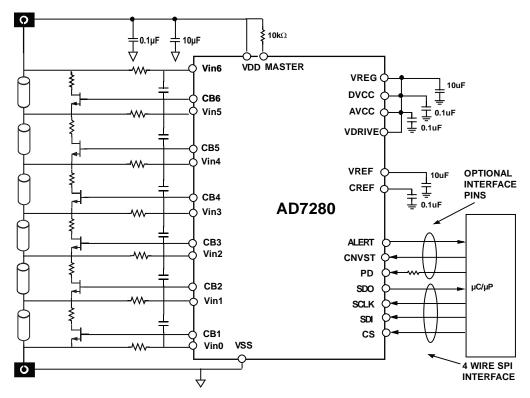

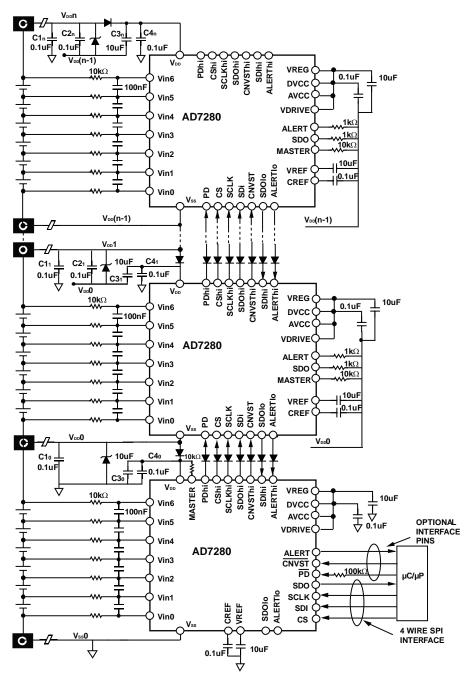

Figure 10. AD7280 Configuration Diagram for 6 Battery Cells

The AD7280 can be used to monitor 6 battery cells connected in series. A typical configuration for a 6 cell battery monitoring application is shown in Figure 10. Lithium Ion Battery applications require a significant number of individual cells to provide the required output voltage. Individual AD7280s can monitor the cell voltages and temperatures of 6 series connected cells. The Daisy Chain Interface of the AD7280 allows each individual AD7280 to communicate with another AD7280 immediately above or below it. The daisy chain interface allows the AD7280s to be electrically connected to the battery management chip, as shown in Figure 11 without the need for individual isolation between each AD7280.

#### **Daisy Chain Connection Diagram**

As shown in Figure 11 external diodes have been included on the  $V_{\rm DD}$  supply to each AD7280 and on each Daisy Chain signal between adjacent AD7280s. These diodes, in combination with the  $10k\Omega$  series resistors on the analog inputs, are recommended to prevent damage to the AD7280 in the event of an open circuit in the battery stack.

It is also recommended that a zener diode be placed across the supplies of each AD7280 as shown in Figure 11. This will prevent an over voltage across the supplies of each AD7280 during the initial connection of the daisychain of AD7280s to the battery stack. A voltage rating of 33V is suggested for this zener diode but lower values may also be used to suit the application.

When using a chain of AD7280s it is also recommended that a 100kOhm series resistor is placed on the PD input. This is recommended to limit current into the PD pin in the event that the uP/DSP or isolators are connected before the supplies of the master AD7280.

Please refer to the Daisy Chain Interface Section for a more detailed description of the Daisy Chain Interface.

In an application which includes a safety mechanism, designed to open circuit the Battery Stack, additional isolation will be required between the AD7280 above the break point and the battery management chip.

#### **EMC Considerations**

In addition to the standard decoupling capacitors, C2n and C3n, as shown in Figure 11, it is also recommended that an option for additional capacitors, C1n and C4n, be included in the circuit to increase immunity to Electromagnetic Interference. These capacitors, placed on either side of the  $V_{\rm DD}$  protection diode, would be used to decouple the  $V_{\rm DD}$  supply of each AD7280 with respect to system ground, that is, the ground of the master AD7280 in the daisychain.

It is recommended that ferrite beads be included on the battery

connections to the  $V_{\text{\tiny DD}}$  and  $V_{\text{\tiny SS}}$  supplies. It is also recommended that pull-down resistors should be used on the

ALERT and SDO outputs on each of the slave parts in the AD7280 daisychain.

Figure 11. AD7280 Daisy Chain Configuration

#### $V_{DRIVE}$

The AD7280 also has a  $V_{\text{DRIVE}}$  feature to control the voltage at which the serial interface operates.  $V_{\text{DRIVE}}$  allows the ADC to easily interface to both 3 V and 5 V processors. For example, in the recommended configuration the AD7280 is operated with a  $V_{\text{CC}}$  of 5 V, however the  $V_{\text{DRIVE}}$  pin could be powered from a 3 V supply, allowing a large dynamic range with low voltage digital

processors.

#### **REFERENCE**

The internal reference is temperature compensated to 2.5 V  $\pm$  5 mV. The reference is trimmed to provide a typical drift of 3 ppm/°C. The internal reference circuitry consists of a 1.2 V band gap reference and a reference buffer. The AD7280 internal

reference is available at the  $V_{REF}$  pin. The  $V_{REF}$  pin should be decoupled to REFGND using a 10  $\mu\text{F},$  or greater, ceramic capacitor. The  $C_{REF}$  pin should be decoupled to REFGND using a 0.1  $\mu\text{F},$  or greater, ceramic capacitor. The internal reference is capable of driving an external load of up to 10kOhms.

# CONVERTING CELL VOLTAGES AND TEMPERATURES

A conversion may be initiated on the AD7280 <u>using ei</u>ther the <u>CNVST</u> input or the serial interface. A single <u>CNVST</u> signal is required to initiate conversions on all 12 channels, that is 6 voltage and 6 temperature channels. Alternatively the conversion can be initiated through the rising edge of <u>CS</u> on the SPI interface.

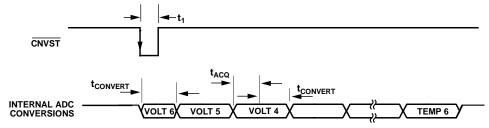

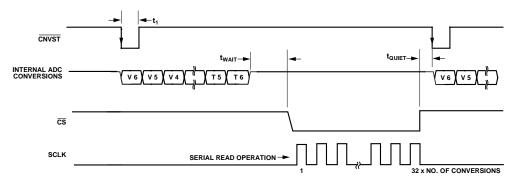

When using the CNVST input the falling edge of CNVST places the track and hold on the voltage inputs Vin6 and Vin5, that is across Cell 6, into hold mode and initiates the conversion. At the end of the first conversion the AD7280 generates an internal End of Conversion signal. This internal EOC will select the next cell voltage inputs for measurement though the multiplexer, that is, Vin5 and Vin4. The track-and-hold circuit will acquire the new input voltage and a second internal convert start signal is generated which places the track-and-hold into hold mode and initiates the conversion. This process is repeated until all the selected voltage and temperature cell inputs have been converted. Please refer to Figure 12 and Figure 13. Note, once all selected conversions have been completed voltage inputs Vin6 and Vin5 are again selected through the multiplexer and the voltage across Cell 6 is acquired in preparation for the next conversion request.

By setting bits D15 and D14 in the control register the voltage and temperature cells to be converted are selected. There are four options available.

Table 6. Voltage and Temperature Cell Selection

| D15 to<br>D14 | Voltage inputs | Temperature Inputs |

|---------------|----------------|--------------------|

| 00            | 1 to 6         | 1 to 6             |

| 01            | 1 to 6         | 1, 3 & 5           |

| 10            | 1 to 6         | None               |

| 11            | ADC Self Test  | None               |

Each voltage and temperature conversion requires a minimum of 1us to acquire and convert the cell voltage or temperature voltage input. For example, when D15 and D14 are set to zero the falling edge of  $\overline{\text{CNVST}}$  will trigger a series of 12 conversions. This will require a minimum of 12 $\mu$ s to convert all selected measurements. If no temperature conversions are required then Bits D15 and D14 would be set to 10. In this case the conversion request will trigger a series of 6 conversions, requiring a minimum of 6 $\mu$ s.

Following the completion of all requested conversions the

results may be read back from either a single device or from all devices in a daisychain by use of the SPI and Daisychain interfaces. More information on this may be found in the Serial Interface and Daisy Chain Interface sections. As shown in Figure 13, a wait time,  $t_{WAIT}$ , is required between the completion of conversions and the start of readback. This time is required to synchronise between the high speed conversion clock and the lower speed clock used for all other AD7280 operations. The maximum value of  $t_{WAIT}$  is  $5\mu$ s.

#### Track-and-Hold

The track-and-hold on the analog input of the AD7280 allows the ADC to accurately convert an input sine wave of full-scale amplitude to 12-bit accuracy.

Following a completed conversion the AD7280 enters its tracking mode. The time required to acquire an input signal depends on how quickly the sampling capacitor is charged. This in turn will depend on the input impedance and any external components placed on the analog inputs. The default acquisition time of the AD7280 on initial power up is 400 ns. This can be increased in steps of 400ns to 1.6 us to provide flexibility in selecting external components on the analog inputs. The acquisition time is selected by writing to bits D6 and D5 in the CONTROL register.

It should also be noted once the acquisition time is reconfigured 90µs should be allowed before performing any conversions. This time should be allowed between writing to the CONTROL register to change the acquisition time and initiating the first conversion. In the case of conversions which are being initiated by the rising edge of the  $\overline{\text{CS}}$  pin, this will require 2 separate write commands to the CONTROL register. The first to configure the AD7280 for the required acquisition time, the second, following a delay of 90µs, to initiate the conversion on the rising edge of  $\overline{\text{CS}}$ .

**Table 7.Analog Input Acquisition Time.**

| D6 to D5 | Acquisition Time |

|----------|------------------|

| 00       | 400 ns           |

| 01       | 800 ns           |

| 10       | 1.2 μs           |

| 11       | 1.6 μs           |

The acquisition time required is calculated using the following formula:

$$t_{ACQ} = 10 \times ((R_{SOURCE} + R) C)$$

where:

${\it C}$  is the sampling capacitance, the value of the sampling capacitor, 13pF

*R* is the resistance seen by the track-and-hold amplifier looking at the input,  $300\Omega$ .

*R*<sub>SOURCE</sub> should include any extra source impedance on the analog input.

Figure 12. ADC conversions on the AD7280

Figure 13. ADC conversions & Readback on the AD7280

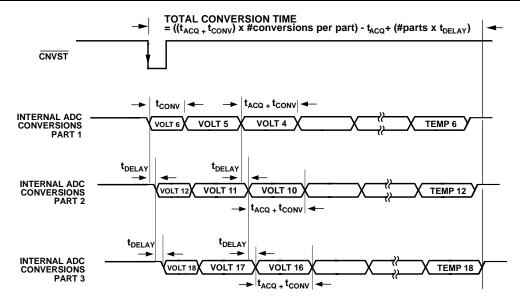

# Converting Cell Voltages and Temperatures with a chain of AD7280s