Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

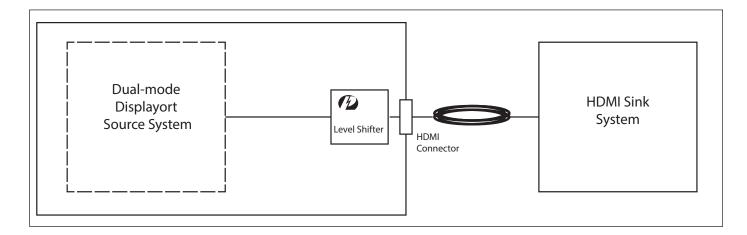

## **Application diagram**

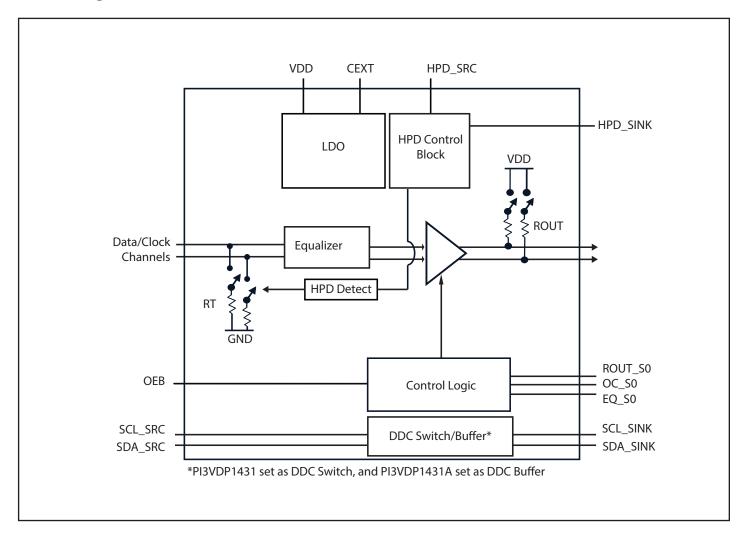

## **Block diagram**

15-0014

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

## **Pin Description**

| Pin#     | Pin Name | Type  | Description                                                                                          |

|----------|----------|-------|------------------------------------------------------------------------------------------------------|

|          |          | DILIE | 3.3V power supply.                                                                                   |

| 1,22     | VDD      | PWR   | Add external 0.1uF capacitor to GND                                                                  |

| _        | ODIVE.   | DILIE | LDO output for internal core supplier.                                                               |

| 2        | CEXT     | PWR   | Add external capacitor (2.2uF-4.7uF) to GND                                                          |

| 14,31,32 | GND      | GND   | Ground connection                                                                                    |

| 29       | HPD_SINK | I     | Sink side hot plug detector input; internal pull-down at 120 Kohm.                                   |

| 11       | HPD_SRC  | О     | HPD output to source side                                                                            |

| 3        | IN_D2-   |       |                                                                                                      |

| 4        | IN_D2+   |       |                                                                                                      |

| 5        | IN_D1-   |       |                                                                                                      |

| 6        | IN_D1+   |       | Th (Do ) PH 500l                                                                                     |

| 7        | IN_D0-   | I     | TMDS inputs. RT=50Ohm                                                                                |

| 8        | IN_D0+   |       |                                                                                                      |

| 9        | IN_CLK-  |       |                                                                                                      |

| 10       | In_CLK+  |       |                                                                                                      |

| 26       | OUT_D2-  |       |                                                                                                      |

| 25       | OUT_D2+  |       |                                                                                                      |

| 24       | OUT_D1-  |       |                                                                                                      |

| 23       | OUT_D1+  |       | TIN CDC DOVITE TOOL                                                                                  |

| 21       | OUT_D0-  | О     | TMDS outputs. ROUT=50Ohm is active when ROUT_S0 = "1"                                                |

| 20       | OUT_D0+  |       |                                                                                                      |

| 19       | OUT_CLK- |       |                                                                                                      |

| 18       | OUT_CLK+ |       |                                                                                                      |

| 13       | SCL_SRC  | IO    | Source side DDC Clock                                                                                |

| 12       | SDA_SRC  | IO    | Source side DDC Data                                                                                 |

| 27       | SCL_SINK | IO    | Sink side DDC Clock for connector                                                                    |

| 28       | SDA_SINK | IO    | Sink side DDC Data for connector                                                                     |

| 16       | OC_S0    | I     | TMDS output three-level pre-emphasis selection. See OC_S0 truth table. GND=0dB, NC=1.5dB, VDD=2.5dB; |

| 17       | EQ_S0    | I     | TMDS input three-level equalization selection. See EQ_S0 truth table. GND=2.5dB, NC=5dB, VDD=7.5dB;  |

| 30       | OEB      | I     | Output Enable control. Active low. Internal pull-down at 100 Kohm.                                   |

| 15       | ROUT_S0  | I     | TMDS output double termination selection. Internally pull-up to VDD.                                 |

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

### **Functional Description**

#### **Squelch Function:**

Automatic output squelch function disables TMDS output when no Input signal presents. Output Disable (Squelch) Mode uses TMDS Clock channel signal detection. When low voltage levels on the TMDS input clock signals are detected, Squelch state enables and TMDS output port signals shall disable; when the TMDS clock input signal levels are above a pre-determined threshold voltage, output ports shall return to the normal voltage swing levels.

#### HPD\_SINK Shut Down

When HPD\_SINK pin is floating or tie to GND, TMDS outputs shall shut down to sleep mode; HPD\_SINK does not control DDC channel.

#### Pre-emphasis Control OC\_S0 Truth Table

| Output pre-emphasis setting |               | Functional Description |              | Notes                       |

|-----------------------------|---------------|------------------------|--------------|-----------------------------|

| ROUT_S0                     | OC_S0         | Single-end Vswing      | Pre-emphasis | Notes                       |

|                             | "0"           | 500 mV                 | 0 dB         | Open drain output.          |

| "0"                         | "NC" or VDD/2 | 500 mV                 | 1.5 dB       | Open drain output: default  |

|                             | "1"           | 500 mV                 | 2.5 dB       | Open drain output           |

|                             | "0"           | 500 mV                 | 0 dB         | Double termination          |

| "1"                         | "NC" or VDD/2 | 500 mV                 | 1.5 dB       | Double termination: default |

|                             | "1"           | 500 mV                 | 2.5 dB       | Double termination          |

#### Input Equalization EQ\_S0Truth Table

| EQ_S0         | Functional Description | Note                                                                    |

|---------------|------------------------|-------------------------------------------------------------------------|

| "0"           | 2.5 dB                 |                                                                         |

| "NC" or VDD/2 | 5 dB                   | TMDS Clock(CLK) channel EQ is always fixed as 3dB without pre-emphasis. |

| "1"           | 7.5 dB                 |                                                                         |

4

#### **Output Signal Enable OEB Truth Table**

| OEB | Functional Description                      |

|-----|---------------------------------------------|

| "0" | Normal mode                                 |

| "1" | Disable output signal for power saving mode |

## Sink side Hot Plug Detect HPD\_SINK Truth Table

|   | HPD_SINK | Functional Description                      |

|---|----------|---------------------------------------------|

|   | "1"      | Normal mode                                 |

| Ī | "0"      | Disable output signal for power saving mode |

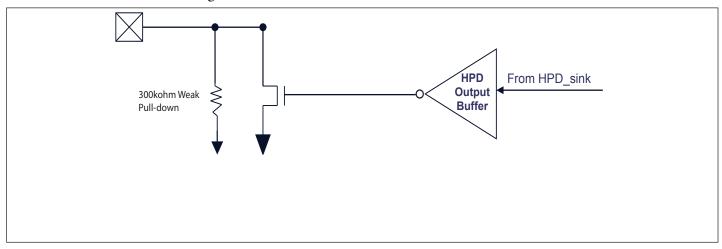

#### Source side HPD\_SRC Block Diagram

5

Note:

<sup>\*1:</sup> Open drain buffer is recommended with external pull-up resistor to <4.5V power supply.

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

### **Absolute Maximum Ratings**

| Item                                          | Absolute Rating*1 |

|-----------------------------------------------|-------------------|

| Supply Voltage to Ground Potential            | 4.5V              |

| All Inputs and Outputs                        | -0.5V to 4.5V     |

| 5V Tolerance I/O (SDA_SINK,SCL_SINK,HPD_SINK) | -0.5V to 5.5V     |

| Storage Temperature                           | -65 to +150°C     |

| Junction Temperature                          | 125°C             |

| Soldering Temperature                         | 260°C             |

Note \*1) Stress beyond those lists under "Absolute Maximum Ratings" may cause permanent damage to the device

## **Recommended Operation Conditions**

| Symbol | Parameter                     | Min. | Тур. | Max. | Unit |

|--------|-------------------------------|------|------|------|------|

| TA     | Ambient Operating Temperature | -20  | 25   | 85   | °C   |

| VDD    | Power Supply Voltage          | 2.89 | 3.3  | 3.6  | V    |

## **DC Specification** (VDD = $3.3V \pm 10\%$ )

| Symbol | Parameter             | Conditions                    | Min. | Тур. | Max. | Unit |

|--------|-----------------------|-------------------------------|------|------|------|------|

| IDD    | VDD Supply Current    | Open drain, 500mV single-end, |      | 80   | 100  | mA   |

| IDD    | VDD Supply Current    | Pre-emphasis 0dB              |      | 80   | 100  | IIIA |

| ISTB   | C4 1 1 1 .            | VDD=3.6V, DDC passive switch, |      | 40   | 50   | A    |

| 131 b  | Stand-by mode         | HPD_SINK="0", OEB="1"         |      |      |      | uA   |

| ICOLLI | Caualah maada ayamant | VDD=3.6V, DDC passive switch, |      | 2.7  | 4    | A    |

| ISQLH  | Squelch mode current  | HPD_SINK=3.6V                 |      | 2.7  | 4    | mA   |

#### HPD\_SRC pin

| Symbol | Parameter                         | Conditions        | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------|-------------------|------|------|------|------|

| VOL    | Open Drain Output Low<br>Voltage  | IOL = 4 mA        | 0    |      | 0.4  | V    |

| IOFF   | Off leakage current               | VDD=0, VIN=3.6V   |      |      | 25   |      |

| IOZ    | Open drain Output leakage current | VDD=3.6, VIN=3.6V |      |      | 25   | μΑ   |

### HPD\_SINK

| Symbol | Parameter                           | <b>Test Conditions</b> | Min. | Typ. | Max. | Unit |

|--------|-------------------------------------|------------------------|------|------|------|------|

| IIH    | High level digital input current(1) | VIH =5.5V              | -10  |      | 80   | μΑ   |

| IIL    | Low level digital input current(1)  | VIL = GND              | -10  |      | 10   | μA   |

| VIH    | High level digital input voltage    | VDD=3.3V               | 2.0  |      |      | V    |

| VIL    | Low level digital input voltage     | VDD=3.3V               | 0    |      | 0.8  | V    |

### Control pin (OEB with 100k pull to gnd)

| Symbol | Parameter                        | <b>Test Conditions</b> | Min. | Typ. | Max. | Unit |

|--------|----------------------------------|------------------------|------|------|------|------|

| IIH    | High level digital input current | VIH =3.3V              | -10  |      | 40   | μΑ   |

| IIL    | Low level digital input current  | VIL = GND              | -10  |      | 10   | μΑ   |

| VIH    | High level digital input voltage |                        | 2.0  |      |      | V    |

| VIL    | Low level digital input voltage  |                        | 0    |      | 0.8  | V    |

### Control pin (EQ\_S0, OC\_S0 with 100k pull high and 100k pull down when TMDS active)

| Symbol | Parameter                        | <b>Test Conditions</b> | Min. | Typ. | Max. | Unit |

|--------|----------------------------------|------------------------|------|------|------|------|

| IIH    | High level digital input current | VIH =3.3V              | -10  |      | 40   | μΑ   |

| IIL    | Low level digital input current  | VIL = GND, VDD=3.3V    | -40  |      | 10   | μΑ   |

### Control pin (ROUT\_S0)

| Symbol | Parameter                        | <b>Test Conditions</b> | Min. | Тур. | Max. | Unit |

|--------|----------------------------------|------------------------|------|------|------|------|

| IIH    | High level digital input current | VIH =VDD               | -10  |      | 10   | μΑ   |

| IIL    | Low level digital input current  | VIL = GND              | -20  |      | 10   | μΑ   |

| VIH    | High level digital input voltage |                        | 2.0  |      |      | V    |

| VIL    | Low level digital input voltage  |                        | 0    |      | 0.8  | V    |

### DDC Channel switch (P/N: PI3VDP1431)

| Symbol | Parameter                                       | <b>Test Conditions</b>        | Min. | Typ. | Max. | Unit |

|--------|-------------------------------------------------|-------------------------------|------|------|------|------|

| ILK    | Input leakage current                           | DDC switch is OFF, VIN=5.5V   | -10  |      | 30   | μΑ   |

| CIO    | Input/Output capacitance when passive switch on | VIpp(peak-peak) = 1V, 100 kHz |      | 10   |      | pF   |

| RON    | Passive Switch resistance                       | IO = 3mA, $VO = 0.4V$         |      | 30   | 50   | Ω    |

| VPASS  | Switch Output voltage                           | VI=3.3V, II=100uA, VDD=3.3V   | 1.5  | 2.0  | 2.5  | V    |

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

### DDC Channel Buffer (P/N: PI3VDP1431A)

| Symbol   | Parameter                                                                   | Conditions                       | Min. | Тур. | Max. | Unit |

|----------|-----------------------------------------------------------------------------|----------------------------------|------|------|------|------|

| VIH_SRC  | Source Side DDC Buffer Input High Voltage                                   |                                  | 0.6  |      |      | V    |

| VIL_SRC  | Source Side DDC Buffer Input Low Voltage                                    |                                  |      |      | 0.4  | V    |

| VOL_SRC  | Source Side DDC Buffer Output Low Voltage                                   | External pull-up to VDD          | 0.47 | 0.52 | 0.6  | V    |

| VOL_SINK | Sink Side DDC Buffer Output Low Voltage                                     | from $1.5k\Omega$ to $10k\Omega$ |      |      | 0.2  | V    |

| VIH_SINK | Sink Side DDC Buffer Input High Voltage                                     |                                  | 2.0  |      |      | V    |

| VIL_SINK | Sink Side DDC Buffer Input Low Voltage                                      |                                  |      |      | 0.8  | V    |

| CI_SRC   | Source side DDC capacitance when active switch is on, or passive switch off | VIpp(peak-peak)=1V, 100          |      | 5    |      | pF   |

| CI_SINK  | Sink side DDC capacitance when active switch is on, or passive switch off   | KHz                              |      | 5    |      | pF   |

#### TMDS differential pins

| Symbol   | Parameter                                                               | <b>Test Conditions</b>         | Min.    | Typ. | Max.              | Unit |

|----------|-------------------------------------------------------------------------|--------------------------------|---------|------|-------------------|------|

| VOH      | Single-ended high level output voltage                                  |                                | VDD-10  |      | VDD+10            | mV   |

| VOL      | Single-ended low level output voltage                                   |                                | VDD-600 |      | VDD-<br>400       | mV   |

| VSWING   | Single-ended output swing voltage                                       | VDD 2.2V DOLLT 500             | 400     |      | 600               | mV   |

| VOD(O)*1 | Overshoot of output differential voltage                                | $VDD = 3.3V$ , $ROUT=50\Omega$ |         |      | 180 <sup>*1</sup> | mV   |

| VOD(U)*2 | Undershoot of output differential voltage                               |                                |         |      | 200*2             | mV   |

| VOC(SS)  | Change in steady-state common- mode output voltage between logic states |                                |         |      | 5                 | mV   |

| IOS      | Short Circuit output current at open drain mode                         | Short to VDD                   | -12     |      | 12                | mA   |

| 103      | Short Circuit output current at double termination mode                 | Short to VDD                   | -24     |      | 24                | mA   |

| VI(open) | Single-ended input voltage under high impedance input or open input     | II = 10uA                      | VDD-10  |      | VDD+10            | mV   |

| RT       | Input termination resistance                                            | VIN = 2.9V                     | 45      | 50   | 55                | Ω    |

| IOZ      | Leakage current with Hi-Z I/O                                           | VDD = 3.6V,                    |         |      | 30                | μΑ   |

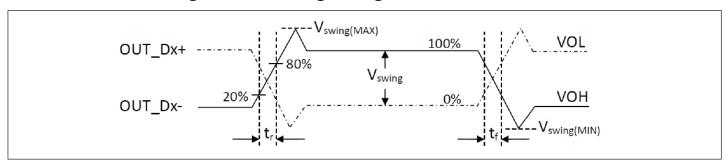

#### Note:

<sup>\*1)</sup> Overshoot of output differential voltage VOD(O) = (VSWING(MAX) \* 2) \* 15%

<sup>\*2)</sup> Undershoot of output differential voltage VOD(O) = (VSWING(MIN) \* 2) \* 25%

AC Characteristics (Over recommended operating conditions unless otherwise noted)

| Symbol        | Parameter                                                                                        | <b>Test Condition</b>                                       | Min. | Typ.  | Max. | Units |

|---------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-------|------|-------|

| TMDS differe  | ential pins                                                                                      | 1                                                           |      | ·     | ,    | ·     |

| tPD           | Propagation delay                                                                                |                                                             |      |       | 2000 |       |

| tR/tF         | Differential output signal rise/fall time(20% - 80%), open drain, 0dB preemphasis                |                                                             |      | 120   |      |       |

|               | Differential output signal rise/fall time (20% - 80%), open drain, 2.5dB preemphasis             | $VDD = 3.3V$ $ROUT = 50\Omega$                              |      | 100   |      |       |

| tSK(P)        | Pulse skew                                                                                       | -                                                           |      | 10    | 50   | ps    |

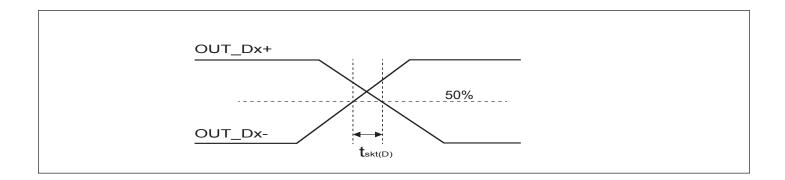

| tSK(D)        | Intra-pair differential skew                                                                     |                                                             |      | 23    | 50   |       |

| tSK(O)        | Inter-pair differential skew                                                                     |                                                             |      |       | 100  |       |

| tJIT(PP)      | Peak-to-peak output Clock residual jitter                                                        | Data Input = 3.4 Gbps                                       |      | 30 60 |      |       |

| tJIT(PP)      | Peak-to-peak output DATA Residual<br>Jitter                                                      | HDMI data patterns                                          |      | 40    | 70   |       |

| tEN           | Enable time                                                                                      |                                                             |      |       | 50   |       |

| tDIS          | Disable time                                                                                     |                                                             |      |       | 0.01 | μs    |

| DDC I/O pins  | Propagation delay : SCL_SINK/SDA_SINK to SCL/SDA or SCL/ SDA to SCL_SINK/SDA_ SINK in passive SW | CL = 10pF                                                   |      |       | 5    | ns    |

| Control and S | status Pins (HPD_SINK, HPD)                                                                      |                                                             |      |       |      |       |

| tPD(HPD)      | Propagation delay : From HPD_SINK to the active port of HPD, high to low                         | CL = 10 pF,<br>Pull high resistor= $1k\Omega$<br>Open drain |      | 10    |      | ns    |

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

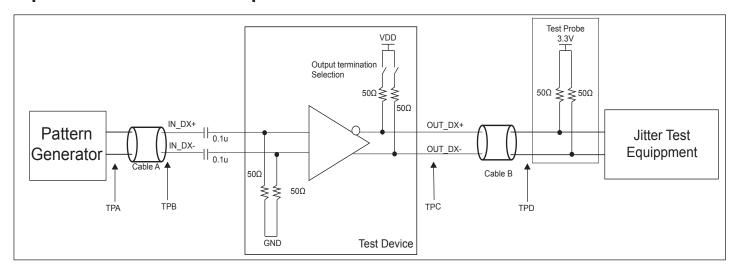

## **Input Measurement Test Setup**

## Rise/Fall Time and Single-ended Swing Voltage

### **Intra-pair Skew Definition**

15-0014

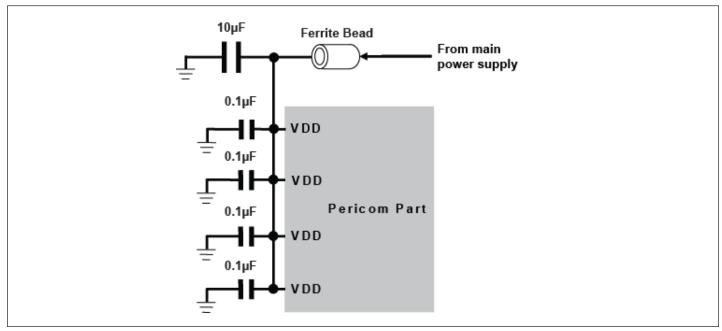

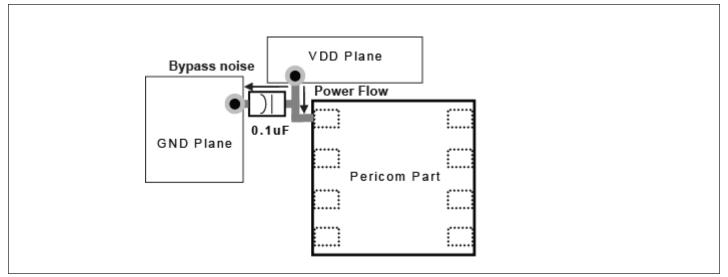

### **Power Supply Decoupling Circuit**

It is recommended to put  $0.1~\mu F$  decoupling capacitors on each VDD pins of our part, there are four  $0.1~\mu F$  decoupling capacitors are put in Figure 1 with an assumption of only four VDD pins on our part, if there is more or less VDD pins on our Pericm parts, the number of  $0.1~\mu F$  decoupling capacitors should be adjusted according to the actual number of VDD pins. On top of  $0.1~\mu F$  decoupling capacitors on each VDD pins, it is recommended to put a  $10~\mu F$  decoupling capacitor near our part's VDD, it is for stabilizing the power supply for our part. Ferrite bead is also recommended for isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Recommended Power Supply Decoupling Capacitor Diagram

### **De-coupling Capacitors Requirements**

There is no special requirement on the material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

#### **Layout Placement Consideration**

- → Each 0.1 μF decoupling capacitor should be placed as close as possible to each VDD pin.

- → VDD and GND planes should be used to provide a low impedance path for power and ground.

- → Via holes should be placed to connect to VDD and GND planes directly.

- → Trace should be as wide as possible

- → Trace should be as short as possible.

- → The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- → 10 µF Capacitor should also be placed closed to our part and should be placed in the middle location of 0.1 µF capacitors.

- → Avoid the large current circuit placed close to our part; especially when it is shared the same VDD and GND planes. Since large current flowing on our VDD or GND planes will generate a potential variation on the VDD or GND of our part.

Decoupling Capacitor Placement Diagram

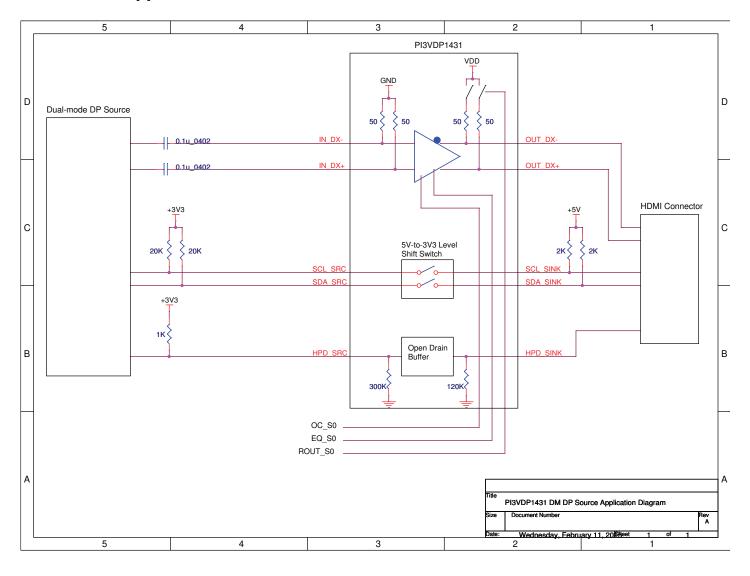

## **PI3VDP1431 Application Schematic**

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

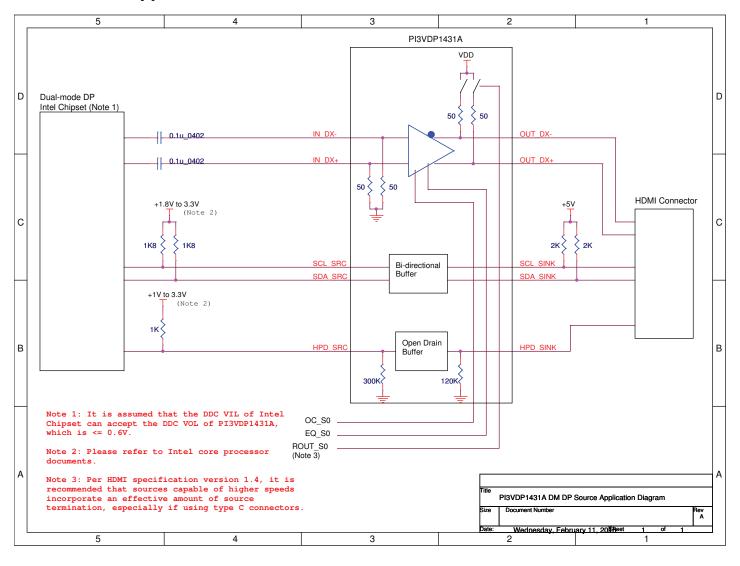

## **PI3VDP1431A Application Schematic**

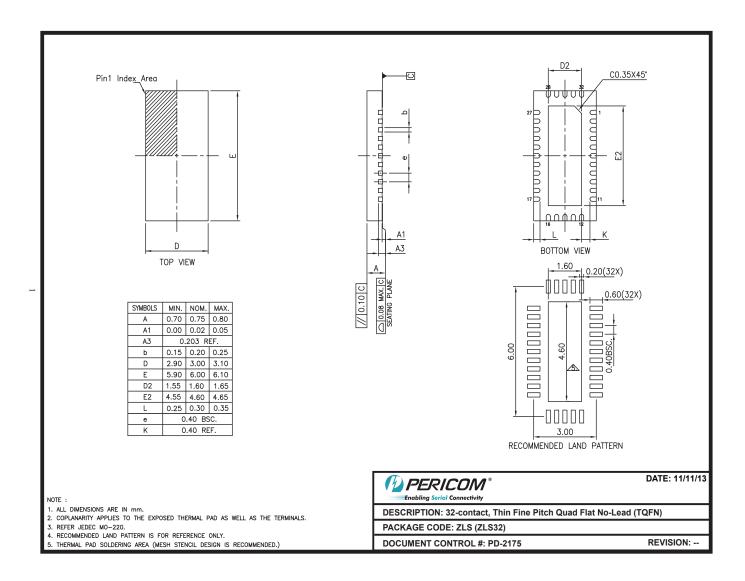

### Packaging Mechanical: 32-Contact TQFN (ZLS)

$Please\ check\ for\ the\ latest\ package\ information\ on\ the\ Pericom\ web\ site\ at\ www.pericom.com/support/packaging.$

## **Ordering Information**

| Ordering Number  | Package Code | Package Description                                                          |

|------------------|--------------|------------------------------------------------------------------------------|

| PI3VDP1431ZLSEX  | ZLS          | 32-Contact, Thin Fine Pitch Quad Flat No Lead Package (TQFN) with DDC Switch |

| PI3VDP1431AZLSEX | ZLS          | 32-Contact, Thin Fine Pitch Quad Flat No Lead Package (TQFN) with DDC Buffer |

15

Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- X suffix = Tape/Reel

Low Power Dual-mode DisplayPort 3.4Gb/s Level Shifter/Redriver

#### **Related Products**

| Part Number  | Product Description                                                  |  |

|--------------|----------------------------------------------------------------------|--|

| PI3WVR12612  | Wide Voltage Range DisplayPort™ & HDMI Video Switch                  |  |

| PI3HDX1204-B | HDMI2.0 Redriver and Displayport Level Shifter for 6Gbps Application |  |

| PI3EQXDP1201 | Displayport 1.2 redriver with built-in auto test mode                |  |

| PI3HDX414    | 1:4 Active 3.4Gbps HDMI1.4b Splitter/DeMux with Signal Conditioning  |  |

| PI3HDX412BD  | 1:2 Active 3.4Gbps HDMI1.4b Splitter/DeMux with Signal Conditioning  |  |

| PI3HDX621    | 2:1 Active 3.4Gbps HDMI 1.4b Switch                                  |  |

| PI3HDMI336   | 3:1 Active 2.5Gbps HDMI Switch with I2C control and ARC Transmitter  |  |

#### **Reference Information**

| Document | Description                                                                          |

|----------|--------------------------------------------------------------------------------------|

| HDMI1.4b | High-Definition Multimedia Interface Specification Version 1.4b, HDMI Licensing, LLC |

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH PERICOM PRODUCT. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN PERICOM'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Pericom may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Pericom reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specification. Current characterized errata are available on request.

Contact your local Pericom Sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright 2014 Pericom Corporation. All rights reserved. Pericom and the Pericom logo are trademarks of Pericom Corporation in the U.S. and other countries.

15-0014