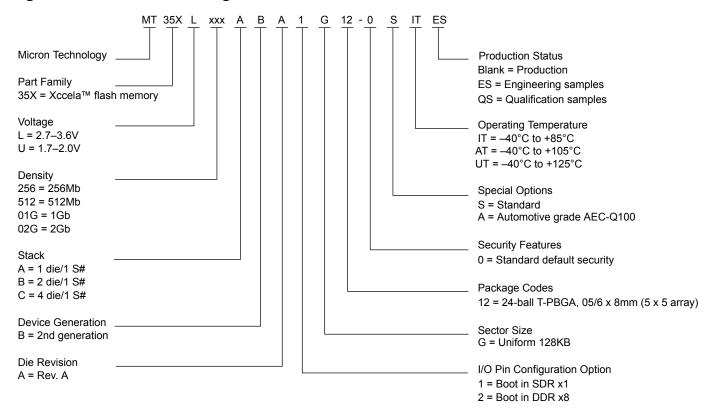

#### **Part Number Ordering**

Micron<sup>®</sup> **Xccela** flash devices are available in different configurations and densities. Verify valid part numbers by using Micron's part catalog search at www.micron.com. To compare features and specifications by device type, visit www.micron.com/products. Contact the factory for devices not found.

**Figure 1: Part Number Ordering Information**

# Xccela<sup>™</sup> Flash Memory Data Sheet Brief Important Notes and Warnings

## **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

#### Xccela<sup>™</sup> Flash Memory Data Sheet Brief Device Description

## **Device Description**

This is a brief version of the MT35X data sheet. For complete information, please refer to the full NDA version.

To request access to the full NDA version of the MT35X data sheet, please contact your sales representative.

The Micron **Xccela** flash is a high-performance, multiple I/O, SPI-compatible flash memory device. It features a high-speed, low pin count **Xccela** bus interface with a DDR clock frequency of up to 200 MHz for 1.8V parts and up to 133 MHz for 3.0 V parts, using eight I/O signals and a data strobe (DQS pin).

SUSPEND and RESUME commands provide the ability to pause and resume PRO-GRAM/ERASE operations. Nonvolatile and volatile configuration registers enable respective default and temporary settings such as READ operation dummy clock cycles and wrap modes, memory protection, output buffer impedance, SPI protocol type and XIP mode.

Memory is organized as uniform 128KB sectors, 4KB and 32KB subsectors, and 256 byte pages. The device also includes a 64-byte one-time-programmable (OTP) memory area that can be permanently locked.

Direct boot in octal DDR protocol provides high performance and ease of use, enabling communication between the host and flash device without need to configure extended SPI protocol operations. However, the device still supports both extended SPI and octal DDR protocols to ensure legacy system support and an easy migration path. The extended SPI protocol supports address and data transmission on one or eight data lines, depending on the command.

Information in octal DDR protocol is always transmitted by eight data lines on both rising and falling clock edges. Most legacy x1 SPI commands are supported, but require only one clock cycle because the command is latched on both the rising and falling edges of the clock. Address cycles are fixed at 4-byte READ operations from the flash array.

The host is not required to drive DQS during the input operation to the memory. The data input (DQ) to the memory still relies on clock (C) to latch all address and data operations. Most register outputs require dummy clock cycles due to the critical timing from command decoding. With the help of DQS for data latching, the number of dummy clocks is transparent to the host.

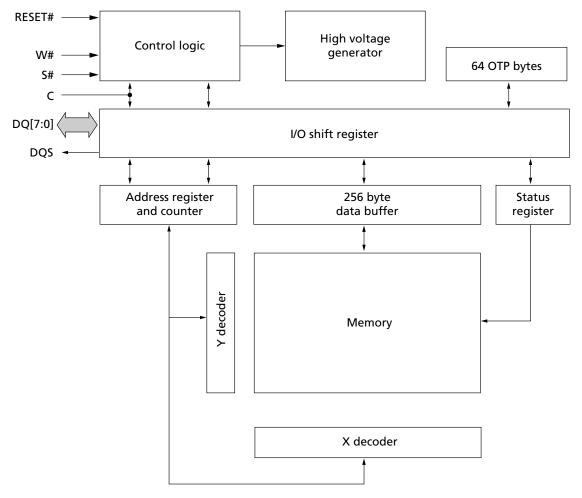

#### **Block Diagram**

Figure 2: Block Diagram - Components and Signals

Note: 1. Each page of memory can be individually programmed, but the device is not page-erasable.

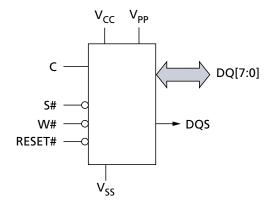

#### **Device Logic Diagram**

#### Figure 3: Logic Diagram

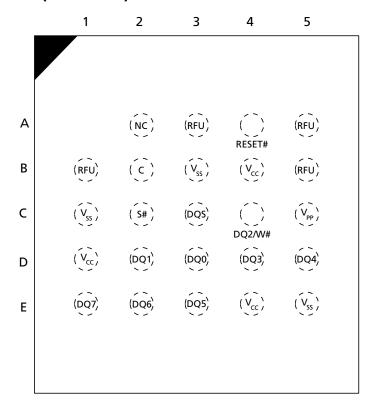

# **Signal Assignments**

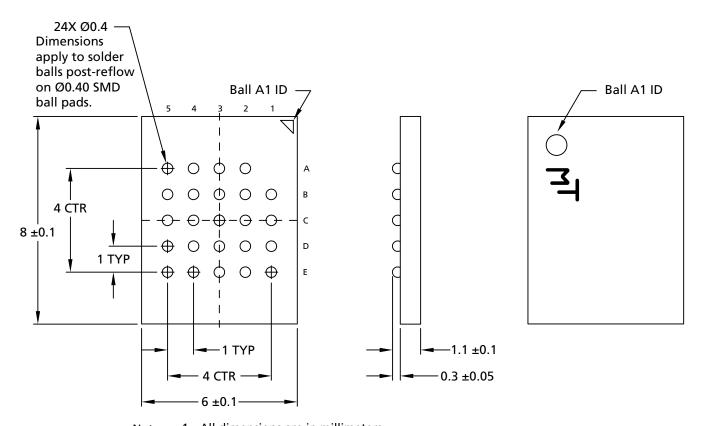

Figure 4: 24-Ball TBGA, 5 x 5 (Balls Down)

### Xccela<sup>™</sup> Flash Memory Data Sheet Brief Signal Descriptions

# **Signal Descriptions**

The table below is a comprehensive list of device signals. All signals listed may not be supported. See Signal Assignments for device-specific information.

**Table 1: Signal Descriptions**

| Symbol          | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С               | Input  | <b>Clock:</b> Provides timing for the serial interface. Command, address, or data inputs are latched on the rising edge of C. Data is shifted out on the falling edge of C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| S#              | Input  | <b>Chip select:</b> When S# is LOW, device is selected and in active power mode. Operations are initiated on the falling edge of S#.  When S# is HIGH, device is deselected, DQ pins are tri-stated, and unless an internal WRITE operation is in progress, device enters standby mode.                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET#          | Input  | <b>RESET:</b> Resets device to its default settings, such as after a volatile configuration register setting which then requires a return to the device default setting.  Reset is optional when device settings are fixed by nonvolatile configuration register settings and always synchronized with the host. This pad is internally tied to weak pull-up so the pin can be floated.                                                                                                                                                                                                                                                                                        |

| W#              | Input  | <b>Write protect:</b> This input signal is used to freeze the status register in conjunction with the enable/disable bit of the status register. When the enable/disable bit of the status register is set to 1 and the W# signal is driven LOW, the status register nonvolatile bits become read-only and the WRITE STATUS REGISTER operation will not be executed. During the extended-SPI protocol with OCTAL READ/PROGRAM instructions, and during octal DDR protocol, this pin functions are an input/output (DQ2 functionality). This signal does not have internal pull-ups, it should not be left floated and must be driven, even if none of W#/DQ2 function is used. |

| DQ[7:0]         | I/O    | <b>Serial I/O:</b> Bidirectional signals that transfer address, data, and command information. In extended-SPI protocol, DQ0 functions as input and DQ1 as output. DQ[7:2] are not used. In octal protocol, input/output on DQ[7:0] depends on the command. Input can be latched on the rising edge of C (SDR) or on both edges of C (DDR). Data can be shifted out on the falling edge of C (SDR) or on both edges of C (DDR). In octal DDR, DQ[7:0] always function as I/O, input is latched on both edges of C, and output is shifted out on both edges of C. DQ2 is used also as write protection control.                                                                 |

| DQS             | Output | <b>Data strobe:</b> Indicates output data valid for DDR modes and is required to support high speed data output. Not required in extended-SPI protocol except to achieve high frequency for specific DDR commands. Used for READ but not for WRITE operations. Configured by nonvolatile and volatile configuration register bit 5 at address 00h. When enabled, DQS is driven to ground at S# LOW and until the device is driving output data, in which case DQS toggles to synchronize data output. When not enabled, DQS is not driven.                                                                                                                                     |

| V <sub>CC</sub> | Supply | Supply voltage: Core and I/O supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>PP</sub> | Supply | <b>Supply voltage:</b> If $V_{PP}$ is in the voltage range of $V_{PPH}$ , the signal acts as an additional power supply for programming operation, as defined in the Operating Conditions table. The $V_{PP}$ pad will be internally pulled up to $V_{CC}$ , so customer can leave $V_{PP}$ pin floated if not used.                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub> | Supply | <b>Ground:</b> Core and I/O ground connection. V <sub>SS</sub> is the reference for the V <sub>CC</sub> supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DNU             | -      | <b>Do not use:</b> Do not connect to any other signal, or power supply; must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RFU             | -      | <b>Reserved for future use:</b> Reserved by Micron for future device functionality and enhancement. Recommend that these should be left floating. May be connected internally, but external connections will not affect operation.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**Table 1: Signal Descriptions (Continued)**

| Symbol | Туре | Description                                                    |

|--------|------|----------------------------------------------------------------|

| NC     | _    | No connect : No internal connection; can be driven or floated. |

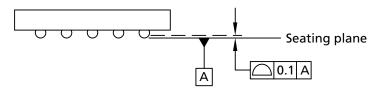

## Package Dimensions - Package Code: 12

Figure 5: 24-Ball T-PBGA (5 × 5 ball grid array) - 6mm × 8mm

Notes: 1. All dimensions are in millimeters.

2. See Part Number Ordering Information for complete package names and details.

### Xccela™ Flash Memory Data Sheet Brief Revision History

# **Revision History**

Rev. A - 04/18

· Initial release

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000 www.micron.com/products/support Sales inquiries: 800-932-4992 Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

This data sheet contains initial characterization limits that are subject to change upon full characterization of production devices.