October 2017

# FOD8316 2.5 A Output Current, IGBT Drive Optocoupler with Desaturation Detection and Isolated Fault Sensing

### Features

- + High Noise Immunity Characterized by Common Mode Rejection 35 kV/µs Minimum,  $V_{CM}$  = 1500  $V_{PEAK}$

- 2.5 A Peak Output Current Driving Capability for Most 1200 V / 150 A IGBTs

- · Optically Isolated Fault Sensing Feedback

- "Soft" IGBT Turn-off

- Built-in IGBT Protection

- Desaturation Detection

- Under-Voltage Lockout (UVLO) Protection

- Wide Supply Voltage Range: 15 V to 30 V

- P-Channel MOSFETs at Output Stage Enables Output Voltage Swing Close to the Supply Rail (Rail-to-Rail Output)

- 3.3 V / 5 V, CMOS/TTL Compatible Inputs

- · High Speed

- 250 ns Maximum Propagation Delay Over Full Operating Temperature Range

- Extended Industrial Temperate Range, -40°C to 100°C

- · Safety and Regulatory Approvals

- UL1577, 4,243 V<sub>RMS</sub> for 1 Minute

- DIN EN/IEC 60747-5-5:

1,414 V<sub>PEAK</sub> Working Insulation Voltage Rating 8,000 V<sub>PEAK</sub> Transient Isolation Voltage Rating

- +  $R_{DS(ON)}$  of 1  $\Omega$  (Typical) Offers Lower Power Dissipation

- User-Configurable: Inverting, Non-inverting, Auto-reset, Auto-shutdown

- 8 mm Creepage and Clearance Distances

### Applications

- Industrial Inverter

- Induction Heating

- Isolated IGBT Drive

### Description

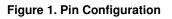

The FOD8316 is an advanced 2.5 A output current IGBT drive optocoupler capable of driving most 1200 V /150 A IGBTs. It is ideally suited for fast-switching driving of power IGBTs and MOSFETs used in motor-control inverter applications and high-performance power systems. The FOD8316 offers critical protection features necessary for preventing fault conditions that lead to destructive thermal runaway of IGBTs.

The device utilizes ON's proprietary Optoplanar<sup>®</sup> coplanar packaging technology, and optimized IC design to achieve high noise immunity, characterized by high common-mode rejection and power supply rejection specifications.

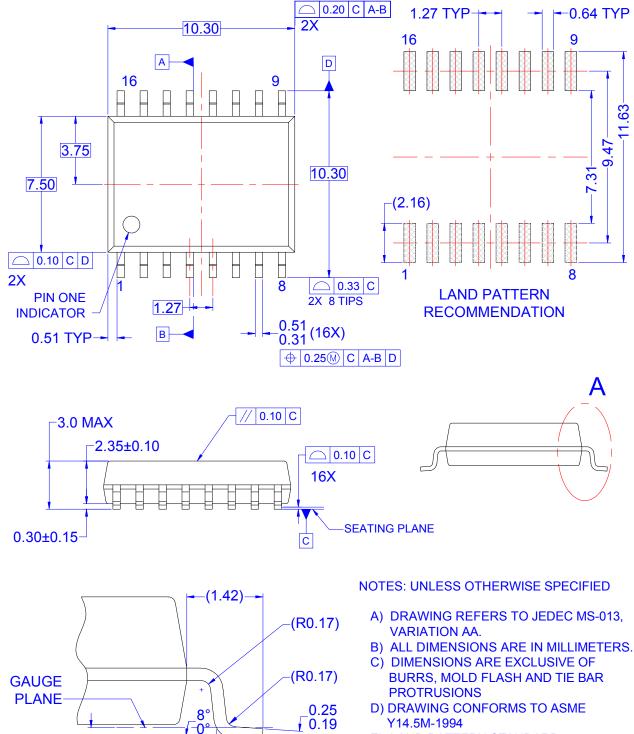

The FOD8316 consists of an integrated gate drive optocoupler featuring low  $R_{DS(ON)}$  CMOS transistors to drive the IGBT from rail-to-rail and an integrated high-speed isolated feedback for fault sensing. The device is housed in a compact 16-pin small-outline plastic package which meets the 8 mm creepage and clearance requirements.

<sup>©</sup> Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

| uth Table        |                  |                                              |                    |       |      |

|------------------|------------------|----------------------------------------------|--------------------|-------|------|

| V <sub>IN+</sub> | V <sub>IN-</sub> | UVLO<br>(V <sub>DD2</sub> – V <sub>E</sub> ) | DESAT<br>Detected? | FAULT | vo   |

| Х                | Х                | Active                                       | Х                  | Х     | LOW  |

| Х                | Х                | Х                                            | Yes                | LOW   | LOW  |

| LOW              | Х                | Х                                            | Х                  | Х     | LOW  |

| Х                | HIGH             | Х                                            | Х                  | Х     | LOW  |

| HIGH             | LOW              | Not Active                                   | No                 | HIGH  | HIGH |

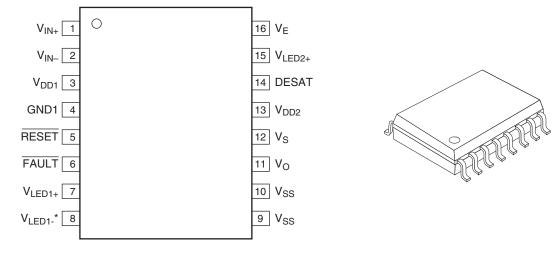

### **Pin Configuration**

### **Pin Definitions**

| Pin # | Name               | Description                                   |  |

|-------|--------------------|-----------------------------------------------|--|

| 1     | V <sub>IN+</sub>   | Non-inverting Gate Drive Control Input        |  |

| 2     | V <sub>IN</sub>    | Inverting Gate-Drive Control Input            |  |

| 3     | V <sub>DD1</sub>   | Positive Input Supply Voltage (3 V to 5.5 V)  |  |

| 4     | GND1               | Input Ground                                  |  |

| 5     | RESET              | FAULT Reset Input                             |  |

| 6     | FAULT              | Fault Output (Open Drain)                     |  |

| 7     | V <sub>LED1+</sub> | LED 1 Anode (Do not connect. Leave floating.) |  |

| 8     | V <sub>LED1-</sub> | LED 1 Cathode (Must be connected to ground.)  |  |

| 9     | V <sub>SS</sub>    | Output Supply Voltage (Negative)              |  |

| 10    | V <sub>SS</sub>    | Output Supply Voltage (Negative)              |  |

| 11    | V <sub>O</sub>     | Gate-Drive Output Voltage                     |  |

| 12    | V <sub>S</sub>     | Pull-up PMOS Transistor Source                |  |

| 13    | V <sub>DD2</sub>   | Positive Output Supply Voltage                |  |

| 14    | DESAT              | Desaturation Voltage Input                    |  |

| 15    | V <sub>LED2+</sub> | LED 2 Anode (Do not connect. Leave floating.) |  |

| 16    | V <sub>E</sub>     | Output Supply Voltage / IGBT Emitter          |  |

### Safety and Insulation Ratings

As per DIN EN/IEC 60747-5-5, this optocoupler is suitable for "safe electrical insulation" only within the safety limit data. Compliance with the safety ratings must be ensured by means of protective circuits.

| Symbol                | Parameter                                                                                                                                             | Min.            | Тур.      | Max. | Unit              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|------|-------------------|

|                       | Installation Classifications per DIN VDE 0110/1.89 Table 1                                                                                            |                 |           |      |                   |

|                       | Rated Mains Voltage < 150 V <sub>RMS</sub>                                                                                                            |                 | I–IV      |      |                   |

|                       | Rated Mains Voltage < 300 V <sub>RMS</sub>                                                                                                            |                 | I–IV      |      |                   |

|                       | Rated Mains Voltage < 450 V <sub>RMS</sub>                                                                                                            |                 | I–IV      |      |                   |

|                       | Rated Mains Voltage < 600 V <sub>RMS</sub>                                                                                                            |                 | I–IV      |      |                   |

|                       | Rated Mains Voltage < 1000 V <sub>RMS</sub>                                                                                                           |                 | I–III     |      |                   |

|                       | Climatic Classification                                                                                                                               |                 | 40/100/21 |      |                   |

|                       | Pollution Degree (DIN VDE 0110/1.89)                                                                                                                  |                 | 2         |      |                   |

| CTI                   | Comparative Tracking Index (DIN IEC 112/VDE 0303 Part 1)                                                                                              | 175             |           |      |                   |

| $V_{PR}$              | Input-to-Output Test Voltage, Method b, $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1$ s, Partial Discharge < 5 pC            | 2651            |           |      | V <sub>peak</sub> |

|                       | Input-to-Output Test Voltage, Method a, $V_{IORM} \times 1.6 = V_{PR}$ ,<br>Type and Sample Test with t <sub>m</sub> = 10 s, Partial Discharge < 5 pC | 2262            |           |      | V <sub>peak</sub> |

| V <sub>IORM</sub>     | Maximum Working Insulation Voltage                                                                                                                    | 1414            |           |      | V <sub>peak</sub> |

| V <sub>IOTM</sub>     | Highest Allowable Over Voltage                                                                                                                        | 8000            |           |      | V <sub>peak</sub> |

|                       | External Creepage                                                                                                                                     | 8.0             |           |      | mm                |

|                       | External Clearance                                                                                                                                    | 8.0             |           |      | mm                |

|                       | Insulation Thickness                                                                                                                                  | 0.5             |           |      | mm                |

|                       | Safety Limit Values – Maximum Values in Failure;                                                                                                      |                 |           |      |                   |

| T <sub>Case</sub>     | Case Temperature                                                                                                                                      | 150             |           |      | °C                |

|                       | Safety Limit Values – Maximum Values in Failure;                                                                                                      |                 |           |      |                   |

| P <sub>S,INPUT</sub>  | Input Power                                                                                                                                           | 100             |           |      | mW                |

| ·                     | Safety Limit Values – Maximum Values in Failure;                                                                                                      |                 |           |      |                   |

| P <sub>S,OUTPUT</sub> | Output Power                                                                                                                                          | 600             |           |      | mW                |

| R <sub>IO</sub>       | Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V                                                                                     | 10 <sup>9</sup> |           |      | Ω                 |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A = 25^{\circ}C$  unless otherwise specified.

| Symbol                                        | Parameter                                             | Value                         | Units |

|-----------------------------------------------|-------------------------------------------------------|-------------------------------|-------|

| T <sub>STG</sub>                              | Storage Temperature                                   | -40 to +125                   | ٥C    |

| T <sub>OPR</sub>                              | Operating Temperature                                 | -40 to +100                   | Ωō    |

| Т <sub>Ј</sub>                                | Junction Temperature                                  | -40 to +125                   | °C    |

| T <sub>SOL</sub>                              | Lead Wave Solder Temperature<br>(no solder immersion) | 260 for 10 seconds            | °C    |

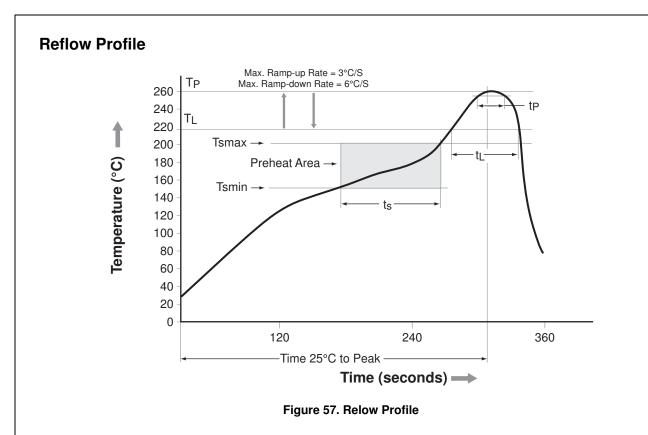

|                                               | Refer to reflow temperature profile on page 27.       |                               |       |

| IFAULT                                        | Fault Output Current                                  | 15                            | mA    |

| I <sub>O(PEAK)</sub>                          | Peak Output Current <sup>(1)</sup>                    | 3                             | А     |

| V <sub>E</sub> -V <sub>SS</sub>               | Negative Output Supply Voltage <sup>(2)</sup>         | 0 to 15                       | V     |

| V <sub>DD2</sub> – V <sub>E</sub>             | Positive Output Supply Voltage                        | -0.5 to $35 - (V_E - V_{SS})$ | V     |

| V <sub>O(peak)</sub>                          | Gate Drive Output Voltage                             | -0.5 to 35                    | V     |

| $V_{DD2} - V_{SS}$                            | Output Supply Voltage                                 | -0.5 to 35                    | V     |

| V <sub>DD1</sub>                              | Positive Input Supply Voltage                         | -0.5 to 6                     | V     |

| $V_{IN+}, V_{IN-}$ and $V_{\overline{RESET}}$ | Input Voltages                                        | -0.5 to V <sub>DD1</sub>      | V     |

| V <sub>FAULT</sub>                            | Fault Pin Voltage                                     | -0.5 to V <sub>DD1</sub>      | V     |

| V <sub>S</sub>                                | Source of Pull-up PMOS Transistor Voltage             | $V_{SS}$ + 6.5 to $V_{DD2}$   | V     |

| V <sub>DESAT</sub>                            | DESAT Voltage                                         | $V_E$ to $V_E$ + 25           | V     |

| PDI                                           | Input Power Dissipation <sup>(3)(5)</sup>             | 100                           | mW    |

| PD <sub>O</sub>                               | Output Power Dissipation <sup>(4)(5)</sup>            | 600                           | mW    |

#### Notes:

- 1. Maximum pulse width = 10  $\mu$ s, maximum duty cycle = 0.2%.

- 2. This negative output supply voltage is optional. It's only needed when negative gate drive is implemented. Refer to "Dual Supply Operation – Negative Bias at Vss" on page 23.

- 3. No derating required across temperature range.

- 4. Derate linearly above 64°C, free air temperature at a rate of 10.2 mW/°C

- 5. Functional operation under these conditions is not implied. Permanent damage may occur if the device is subjected to conditions outside these ratings.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol             | Parameter                                     | Min.                  | Max.                    | Unit |

|--------------------|-----------------------------------------------|-----------------------|-------------------------|------|

| T <sub>A</sub>     | Ambient Operating Temperature                 | -40                   | +100                    | °C   |

| V <sub>DD1</sub>   | Input Supply Voltage <sup>(6)</sup>           | 3                     | 5.5                     | V    |

| $V_{DD2} - V_{SS}$ | Total Output Supply Voltage                   | 15                    | 30                      | V    |

| $V_{E} - V_{SS}$   | Negative Output Supply Voltage                | 0                     | 15                      | V    |

| $V_{DD2} - V_E$    | Positive Output Supply Voltage <sup>(6)</sup> | 15                    | $30 - (V_{E} - V_{SS})$ | V    |

| V <sub>S</sub>     | Source of Pull-up PMOS Transistor Voltage     | V <sub>SS</sub> + 7.5 | V <sub>DD2</sub>        | V    |

Note:

During power up or down, it is important to ensure that V<sub>IN+</sub> remains low until both the input and output supply voltages reaches the proper recommended operating voltages to avoid any momentary instability at the output state. See also the discussion in the "Time to Good Power" section on page 23.

### **Isolation Characteristics**

| Symbol           | Parameter                         | Conditions                                                                                                         | Min.  | Тур.             | Max. | Units            |

|------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|------------------|------|------------------|

| V <sub>ISO</sub> | Input-Output Isolation<br>Voltage | $T_A = 25$ °C, Relative Humidity < 50%,<br>t = 1.0 minute, I <sub>I-O</sub> ≤ 10 μA,<br>50 Hz <sup>(7)(8)(9)</sup> | 4,243 |                  |      | V <sub>RMS</sub> |

| R <sub>ISO</sub> | Isolation Resistance              | $V_{I-O} = 500 V^{(7)}$                                                                                            |       | 10 <sup>11</sup> |      | Ω                |

| C <sub>ISO</sub> | Isolation Capacitance             | V <sub>I-O</sub> = 0 V, Freq = 1.0 MHz <sup>(7)</sup>                                                              |       | 1                |      | pF               |

Apply over all recommended conditions, typical value is measured at T<sub>A</sub> = 25°C

#### Notes:

- 7. Device is considered a two terminal device: pins 1 to 8 are shorted together and pins 9 to 16 are shorted together.

- 8. 4,243 VRMS for 1-minute duration is equivalent to 5,091 VRMS for 1-second duration.

- The input-output isolation voltage is a dielectric voltage rating as per UL1577. It should not be regarded as an input-output continuous voltage rating. For the continuous working voltage rating refer to your equipment-level safety specification or DIN EN/IEC 60747-5-5 Safety and Insulation Ratings Table.

### **Electrical Characteristics**

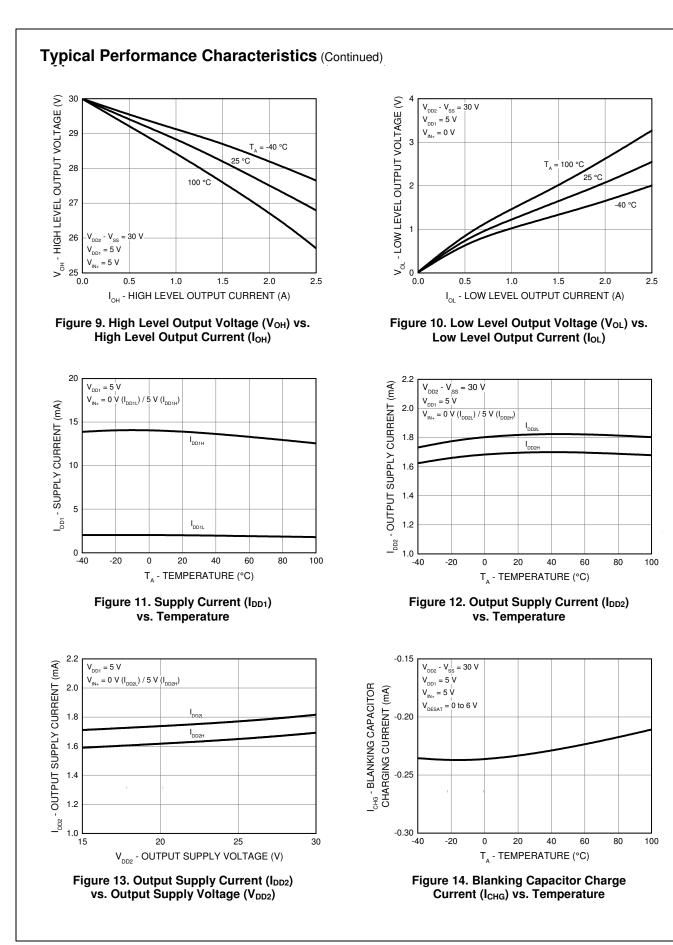

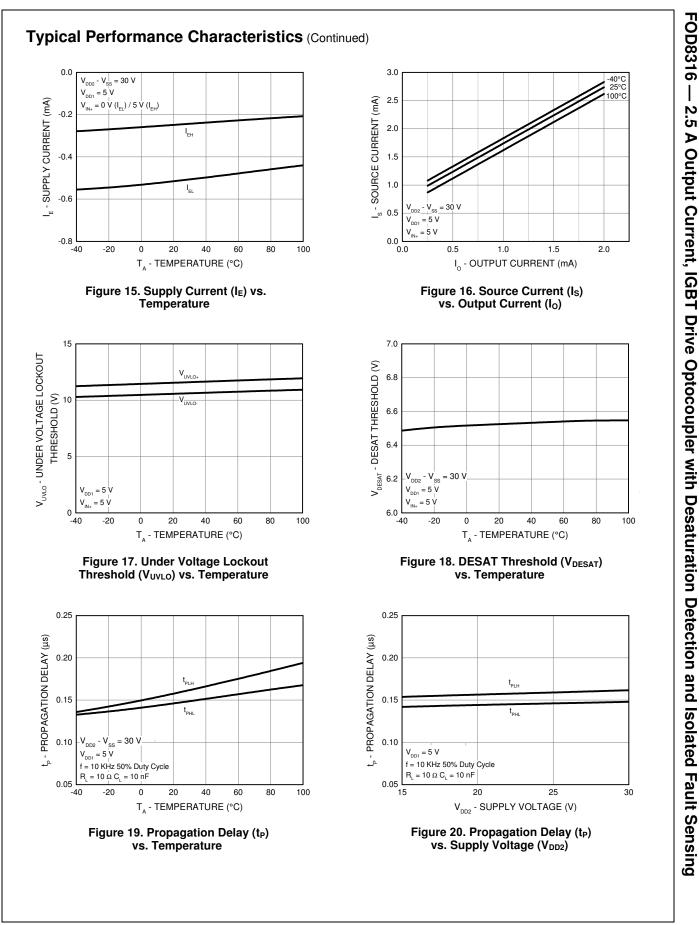

Apply over all recommended conditions, typical value is measured at  $V_{DD1} = 5V$ ,  $V_{DD2} - V_{SS} = 30V$ ,  $V_E - V_{SS} = 0V$ , and  $T_A = 25^{\circ}C$ ; unless otherwise specified.

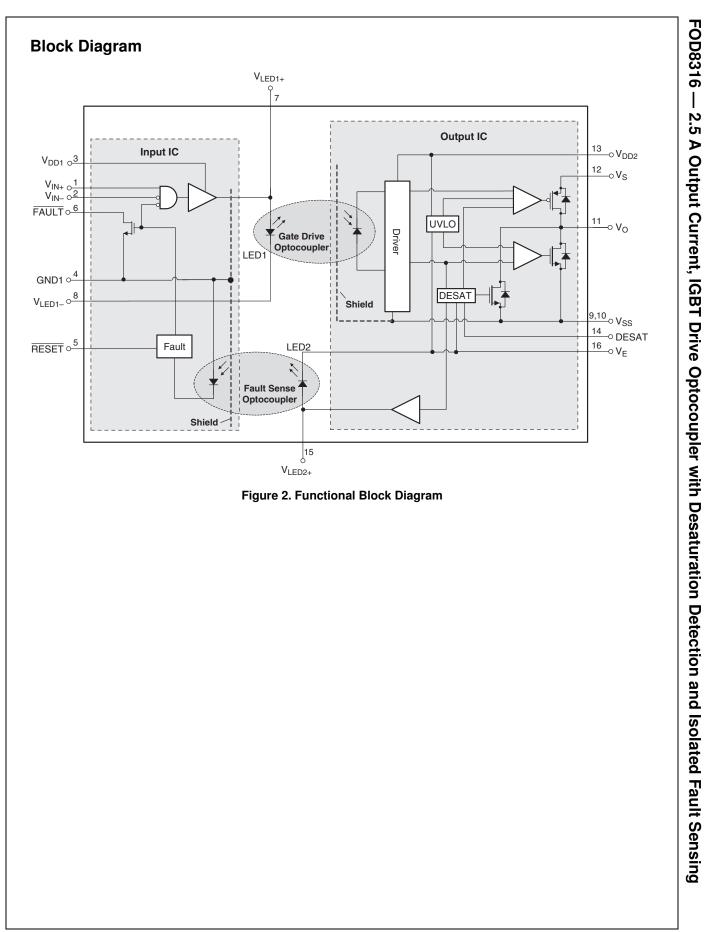

| Symbol                                                                                           | Parameter                                          | Conditions                                                             | Min.                   | Тур.              | Max.  | Units | Figure       |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------|-------------------|-------|-------|--------------|

| V <sub>IN+L</sub> , V <sub>IN-L</sub> ,<br>V <sub>RESETL</sub>                                   | Logic Low Input Voltages                           |                                                                        |                        |                   | 0.8   | V     |              |

| $\begin{array}{c} V_{\text{IN+H}}, V_{\text{IN-H}}, \\ V_{\overline{\text{RESETH}}} \end{array}$ | Logic High Input Voltages                          |                                                                        | 2.0                    |                   |       | V     |              |

| I <sub>IN+L</sub> , I <sub>IN-L</sub> ,<br>I <u>resetl</u>                                       | Logic Low Input Currents                           | V <sub>IN</sub> = 0.4 V                                                | -0.5                   | -0.001            |       | mA    |              |

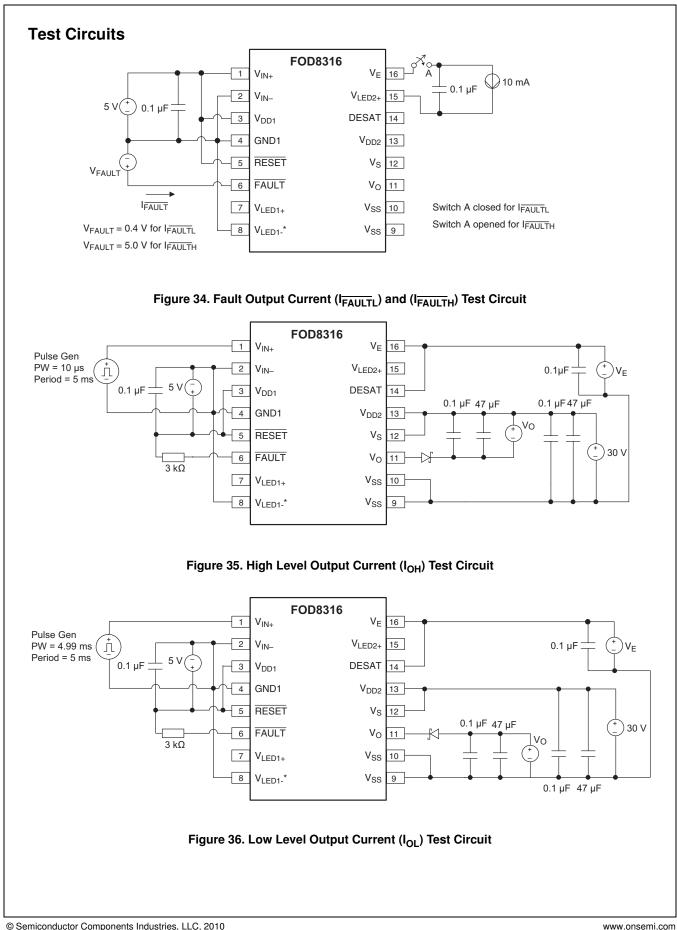

| IFAULTL                                                                                          | FAULT Logic Low Output Current                     | V <sub>FAULT</sub> = 0.4 V                                             | 5.0                    | 12.0              |       | mA    | 3, 34        |

| I <sub>FAULTH</sub>                                                                              | FAULT Logic High Output Current                    | V <sub>FAULT</sub> = V <sub>DD1</sub>                                  | -40                    | 0.002             |       | μA    | 34           |

| I <sub>OH</sub>                                                                                  | High Level Output Current                          | $V_{O} = V_{DD2} - 3 V$                                                | -1                     | -2.5              |       | А     | 4, 9, 35     |

|                                                                                                  |                                                    | $V_{\rm O} = V_{\rm DD2} - 6 \ V^{(10)}$                               | -2.5                   |                   |       | А     |              |

| I <sub>OL</sub>                                                                                  | Low Level Output Current                           | $V_O = V_{SS} + 3 V$                                                   | 1                      | 3                 |       | А     | 5, 36        |

|                                                                                                  |                                                    | $V_{O} = V_{SS} + 6 V^{(11)}$                                          | 2.5                    |                   |       | А     |              |

| I <sub>OLF</sub>                                                                                 | Low Level Output Current During<br>Fault Condition | V <sub>O</sub> – V <sub>SS</sub> = 14 V                                | 70                     | 125               | 170   | mA    | 6, 40        |

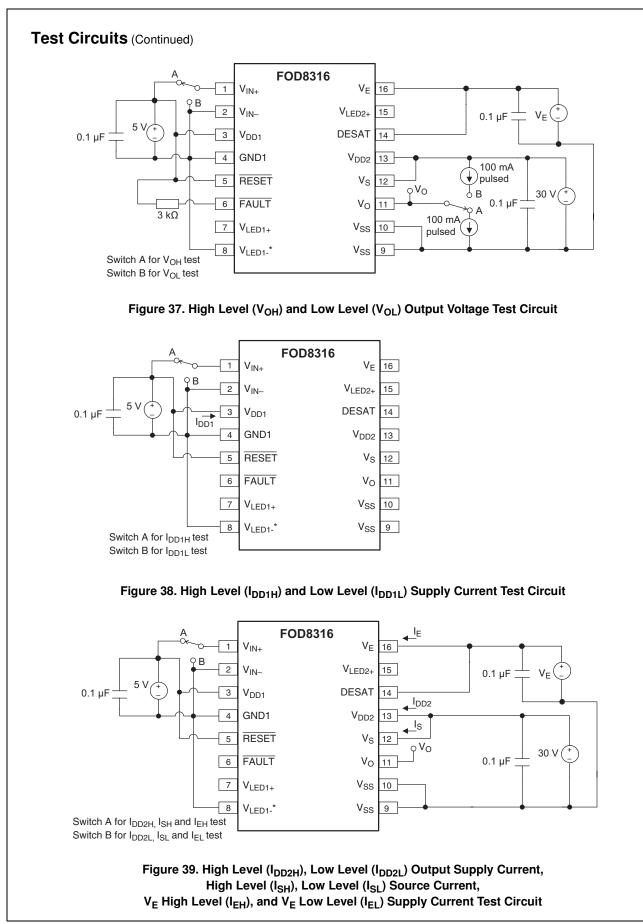

| V <sub>OH</sub>                                                                                  | High Level Output Voltage                          | $I_{\rm O} = -100 \text{ mA}^{(12)(13)(14)}$                           | V <sub>S</sub> – 1.0 V | $V_{\rm S}-0.5~V$ |       | V     | 7, 9, 37     |

| V <sub>OL</sub>                                                                                  | Low Level Output Voltage                           | l <sub>O</sub> = 100 mA                                                |                        | 0.1               | 0.5   | V     | 8, 10,<br>37 |

| I <sub>DD1H</sub>                                                                                | High Level Supply Current                          | $V_{IN+} = V_{DD1} = 5.5 V,$<br>$V_{IN-} = 0 V$                        |                        | 14                | 17    | mA    | 11, 38       |

| I <sub>DD1L</sub>                                                                                | Low Level Supply Current                           | V <sub>IN+</sub> = V <sub>IN-</sub> = 0 V,<br>V <sub>DD1</sub> = 5.5 V |                        | 2                 | 3     | mA    |              |

| I <sub>DD2H</sub>                                                                                | High Level Output Supply Current                   | V <sub>O</sub> = Open <sup>(14)</sup>                                  |                        | 1.7               | 3     | mA    | 12, 13,      |

| I <sub>DD2L</sub>                                                                                | Low Level Output Supply Current                    | V <sub>O</sub> = Open                                                  |                        | 1.8               | 2.8   | mA    | 39           |

| I <sub>SH</sub>                                                                                  | High Level Source Current                          | I <sub>O</sub> = 0 mA                                                  |                        | 0.65              | 1.5   | mA    | 39           |

| I <sub>SL</sub>                                                                                  | Low Level Source Current                           | I <sub>O</sub> = 0 mA                                                  |                        | 0.6               | 1.4   | mA    | 39           |

| I <sub>EL</sub>                                                                                  | V <sub>E</sub> Low Level Supply Current            |                                                                        | -0.8                   | -0.5              |       | mA    | 15, 39       |

| I <sub>EH</sub>                                                                                  | V <sub>E</sub> High Level Supply Current           |                                                                        | -0.5                   | -0.25             |       | mA    | 1            |

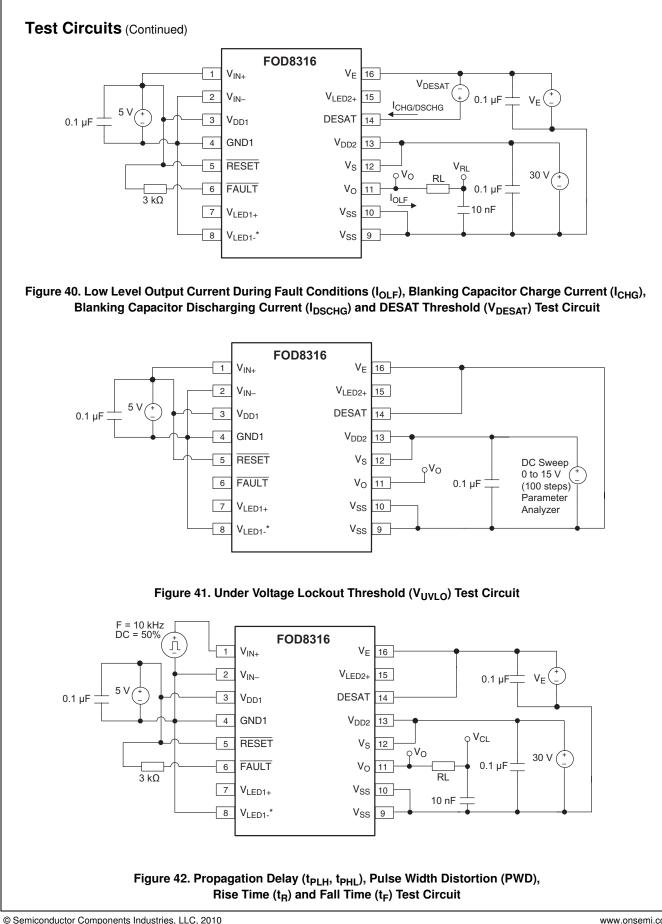

| I <sub>CHG</sub>                                                                                 | Blanking Capacitor Charge<br>Current               | $V_{\text{DESAT}} = 2 V^{(14)(15)}$                                    | -0.13                  | -0.25             | -0.33 | mA    | 14, 40       |

© Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

### Electrical Characteristics (Continued)

Apply over all recommended conditions, typical value is measured at  $V_{DD1} = 5 V$ ,  $V_{DD2} - V_{SS} = 30 V$ ,  $V_E - V_{SS} = 0V$ , and  $T_A = 25^{\circ}C$ ; unless otherwise specified.

| Symbol              | Parameter                                     | Conditions                                | Min. | Тур. | Max. | Units | Figure  |

|---------------------|-----------------------------------------------|-------------------------------------------|------|------|------|-------|---------|

| I <sub>DSCHG</sub>  | Blanking Capacitor<br>Discharge Current       | V <sub>DESAT</sub> = 7 V                  | 10   | 36   |      | mA    | 40      |

| V <sub>UVLO+</sub>  | Under Voltage Lockout                         | V <sub>O</sub> > 5 V @ 25°C               | 10.8 | 11.7 | 12.7 | V     | 17, 31, |

| V <sub>UVLO-</sub>  | Threshold <sup>(14)</sup>                     | V <sub>O</sub> < 5 V @ 25°C               | 9.8  | 10.7 | 11.7 | V     | 41      |

| UVLO <sub>HYS</sub> | Under Voltage Lockout<br>Threshold Hysteresis | @ 25°C                                    | 0.4  | 1.0  |      | V     |         |

| V <sub>DESAT</sub>  | DESAT Threshold <sup>(14)</sup>               | $V_{DD2} - V_E > V_{ULVO-}, \\ V_O < 5 V$ | 6.0  | 6.5  | 7.2  | V     | 18, 40  |

Notes:

10. Maximum pulse width = 10  $\mu$ s, maximum duty cycle = 0.2%.

11. Maximum pulse width = 4.99 ms, maximum duty cycle = 99.8%.

12. V<sub>OH</sub> is measured with the DC load current in this testing (Maximum pulse width = 1 ms, maximum duty cycle = 20%).When driving capacitive loads, V<sub>OH</sub> will approach V<sub>DD</sub> as I<sub>OH</sub> approaches zero units.

- Positive output supply voltage (V<sub>DD2</sub> V<sub>E</sub>) should be at least 15 V to ensure adequate margin in excess of the maximum under-voltage lockout threshold, V<sub>UVLO+</sub>, of 13.5 V.

- 14. When V<sub>DD2</sub> V<sub>E</sub> > V<sub>UVLO</sub> and output state V<sub>O</sub> is allowed to go high, the DESAT detection feature is active and provides the primary source of IGBT protection. UVLO is needed to ensure DESAT detection is functional.

- 15. The blanking time,  $t_{BLANK}$ , is adjustable by an external capacitor ( $C_{BLANK}$ ), where  $t_{BLANK} = C_{BLANK} \times (V_{DESAT} / I_{CHG})$ .

#### **Switching Characteristics**

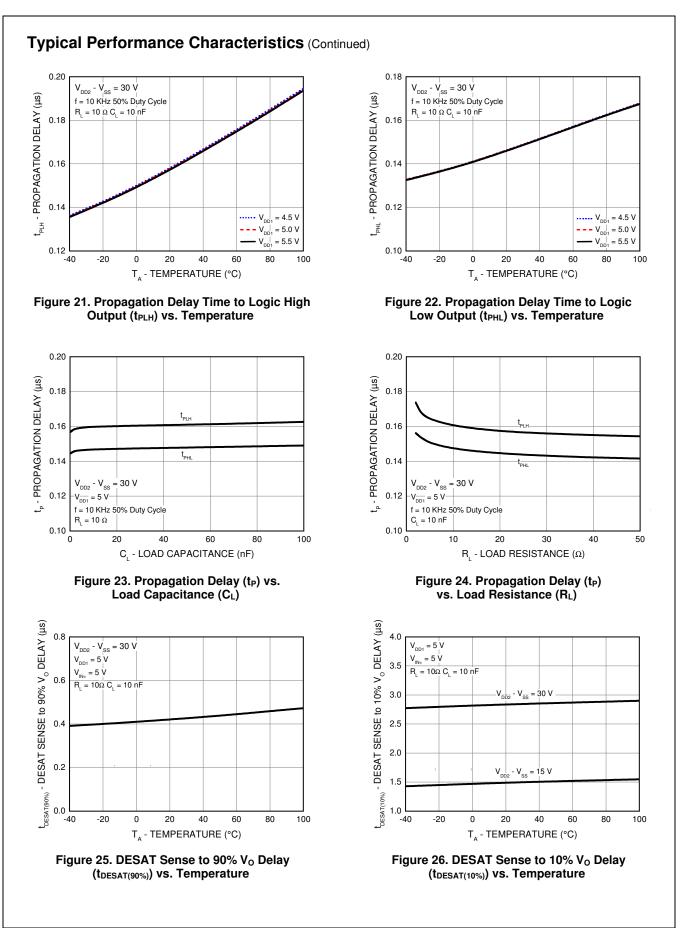

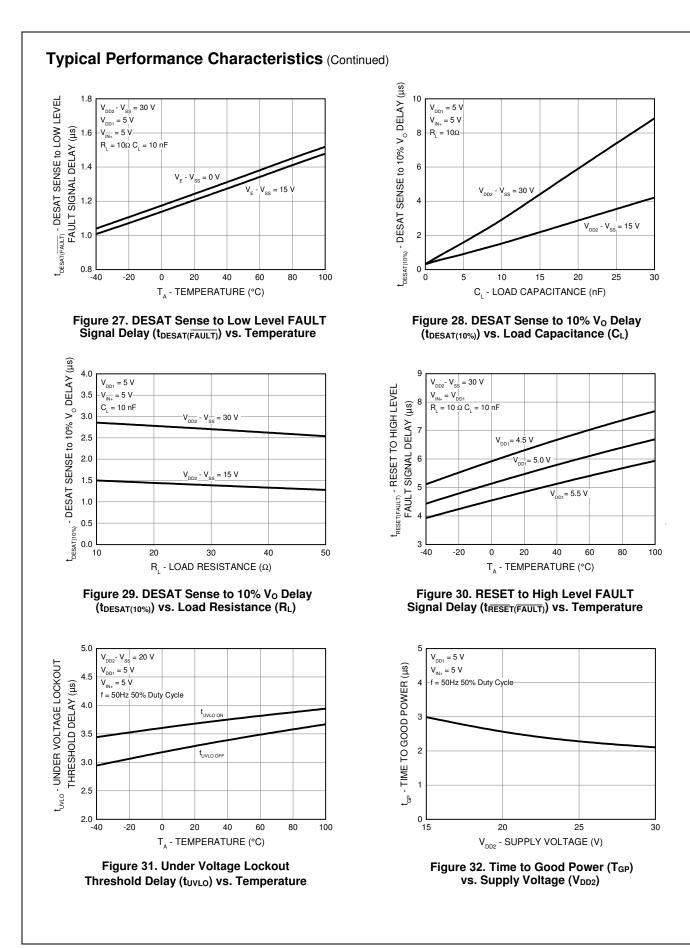

Apply over all recommended conditions, typical value is measured at  $V_{DD1} = 5 \text{ V}$ ,  $V_{DD2} - V_{SS} = 30 \text{ V}$ ,  $V_E - V_{SS} = 0 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ ; unless otherwise specified.

| Symbol                     | Parameter                                                                                                     | Conditions                                | Min. | Тур. | Max. | Units | Figure            |

|----------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|------|------|-------|-------------------|

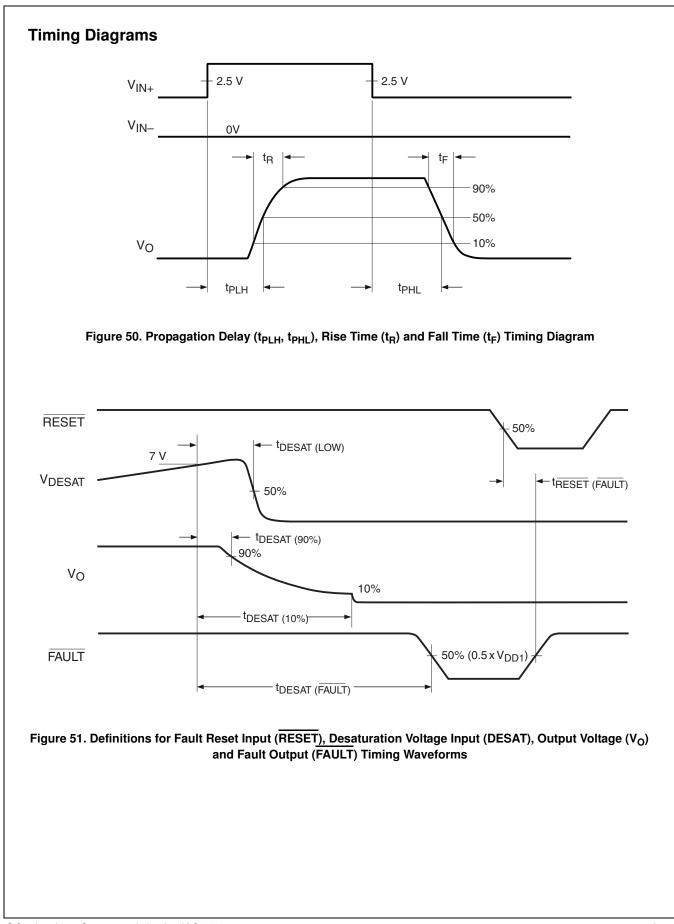

| t <sub>PHL</sub>           | Propagation Delay Time to<br>Logic Low Output <sup>(17)</sup>                                                 | Rg = 10 Ω, Cg = 10nF,<br>f = 10 kHz, (10) |      | 140  | 250  | ns    | 19,20,<br>21,22,  |

| t <sub>PLH</sub>           | Propagation Delay Time to<br>Logic High Output <sup>(18)</sup>                                                | Duty Cycle = 50% <sup>(16)</sup>          |      | 160  | 250  | ns    | 23, 24,<br>42, 50 |

| PWD                        | Pulse Width Distortion,<br>  t <sub>PHL</sub> – t <sub>PLH</sub>   <sup>(19)</sup>                            |                                           |      | 20   | 100  | ns    |                   |

| PDD Skew                   | Propagation Delay Difference<br>Between Any Two Parts or<br>Channels, ( $t_{PHL} - t_{PLH}$ ) <sup>(20)</sup> |                                           | -150 |      | 150  | ns    |                   |

| t <sub>R</sub>             | Output Rise Time (10% to 90%)                                                                                 |                                           |      | 25   |      | ns    | 42, 50            |

| t <sub>F</sub>             | Output Fall Time (90% to 10%)                                                                                 |                                           |      | 25   |      | ns    |                   |

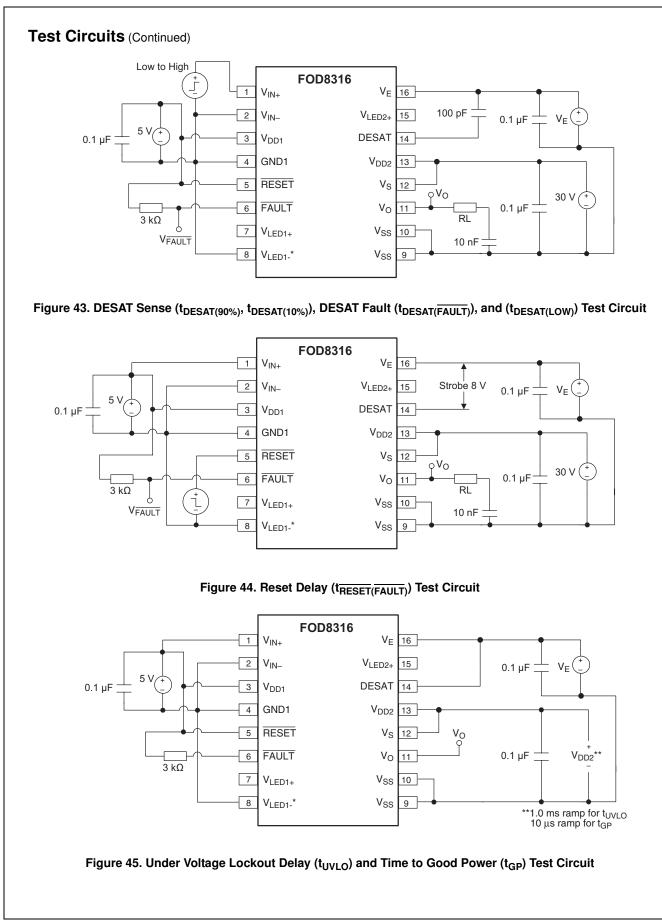

| t <sub>DESAT(90%)</sub>    | DESAT Sense to 90% V <sub>O</sub> Delay <sup>(21)</sup>                                                       | $Rg = 10 \Omega$ , $Cg = 10 nF$ ,         |      | 450  | 700  | ns    | 25, 43            |

| t <sub>DESAT(10%)</sub>    | DESAT Sense to 10% V <sub>O</sub> Delay <sup>(21)</sup>                                                       | V <sub>DD2</sub> – V <sub>SS</sub> = 30 V |      | 2.7  | 4    | μs    | 26, 28,<br>29, 43 |

| t <sub>DESAT</sub> (FAULT) | DESAT Sense to Low Level FAULT<br>Signal Delay <sup>(22)</sup>                                                |                                           |      | 1.4  | 5    | μs    | 27, 43,<br>51     |

| t <sub>DESAT(LOW)</sub>    | DESAT Sense to DESAT Low<br>Propagation Delay <sup>(23)</sup>                                                 |                                           |      | 250  |      | ns    | 43                |

| tRESET(FAULT)              | RESET to High Level FAULT Signal Delay <sup>(24)</sup>                                                        |                                           | 3    | 6    | 20   | μs    | 30, 44,<br>51     |

| t <sub>DESAT(MUTE)</sub>   | DESAT Input Mute                                                                                              | ]                                         | 10   | 22   | 35   | μs    |                   |

| PWRESET                    | RESET Signal Pulse Width                                                                                      | 1                                         | 1.2  |      |      | μs    |                   |

© Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

### Switching Characteristics (Continued)

Apply over all recommended conditions, typical value is measured at  $V_{DD1} = 5 \text{ V}$ ,  $V_{DD2} - V_{SS} = 30 \text{ V}$ ,  $V_E - V_{SS} = 0 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ ; unless otherwise specified.

| Symbol                | Parameter                                        | Conditions                                                                                                                           | Min. | Тур. | Max. | Units | Figure        |

|-----------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|---------------|

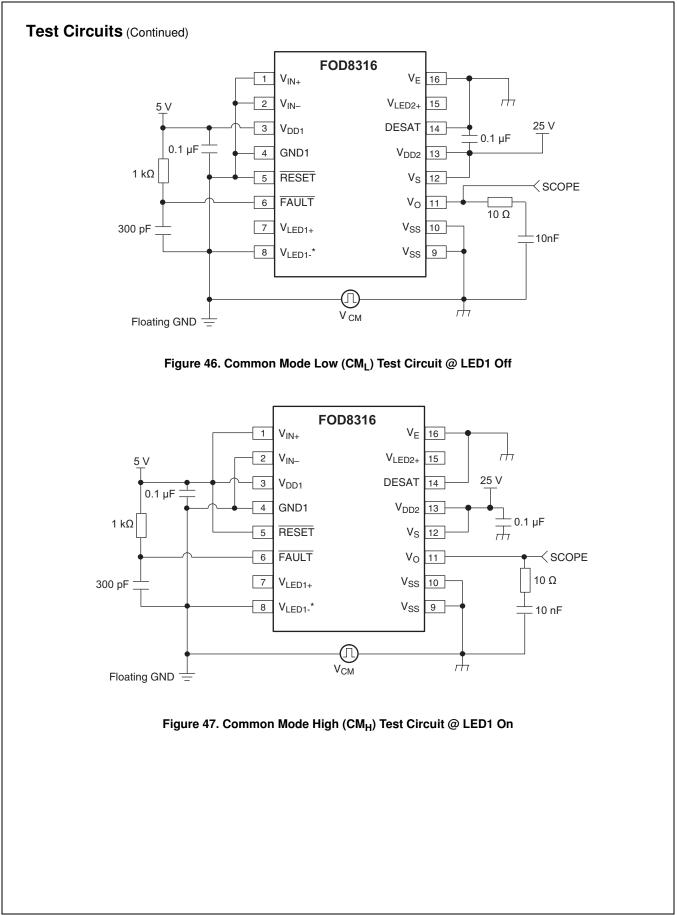

| t <sub>UVLO ON</sub>  | UVLO Turn On Delay <sup>(25)</sup>               | V <sub>DD2</sub> = 20V in                                                                                                            |      | 4    |      | μs    | 31, 45        |

| t <sub>UVLO OFF</sub> | UVLO Turn Off Delay <sup>(26)</sup>              | 1.0ms Ramp                                                                                                                           |      | 3    |      | μs    |               |

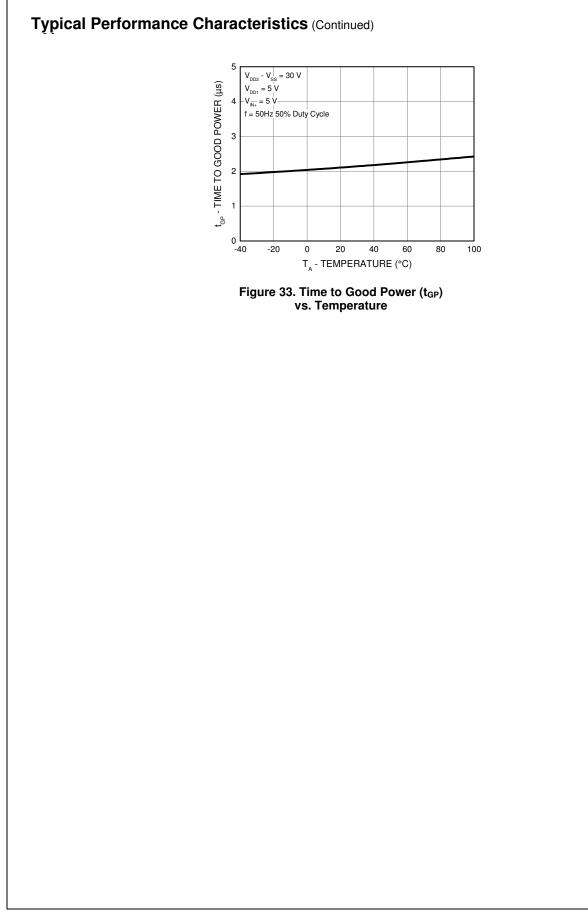

| t <sub>GP</sub>       | Time to Good Power <sup>(27)</sup>               | V <sub>DD2</sub> = 0 to 30V in<br>10µs Ramp                                                                                          |      | 2.5  |      | μs    | 32, 33,<br>45 |

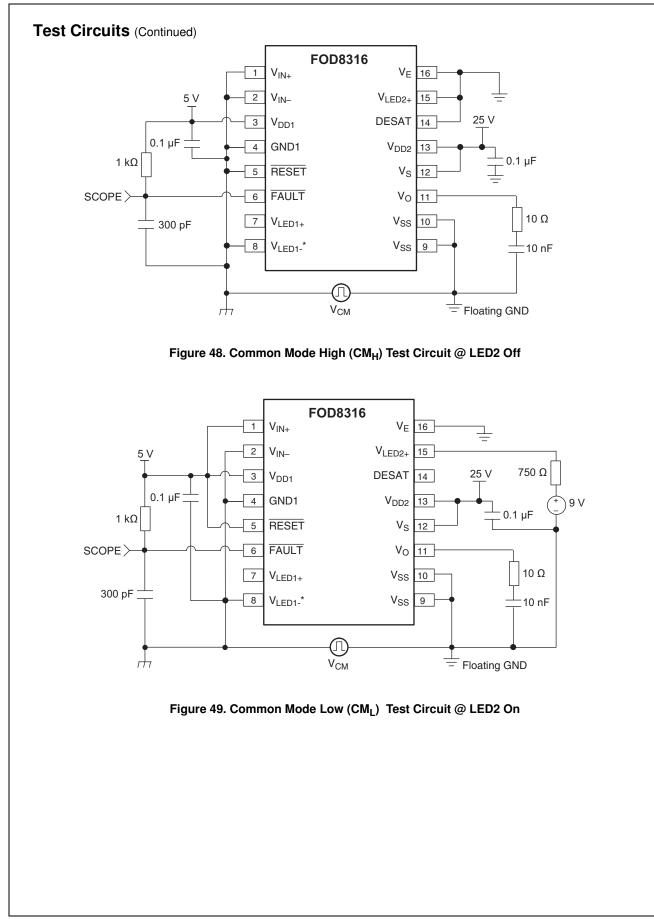

| CM <sub>H</sub>       | Common Mode Transient<br>Immunity at Output High | $\begin{array}{l} T_{A}=25^{\circ}C, \ V_{DD1}=5V, \\ V_{DD2}=25V, \\ V_{SS}=Ground, \\ V_{CM}=1500Vpk^{(28)} \end{array}$           | 35   | 50   |      | kV/μs | 47, 48        |

| CM <sub>L</sub>       | Common Mode Transient<br>Immunity at Output Low  | $\begin{array}{l} T_{A} = 25^{\circ}C, \ V_{DD1} = 5V, \\ V_{DD2} = 25V, \\ V_{SS} = Ground, \\ V_{CM} = 1500Vpk^{(29)} \end{array}$ | 35   | 50   |      | kV/μs | 46, 49        |

#### Notes:

- 16. This load condition approximates the gate load of a 1200 V / 150 A IGBT.

- 17. Propagation delay  $t_{PHL}$  is measured from the 50% level on the falling edge of the input pulse ( $V_{IN+}$ ,  $V_{IN-}$ ) to the 50% level of the falling edge of the  $V_O$  signal. Refer to Figure 50.

- 18. Propagation delay  $t_{PLH}$  is measured from the 50% level on the rising edge of the input pulse ( $V_{IN+}, V_{IN-}$ ) to the 50% level of the rising edge of the  $V_O$  signal. Refer to Figure 50.

- 19. PWD is defined as | t<sub>PHL</sub> t<sub>PLH</sub> | for any given device.

- 20. The difference between t<sub>PHL</sub> and t<sub>PLH</sub> between any two FOD8316 parts under same operating conditions with equal loads.

- 21. This is the amount of time the DESAT threshold must be exceeded before V<sub>O</sub> begins to go LOW. This is supply voltage dependent. See Figure 51.

- 22. This is the amount of time from when the DESAT threshold is exceeded, until the FAULT output goes LOW. See Figure 51.

- 23. The length of time the DESAT threshold must be exceeded before V<sub>O</sub> begins to go LOW, and the FAULT output begins to go LOW. See Figure 51.

- 24. The length of time from when RESET is asserted LOW, until FAULT output goes HIGH. See Figure 51.

- 25. The UVLO turn-on delay, t<sub>UVLO ON</sub>, is measured from V<sub>UVLO+</sub> threshold voltage of the output supply voltage (V<sub>DD2</sub>) to the 5 V level of the rising edge of the V<sub>O</sub> signal.

- The UVLO turn-off delay, t<sub>UVLO OFF</sub>, is measured from V<sub>UVLO</sub> threshold voltage of the output supply voltage (V<sub>DD2</sub>) to the 5 V level of the falling edge of the V<sub>O</sub> signal.

- 27. The time to good power,  $t_{GP}$ , is measured from 13.5 V level of the rising edge of the output supply voltage ( $V_{DD2}$ ) to the 5 V level of the rising edge of the  $V_O$  signal.

- Common-mode transient immunity at output HIGH state is the maximum tolerable negative dVCM/dt on the trailing edge of the common-mode pulse, V<sub>CM</sub>, to assure the output will remain in HIGH state (i.e., V<sub>O</sub> > 15 V or FAULT > 2 V).

- 29.Common-mode transient immunity at output LOW state is the maximum positive tolerable dVCM/dt on the leading edge of the common-mode pulse,  $V_{CM}$ , to assure the output will remain in LOW state (i.e.,  $V_O < 1.0$  V or FAULT < 0.8 V).

@ Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

$\circledast$  Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

0 Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

FOD8316 Rev. 2

FOD8316 Rev. 2

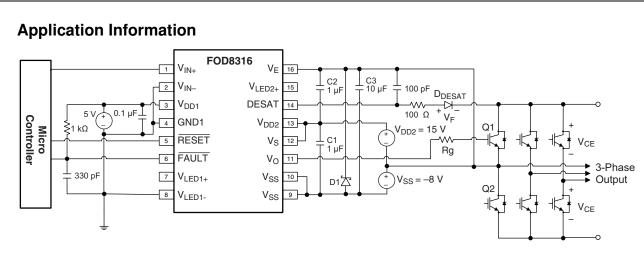

Figure 52. Recommended Application Circuit

#### **Functional Description**

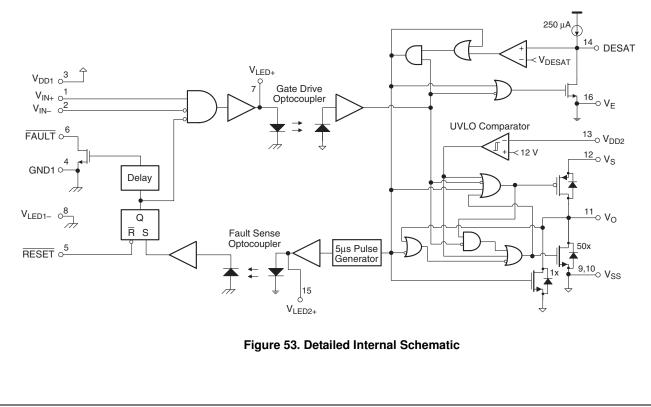

The typical application circuit is shown in Figure 52 and the functional behavioral of the FOD8316 is illustrated by the detailed internal schematic shown in Figure 53. This helps explain the interaction and sequence of internal and external signals, together with the timing diagrams.

#### 1. Non-Inverting and Inverting Inputs

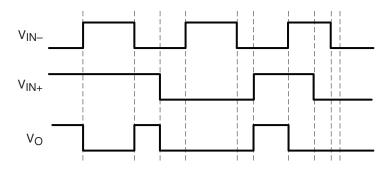

There are two CMOS/TTL compatible inputs,  $V_{IN+}$  and  $V_{IN-}$  to control the IGBT, in non-inverting and inverting configurations respectively. When  $V_{IN-}$  is set to LOW,  $V_{IN+}$  controls the driver output,  $V_O$ , in non-inverting configuration. When  $V_{IN+}$  is set to HIGH,  $V_{IN-}$  controls the driver output in inverting configuration.

The relationship between the inputs and output are illustrated in the Figure 54.

During normal operation, when no fault is detected, the FAULT output, which is an open-drain configuration, will be latched to HIGH state. This allows the gate driver to be controlled by the input logic signal.

When a fault is detected, the FAULT output will be latched to LOW state. This condition will remain until the RESET pin is also pulled low for a period longer than PW<sub>RESET</sub>. While setting the RESET pin to a low state, the input pins must be pulled to low to ensure an output state (V<sub>IN+</sub> is low or V<sub>IN-</sub> is HIGH).

© Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

#### 2. Gate Driver Output

A pair of PMOS and NMOS transistors made up the output driver stage, which facilitates close to rail-to-rail output swing. This feature allows a tight control of gate voltage during on-state and short circuit condition. The output driver is typically capable of sinking 2 A and sourcing 2 A at room temperature. Due to the low  $RDS_{(ON)}$  of the MOSFETs, the power dissipation is reduced as compared to those bipolar-type driver output stages. The absolute maximum rating of the output peak current,  $I_{O(PEAK)}$  is 3 A, thus the careful selection of the gate resistor, Rg, is required to limit the short circuit current of the IGBT.

As shown in Figure 53, the gate driver output is influenced by signals from the photodetector circuitry, the UVLO comparator, and the DESAT signals. Under no fault condition, normal operation resumes while the supply voltage is above the UVLO threshold, the output of the photodetector will drive the MOSFETs of the output stage.

The logic circuitry of the output stage will ensure that the push-pull devices will never be turned "ON" simultaneously. When the output of the photodetector is HIGH, the output,  $V_O$  will be pulled to HIGH state by turning on the PMOS. When the output of the photodetector is LOW,  $V_O$  will be pulled to LOW state by turning on the NMOS.

When  $V_{DD2}$  supply goes below  $V_{UVLO}$ , which is the designated ULVO threshold at the comparator,  $V_O$  will be pulled down to LOW state regardless of photo-detector output.

When desaturation is detected,  $V_O$  will turn off slowly as it is pulled low by the 1XNMOS device, the input to the Fault Sense circuitry will be latched to HIGH state and turns on the LED. When  $V_O$  goes below 2 V, the 50XNMOS device turns on again, clamping the IGBT gate firmly to  $V_{SS}$ . The Fault Sense signal will remain latched in the HIGH state until the LED of the gate driver circuitry turns off.

#### 3. Desaturation Protection, FAULT Output

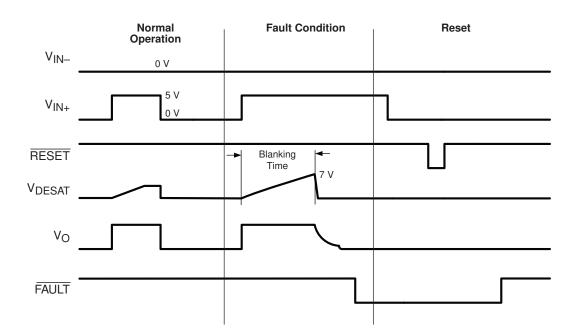

Desaturation detection protection ensures the protection of the IGBT at short circuit by monitoring the collectoremitter voltage of the IGBT in the half bridge. When the DESAT voltage goes up and reaches above the threshold voltage, a short circuit condition is detected and the driver output stage will execute a "soft" IGBT turn-off and will be eventually driven low. This sequence is illustrated in Figure 55. The FAULT open-drain output is triggered active low to report a desaturation error. It could only be cleared by activating active low by the external controller to the RESET input.

The DESAT fault detector should be disabled for a short time period (blanking time) before the IGBT turns on to allow the collector voltage to fall below DESAT threshold. This blanking period protects against false trigger of the DESAT while the IGBT is turning on.

#### 4. "Soft" Turn-Off

The soft turn-off feature ensures the safe turn off of the IGBT under fault condition. This reduces the voltage spike on the collector of the IGBT. Without this, the IGBT would see a heavy spike on the collector, resulting in a permanent damage to the device when it's turned off immediately.

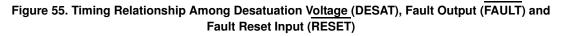

#### 5. Under Voltage Lockout (UVLO)

Under voltage detection prevents the application of insufficient gate voltage to the IGBT. This could be dangerous, as it would drive the IGBT out of saturation and into the linear operation where the losses are very high and quickly overheats. This feature ensures proper operating of the IGBTs. The output voltage, V<sub>O</sub>, remains LOW irregardless of the inputs, as long as the supply voltage, V<sub>DD2</sub> - V<sub>E</sub>, is less than V<sub>ULVO+</sub>. When the supply voltage falls below V<sub>ULVO-</sub>, V<sub>O</sub> goes LOW, as illustrated in Figure 56.

#### 6. Time to Good Power

At initial power up, the LED is off and the output of the gate driver should be in the LOW or OFF state. Sometimes race conditions exist that cause the output to follow  $V_D$  (assuming  $V_{DD2}$  and  $V_E$  are connected externally), until all of the circuits in the output IC have stabilized. This condition can result in output transitions or transients that are coupled to the driven IGBT. These transients can cause the high- and low-side IGBTs to conduct shoot-through current that can damage power semiconductor devices.

ON has introduced an initial turn-on delay, called "time to good power". This delay, typically 2.5  $\mu$ s, is only present during the initial power-up of the device. Once powered, the "time to good power" delay is determined by the delay of the UVLO circuitry. If the LED is ON during the initial turn-on activation, low-to-high transition at the output of the gate driver will only occur 2.5  $\mu$ s after the V<sub>DD2</sub> power is applied.

#### 7. Dual Supply Operation – Negative Bias at V<sub>SS</sub>

The IGBT's off-state noise immunity can be enhanced by providing a negative gate-to-emitter bias when the IGBT is in the OFF state. This static off-state bias can be supplied by connecting a separate negative voltage source between the V<sub>E</sub> (pin 16) and V<sub>SS</sub> (pin 9 &10). Figure 53 illustrates the two distinct grounds. The primary ground reference is the IGBT's emitter connection. V<sub>E</sub> (pin 16). The under-voltage threshold and desaturation voltage detection are referenced to the IGBT's emitter (V<sub>E</sub>) ground.

The recommended application circuit, Figure 52, shows the interconnection of the  $V_{DD2}$  and  $V_E$  supplies. The IGBT's gate to emitter voltage is the absolute value sum of the  $V_{DD2}$  supply and the  $V_{SS}$  reverse bias. The negative voltage supply at  $V_{SS}$  appears at the gate drive input,  $V_O$ , when the FOD8316 is in the LOW state. When the input drives the output high, the output voltage,  $V_O$ , will have the potential of the  $V_{DD2}$  and  $V_{SS}$ .

© Semiconductor Components Industries, LLC, 2010 FOD8316 Rev. 2

Figure 52 shows the operation with a dual or split power supply. The Vss supply provides the negative gate bias, and  $V_{DD2} + V_{SS}$  supplies power to the output IC. The  $V_{SS}$  and  $V_{DD2}$  supplies require three power supply bypass capacitors. These capacitors provide the low equivalent series resistant (ESR) paths for the instantaneous gate charging and discharging currents. Selecting capacitors with low ESR will optimize the

available output current. C3 is a low ESR 1812 style, 10  $\mu$ F, multilayer ceramic capacitor. This capacitor is the primary filter for the Vss and V<sub>DD2</sub> supplies. C1 and C2 are also low ESR capacitors. They provide the primary gate charge and discharge paths. The Schottky diode, D1, is connected between V<sub>E</sub> and V<sub>SS</sub> to protect against a reverse voltage greater than 0.5 V.

### **Ordering Information**

| Part Number | Package                                | Packing Method                     |

|-------------|----------------------------------------|------------------------------------|

| FOD8316     | SO 16-Pin                              | Tube (50 units per tube)           |

| FOD8316R2   | SO 16-Pin                              | Tape and Reel (750 units per reel) |

| FOD8316V    | SO 16-Pin, DIN EN/IEC 60747-5-5 option | Tube (50 units per tube)           |

| FOD8316R2V  | SO 16-Pin, DIN EN/IEC 60747-5-5 option | Tape and reel (750 units per reel) |

All packages are lead free per JEDEC: J-STD-020B standard.

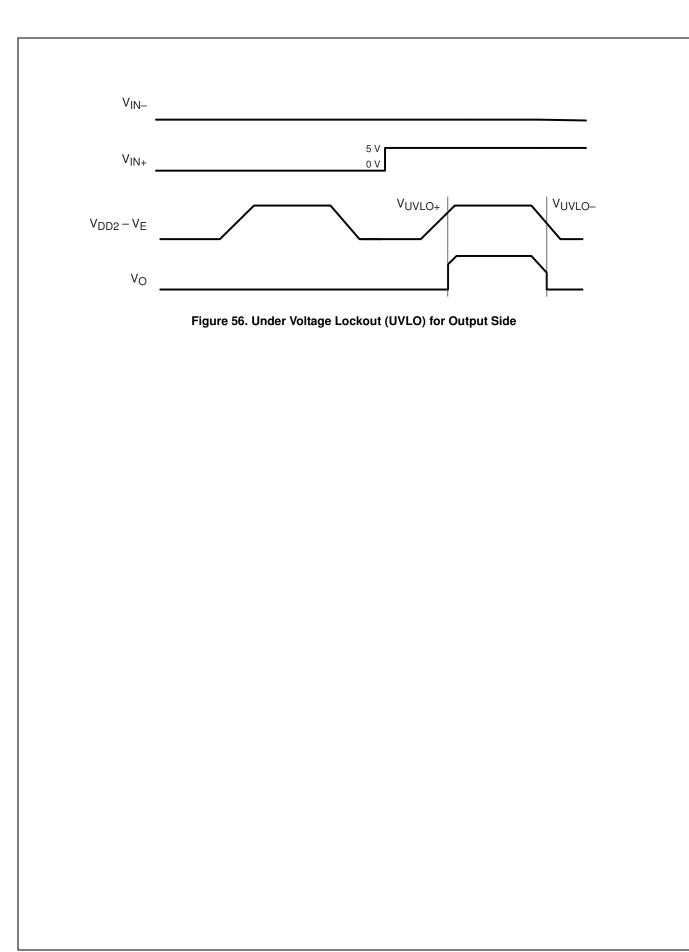

## **Marking Information**

| Defini | Definitions                                                                        |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------|--|--|--|--|--|

| 1      | Company logo                                                                       |  |  |  |  |  |

| 2      | Device number, e.g., '8316' for FOD8316                                            |  |  |  |  |  |

| 3      | DIN EN/IEC60747-5-5 Option (only appears on<br>component ordered with this option) |  |  |  |  |  |

| 4      | Plant code, e.g., 'D'                                                              |  |  |  |  |  |

| 5      | Last digit year code, e.g., 'E' for 2014                                           |  |  |  |  |  |

| 6      | Two digit work week ranging from '01' to '53'                                      |  |  |  |  |  |

| 7      | Lot traceability code                                                              |  |  |  |  |  |

| 8      | Package assembly code, e.g., 'J'                                                   |  |  |  |  |  |

| Profile Freature                                    | Pb-Free Assembly Profile |

|-----------------------------------------------------|--------------------------|

| Temperature Minimum (T <sub>smin</sub> )            | 150°C                    |

| Temperature Maximum (T <sub>smax</sub> )            | 200°C                    |

| Time $(t_S)$ from $(T_{smin} \text{ to } T_{smax})$ | 60 to 120 seconds        |

| Ramp-up Rate ( $t_L$ to $t_P$ )                     | 3°C/second maximum       |

| Liquidous Temperature (T <sub>L</sub> )             | 217°C                    |

| Time $(t_L)$ Maintained Above $(T_L)$               | 60–150 seconds           |

| Peak Body Package Temperature                       | 260°C +0°C / -5°C        |

| Time (t <sub>P</sub> ) within 5°C of 260°C          | 30 seconds               |

| Ramp-Down Rate $(T_P \text{ to } T_L)$              | 6°C/second maximum       |

| Time 25°C to Peak Temperature                       | 8 minutes maximum        |

| FOD8316 — 2.                               |

|--------------------------------------------|

| - 2.5 A (                                  |

| Output C                                   |

| urren                                      |

| IGBT                                       |

| t, IGBT Drive Optoc                        |

| Optoc                                      |

| couple                                     |

| r with                                     |

| t, IGBT Drive Optocoupler with Desaturatio |

| n Det                                      |

| ection and Isolated Fault Sensin           |

| nd Is                                      |

| olated                                     |

| Fault                                      |

| Sensi                                      |

| рŋ                                         |

1

r

**DETAIL A**

SCALE: 3:1

1.27 0.40

- E) LAND PATTERN STANDARD: SOIC127P1030X275-16N

- F) DRAWING FILE NAME: MKT-M16FREV2

0.25

SEATING

PLANE

C

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC

Downloaded from Arrow.com.