# **TABLE OF CONTENTS**

| Features                                                 | $\Sigma$ - $\Delta$ Output Data                   | 51   |

|----------------------------------------------------------|---------------------------------------------------|------|

| Applications1                                            | ADC Conversion Output—Header and Data             | 51   |

| General Description1                                     | Sample Rate Converter (SRC) (SPI Control Mode)    | 52   |

| Revision History4                                        | Data Output Interface                             | 53   |

| Functional Block Diagram5                                | Calculating the CRC Checksum                      | 58   |

| Specifications6                                          | Register Summary                                  | 60   |

| DOUTx Timing Characterististics                          | Register Details                                  | 64   |

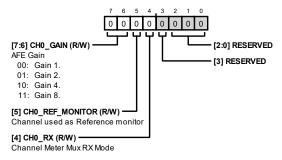

| SPI Timing Characterististics11                          | Channel 0 Configuration Register                  | 64   |

| Synchronization Pins and Reset Timing Characteristics 12 | Channel 1 Configuration Register                  | 64   |

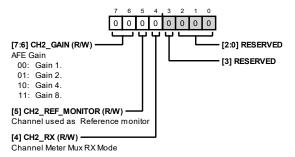

| SAR ADC Timing Characterististics                        | Channel 2 Configuration Register                  | 65   |

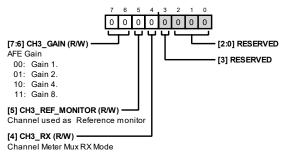

| GPIO SRC Update Timing Characterististics13              | Channel 3 Configuration Register                  | 65   |

| Absolute Maximum Ratings14                               | Channel 4 Configuration Register                  | 66   |

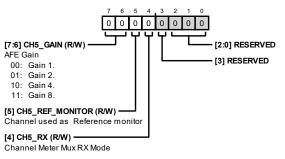

| Thermal Resistance                                       | Channel 5 Configuration Register                  | 66   |

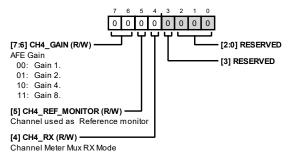

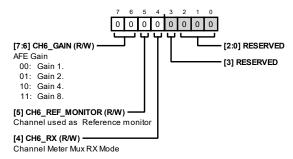

| ESD Caution14                                            | Channel 6 Configuration Register                  | 67   |

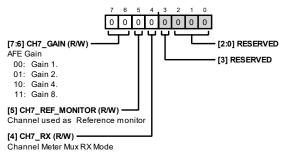

| Pin Configuration and Function Descriptions15            | Channel 7 Configuration Register                  | 67   |

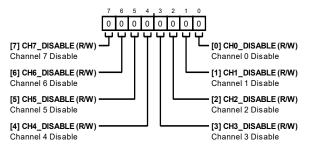

| Typical Performance Characteristics                      | Disable Clocks to ADC Channel Register            | 68   |

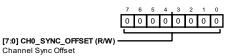

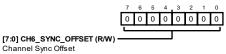

| Terminology                                              | Channel 0 Sync Offset Register                    | 68   |

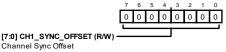

| Theory of Operation                                      | Channel 1 Sync Offset Register                    | 68   |

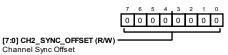

| Analog Inputs                                            | Channel 2 Sync Offset Register                    | 68   |

| Transfer Function                                        | Channel 3 Sync Offset Register                    | 69   |

| Core Signal Chain                                        | Channel 4 Sync Offset Register                    | 69   |

| Capacitive PGA35                                         | Channel 5 Sync Offset Register                    | 69   |

| Internal Reference and Reference Buffers35               | Channel 6 Sync Offset Register                    | 69   |

| Integrated LDOs                                          | Channel 7 Sync Offset Register                    | 69   |

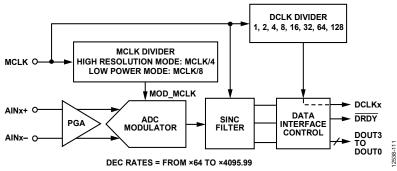

| Clocking and Sampling                                    | General User Configuration 1 Register             | 70   |

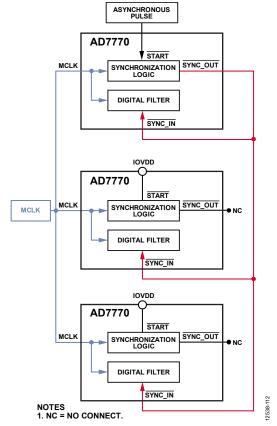

| Digital Reset and Synchronization Pins                   | General User Configuration 2 Register             | 70   |

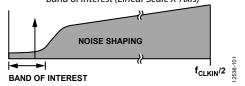

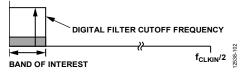

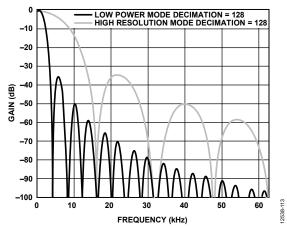

| Digital Filtering37                                      | General User Configuration 3 Register             | 71   |

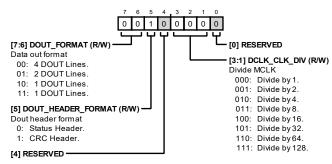

| Shutdown Mode37                                          | Data Output Format Register                       | 72   |

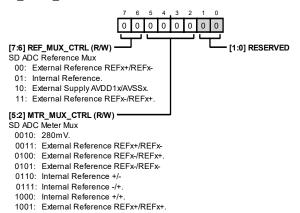

| Controlling the AD7770                                   | Main ADC Meter and Reference Mux Control Register | c 73 |

| Pin Control Mode38                                       | Global Diagnostics Mux Register                   | 74   |

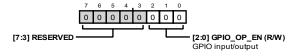

| SPI Control                                              | GPIO Configuration Register                       | 74   |

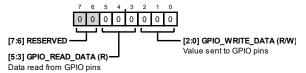

| Digital SPI43                                            | GPIO Data Register                                | 75   |

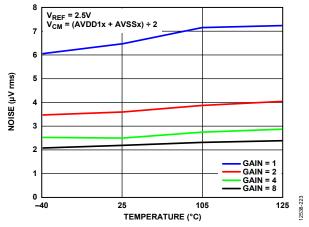

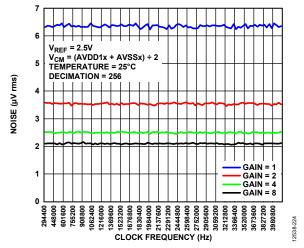

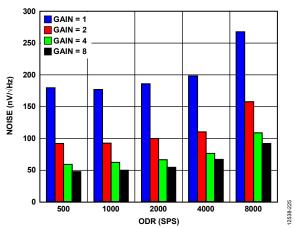

| RMS Noise and Resolution46                               | Buffer Configuration 1 Register                   | 75   |

| High Resolution Mode46                                   | Buffer Configuration 2 Register                   | 75   |

| Low Power Mode46                                         | Channel 0 Offset Upper Byte Register              | 76   |

| Diagnostics and Monitoring47                             | Channel 0 Offset Middle Byte Register             | 76   |

| Self Diagnostics Error                                   | Channel 0 Offset Lower Byte Register              | 76   |

| Monitoring Using the AD7770 SAR ADC (SPI Control         | Channel 0 Gain Upper Byte Register                | 76   |

| Mode)                                                    | Channel 0 Gain Middle Byte Register               | 76   |

| Σ-Δ ADC Diagnostics (SPI Control Mode)50                 | Channel 0 Gain Lower Byte Register                | 77   |

| Channel 1 Offset Upper Byte Register77  |

|-----------------------------------------|

| Channel 1 Offset Middle Byte Register77 |

| Channel 1 Offset Lower Byte Register77  |

| Channel 1 Gain Upper Byte Register78    |

| Channel 1 Gain Middle Byte Register78   |

| Channel 1 Gain Lower Byte Register78    |

| Channel 2 Offset Upper Byte Register78  |

| Channel 2 Offset Middle Byte Register78 |

| Channel 2 Offset Lower Byte Register79  |

| Channel 2 Gain Upper Byte Register79    |

| Channel 2 Gain Middle Byte Register79   |

| Channel 2 Gain Lower Byte Register79    |

| Channel 3 Offset Upper Byte Register79  |

| Channel 3 Offset Middle Byte Register80 |

| Channel 3 Offset Lower Byte Register80  |

| Channel 3 Gain Upper Byte Register80    |

| Channel 3 Gain Middle Byte Register80   |

| Channel 3 Gain Lower Byte Register80    |

| Channel 4 Offset Upper Byte Register81  |

| Channel 4 Offset Middle Byte Register81 |

| Channel 4 Offset Lower Byte Register81  |

| Channel 4 Gain Upper Byte Register81    |

| Channel 4 Gain Middle Byte Register81   |

| Channel 4 Gain Lower Byte Register82    |

| Channel 5 Offset Upper Byte Register82  |

| Channel 5 Offset Middle Byte Register82 |

| Channel 5 Offset Lower Byte Register82  |

| Channel 5 Gain Upper Byte Register82    |

| Channel 5 Gain Middle Byte Register83   |

| Channel 5 Gain Lower Byte Register83    |

| Channel 6 Offset Upper Byte Register83  |

| Channel 6 Offset Middle Byte Register83 |

| Channel 6 Offset Lower Byte Register83  |

| Channel 6 Gain Upper Byte Register84    |

| Channel 6 Gain Middle Byte Register 84  |

|   | Channel 6 Gain Lower Byte Register                    | 84 |

|---|-------------------------------------------------------|----|

|   | Channel 7 Offset Upper Byte Register                  | 84 |

|   | Channel 7 Offset Middle Byte Register                 | 84 |

|   | Channel 7 Offset Lower Byte Register                  | 85 |

|   | Channel 7 Gain Upper Byte Register                    | 85 |

|   | Channel 7 Gain Middle Byte Register                   | 85 |

|   | Channel 7 Gain Lower Byte Register                    | 85 |

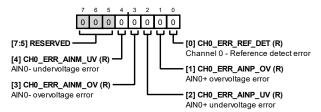

|   | Channel 0 Status Register                             | 86 |

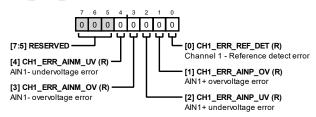

|   | Channel 1 Status Register                             | 86 |

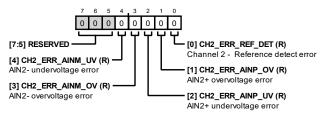

|   | Channel 2 Status Register                             | 87 |

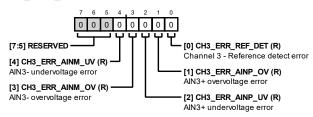

|   | Channel 3 Status Register                             | 87 |

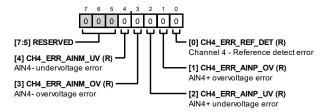

|   | Channel 4 Status Register                             | 88 |

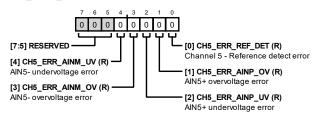

|   | Channel 5 Status Register                             | 88 |

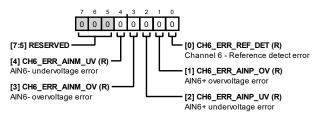

|   | Channel 6 Status Register                             | 89 |

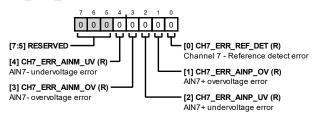

|   | Channel 7 Status Register                             | 89 |

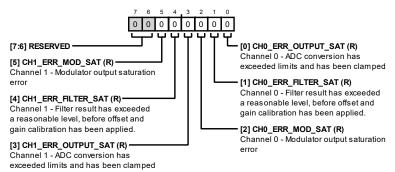

|   | Channel 0/Channel 1 DSP Errors Register               | 90 |

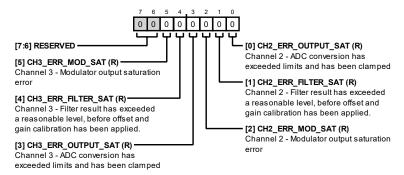

|   | Channel 2/Channel 3 DSP Errors Register               | 90 |

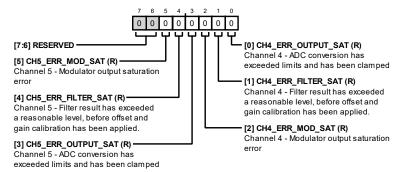

|   | Channel 4/Channel 5 DSP Errors Register               | 91 |

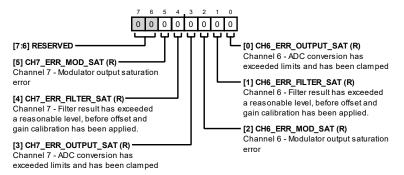

|   | Channel 6/Channel 7 DSP Errors Register               | 91 |

|   | Channel 0 to Channel 7 Error Register Enable Register | 92 |

|   | General Errors Register 1                             | 92 |

|   | General Errors Register 1 Enable                      | 93 |

|   | General Errors Register 2                             | 93 |

|   | General Errors Register 2 Enable                      | 94 |

|   | Error Status Register 1                               | 94 |

|   | Error Status Register 2                               | 95 |

|   | Error Status Register 3                               | 95 |

|   | Decimation Rate (N) MSB Register                      | 95 |

|   | Decimation Rate (N) LSB Register                      | 96 |

|   | Decimation Rate (IF) MSB Register                     | 96 |

|   | Decimation Rate (IF) LSB Register                     | 96 |

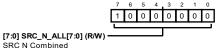

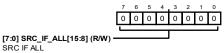

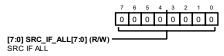

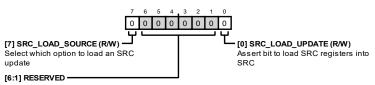

|   | SRC Load Source and Load Update Register              | 96 |

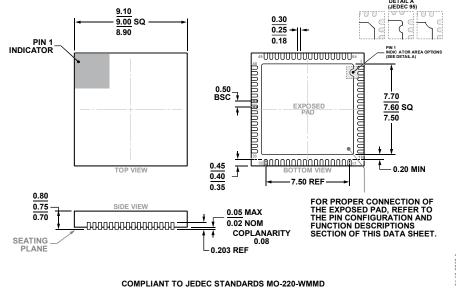

| C | Outline Dimensions                                    | 97 |

|   | Ordering Guide                                        | 97 |

## **REVISION HISTORY**

| 5/2020—Rev. D to Rev. E                                       |

|---------------------------------------------------------------|

| Changes to Table 16                                           |

| Changes to Table 6 and Figure 6                               |

| Changes to Terminology Section                                |

| Changes to Figure 99                                          |

| Changes to Sample Rate Converter (SRC) (SPI Control Mode)     |

| Section and Figure 11052                                      |

| Changes to Figure 119                                         |

| 5/2018—Rev. C to Rev. D                                       |

| Change to t <sub>22B</sub> Parameter, Table 3                 |

| Changes to AUXAIN± Parameter, Table 7 14                      |

| Changes to Table 13                                           |

| Changes to $\Sigma$ - $\Delta$ Data, ADC Mode Section45       |

| Added Figure 105; Renumbered Sequentially 45                  |

| Changes to SRC Group Delay and Latency Section 53             |

| Changed SPI Section to SPI Interface Section                  |

| Updated Outline Dimensions                                    |

| Changes to Ordering Guide                                     |

| 8/2017—Rev. B to Rev. C                                       |

| Changes to Features Section and General Description Section 1 |

| Change to START Pin Description, Table 9                      |

| Changes to Figure 48                                          |

| Change to Digital Reset and Synchronization Pins Section and  |

| Internal Reference and Reference Buffers Section              |

| Change to Figure 95                                           |

| Changes to Phase Adjustment Section and Table 1641            |

| Added Table 17; Renumbered Sequentially4                    | 1  |

|-------------------------------------------------------------|----|

| Change to Digital SPI Section4                              | 3  |

| Change to Table 254                                         | 6  |

|                                                             |    |

| 10/2016—Rev. A to Rev. B                                    |    |

| Changes to Figure 45                                        | 4  |

| Changes to Figure 56, Figure 59, and Figure 612             | 6  |

| Changes to Figure 72 and Figure 73                          | 8  |

| Changes to Figure 76                                        | 9  |

| Added Figure 82; Renumbered Sequentially                    | 0  |

| Changes to Figure 86 to Figure 89                           | 4  |

| Changes to SPI Transmission Errors (SPI Control Mode)       |    |

| Section4                                                    |    |

| Changes to Table 33 and Table 345                           | 1  |

| Changes to SRC Group Delay and Latency Section and Settling | 5  |

| Time Section                                                | 3  |

| Changes to Table 39 and Table 405                           | 7  |

| Changes to Calculating the CRC Checksum Section and         |    |

| Table 42                                                    | 8  |

| Changes to Ordering Guide                                   | 7  |

|                                                             |    |

| 5/2016—Rev. 0 to Rev. A                                     |    |

| Change to Features                                          | .1 |

| Changes to Table 1                                          | .6 |

| Changes to Figure 33 and Figure 36                          | 1  |

| Change to Figure 78                                         | 8  |

4/2016—Revision 0: Initial Version

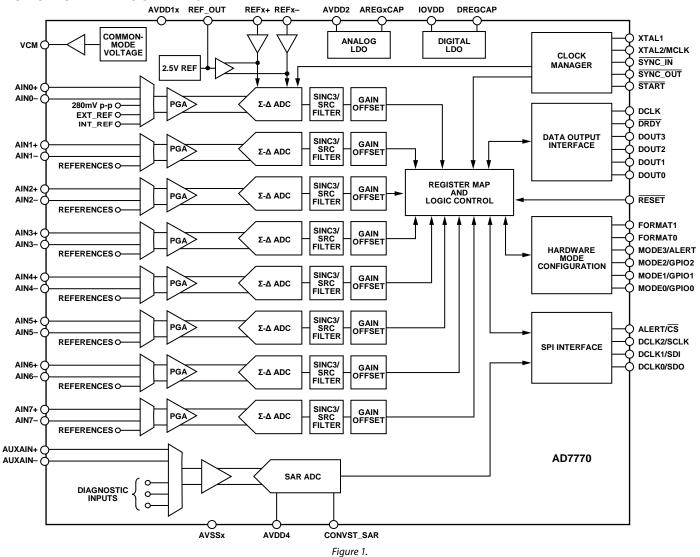

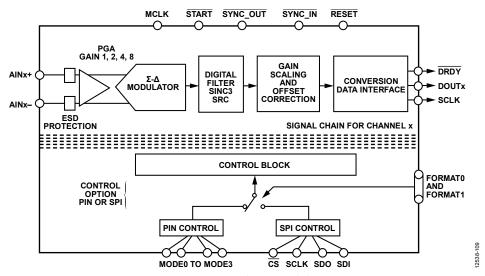

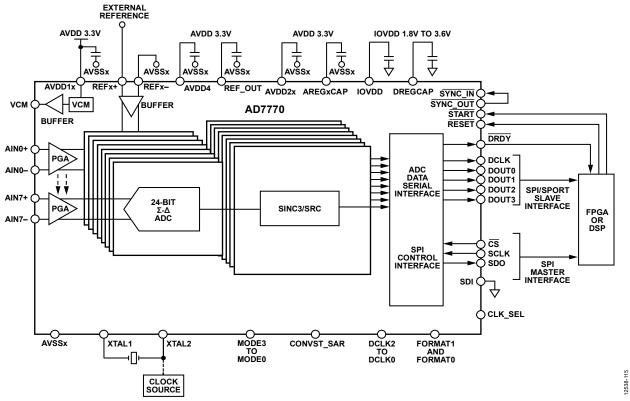

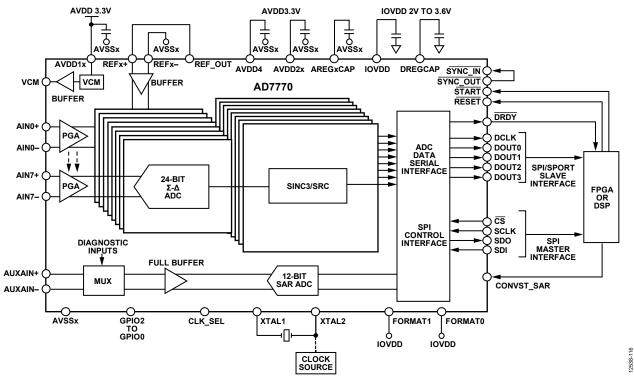

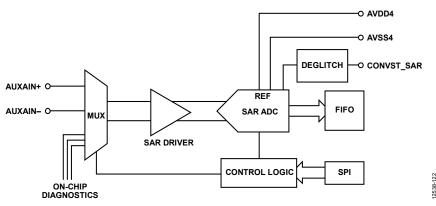

## **FUNCTIONAL BLOCK DIAGRAM**

## **SPECIFICATIONS**

$AVDD1x = 1.65 \ V, \ AVSSx^1 = -1.65 \ V \ (dual \ supply \ operation), \ AVDD1x = 3.3 \ V, \ AVSSx = analog \ ground \ (AGND) \ (single-supply \ operation), \\ AVDD2x - AVSSx = 2.2 \ V \ to \ 3.6 \ V; \ IOVDD = 1.8 \ V \ to \ 3.6 \ V; \ DGND = 0 \ V, \ REFx+/REFx- = 2.5 \ V \ (internal/external), \ master \ clock \\ (MCLK) = 8192 \ kHz \ for \ high \ resolution \ mode \ and \ 4096 \ kHz \ for \ low \ power \ mode; \ AVSSx = 2.2 \ V \ (internal/external), \ master \ clock \ (MCLK) = 8192 \ kHz \ for \ high \ resolution \ mode \ and \ 8 \ kSPS \ for \ low \ power \ mode; \ all \ specifications \ at \ T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted.$

Table 1.

| Parameter                                       | Test Conditions/Comments                                             | Min      | Тур           | Max  | Unit                     |

|-------------------------------------------------|----------------------------------------------------------------------|----------|---------------|------|--------------------------|

| Σ-Δ ADC CHANNELS                                |                                                                      |          |               |      |                          |

| Speed and Performance                           |                                                                      |          |               |      |                          |

| Resolution                                      |                                                                      | 24       |               |      | Bits                     |

| ODR                                             | High resolution mode                                                 |          |               | 32   | kSPS                     |

|                                                 | Low power mode                                                       |          |               | 8    | kSPS                     |

| No Missing Codes                                | Up to 24 kSPS                                                        | 24       |               |      | Bits                     |

| Gain Settings, PGA <sub>GAIN</sub>              |                                                                      |          | 1, 2, 4, or 8 |      |                          |

| Bandwidth                                       | Small signal, high resolution mode                                   |          |               | 2    | MHz                      |

|                                                 | Small signal, low power mode                                         |          |               | 512  | kHz                      |

|                                                 | Large signal, high resolution mode                                   |          |               | 5    | kHz                      |

|                                                 | Large signal, low power mode                                         |          |               | 1.5  | kHz                      |

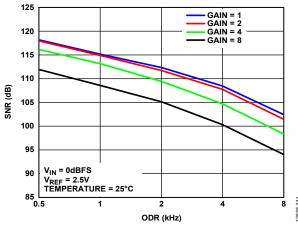

| AC Accuracy                                     |                                                                      |          |               |      |                          |

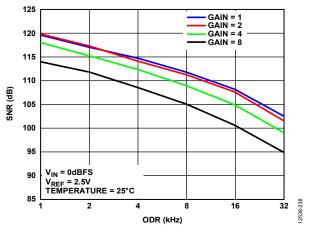

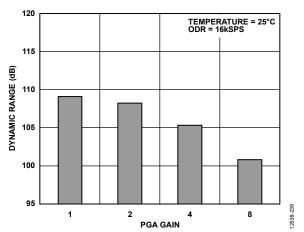

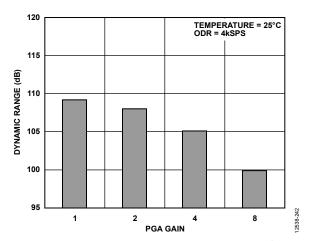

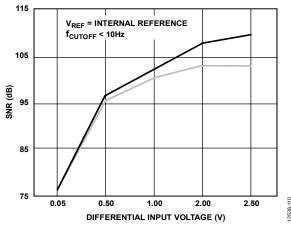

| Dynamic Range                                   | Shorted inputs, PGA <sub>GAIN</sub> = 1                              |          |               |      |                          |

| 32 kSPS                                         | High resolution mode                                                 |          | 103           |      | dB                       |

| 8 kSPS                                          | High resolution mode                                                 |          | 113           |      | dB                       |

|                                                 | Low power mode                                                       |          | 103           |      | dB                       |

| 2 kSPS                                          | Low power mode                                                       |          | 113           |      | dB                       |

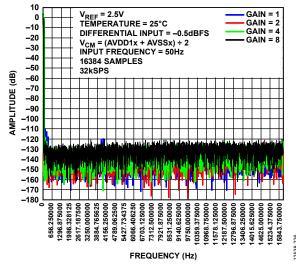

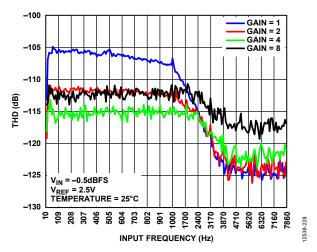

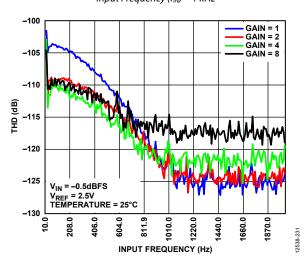

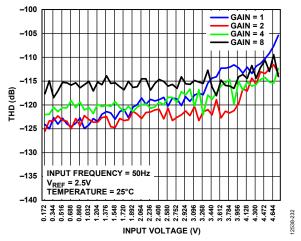

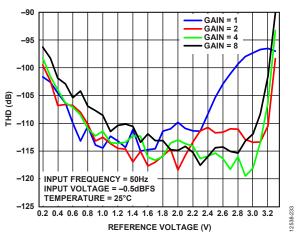

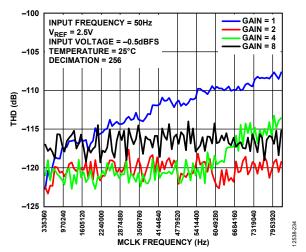

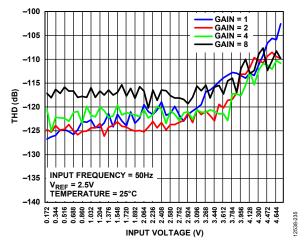

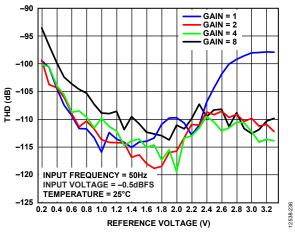

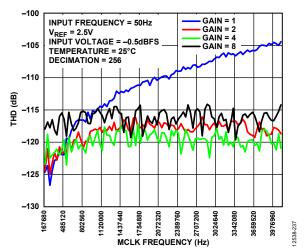

| THD                                             | -0.5 dBFS, high resolution mode                                      |          | -109          |      | dB                       |

| 2                                               | -0.5 dBFS, low power mode                                            |          | -105          |      | dB                       |

| Signal-to-Noise-and-Distortion<br>Ratio (SINAD) | f <sub>IN</sub> = 60 Hz                                              |          | 106           |      | dB                       |

| SFDR                                            | High resolution mode, 16 kSPS, PGA <sub>GAIN</sub> = 1               |          | 132           |      | dB                       |

| Intermodulation Distortion (IMD)                | $f_A = 50 \text{ Hz}$ , $f_B = 51 \text{ Hz}$ , high resolution mode |          | -125          |      | dB                       |

|                                                 | $f_A = 50$ Hz, $f_B = 51$ Hz, low power mode                         |          | -105          |      | dB                       |

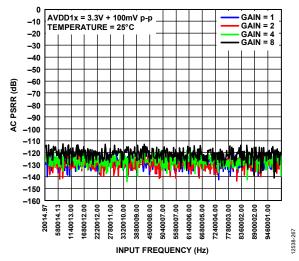

| DC Power Supply Rejection                       | AVDD1x = 3.3 V                                                       |          | -90           |      | dB                       |

| DC Common-Mode Rejection<br>Ratio               |                                                                      | 80       |               |      | dB                       |

| Crosstalk                                       |                                                                      |          | -120          |      | dB                       |

| DC ACCURACY                                     |                                                                      |          |               |      |                          |

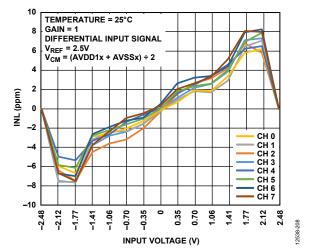

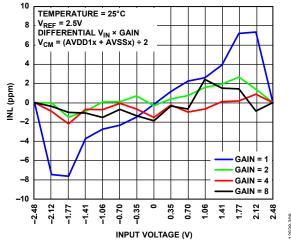

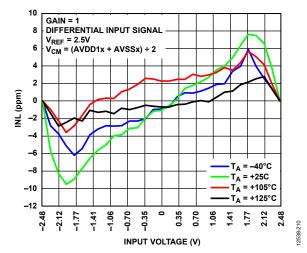

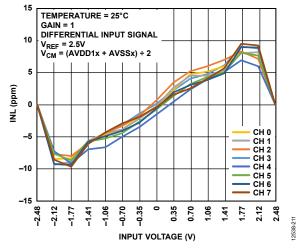

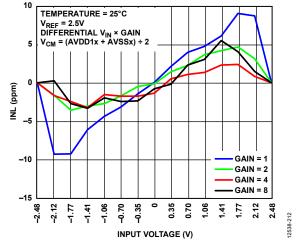

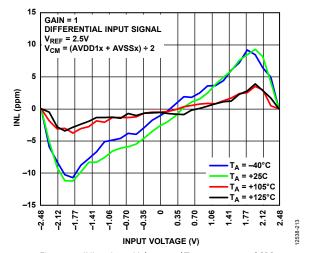

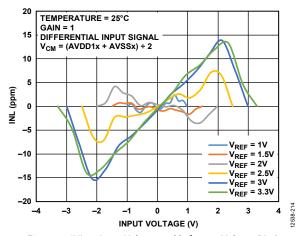

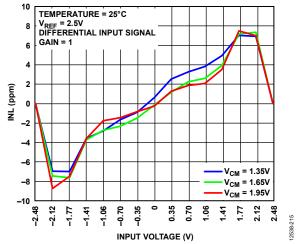

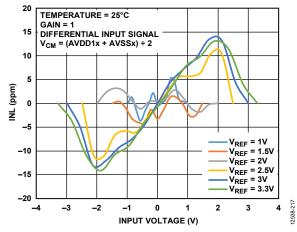

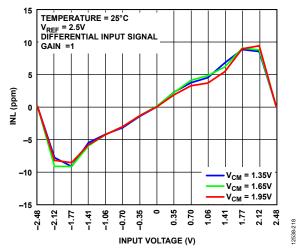

| INL                                             | Endpoint mathed DCA - 1                                              |          | то            |      | nom of ECD               |

| High Resolution Mode                            | Endpoint method, PGA <sub>GAIN</sub> = 1                             |          | ±8            |      | ppm of FSR<br>ppm of FSR |

| Lave Davison Marila                             | Other PGA gains                                                      |          | ±4            |      |                          |

| Low Power Mode                                  | Endpoint method, PGA <sub>GAIN</sub> = 1                             |          | ±9            |      | ppm of FSR               |

| 011.                                            | Other PGA gains                                                      |          | ±6            | . 00 | ppm of FSR               |

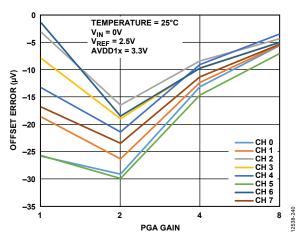

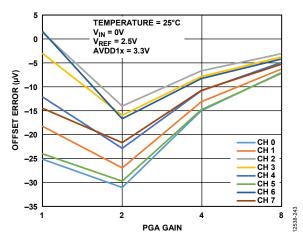

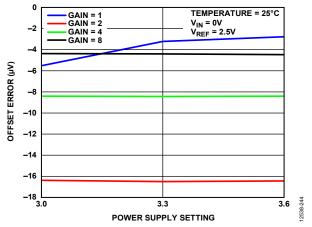

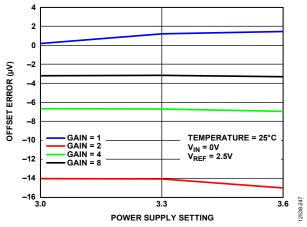

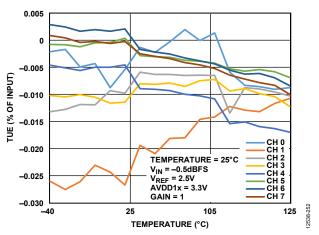

| Offset Error                                    |                                                                      |          | ±15           | ±90  | μV                       |

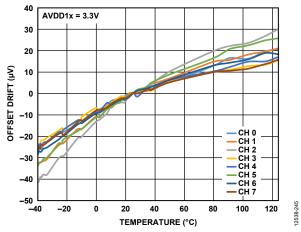

| Offset Error Drift                              |                                                                      |          | ±0.25         |      | μV/°C                    |

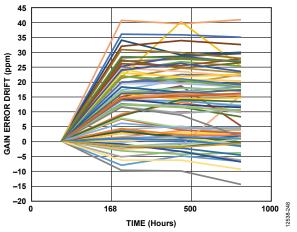

|                                                 | Over time                                                            |          | -2            |      | μV/<br>1000 hours        |

| Offset Matching                                 |                                                                      | 1        | 25            |      | μV                       |

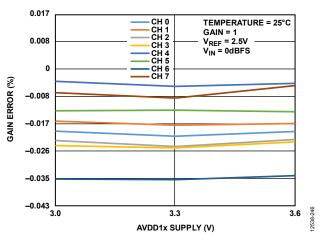

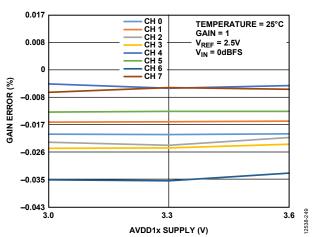

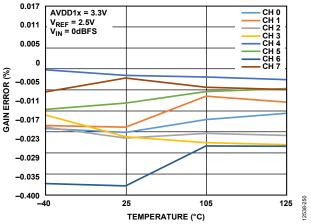

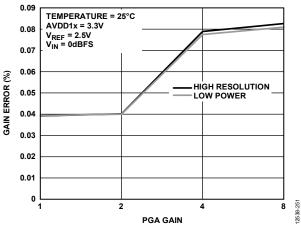

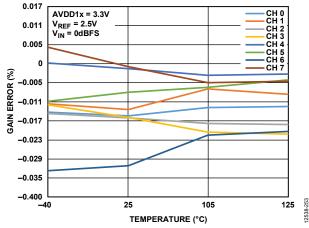

| Gain Error                                      |                                                                      | 1        | ±0.1          |      | % FS                     |

| Gain Drift vs. Temperature                      |                                                                      |          | ±0.75         |      | ppm/°C                   |

| Gain Matching                                   |                                                                      | <u> </u> | ±0.1          |      | %                        |

| Parameter                                           | Test Conditions/Comments                                      | Min          | Тур                  | Max                         | Unit   |

|-----------------------------------------------------|---------------------------------------------------------------|--------------|----------------------|-----------------------------|--------|

| ANALOG INPUTS                                       |                                                               |              | •                    |                             |        |

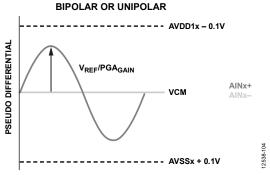

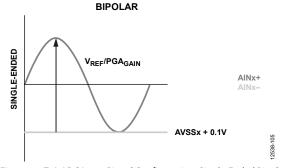

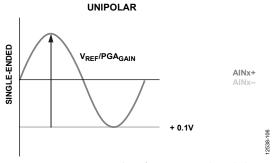

| Differential Input Voltage Range                    | $V_{REF} = (REFx + - REFx -)$                                 |              |                      | $\pm V_{REF}/PGA_{GAIN}$    | V      |

| Single-Ended Input Voltage Range                    |                                                               |              |                      | $0$ to $V_{REF}/PGA_{GAIN}$ | ٧      |

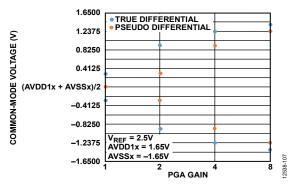

| AINx± Common-Mode Input                             |                                                               | AVSSx + 0.10 | (AVDD1x+             | AVDD1x - 0.10               | V      |

| Range                                               |                                                               |              | AVSSx)/2             |                             |        |

| Absolute AINx± Voltage Limits                       |                                                               | AVSSx + 0.10 |                      | AVDD1x – 0.10               | V      |

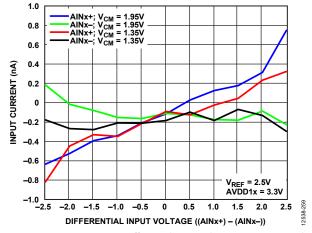

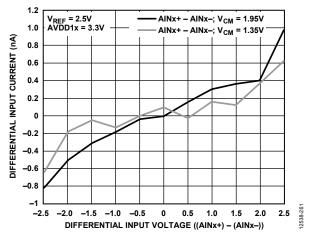

| DC Input Current                                    |                                                               |              |                      |                             |        |

| Differential                                        | High resolution, MCLK = 8192 kHz                              |              | 4                    |                             | nA     |

|                                                     | Low power mode, MCLK = 4096 kHz                               |              | 1                    |                             | nA     |

| Single-Ended                                        | High resolution, MCLK = 8192 kHz                              |              | 8                    |                             | nA     |

|                                                     | Low power mode, MCLK = 4096 kHz                               |              | 2                    |                             | nA     |

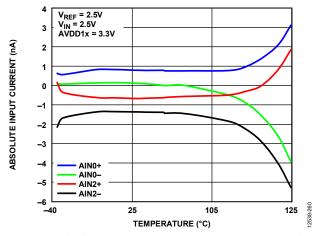

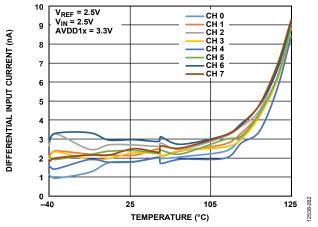

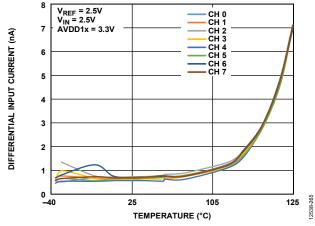

| Input Current Drift                                 |                                                               |              | 50                   |                             | pA/°C  |

| AC Input Capacitance                                |                                                               |              | 8                    |                             | pF     |

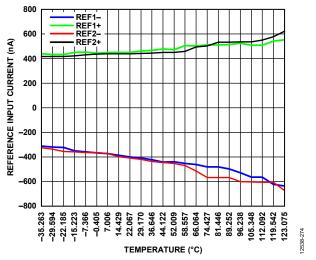

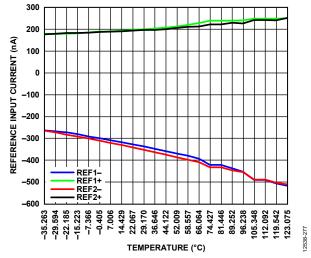

| REFERENCE                                           |                                                               |              |                      |                             |        |

| Internal                                            |                                                               |              |                      |                             |        |

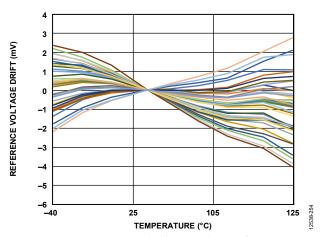

| Initial Accuracy                                    | REF_OUT, T <sub>A</sub> = 25°C                                | 2.495        | 2.5                  | 2.505                       | V      |

| Temperature Coefficient                             |                                                               |              | ±10                  | ±38                         | ppm/°C |

| Reference Load Current, I∟                          |                                                               | -10          |                      | +10                         | mA     |

| DC Power Supply Rejection                           | Line regulation                                               |              | 95                   |                             | dB     |

| Load Regulation, ΔV <sub>OUT</sub> /ΔI <sub>L</sub> |                                                               |              | 100                  |                             | μV/mA  |

| Voltage Noise, e <sub>N p-p</sub>                   | 0.1 Hz to 10 Hz                                               |              | 6.8                  |                             | μV rms |

| Voltage Noise Density, e <sub>N</sub>               | 1 kHz, 2.5 V reference                                        |              | 273.5                |                             | nV/√Hz |

| Turn On Settling Time                               | 100 nF                                                        |              | 1.5                  |                             | ms     |

| External                                            |                                                               |              |                      |                             |        |

| Input Voltage                                       | $V_{REF} = (REFx + - REFx -)$                                 | 1            | 2.5                  | AVDD1x                      | V      |

| Buffer Headroom                                     |                                                               | AVSSx + 0.1  |                      | AVDD1x – 0.1                | V      |

| REFx- Input Voltage                                 |                                                               |              | AVSSx                | AVDD1x – REFx+              | V      |

| Average REFx± Input Current                         | Current per channel                                           |              |                      |                             |        |

|                                                     | Reference buffer disabled, high resolution mode               |              | 18                   |                             | μA/V   |

|                                                     | Reference buffer precharge mode (pre-Q), high resolution mode |              | 600                  |                             | nA/V   |

|                                                     | Reference buffer disabled, low power mode                     |              | 4.5                  |                             | μA/V   |

|                                                     | Reference buffer pre-Q, low power mode                        |              | 100                  |                             | nA/V   |

|                                                     | Reference buffer enabled, high resolution mode                |              | 12                   |                             | nA/V   |

|                                                     | Reference buffer enabled, low power mode                      |              | 5                    |                             | nA/V   |

| TEMPERATURE RANGE                                   | 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                       |              |                      |                             |        |

| Specified Performance                               | T <sub>MIN</sub> to T <sub>MAX</sub>                          | -40          |                      | +105                        | °C     |

| Functional <sup>2</sup>                             | T <sub>MIN</sub> to T <sub>MAX</sub>                          | -40          |                      | +125                        | °C     |

| TEMPERATURE SENSOR                                  |                                                               |              |                      |                             |        |

| Accuracy                                            |                                                               |              | ±2                   |                             | °C     |

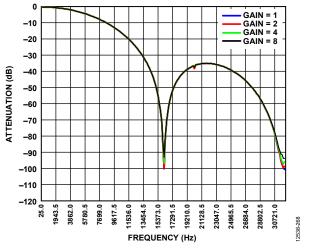

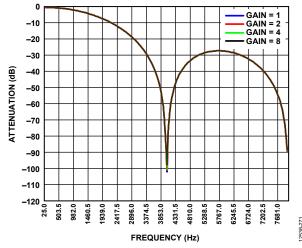

| DIGITAL FILTER RESPONSE (SINC3)                     |                                                               |              |                      |                             | -      |

| Group Delay                                         |                                                               | See          | the SRC Group Dela   | v section                   |        |

| Settling Time                                       |                                                               |              | ee the Settling Time | •                           |        |

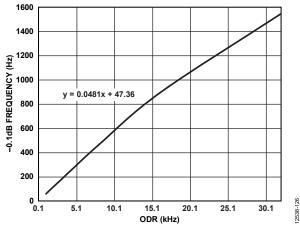

| Pass Band                                           | −0.1 dB                                                       |              | the SRC Bandwidth    |                             |        |

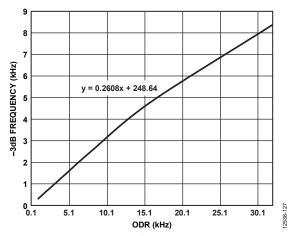

|                                                     | -3 dB                                                         |              | the SRC Bandwidth    |                             |        |

| Decimation Rate                                     |                                                               | 64           |                      | 4095.99                     |        |

| Parameter                                                                                | Test Conditions/Comments                                                        | Min         | Тур                          | Max         | Unit  |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------|------------------------------|-------------|-------|

| CLOCK SOURCE                                                                             |                                                                                 |             |                              |             |       |

| Frequency                                                                                | High resolution mode                                                            | 0.655       |                              | 8.192       | MHz   |

|                                                                                          | Low power mode                                                                  | 1.3         |                              | 4.096       | MHz   |

| Duty Cycle                                                                               |                                                                                 | 45:55       | 50:50                        | 55:45       | %     |

| SAR ADC                                                                                  |                                                                                 |             |                              |             |       |

| Speed and Performance                                                                    |                                                                                 |             |                              |             |       |

| Resolution                                                                               |                                                                                 |             | 12                           |             | Bits  |

| Analog Input Range                                                                       |                                                                                 | AVSS4 + 0.1 |                              | AVDD4 - 0.1 | V     |

| Analog Input Common-Mode<br>Range                                                        |                                                                                 | AVSS4 + 0.1 | (AVDD4 +<br>AVSS4)/2         | AVDD4 – 0.1 | V     |

| Analog Input Dynamic Current                                                             | 256 kSPS, 0 dBFS                                                                |             | ±100                         |             | nA    |

| Throughput                                                                               |                                                                                 |             |                              | 256         | kSPS  |

| DC Accuracy                                                                              | Differential mode                                                               |             |                              |             |       |

| INL                                                                                      |                                                                                 |             | 1.5                          |             | LSB   |

| DNL                                                                                      | No missing codes (12-bit)                                                       | -0.99       |                              | +1          | LSB   |

| Offset                                                                                   |                                                                                 |             | ±1                           |             | LSB   |

| Gain                                                                                     |                                                                                 |             | 12                           |             | LSB   |

| AC Performance                                                                           |                                                                                 |             |                              |             |       |

| SNR                                                                                      | 1 kHz                                                                           |             | 66                           |             | dB    |

| THD                                                                                      | 1 kHz                                                                           |             | <del>-</del> 81              |             | dB    |

| VCM PIN                                                                                  |                                                                                 |             |                              |             |       |

| Output                                                                                   |                                                                                 |             | (AVDD1x +<br>AVSSx)/2        |             | V     |

| Load Current, I∟                                                                         |                                                                                 |             | 1                            |             | mA    |

| Load Regulation, ΔV <sub>OUT</sub> /Δl <sub>L</sub>                                      |                                                                                 |             | 12                           |             | mV/mA |

| Short-Circuit Current                                                                    |                                                                                 |             | 5                            |             | mA    |

| LOGIC INPUTS                                                                             |                                                                                 |             |                              |             |       |

| Input Voltage                                                                            |                                                                                 |             |                              |             |       |

| High, V <sub>⊞</sub>                                                                     |                                                                                 | 0.7 × IOVDD |                              |             | V     |

| Low, V <sub>IL</sub>                                                                     |                                                                                 |             |                              | 0.4         | V     |

| Hysteresis                                                                               |                                                                                 |             | 0.1                          |             | V     |

| Input Currents                                                                           |                                                                                 | -10         |                              | +10         | μA    |

| LOGIC OUTPUTS <sup>3</sup>                                                               |                                                                                 |             |                              | -           |       |

| Output Voltage                                                                           |                                                                                 |             |                              |             |       |

| High, V <sub>OH</sub>                                                                    | IOVDD ≥ 3 V, I <sub>SOURCE</sub> = 1 mA                                         | 0.8 × IOVDD |                              |             | V     |

| Tilgii, Von                                                                              | 2.3 V ≤ IOVDD < 3 V, Isource = 500 µA                                           | 0.8 × IOVDD |                              |             | v     |

|                                                                                          | IOVDD < 2.3 V, I <sub>SOURCE</sub> = 200 μA                                     | 0.8 × IOVDD |                              |             | V     |

| Low, V <sub>OL</sub>                                                                     | $IOVDD \ge 3 \text{ V, } I_{SINK} = 2 \text{ mA}$                               |             |                              | 0.4         | v     |

| , - 52                                                                                   | $2.3 \text{ V} \leq \text{IOVDD} < 3 \text{ V}, \text{I}_{SINK} = 1 \text{ mA}$ |             |                              | 0.4         | v     |

|                                                                                          | $IOVDD < 2.3 \text{ V, } I_{SINK} = 100  \mu\text{A}$                           |             |                              | 0.4         | v     |

| Leakage Current                                                                          | Floating state                                                                  | -10         |                              | +10         | μΑ    |

|                                                                                          | _                                                                               |             | 10                           | 110         | pF    |

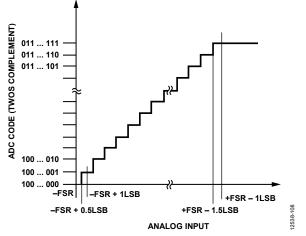

|                                                                                          | Trouting state                                                                  |             |                              | ment        | l bi  |

|                                                                                          |                                                                                 |             | -                            | HEHL        |       |

| Output Capacitance $\Sigma$ - $\Delta$ ADC Data Output Coding SAR ADC Data Output Coding | Floating state                                                                  |             | 10<br>Twos compler<br>Binary | ment        | þ     |

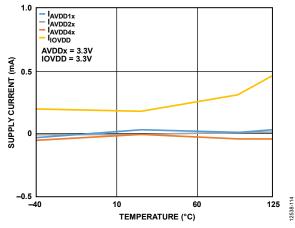

| Parameter                          | Test Conditions/Comments                                                                           | Min             | Тур  | Max    | Unit |

|------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|------|--------|------|

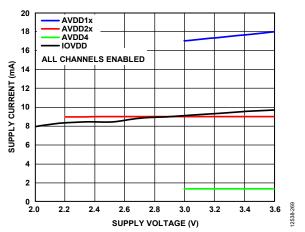

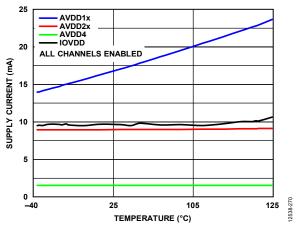

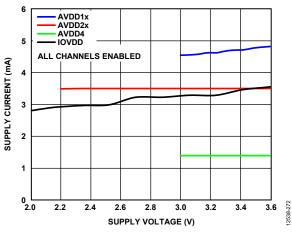

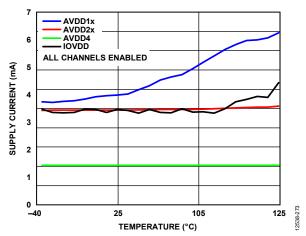

| POWER SUPPLIES                     | All Σ-Δ channels enabled                                                                           |                 |      |        |      |

| AVDD1x – AVSSx                     |                                                                                                    | 3.0             |      | 3.6    | V    |

| I <sub>AVDD1x</sub> <sup>4,5</sup> | Reference buffer pre-Q, VCM enabled, internal reference enabled                                    |                 |      |        |      |

|                                    | High resolution mode                                                                               |                 | 18.5 | 23.7   | mA   |

|                                    | Low power mode                                                                                     |                 | 5    | 6.4    | mA   |

|                                    | Reference buffer enabled, VCM enabled, internal reference enabled                                  |                 |      |        |      |

|                                    | High resolution mode                                                                               |                 | 20.5 | 26.7   | mA   |

|                                    | Low power mode                                                                                     |                 | 5.5  | 7.1    | mA   |

|                                    | Reference buffer disabled, VCM disabled, internal reference disabled                               |                 |      |        |      |

|                                    | High resolution mode                                                                               |                 | 14.3 | 18.8   | mA   |

|                                    | Low power mode                                                                                     |                 | 3.9  | 5.1    | mA   |

| AVDD2x – AVSSx                     |                                                                                                    | 2.2             |      | 3.6    | V    |

| I <sub>AVDD2x</sub>                | High resolution mode                                                                               |                 | 9    | 9.45   | mA   |

|                                    | Low power mode                                                                                     |                 | 3.5  | 3.7    | mA   |

| AVDD4 – AVSSx                      |                                                                                                    | AVDD1x –<br>0.3 |      | AVDD1x | V    |

| I <sub>AVDD4</sub>                 | SAR enabled                                                                                        |                 | 1.7  | 2      | mA   |

|                                    | SAR disabled                                                                                       |                 | 1    | 10     | μΑ   |

| AVSSxv – DGND                      |                                                                                                    | -1.8            |      | 0      | V    |

| IOVDD – DGND                       |                                                                                                    | 1.8             |      | 3.6    | V    |

| liovdd                             | High resolution mode                                                                               |                 | 8    | 11.3   | mA   |

|                                    | Low power mode                                                                                     |                 | 3    | 4.4    | mA   |

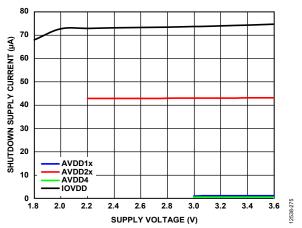

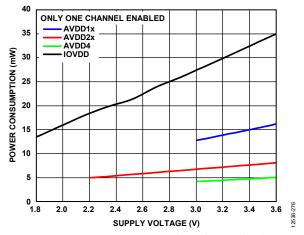

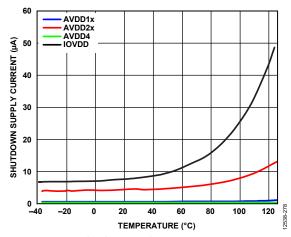

| Power Dissipation <sup>6</sup>     | Internal buffers bypassed, internal reference disabled, internal oscillator disabled, SAR disabled |                 |      |        |      |

| <b>High Resolution Mode</b>        | 32 kSPS                                                                                            |                 | 117  | 136    | mW   |

| Low Power Mode                     | 8 kSPS                                                                                             |                 | 38   | 44     | mW   |

| Power-Down                         | All ADCs disabled                                                                                  |                 | 530  |        | μW   |

<sup>&</sup>lt;sup>1</sup> AVSSx refers to the following pins: AVSS1A, AVSS1B, AVSS2A, AVSS2B, AVSS3, and AVSS4. This term is used throughout the data sheet.

<sup>&</sup>lt;sup>2</sup> At temperatures higher than 105°C, the device can be operated normally, though slight degradation on the maximum/minimum specifications is expected because these specifications are only guaranteed up to 105°C. See the Typical Performance Characteristics section for plots showing the typical performance of the device at high temperatures.

<sup>&</sup>lt;sup>3</sup> The SDO pin and the DOUTx pin are configured in the default mode of strength.

$<sup>^4</sup>$ AVDD1x = 3.3 V, AVSSx = GND = ground, IOVDD = 1.8 V, CMOS clock.

<sup>&</sup>lt;sup>5</sup> Disabling either the VCM pin or the internal reference results in a 40 µA typical current consumption reduction.

<sup>&</sup>lt;sup>6</sup> Power dissipation is calculated using the maximum supply voltage, 3.6 V.

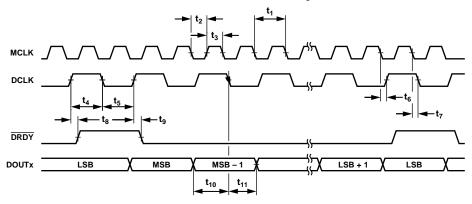

### **DOUTX TIMING CHARACTERISTISTICS**

$AVDD1x = 1.65 \ V, \ AVSSx^1 = -1.65 \ V \ (dual \ supply \ operation), \ AVDD1x = 3.3 \ V, \ AVSSx = AGND \ (single-supply \ operation), \ AVDD2 - AVSSx = 2.2 \ V \ to \ 3.6 \ V; \ IOVDD = 1.8 \ V \ to \ 3.6 \ V; \ DGND = 0 \ V, \ REFx+/REFx- = 2.5 \ V \ internal/external, \ MCLK = 8192 \ kHz; \ all \ specifications \ at \ T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted.$

Table 2.

| Parameter             | Description <sup>2</sup>               | Test Conditions/Comments | Min   | Тур | Max   | Unit |

|-----------------------|----------------------------------------|--------------------------|-------|-----|-------|------|

| t <sub>1</sub>        | MCLK frequency                         | 50:50                    | 0.655 |     | 8.192 | MHz  |

| $t_2$                 | MCLK low time                          |                          | 60    |     |       | ns   |

| t <sub>3</sub>        | MCLK high time                         |                          | 60    |     |       | ns   |

| t <sub>4</sub>        | DCLK high time                         | MCLK/2                   | 121   |     |       | ns   |

| <b>t</b> <sub>5</sub> | DCLK low time                          | MCLK/2                   | 121   |     |       | ns   |

| t <sub>6</sub>        | MCLK falling edge to DCLK rising edge  |                          |       |     | 45    | ns   |

| <b>t</b> <sub>7</sub> | MCLK falling edge to DCLK falling edge |                          |       |     | 45    | ns   |

| t <sub>8</sub>        | DCLK rising edge to DRDY rising edge   |                          | 2     |     |       | ns   |

| t <sub>9</sub>        | DCLK rising edge to DRDY falling edge  |                          | 1     |     |       | ns   |

| t <sub>10</sub>       | DOUTx setup time                       |                          | 20    |     |       | ns   |

| t <sub>11</sub>       | DOUTx hold time                        |                          | 20    |     |       | ns   |

AVSSx refers to the following pins: AVSS1A, AVSS1B, AVSS2A, AVSS2B, AVSS3, and AVSS4. This term is used throughout the data sheet.

<sup>&</sup>lt;sup>2</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of IOVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

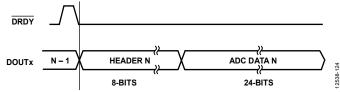

Figure 2. Data Interface Timing Diagram

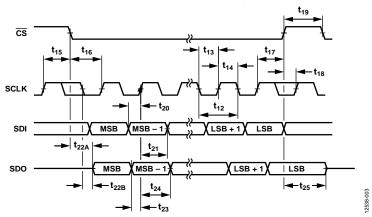

## **SPI TIMING CHARACTERISTISTICS**

AVDD1x = 1.65 V,  $AVSSx^1 = -1.65 \text{ V}$  (dual supply operation), AVDD1x = 3.3 V, AVSSx = AGND, AVDD2 - AVSSx = 2.2 V to 3.6 V; IOVDD = 1.8 V to 3.6 V; DGND = 0 V, REFx + /REFx - = 2.5 V (internal/external), MCLK = 8192 kHz; all specifications at  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 3.

| Parameter              | Description <sup>2</sup>                                  | Test Conditions/Comments | Min | Тур | Max | Unit |

|------------------------|-----------------------------------------------------------|--------------------------|-----|-----|-----|------|

| t <sub>12</sub>        | SCLK period                                               | 50:50                    |     |     | 30  | MHz  |

| t <sub>13</sub>        | SCLK low time                                             |                          | 7   |     |     | ns   |

| t <sub>14</sub>        | SCLK high time                                            |                          | 7   |     |     | ns   |

| <b>t</b> <sub>15</sub> | SCLK rising edge to CS falling edge                       |                          | 10  |     |     | ns   |

| t <sub>16</sub>        | CS falling edge to SCLK rising edge                       |                          | 10  |     |     | ns   |

| t <sub>17</sub>        | SCLK rising edge to $\overline{\text{CS}}$ rising edge    |                          | 10  |     |     | ns   |

| t <sub>18</sub>        | CS rising edge to SCLK rising edge                        |                          | 10  |     |     | ns   |

| t <sub>19</sub>        | Minimum CS high time                                      |                          | 10  |     |     | ns   |

| t <sub>20</sub>        | SDI setup time                                            |                          | 5   |     |     | ns   |

| t <sub>21</sub>        | SDI hold time                                             |                          | 5   |     |     | ns   |

| t <sub>22A</sub>       | $\overline{CS}$ falling edge to SDO enable (SPI = Mode 0) |                          | 30  |     |     | ns   |

| t <sub>22B</sub>       | SCLK falling edge to SDO enable (SPI = Mode 3)            |                          | 49  |     |     | ns   |

| t <sub>23</sub>        | SDO setup time                                            |                          | 10  |     |     | ns   |

| t <sub>24</sub>        | SDO hold time                                             |                          | 10  |     |     | ns   |

| t <sub>25</sub>        | CS rising edge to SDO disable                             |                          | 30  |     |     | ns   |

AVSSx refers to the following pins: AVSS1A, AVSS1B, AVSS2A, AVSS2B, AVSS3, and AVSS4. This term is used throughout the data sheet.

<sup>&</sup>lt;sup>2</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of IOVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

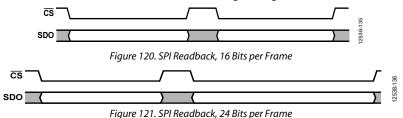

Figure 3. SPI Control Interface Timing Diagram

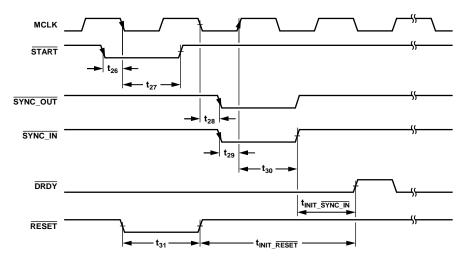

### SYNCHRONIZATION PINS AND RESET TIMING CHARACTERISTICS

AVDD1x = 1.65 V,  $AVSSx^1 = -1.65 \text{ V}$  (dual supply operation), AVDD1x = 3.3 V, AVSSx = AGND, AVDD2 - AVSSx = 2.2 V to 3.6 V; IOVDD = 1.8 V to 3.6 V; DGND = 0 V, REFx + /REFx - = 2.5 V (internal/external), MCLK = 8192 kHz; all specifications at  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 4.

| Parameter                  | Description <sup>2</sup>                   | Test Conditions/Comments                       | Min      | Тур | Max | Unit |

|----------------------------|--------------------------------------------|------------------------------------------------|----------|-----|-----|------|

| t <sub>26</sub>            | START setup time                           |                                                | 10       |     |     | ns   |

| t <sub>27</sub>            | START hold time                            |                                                | MCLK     |     |     | ns   |

| t <sub>28</sub>            | MCLK falling edge to SYNC_OUT falling edge |                                                | MCLK     |     |     | ns   |

| t <sub>29</sub>            | SYNC_IN setup time                         |                                                | 10       |     |     | ns   |

| t <sub>30</sub>            | SYNC_IN hold time                          |                                                | MCLK     |     |     | ns   |

| t <sub>INIT_</sub> SYNC_IN | SYNC_IN rising edge to first DRDY          | 16 kSPS, high resolution mode                  | 145      |     |     | μs   |

| $t_{\text{INIT}}$ RESET    | RESET rising edge to first DRDY            | 16 kSPS, high resolution mode                  | 225      |     |     | μs   |

| t <sub>31</sub>            | RESET hold time                            |                                                | 2 × MCLK |     |     | ns   |

| t <sub>POWER_UP</sub>      | Start time                                 | t <sub>POWER_UP</sub> is not shown in Figure 4 |          | 2   |     | ms   |

AVSSx refers to the following pins: AVSS1A, AVSS1B, AVSS2A, AVSS2B, AVSS3, and AVSS4. This term is used throughout the data sheet.

<sup>&</sup>lt;sup>2</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of IOVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

Figure 4. Synchronization Pins and Reset Control Interface Timing Diagram

12538-004

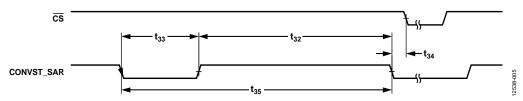

#### **SAR ADC TIMING CHARACTERISTISTICS**

AVDD1x = 1.65 V,  $AVSSx^1 = -1.65 \text{ V}$  (dual supply operation), AVDD1x = 3.3 V, AVSSx = AGND, AVDD2 - AVSSx = 2.2 V to 3.6 V; IOVDD = 1.8 V to 3.6 V; IOVDD = 1.8 V to 3.6 V; IOVDD = 0 V,  $IOVDD = 0 \text{$

Table 5.

| Parameter       | Description <sup>2</sup>      | Min | Тур | Max | Unit |

|-----------------|-------------------------------|-----|-----|-----|------|

| t <sub>32</sub> | Conversion time               | 1   |     | 3.4 | μs   |

| t <sub>33</sub> | Acquisition time <sup>3</sup> | 500 |     |     | ns   |

| t <sub>34</sub> | Delay time                    | 50  |     |     | ns   |

| t <sub>35</sub> | Throughput data rate          |     |     | 256 | kSPS |

AVSSx refers to the following pins: AVSS1A, AVSS1B, AVSS2A, AVSS2B, AVSS3 and AVSS4. This term is used throughout the data sheet.

<sup>&</sup>lt;sup>3</sup> Direct mode enabled. If deglitch mode is enabled, add 1.5/MCLK as described in Table 30.

Figure 5. SAR ADC Timing Diagram

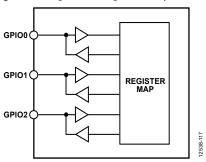

#### **GPIO SRC UPDATE TIMING CHARACTERISTISTICS**

AVDD1x = 1.65 V,  $AVSSx^1 = -1.65 \text{ V}$  (dual supply operation), AVDD1x = 3.3 V, AVSSx = AGND, AVDD2 - AVSSx = 2.2 V to 3.6 V; IOVDD = 1.8 V to 3.6 V; IOVDD = 1.8 V to 3.6 V; IOVDD = 0 V,  $IOVDD = 0 \text{$

Table 6.

| Parameter              | Description <sup>2</sup>                   | Min      | Тур | Max | Unit |

|------------------------|--------------------------------------------|----------|-----|-----|------|

| t <sub>36</sub>        | GPIO2 setup time                           | 10       |     |     | ns   |

|                        | GPIO2 hold time                            |          |     |     |      |

| t <sub>37</sub>        | High resolution mode                       | MCLK     |     |     | ns   |

| <b>t</b> <sub>37</sub> | Low power mode                             | 2 × MCLK |     |     |      |

| t <sub>38</sub>        | MCLK rising edge to GPIO1 rising edge time | 20       |     |     | ns   |

| t <sub>39</sub>        | GPIO0 hold time                            | MCLK     |     |     | ns   |

| t <sub>40</sub>        | GPIO0 setup time                           | 5        |     |     | ns   |

<sup>1</sup> AVSSx refers to the following pins: AVSS1A, AVSS1B, AVSS2A, AVSS2B, AVSS3 and AVSS4. This term is used throughout the data sheet.

<sup>&</sup>lt;sup>2</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of IOVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

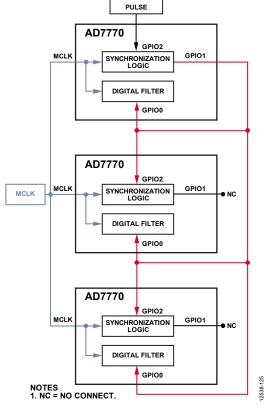

Figure 6. GPIOs for SRC Update Timing Diagram

<sup>&</sup>lt;sup>2</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of IOVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

## **ABSOLUTE MAXIMUM RATINGS**

Table 7

| Table 7.                                        |                                                               |

|-------------------------------------------------|---------------------------------------------------------------|

| Parameter                                       | Rating                                                        |

| Any Supply Pin to AVSSx                         | -0.3 V to +3.96 V                                             |

| AVSSx to DGND                                   | –1.98 V to +0.3 V                                             |

| AREGxCAP to AVSSx                               | −0.3 V to +1.98 V                                             |

| DREGCAP to DGND                                 | −0.3 V to +1.98 V                                             |

| IOVDD to DGND                                   | −0.3 V to +3.96 V                                             |

| IOVDD to AVSSx                                  | −0.3 V to +5.94 V                                             |

| AVDD4 to AVSSx                                  | AVDD1x - 0.3 V to 3.96 V                                      |

| Analog Input Voltage                            | AVSSx – 0.3 V to AVDD1x + 0.3 V or 3.96 V (whichever is less) |

| REFx± Input Voltage                             | AVSSx – 0.3 V to AVDD1x + 0.3 V or 3.96 V (whichever is less) |

| AUXAIN±                                         | AVSSx – 0.3 V to AVDD4 + 0.3 V or 3.96 V (whichever is less)  |

| Digital Input Voltage to<br>DGND                | DGND – 0.3 V to IOVDD + 0.3 V or 3.96 V (whichever is less)   |

| Digital Output Voltage to<br>DGND               | DGND – 0.3 V to IOVDD + 0.3 V or 3.96 V (whichever is less)   |

| XTAL1 to DGND                                   | DGND – 0.3 V to DREGCAP + 0.3 V or 1.98 V (whichever is less) |

| AINx±, AUXAIN±, and<br>Digital Input Current    | ±10 mA                                                        |

| Operating Temperature<br>Range                  | −40°C to +125°C                                               |

| Junction Temperature,<br>T <sub>J</sub> Maximum | 150°C                                                         |

| Storage Temperature Range                       | −65°C to +150°C                                               |

| Reflow Soldering                                | 260°C                                                         |

| ESD                                             | 2 kV                                                          |

| Field Induced Charged<br>Device Model (FICDM)   | 500 V                                                         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

**Table 8. Thermal Resistance**

| Package Type <sup>1</sup> | θја   | <b>Ө</b> лв | Ψл   | $\Psi_{JB}$ | Unit |

|---------------------------|-------|-------------|------|-------------|------|

| 64-Lead LFCSP             |       |             |      |             |      |

| No Thermal Vias           | 30.43 | $N/A^2$     | 0.13 | 6.59        | °C/W |

| 49 Thermal Vias           | 22.62 | 3.17        | 0.09 | 3.19        | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board. See JEDEC JESD51.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> N/A means not applicable.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 7. Pin Configuration

**Table 9. Pin Function Descriptions**

| Pin No. | Mnemonic    | Туре         | Direction | Description                                                                                                                                                              |

|---------|-------------|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AIN0-       | Analog input | Input     | Analog Input Channel 0, Negative.                                                                                                                                        |

| 2       | AIN0+       | Analog input | Input     | Analog Input Channel 0, Positive.                                                                                                                                        |

| 3       | AIN1-       | Analog input | Input     | Analog Input Channel 1, Negative.                                                                                                                                        |

| 4       | AIN1+       | Analog input | Input     | Analog Input Channel 1, Positive.                                                                                                                                        |

| 5       | AVSS1A      | Supply       | Supply    | Negative Front-End Analog Supply for Channel 0 to Channel 3, Typical at –1.65 V (Dual Supply) or AGND (Single Supply). Connect all the AVSSx pins to the same potential. |

| 6       | AVDD1A      | Supply       | Supply    | Positive Front-End Analog Supply for Channel 0 to Channel 3, Typical at AVSSx + 3.3 V. Connect this pin to AVDD1B.                                                       |

| 7       | REF1-       | Reference    | Input     | Negative Reference Input 1 for Channel 0 to Channel 3, Typical at AVSSx. Connect all the REFx— pins to the same potential.                                               |

| 8       | REF1+       | Reference    | Input     | Positive Reference Input 1 for Channel 0 to Channel 3, Typical at REF1 – + 2.5 V.                                                                                        |

| 9       | AIN2-       | Analog input | Input     | Analog Input Channel 2, Negative.                                                                                                                                        |

| 10      | AIN2+       | Analog input | Input     | Analog Input Channel 2, Positive.                                                                                                                                        |

| 11      | AIN3-       | Analog input | Input     | Analog Input Channel 3, Negative.                                                                                                                                        |

| 12      | AIN3+       | Analog input | Input     | Analog Input Channel 3, Positive.                                                                                                                                        |

| 13      | MODE0/GPIO0 | Digital I/O  | I/O       | Mode 0 Input in Pin Control Mode (MODE0). See Table 14 for more details.                                                                                                 |

|         |             |              |           | Configurable General-Purpose Input/Output 0 in SPI Control Mode (GPIO0). If not in use, connect this pin to DGND or IOVDD.                                               |

| 14      | MODE1/GPIO1 | Digital I/O  | I/O       | Mode 1 Input in Pin Control Mode (MODE1). See Table 14 for more details.                                                                                                 |

|         |             |              |           | Configurable General-Purpose Input/Output 1 in SPI Control Mode (GPIO1). If not in use, connect this pin to DGND or IOVDD.                                               |

| Pin No.        | Mnemonic       | Туре           | Direction | Description                                                                                                                                                                                                                                                                                                          |

|----------------|----------------|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15             | MODE2/GPIO2    | Digital I/O    | I/O       | Mode 2 Input in Pin Control Mode (MODE2). See Table 14 for more details.                                                                                                                                                                                                                                             |

|                |                |                |           | Configurable General-Purpose Input/Output 2 in SPI Control Mode (GPIO2). If not in use, connect this pin to DGND or IOVDD.                                                                                                                                                                                           |

| 16             | MODE3/ALERT    | Digital I/O    | I/O       | Mode 3 Input in Pin Control Mode (MODE3). See Table 14 for more details.  Alert Output in SPI Control Mode (ALERT).                                                                                                                                                                                                  |

| 17             | CONVST_SAR     | Digital input  | Input     | $\Sigma$ - $\Delta$ Output Interface Selection Pin in Pin Control Mode. See Table 13 for more details. This pin also functions as the start for the SAR conversion in SPI control mode.                                                                                                                              |

| 18             | ALERT/CS       | Digital input  | Input     | Alert Output in Pin Control Mode (ALERT). Chip Select in SPI Control Mode ( $\overline{\text{CS}}$ ).                                                                                                                                                                                                                |

| 19             | DCLK2/SCLK     | Digital input  | Input     | DCLK Frequency Selection Pin 2 in Pin Control Mode (DCLK2). See Table 15 for more details.                                                                                                                                                                                                                           |

| 20             | DCLK1/SDI      | Digital input  | Input     | SPI Clock in SPI Control Mode (SCLK).  DCLK Frequency Selection Pin 1 in Pin Control Mode (DCLK1). See Table 15 for more details.                                                                                                                                                                                    |

| 21             | DCLK0/SDO      | Digital output | Output    | SPI Data Input in SPI Control Mode (SDI). Connect this pin to DGND if the device is configured in pin control mode with the SPI as the data output interface. DCLK Frequency Selection Pin 0 in Pin Control Mode (DCLKO). See Table 15 for                                                                           |

|                |                |                |           | more details.  SPI Data Output in SPI Control Mode (SDO).                                                                                                                                                                                                                                                            |

| 22             | DGND           | Supply         | Supply    | Digital Ground.                                                                                                                                                                                                                                                                                                      |

| 23             | DREGCAP        | Supply         | Output    | Digital Low Dropout (LDO) Output. Decouple this pin to DGND with a 1 $\mu$ F capacitor.                                                                                                                                                                                                                              |

| 24             | IOVDD          | Supply         | Supply    | Digital Levels Input/Output and Digital LDO (DLDO) Supply from 1.8 V to 3.6 V. IOVDD must not be lower than DREGCAP.                                                                                                                                                                                                 |

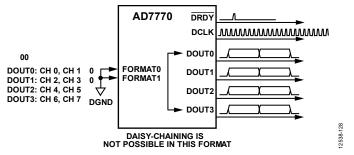

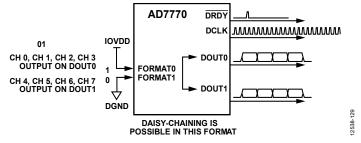

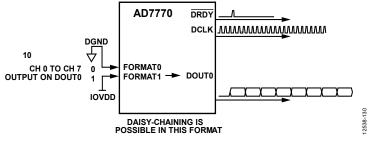

| 25             | DOUT3          | Digital output | I/O       | Data Output Pin 3. If the device is configured in daisy-chain mode, this pin acts as an input pin. See the Daisy-Chain Mode section for more details.                                                                                                                                                                |

| 26             | DOUT2          | Digital output | I/O       | Data Output Pin 2. If the device is configured in daisy-chain mode, this pin acts as an input pin. See the Daisy-Chain Mode section for more details.                                                                                                                                                                |

| 27             | DOUT1          | Digital output | Output    | Data Output Pin 1.                                                                                                                                                                                                                                                                                                   |

| 28             | DOUT0          | Digital output | Output    | Data Output Pin 0.                                                                                                                                                                                                                                                                                                   |

| 29             | DCLK           | Digital output | Output    | Data Output Clock.                                                                                                                                                                                                                                                                                                   |

| 30             | DRDY           | Digital output | Output    | Data Output Ready Pin.                                                                                                                                                                                                                                                                                               |

| 31             | XTAL1          | Clock          | Input     | Crystal 1 Input Connection. If CMOS is used as a clock source, tie this pin to DGND. See Table 12 for more details.                                                                                                                                                                                                  |

| 32             | XTAL2/MCLK     | Clock          | Input     | Crystal 2 Input Connection (XTAL2). See Table 12 for more details.  CMOS Clock (MCLK). See Table 12 for more details.                                                                                                                                                                                                |

| 33             | START          | Digital input  | Input     | Synchronization Pulse. This pin internally synchronizes an external START asynchronous pulse with MCLK. The synchronize signal is shifted out by the SYNC_OUT pin. If not in use, tie this pin to IOVDD. See the Phase Adjustment                                                                                    |

| 34             | SYNC_OUT       | Digital output | Input     | section and the Digital Reset and Synchronization Pins section for more details.  Synchronization Signal. This pin generates a synchronous pulse generated and driven by hardware (via the START pin) or by software (GENERAL_USER_CONFIG_2, Bit 0). If this pin is in use, it must be wired to the SYNC_IN pin. See |

|                |                |                |           | the Phase Adjustment section and the Digital Reset and Synchronization Pins                                                                                                                                                                                                                                          |

| 35             | SYNC_IN        | Digital input  | Input     | section for more details.  Reset for the Internal Digital Block and Synchronize for Multiple Devices. See the Digital Reset and Synchronization Pins section for more details.                                                                                                                                       |

| 36             | RESET          | Digital input  | Input     | Asynchronous Reset Pin. This pin resets all registers to their default value. It is recommended to generate a pulse on this pin after the device is powered up because a slow slew rate in the supplies may generate an incorrect                                                                                    |

| 27             | A1N17 :        | Apples         | lmmut     | initialization in the digital block.                                                                                                                                                                                                                                                                                 |

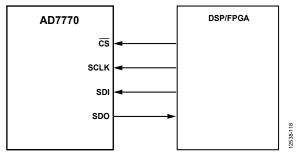

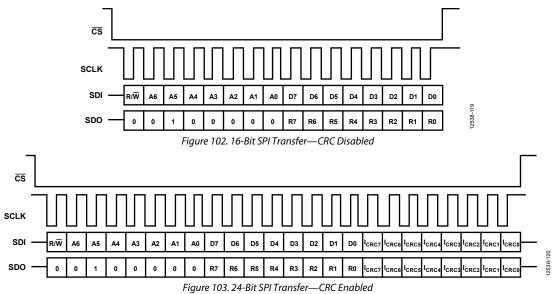

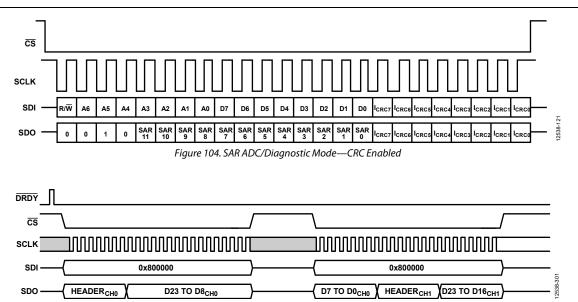

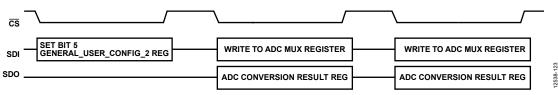

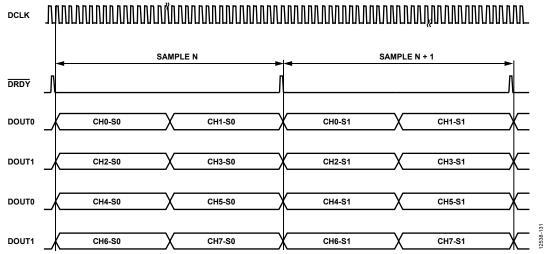

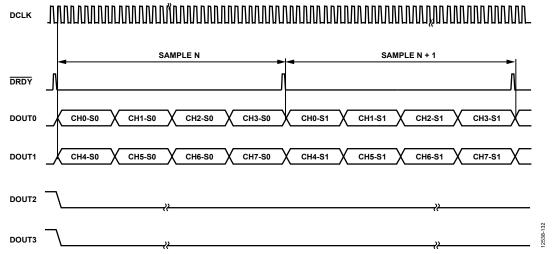

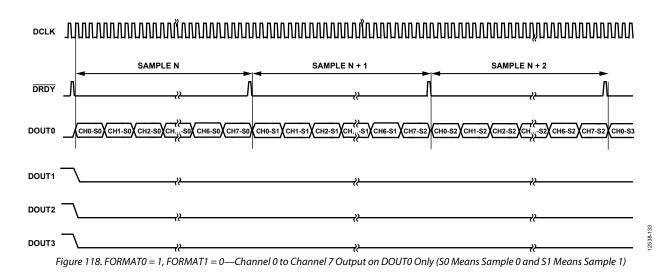

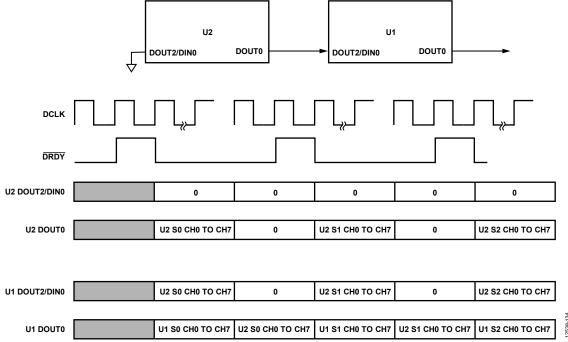

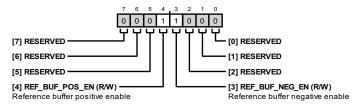

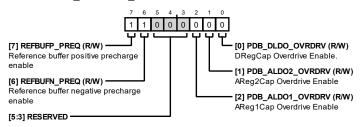

| 37<br>39       | AIN7+          | Analog input   | Input     | Analog Input Channel 7, Positive.                                                                                                                                                                                                                                                                                    |