# 1.0 Features

## **1.1 Time Synchronization Algorithm**

- External algorithm controls software digital PLL to adjust frequency & phase alignment

- Frequency, Phase and Time Synchronization over IP, MPLS and Ethernet Packet Networks

- Frequency accuracy performance for WCDMA-FDD, GSM, LTE-FDD and femtocell applications, with target performance less than ± 15 ppb.

- Frequency performance for ITU-T G.823 and G.824 synchronization interface, as well as G.8261 PNT EEC, PNT PEC and CES interface specifications.

- Phase Synchronization performance for WCDMA-TDD, Mobile WiMAX, TD-SCDMA and CDMA2000 applications with target performance less than  $\pm$  1  $\mu$ s phase alignment.

- Time Synchronization for UTC-traceability and GPS replacement.

- Client reference switching between multiple Servers

- Client holdover when Server packet connectivity is lost

## 1.2 Electrical Clock Engine

- Supports the requirements of ITU-T G.8262 for synchronous Ethernet Equipment slave Clocks (EEC option 1 and 2)

- Supports the requirements of Telcordia GR-1244 Stratum 3 and GR-253, ITU-T G.813, and G.781 SETS

- Supports ITU-T G.823, G.824 and G.8261 for 2048 kbit/s and 1544 kbit/s interfaces

- Meets the SONET/SDH jitter generation requirements up to OC-48/STM-16

- Synchronizes to telecom reference clocks (2 kHz, N\*8 kHz up to 77.76 MHz, 155.52 MHz) or to Ethernet reference clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz)

- Supports composite clock inputs (64 kHz, 64 kHz + 8 kHz, 64 kHz + 8 kHz + 400 Hz)

- Provides two DPLLs which are independently configurable through a serial interface

- Internal state machine automatically controls mode of operation (free-run, locked, holdover)

- Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities

- Supports master/slave configuration and dynamic input to output delay compensation for AdvancedTCA<sup>TM</sup>

- · Provides automatic reference switching and holdover during loss of reference input

#### 1.3 Electrical Clock Generation

- Generates standard SONET/SDH clock rates (e.g., 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, 622.08 MHz) or Ethernet clock rates (e.g., 25 MHz, 50 MHz, 125 MHz, 156.25 MHz, 312.5 MHz) for synchronizing Gigabit Ethernet PHYs

- Programmable output synthesizers (P0, P1) generate telecom clock frequencies from any multiple of 8 kHz up to 100 MHz

- Generates several styles of telecom frame pulses with selectable pulse width, polarity and frequency

- Configurable input to output delay and output to output phase alignment

## 1.4 API Software

- Interfaces to 1588-capable PHY and switches with integrated timestamping

- Abstraction layer for independence from OS and CPU, from embedded SoC to home-grown

- Fits into centralized, highly integrated pizza box architectures as well as distributed architectures with multiple line cards and timing cards

# 2.0 Applications

- ITU-T G.8262 System Timing Cards which support 1 GbE and 10 GbE interfaces

- Telcordia GR-253 Carrier Grade SONET/SDH Stratum 3 System Timing Cards

- System Timing Cards which supports ITU-T G.781 SETS (SDH Equipment Timing Source)

- Integrated basestation reference clock for air interface for GSM, WCDMA, LTE and WiMAX macro, micro or femtocells

- Mobile Backhaul NID, edge router or access aggregation node

- EPON/GE-PON & GPON OLT

- EPON/GE-PON & GPON ONU/OLT

- DSLAM and RT-DSLAM

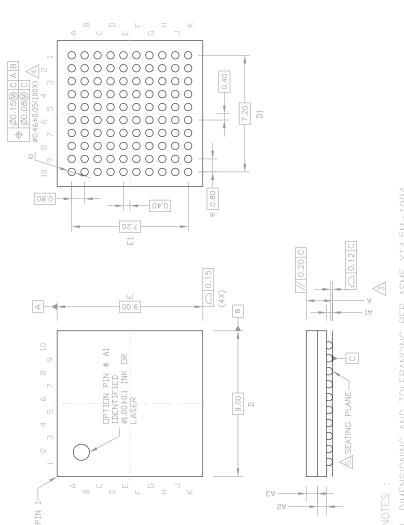

|            | MAX    | .069 | .016 | .024 | .029 | .020 | .358 | C        | .358 | D        | C        |

|------------|--------|------|------|------|------|------|------|----------|------|----------|----------|

| H          | NOM    | .064 | .014 | .022 | .028 | .018 | .354 | 283 BSC  | .354 | 283 BSC  | .020 BSC |

| INCH       | MIN    | .059 | .012 | .020 | .026 | .016 | .350 | N.       | .350 | N.       | 0.       |

|            | MAX    | 1.72 | 0.41 | 0.61 | 0.75 | 0.51 | 9.10 | с<br>С   | 9.10 | U<br>U   | 7)       |

| MILLIMETER | NOM    | 1.62 | 0.36 | 0.56 | 0.70 | 0.46 | 9.00 | 7.20 BSC | 9.00 | 7.20 BSC | 0.8 BSC  |

| MIL        | MIN    | 1.52 | 0.31 | 0.51 | 0.65 | 0.41 | 8.90 | 2.       | 8.90 | ~        | 0        |

|            | SYMBUL | A    | A1   | A2   | A3   | p    | D    | D1       | ы    | E1       | e        |

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- HEATSINK OR CHIP CAPACITORS. AN INTEGRAL HEATSLUG IS NOT CONSIDERED AN

- DIMENSION IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, <<u>+</u>

- PRIMARY DATUM C AND SEATING PLANE ARE DEFINED BY THE SPHERICAL

|                                              | DWG. NO.      | REV. |

|----------------------------------------------|---------------|------|

| MICROSEMI UMPU                               | CDCA# 22-0055 | 10   |

| TITLE                                        | 84-06-128-304 | 5    |

| 100L LFBGA PACKAGE OUTLINE                   | warman        | -    |

| VALU 100 1 V V V V V V V V V V V V V V V V V | DIBBI         | 9770 |

| BUUT SIZE 39 X 9 XI.5ZMM MAX<br>PITCH 1.0MM  | 1 OF 1        | A4   |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.