| Product Line | Ordering Part Number               | Product Status                         | Reference PCN     |

|--------------|------------------------------------|----------------------------------------|-------------------|

|              | LX256C-35F484C                     |                                        |                   |

| LX256C       | LX256C-35FN484C                    | Discontinued                           | PCN#09-10         |

| LAZJOC       | LX256C-5F484C                      | Discontinued                           | <u>FCIN#09-10</u> |

|              | LX256C-5FN484C                     |                                        |                   |

|              | LX64EV-3F100C                      |                                        |                   |

|              | LX64EV-3FN100C                     |                                        |                   |

|              | LX64EV-5F100C                      |                                        |                   |

| LX64EV       | LX64EV-5F100I                      | Active / Orderable                     |                   |

|              | LX64EV-5FN100C                     | _                                      |                   |

|              | LX64EV-5FN100I                     | _                                      |                   |

|              | LX64EB-3F100C                      |                                        |                   |

|              | LX64EB-3FN100C                     | _                                      |                   |

|              | LX64EB-5F100C                      |                                        |                   |

| LX64EB       | LX64EB-5F100I                      | Discontinued                           | <u>PCN#09-10</u>  |

|              | LX64EB-5FN100C                     | _                                      |                   |

|              | LX64EB-5FN100I                     | -                                      |                   |

|              | LX64EC-3F100C                      |                                        |                   |

|              | LX64EC-3FN100C                     | -                                      |                   |

|              | LX64EC-5F100C                      | -                                      |                   |

| LX64EC       | LX64EC-5F100I                      | <ul> <li>Discontinued</li> </ul>       | <u>PCN#09-10</u>  |

|              | LX64EC-5FN100C                     | -                                      |                   |

|              | LX64EC-5FN100I                     | -                                      |                   |

|              | LX128EV-32F208C                    |                                        |                   |

|              | LX128EV-32FN208C                   | -                                      |                   |

|              | LX128EV-5F208C                     | -                                      |                   |

| LX128EV      | LX128EV-5F208I                     | <ul> <li>Active / Orderable</li> </ul> |                   |

|              | LX128EV-5FN208C                    |                                        |                   |

|              | LX128EV-5FN208I                    |                                        |                   |

|              | LX128EB-32F208C                    |                                        |                   |

|              | LX128EB-32FN208C                   | _                                      |                   |

|              | LX128EB-5F208C                     | _                                      |                   |

| LX128EB      | LX128EB-5F2080                     | <ul> <li>Discontinued</li> </ul>       | PCN#09-10         |

|              |                                    | _                                      |                   |

|              | LX128EB-5FN208C                    | _                                      |                   |

|              | LX128EB-5FN208I<br>LX128EC-32F208C |                                        |                   |

|              |                                    | _                                      |                   |

|              | LX128EC-32FN208C                   | _                                      |                   |

| LX128EC      | LX128EC-5F208C                     | Discontinued                           | PCN#09-10         |

|              | LX128EC-5F208I                     | _                                      |                   |

|              | LX128EC-5FN208C                    | _                                      |                   |

|              | LX128EC-5FN208I                    |                                        |                   |

|              | LX256EV-35F484C                    | _                                      |                   |

|              | LX256EV-35FN484C                   | 4                                      |                   |

| LX256EV      | LX256EV-5F484C                     | Active / Orderable                     |                   |

|              | LX256EV-5F484I                     | _                                      |                   |

|              | LX256EV-5FN484C                    | _                                      |                   |

|              | LX256EV-5FN484I                    |                                        |                   |

| Product Line | Ordering Part Number | Product Status | Reference PCN             |  |

|--------------|----------------------|----------------|---------------------------|--|

|              | LX256EB-35F484C      |                |                           |  |

|              | LX256EB-35FN484C     |                |                           |  |

| LX256EB      | LX256EB-5F484C       | Discontinued   | ontinued <u>PCN#09-10</u> |  |

| LAZJUED      | LX256EB-5F484I       | Discontinued   | <u>FCIN#09-10</u>         |  |

|              | LX256EB-5FN484C      |                |                           |  |

|              | LX256EB-5FN484I      |                |                           |  |

|              | LX256EC-35F484C      |                |                           |  |

|              | LX256EC-35FN484C     |                |                           |  |

| LX256EC      | LX256EC-5F484C       | Discontinued   | PCN#09-10                 |  |

| LAZJOEC      | LX256EC-5F484I       | Discontinued   | <u>FCIN#09-10</u>         |  |

|              | LX256EC-5FN484C      |                |                           |  |

|              | LX256EC-5FN484I      |                |                           |  |

Downloaded from Arrow.com.

### September 2005

### Features

- High bandwidth

- Up to 12.8 Gbps (SERDES)

- Up to 38 Gbps (without SERDES)

- Up to 16 (15x10) FIFOs for data buffering

- · High speed performance

- f<sub>MAX</sub> = 360MHz

- t<sub>PD</sub> = 3.0ns

- t<sub>CO</sub> = 2.9ns

- t<sub>S</sub> = 2.0ns

- Built-in programmable control logic capability

- I/O intensive: 64 to 256 I/Os

- Expanded MUX capability up to 188:1 MUX

### ■ sysCLOCK<sup>™</sup> PLL

- Frequency synthesis and skew management

- Clock multiply and divide capability

- Clock shifting up to +/-2.35ns in 335ps steps

- Up to four PLLs

### ■ sysIO<sup>™</sup> Interfacing

- LVCMOS 1.8, 2.5, 3.3 and LVTTL support for standard board interfaces

- SSTL 2/3 Class I and II support

- HSTL Class I, III and IV support

- GTL+, PCI-X for bus interfaces

- LVPECL, LVDS and Bus LVDS differential support

- Hot socketing

- Programmable drive strength

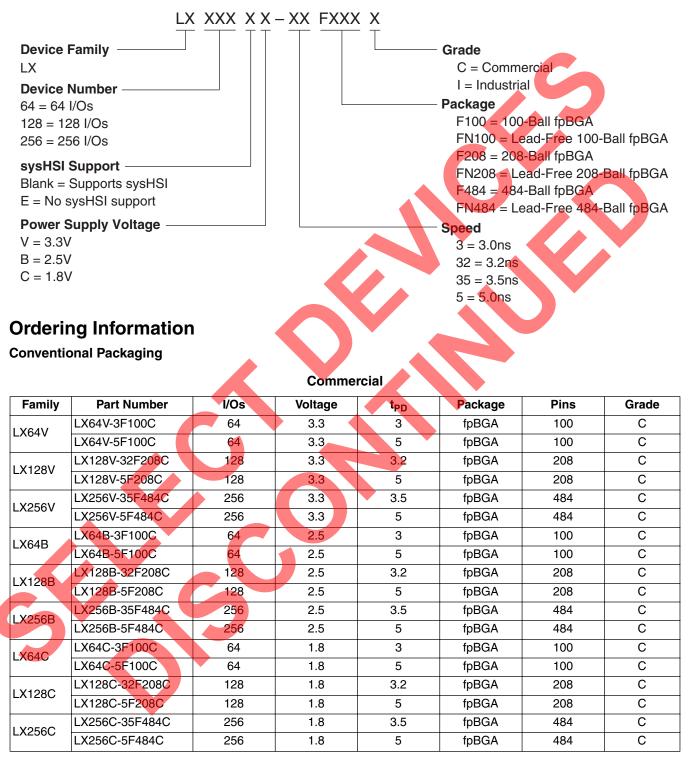

### Table 1. ispGDX2 Family Selection Guide

High Performance Interfacing and Switching

### Data Sheet

### **Two Options Available**

- High-performance sysHSI (standard part number)

- Low-cost, no sysHSI ("E-Series")

- sysHSI Blocks Provide up to 16 High-speed Channels

- Serializer/de-serializer (SERDES) included

- Clock Data Recovery (CDR) built in

- 800 Mbps per channel

- LVDS differential support

- 10B/12B support

- Encoding / decoding

- Bit alignment

- Symbol alignment

- 8B/10B support

- Bit alignment

- Symbol alignment

- Source Synchronous support

### Flexible Programming and Testing

- IEEE 1532 compliant In-System Programmability (ISP™)

- Boundary scan test through IEEE 1149.1 interface

- 3.3V, 2.5V or 1.8V power supplies

- 5V tolerant I/O for LVCMOS 3.3 and LVTTL interfaces

|                              |                        | isp <mark>GD</mark> X2-64/E | ispGDX2-128/E  | ispGDX2-256/E  |

|------------------------------|------------------------|-----------------------------|----------------|----------------|

| I/Os                         |                        | 64                          | 128            | 256            |

| GDX Blocks                   |                        | 4                           | 8              | 16             |

| t <sub>PD</sub>              |                        | 3.0ns                       | 3.2ns          | 3.5ns          |

| ts                           |                        | 2.0ns                       | 2.0ns          | 2.0ns          |

| t <sub>CO</sub>              |                        | 2.9ns                       | 3.1ns          | 3.2ns          |

| f <sub>MAX</sub> (Toggle)    |                        | 360MHz                      | 330MHz         | 300MHz         |

| Max Bandwidth                | SERDES <sup>1, 2</sup> | 3.2Gbps                     | 6.4Gbps        | 12.8Gbps       |

| Max Danuwiulin               | Without SERDI          | ES <sup>3</sup> 11Gbps      | 21Gbps         | 38Gbps         |

| sysHSI Channels <sup>2</sup> |                        | 4                           | 8              | 16             |

| LVDS/Bus LVDS (F             | airs)                  | 32                          | 64             | 128            |

| PLLs                         |                        | 2                           | 2              | 4              |

| Package                      |                        | 100-ball fpBGA              | 208-ball fpBGA | 484-ball fpBGA |

|                              |                        |                             |                |                |

1. Max number of SERDES channels per device \* 800Mbps

- 2. "E-Series" does not support sysHSI.

- 3. f<sub>MAX</sub> (Toggle) \* maximum I/Os divided by 2.

© 2005 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

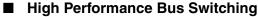

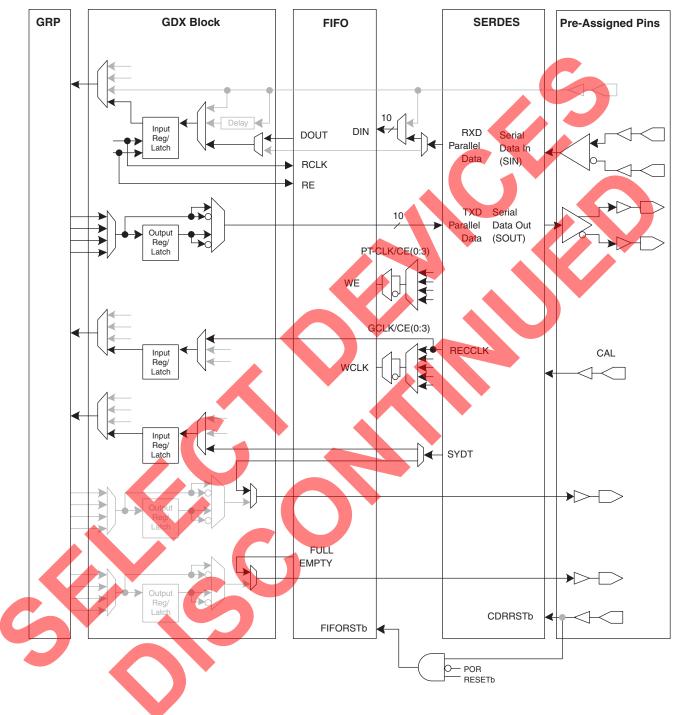

Figure 1. ispGDX2 Block Diagram (256-I/O Device)

# Introduction

The ispGDX2<sup>™</sup> family is Lattice's second generation in-system programmable generic digital crosspoint switch for high speed bus switching and interface applications.

The ispGDX2 family is available in two options. The standard device supports sysHSI capability for ultra fast serial communications while the lower-cost "E-series" supports the same high-performance FPGA fabric without the sysHSI Block.

This family of switches combines a flexible switching architecture with advanced sysIO interfaces including high performance sysHSI Blocks, and sysCLOCK PLLs to meet the needs of the today's high-speed systems. Through a muliplexer-intensive architecture, the ispGDX2 facilitates a variety of common switching functions.

The availability of on-chip control logic further enhances the power of these devices. A high-performance solution, the family supports bandwidth up to 38Gbps.

Every device in the family has a number of PLLs to provide the system designer with the ability to generate multiple clocks and manage clock skews in their systems.

The sysIO interfaces provide system-level performance and integration. These I/Os support various modes of LVCMOS/LVTTL and support popular high-speed standard interfaces such as GTL+, PCI-X, HSTL, SSTL, LVDS and Bus-LVDS. The sysHSI Blocks further extend this capability by providing high speed serial data transfer capability.

Devices in the family can operate at 3.3V, 2.5V or 1.8V core voltages and can be programmed in-system via an IEEE 1149.1 interface that is compliant with the IEEE 1532 standard. Voltages required for the I/O buffers are independent of the core voltage supply. This further enhances the flexibility of this family in system designs.

Typical applications for the ispGDX2 include multi-port multi-processor interfaces, wide data and address bus multiplexing, programmable control signal routing and programmable bus interfaces. Table 1 shows the members of the ispGDX2 family and their key features.

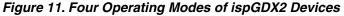

# Architecture

The ispGDX2 devices consist of GDX Blocks interconnected by a Global Routing Pool (GRP). Signals interface with the external system via sysIO banks. In addition, each GDX Block is associated with a FIFO and a sysHSI Block to facilitate the transfer of data on- and off-chip. Figure 1 shows the ispGDX2 block diagram. Each GDX Block can be individually configured in one of four modes:

- Basic (No FIFO or SERDES)

- FIFO Only

- SERDES Only

- SERDES and FIFO

Each sysIO bank has its own I/O power supply and reference voltage. Designers can use any output standard within a bank that is compatible with the power supply. Any input standard may be used, providing it is compatible with the reference voltage. The banks are independent.

# Global Routing Pool (GRP)

The ispGDX2 architecture is organized into GDX Blocks, which are connected via a Global Routing Pool. The innovative GRP is optimized for routability, flexibility and speed. All the signals enter via the GDX Block. The block supplies these either directly or in registered form to the GRP. The GRP routes the signals to different blocks, and provides separate data and control routing. The data path is optimized to achieve faster speed and routing flexibility for nibble oriented signals. The control routing is optimized to provide high-speed bit oriented routing of control signals.

There are some restrictions on the allocation of pins for optimal bus routing. These restrictions are considered by the software in the allocation of pins.

## GDX Block

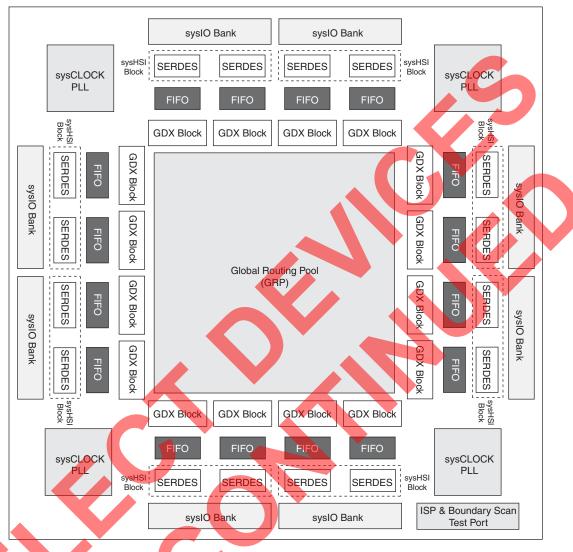

The blocks are organized in a "block" (nibble) manner, with each GDX Block providing data flow and control logic for 16 I/O buffers. The data flow is organized as four nibbles, each nibble containing four Multiplexer Register Blocks (MRBs). Data for the MRBs is provided from 64 lines from the GRP. Figure 2 illustrates the groups of signals going into and out of a GDX Block.

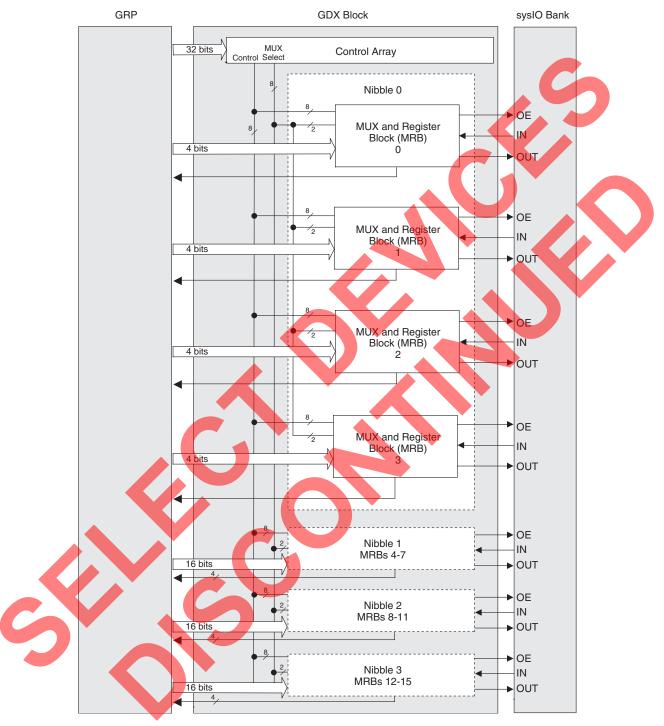

Control signals for the MRBs are provided from the Control Array. The Control Array receives the 32 signals from the GRP and generates 16 control signals: eight MUX Select, four Clock/Clock Enable, two Set/Reset and two Output Enable. Each nibble is controlled via two MUX select signals. The remaining control signals go to all the MRBs.

Besides the control signals from the Control Array, the following global signals are available to the MRBs in each GDX Block: four Clock/Clock Enable, one reset/preset, one power-on reset, two of four MUX select (two of two in 64 I/O), four Output Enable (two in 64 I/O) and Test Out Enable (TOE).

### MUX and Register Block (MRB)

Every MRB Block has a 4:1 MUX (I/O MUX) and a set of three registers which are connected to the I/O buffers, FIFO and sysHSI Blocks. Multiple MRBs can be combined to form large multiplexers as described below. Figure 3 shows the structure of the MRB.

Each of the three registers in the MRB can be configured as edge-triggered D-type flip-flop or as a level sensitive latch. One register operates on the input data, the other output data and the last register synchronizes the output enable function. The input and output data signals can bypass each of their registers. The polarity of the data out and output enable signals can be selected.

The Output and OE register share the same clock and clock enable signals. The Input register has a separate clock and clock enable. The initialization signals of each register can be independently configured as Set or Reset. These registers have programmable polarity control for Clock, Clock Enable and Set/Reset. The output enable register input can be set either by one of the two output enables generated locally from the Control Array or from one of the four (two in 64 I/O) Global OE enable pins. In addition to the local clock and clock enable signals, each MRB has access to Global Clock, Clock Enable, Reset and TOE nets.

### Figure 2. GDX Block

The output register of the MRB has a built-in bi-directional shift register capability. Each output register corresponding to MRB "n", receives data output from its two adjacent MRBs, MRB (n-1) and MRB (n+1), to provide shift register capability. Like the output register, each input register of the MRB has built-in shift register capability. Each input register can receive data from its two adjacent MRB input registers, to provide bi-directional shift register capability. The chaining crosses GDX Block boundaries. The chain of input registers and the chain of output registers can be combined as one shift register via the GRP.

### Lattice Semiconductor

The four data inputs to the 4:1 MUX come from the GRP. The output of this MUX connects to the output register. A fast feedback path from the MUX to the GRP allows wider MUXes to be built. Table 2 summarizes the various MUX sizes and delay levels.

### Table 2. MUX Size Versus Internal Delay

| MUX Sizes                      | Levels of Internal GRP Delays | 0 |

|--------------------------------|-------------------------------|---|

| 4:1                            | One Level                     |   |

| Up to 16:1                     | Two Levels                    |   |

| Up to 64:1                     | Three Levels                  |   |

| Up to 188:1 (with ispGDX2-256) | Four Levels                   |   |

### Figure 3. ispGDX2 Family MRB Global GDX Signals Control Array MUX Select **Control Array Signals** 4 2 0 CK/CE В MUX CIK OE Select Reg/Latch Global Signals CE Flags\* Vcc (FIFO, SERDES or PLL) Reset CK/CE from Out\_Reg(n-1) From GRP ШО Q to Out\_Reg(n-1) fron Out\_Reg(n+1) - to Out\_Reg(n+1 CIK Out Reg/Latch CF Vcc Global Resetb Ŀ to IN\_Reg(n-1) FIFO Ou from IN\_Reg(n from IN\_Reg(nto IN\_Reg(n+1) D/L Q CIK Input CK Reg/Latch Global Resetb

\*Selected MRBs see Logic Signal Connection Table for details

## **Control Array**

The control array generates control signals for the 16 MRBs within a GDX Block. The true and complement forms of 32 inputs from the GRP are available in the control array. The 20 NAND terms can use any or all of these inputs to form the control array outputs. Two AND terms are combined with a NOR term to form Set/Reset and OE signals. Figure 4 illustrates the control array.

### Figure 4. ispGDX2 Family Control Array

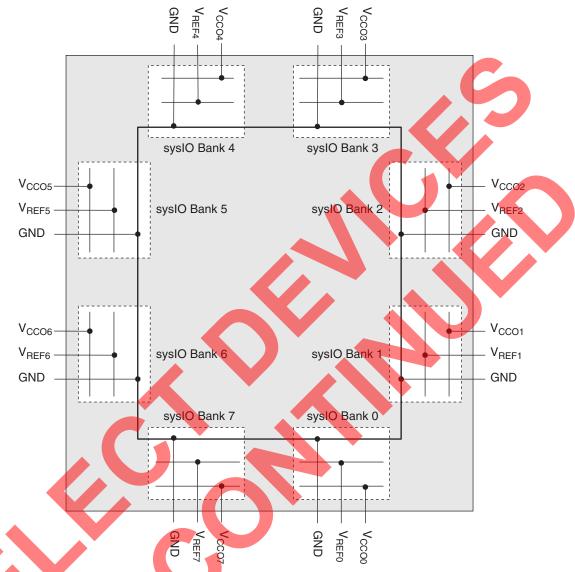

### sysIO Banks

The inputs and outputs of ispGDX2 devices are divided into eight sysIO banks, where each bank is capable of supporting different I/O standards. The number of I/Os per bank is 32, 16 and 8 for the 256-, 128- and 64-I/O devices respectively. Each sysIO bank has its own I/O supply voltage ( $V_{CCO}$ ) and reference voltage ( $V_{REF}$ ), allowing each bank complete independence from the other banks. Each I/O within a bank can be individually configured to any standard consistent with the  $V_{CCO}$  and  $V_{REF}$  settings. Figure 5 shows the I/O banks for the ispGDX2-256 device.

The I/O of the ispGDX2 devices contain a programmable strength and slew rate tri-state output buffer, a programmable pull-up resistor, a programmable pull-down resistor and a programmable buskeeper latch. These programmable capabilities allow the support of a wide range of I/O standards.

### Figure 5. ispGDX2-256 sysIO Banks

There are three classes of I/O interface standards implemented in the ispGDX2 devices. The first is the non-terminated, single-ended interface; it includes the 3.3V LVTTL standard along with the 1.8V, 2.5V and 3.3V LVCMOS interface standards. The slew rate and strength of these output buffers can be controlled individually. Additionally, PCI 3.3, PCI-X and AGP-1X are all subsets of this interface type. The second interface class implemented is the terminated, single-ended interface standard. This group of interfaces includes different versions of SSTL and HSTL interfaces along with CTT and GTL+. Use of these I/O interfaces requires an additional V<sub>REF</sub> signal. At the system level, a termination voltage, V<sub>TT</sub>, is also required. Typically, an output will be terminated to V<sub>TT</sub> at the receiving end of the transmission line it is driving. The final types of interfaces implemented are the differential standards LVPECL, LVDS and Bus LVDS. Table 3 shows the I/O standards supported by the ispGDX2 devices along with nominal V<sub>CCO</sub>, V<sub>REF</sub> and V<sub>TT</sub>.

The ispGDX2 family also features 5V tolerant I/O. I/O banks with  $V_{CCO} = 3.3V$  may have inputs driven to a maximum of 5.5V for easy interfacing with legacy systems. Up to 64 I/O pins per device may be driven by 5V inputs.

### Table 3. ispGDX2 Supported I/O Standards

| sysIO Standard            | Nominal V <sub>CCO</sub> | Nominal V <sub>REF</sub> | Nominal V <sub>TT</sub> |

|---------------------------|--------------------------|--------------------------|-------------------------|

| LVCMOS 3.3                | 3.3V                     | —                        | —                       |

| LVCMOS 2.5                | 2.5V                     | —                        | _                       |

| LVCMOS 1.8                | 1.8V                     | _                        | -                       |

| LVTTL                     | 3.3V                     | _                        |                         |

| PCI 3.3                   | 3.3V                     | -                        |                         |

| PCI -X                    | 3.3V                     |                          | -                       |

| AGP-1X                    | 3.3V                     | -                        | -                       |

| SSTL3 class I & II        | 3.3V                     | 1.5V                     | 1.5V                    |

| SSTL2 class I & II        | 2.5V                     | 1.25V                    | 1.25V                   |

| CTT 3.3                   | 3.3V                     | 1.5V                     | 1.5V                    |

| CTT 2.5                   | 2.5V                     | 1.25V                    | 1.25V                   |

| HSTL class I              | 1.5V                     | 0.75V                    | 0.75V                   |

| HSTL class III            | 1.5V                     | 0.9V                     | 0.75V                   |

| HSTL class IV             | 1.5V                     | 0.9V                     | 1.5V                    |

| GTL+                      | 1.8/2.5/3.3V             | 1.0V                     | 1.5V                    |

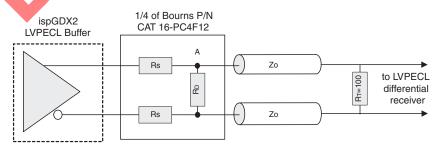

| LVPECL <sup>1, 2, 3</sup> | 3.3V                     |                          | -                       |

| LVDS                      | 2.5/3.3V                 | -                        | -                       |

| Bus-LVDS                  | 2.5/3.3V                 |                          | —                       |

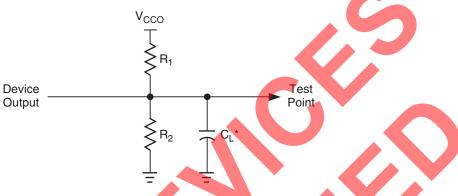

1. LVPECL drivers require three resistor pack (see Figure 17).

2. Depending on the driving LVPECL output specification, GDX2 LVPECL input driver may require terminating resistors.

3. For additional information on LVPECL refer to Lattice technical note number TN1000, sysIO Design and Usage Guidelines.

The dedicated inputs support a subset of the sysIO standards indicated in Table 4. These inputs are associated with a bank consistent with their location.

### Table 4. I/O Standards Supported by Dedicated Inputs

|                                | LVCMOS           | LVDS | All other ASIC I/Os |

|--------------------------------|------------------|------|---------------------|

| Global OE Pins                 | Yes              | No   | Yes <sup>2</sup>    |

| Global MUX Select Pins         | Yes              | No   | Yes <sup>2</sup>    |

| Resetb                         | Yes              | No   | Yes <sup>2</sup>    |

| Global Clock/Clock Enables     | Yes              | Yes  | Yes <sup>2</sup>    |

| ispJTAG™ Port                  | Yes <sup>1</sup> | No   | No                  |

| TOE                            | Yes              | No   | No                  |

| 1 LVCMOS as defined by the Voo | nin voltage      |      | •                   |

LVCMOS as defined by the V<sub>CCJ</sub> pin voltage

2. No PCI clamp.

For more information on the sysIO capability, please refer to Lattice technical note number TN1000, sysIO Design and Usage Guidelines.

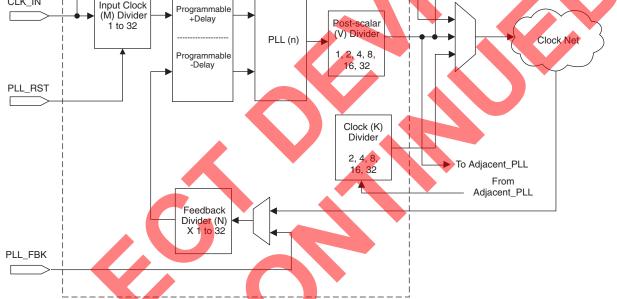

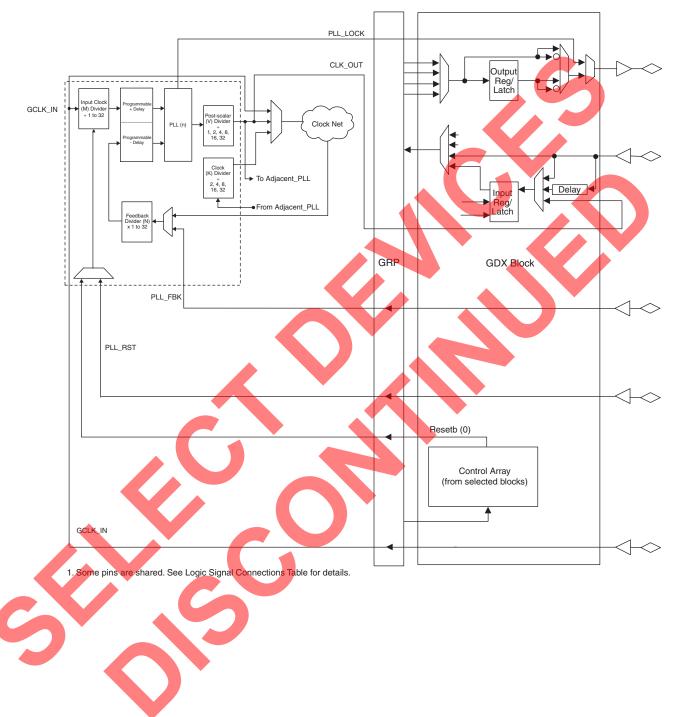

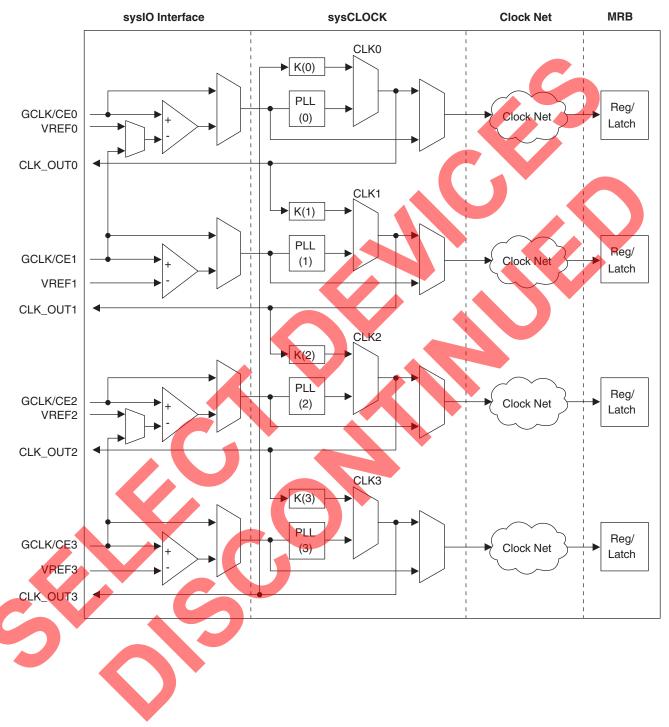

### sysCLOCK PLL

The sysCLOCK PLL circuitry consists of Phase-Lock Loops (PLLs) along the various dividers and reset and feedback signals associated with the PLLs. This feature gives the user the ability to synthesize clock frequencies and generate multiple clock signals for routing within the device. Furthermore, it can generate clock signals that are deskewed either at the board level or the device level. Figure 6 shows the ispGDX2 PLL block diagram.

Each PLL has a set of PLL\_RST, PLL\_FBK and PLL\_LOCK signals. In order to facilitate the multiply and divide capabilities of the PLL, each PLL has associated dividers. The M divider is used to divide the clock signal, while the

### Lattice Semiconductor

PLL\_LOCK

CLK\_OUT

N divider is used to multiply the clock signal. The K divider is used to provide a divided clock frequency of the adjacent PLL. This output can be routed to the global clock net. The V divider is used to provide lower frequency output clocks, while maintaining a stable, high frequency output from the PLL's VCO circuit. The PLL also has a delay feature that allows the output clock to be advanced or delayed to improve set-up and clock-to-out times for better performance. For more information on the PLL, please refer to Lattice technical note number TN1003, *sysCLOCK PLL Design and Usage Guidelines.*

# Figure 6. sysCLOCK PLL

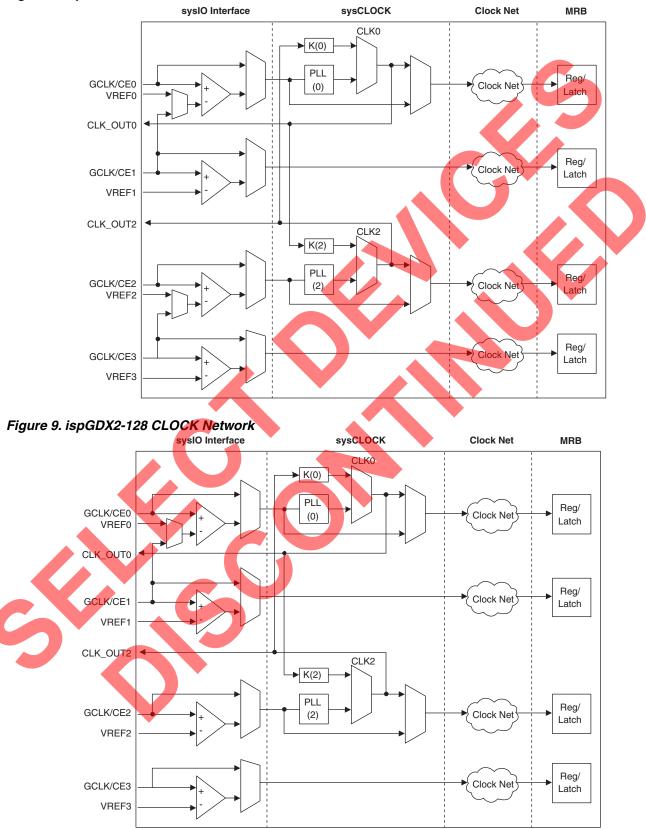

There are four global clock networks routed to each MRB block. These global clocks, CLK0-3, can either be generated by the PLL circuits or supplied externally. External clock pins can be configured as single-ended or differential (LVDS) input Figure 7 illustrates how the sysCLOCK PLL inputs and outputs can be routed to the I/O pins or general routing. Figure 10 shows the clock network for the ispGDX2-256 and Figure 8 shows the clock networks for ispGDX2-128 and ispGDX2-64. The Reset (0) pin from the Control Array of selected GDX Blocks can be programmed to reset the M Divider of the PLLs. This provides a means for generating the reset signal internally. Table 5 details which GDX Block provides reset to the PLLs.

### Table 5. Internal Reset Input of the PLL (M Divider)

|             | PLL0         | PLL1         | PLL2         | PLL3         |

|-------------|--------------|--------------|--------------|--------------|

| ispGDX2-256 | GDX Block 5A | GDX Block 7B | GDX Block 1A | GDX Block 3B |

| ispGDX2-128 | GDX Block 2A | _            | GDX Block 0A | _            |

| ispGDX2-64  | GDX Block 0A | —            | GDX Block 1B | —            |

Figure 7. I/O Pin Connection to the sysCLOCK PLL<sup>1</sup>

### Figure 8. ispGDX2-64 CLOCK Network

### Figure 10. ispGDX2-256 CLOCK Network

# **Operating Modes**

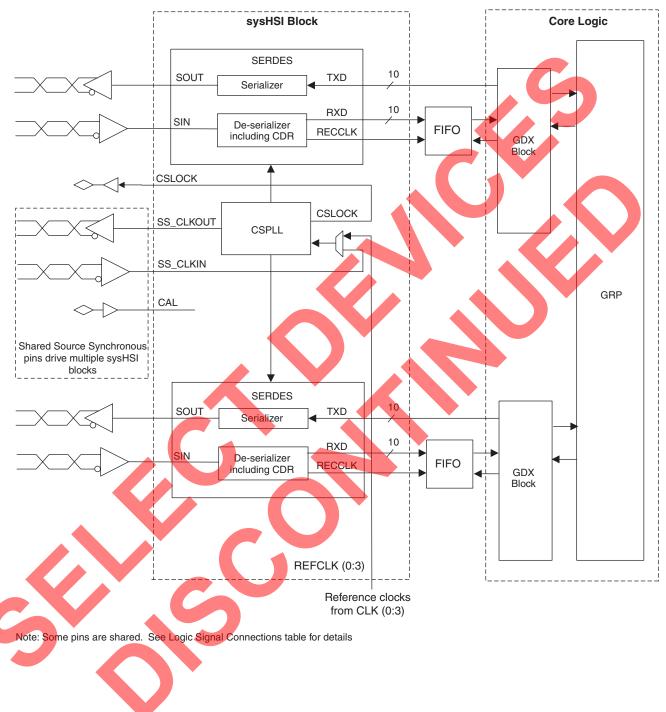

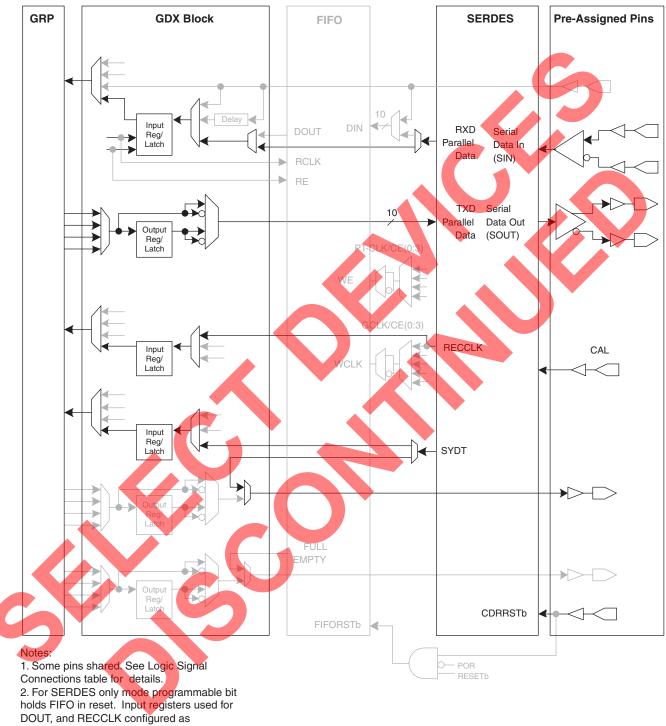

All the GDX Blocks in the ispGDX2 family can be programmed in four modes: Basic, FIFO only, SERDES only, and FIFO with SERDES mode. In basic mode, the SERDES and FIFO are disabled and the MUX output of the MRB connects to the output register. Inputs are connected to the GRP via the MRB.

Figure 11 shows the four different operating modes. Precise detail of the FIFO and SERDES connections is provided in their respective sections.

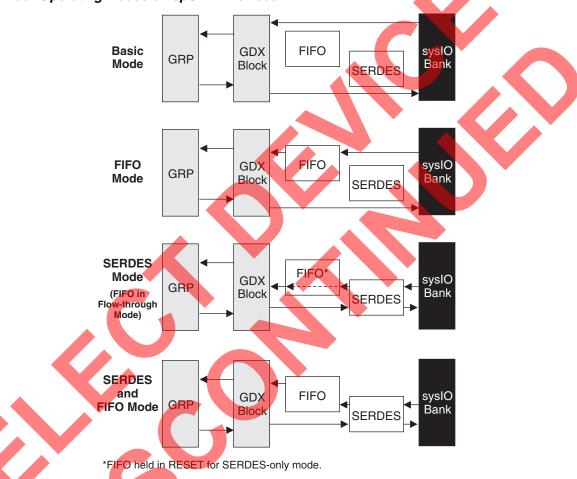

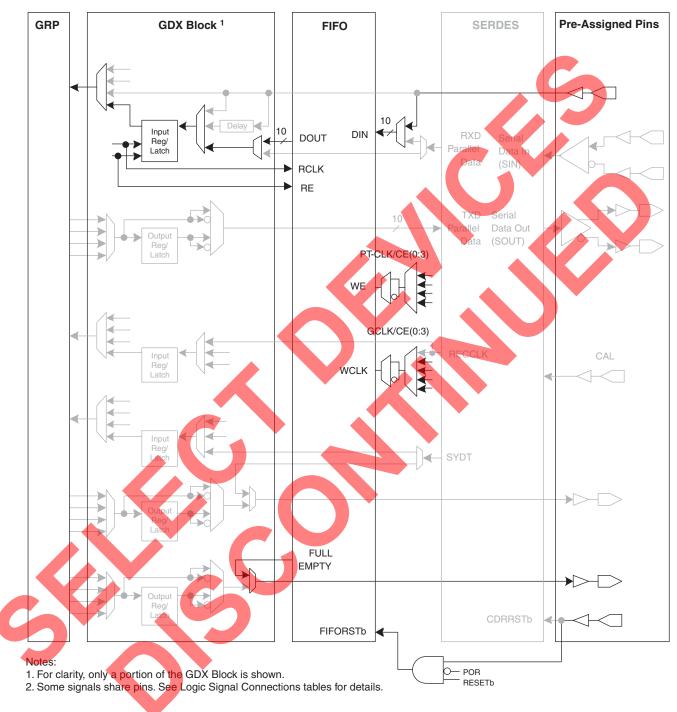

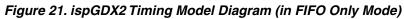

# **FIFO** Operations

Each GDX Block is associated with a 10-bit wide and 15-word deep (10x15) RAM. This RAM, combined with two address counters and two comparators, is used to implement a FIFO as a "circular queue". The FIFO has separate clocks, the Read Clock (RCLK) and Write Clock (WCLK), for asynchronous operation. The FIFO has three additional control signals Write Enable, Read Enable and FIFO Reset. Three flags show the status of the FIFO: Empty, Full and Start Read. Each FIFO receives the global Power-on Reset and Reset signals. Figure 12 shows the connections to the FIFO.

### Figure 12. ispGDX2 FIFO Signals

Read Clock and Read Enable are the same as the Clock and Clock Enable signals of the input registers of the associated MRB. These registers are used to register the FIFO outputs, and in modes that utilize the FIFO are configured to use the same clock and clock enable signals. The Write Clock is selected from one of the GCLK/CE signals or the RECCLK (Recovered Clock) signal from the associated SERDES. The Write Enable is selected from one of the local MRB product term CLK/CE signals. All FIFO operations occur on the rising edge of the clock although clock polarity of these signals can be programmed.

The flags from the FIFO, FULL, EMPTY and STRDb (Start Read) are each fed via a MUX in the MRB to an I/O buffer. The STRDb (half full) signal is used in conjunction with SERDES. STRDb is an active low signal, the signal is inactive (high) on FIFO RESET. After the FIFO reset when the FIFO contains data in five memory locations, at the following write clock transition the STRDb becomes active (low). Note, if the Read Clocks arrive before writing the sixth location, it may take longer than five write clocks before the STRDb becomes active. When the FIFO has data in the first six locations, at the next write clock transition the STRDb becomes inactive (high). Again, if the Read Clocks arrive before writing the seventh location, the STRDb may stay active for longer than one write clock period, even if the FIFO contains data in less than five locations. After this event, the STRDb stays inactive until the FIFO is RESET again. STRDb does not become active again even if less than six memory locations are occupied in the FIFO. It is the user's responsibility to monitor the FULL and EMPTY signals to avoid data underflow/overflow and to take appropriate actions.

Figure 13 shows how the FIFO is connected between the I/O banks and the GDX Blocks in FIFO mode. For more information on the FIFO, please refer to Lattice technical note number TN1020, *sysHSI Usage Guidelines*.

### Lattice Semiconductor

### Figure 13. Operation in FIFO Mode<sup>2</sup>

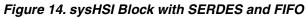

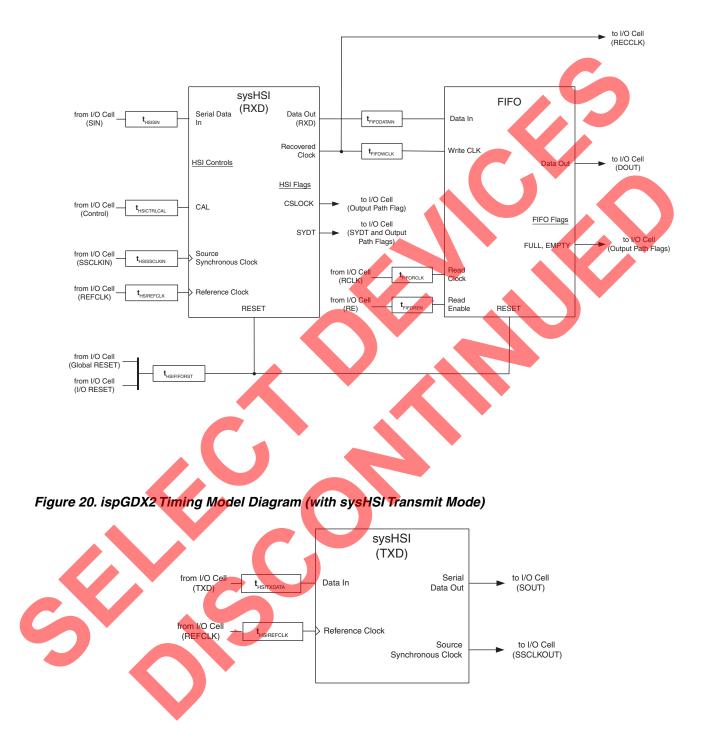

# High Speed Serial Interface Block (sysHSI Block)<sup>1</sup>

The High Speed Serial Interface (sysHSI) allows high speed serial data transfer over a pair of LVDS I/O. The ispGDX2 devices have multiple sysHSI Blocks.

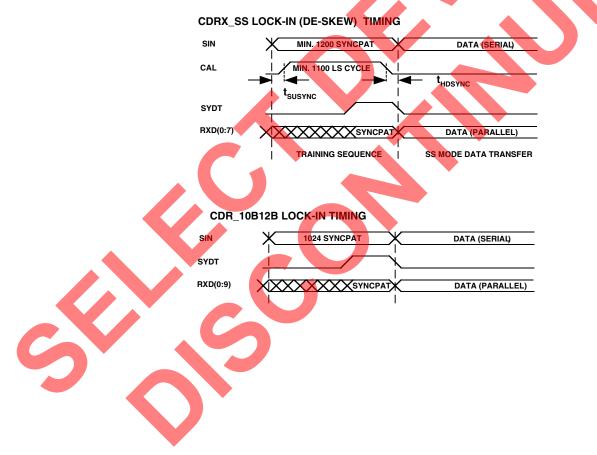

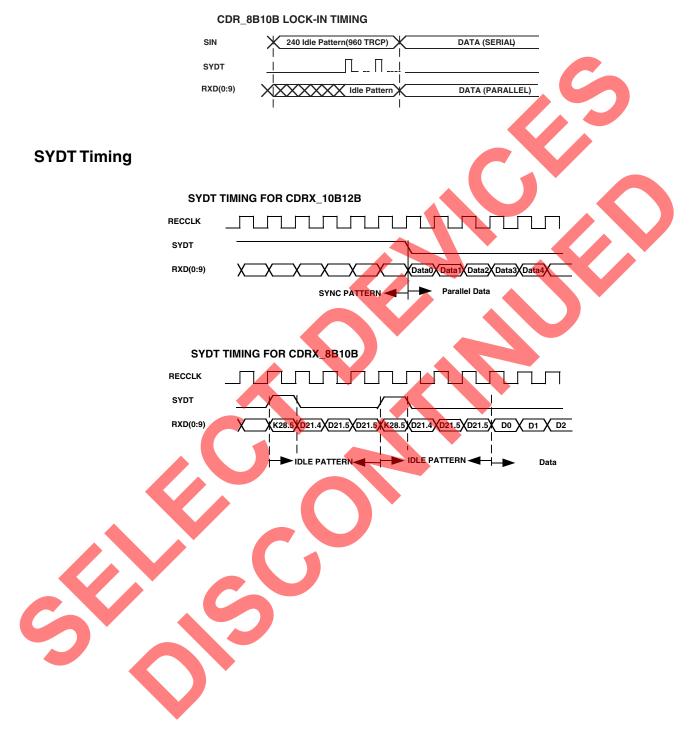

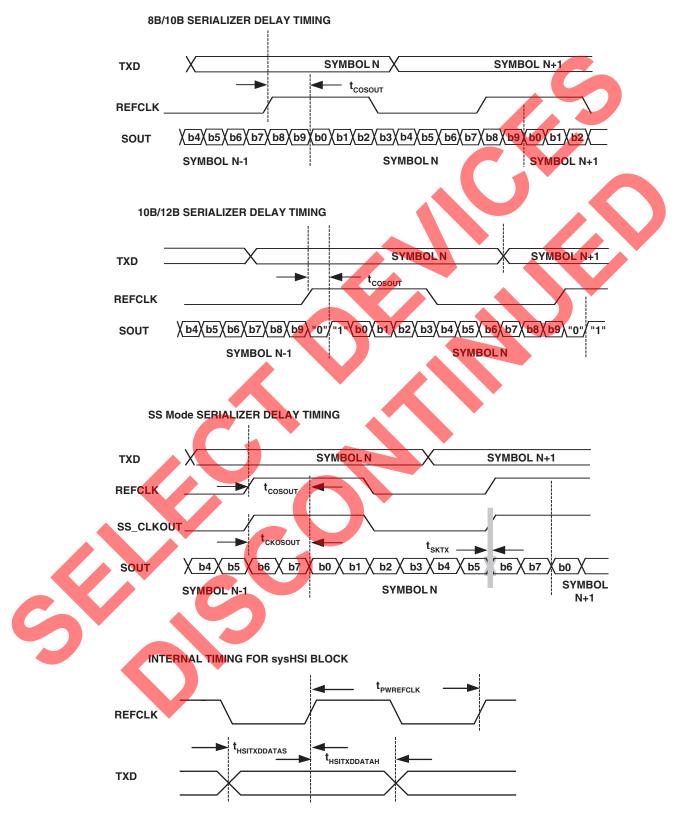

Each sysHSI Block has two SERDES blocks which contain two main sub-blocks, Transmitter (with a serializer) and Receiver (with a deserializer) including Clock/Data Recovery Circuit (CDR). Each SERDES can be used as a full duplex channel. The two SERDES in a given sysHSI Block share a common clock and must operate at the same nominal frequency. Figure 14 shows the sysHSI Block.

Device features support two data coding modes: 10B/12B and 8B/10B (for use with other encoding schemes, see Lattice's sysHSI application notes). The encoding and decoding of the 10B/12B standard are performed within the device in dedicated logic. For the 8B/10B standard, the symbol boundaries are aligned internally but the encoding and decoding are performed outside the device.

Each SERDES block receives a single high speed serial data input stream (with embedded clock) from an input, and provide a low speed 10-bit wide data stream and a recovered clock to the device. For transmitting, the SER-DES converts a 10-bit wide low-speed data stream to a single high-speed data stream with embedded clock for output.

Additionally, multiple sysHSI Blocks can be grouped together to form a source synchronous interface of between 1-8 channels.

Figure 15 shows the connections of the SERDES block with the FIFO, sysIO block and the MRB. Table 6 provides the descriptions of the SERDES.

For more information on the SERDES/CDR, refer to Lattice technical note number TN1020, sysHSI Usage Guidelines.

| Signal    | I/O      | Description                                              |

|-----------|----------|----------------------------------------------------------|

| CDRRSTb   |          | Resets the CDR circuit of sysHSI block                   |

| SYDT      | 0        | Symbol alignment detect for sysHSI block                 |

| CAL       | I        | Initiates source synchronous calibration sequence        |

| RXD       | Internal | Parallel data in for sysHSI block                        |

| TXD       | Internal | Parallel data out for sysHSI block                       |

| REFCLK    | Internal | Reference clock received from the clock tree             |

| SIN       |          | Serial data input for sysHSI block (LVDS input)          |

| SOUT      | 0        | Serial data output for sysHSI block (LVDS output)        |

| SS_CLKIN  |          | Clock input for source synchronous group                 |

| SS_CLKOUT | 0        | Clock output for source synchronous group                |

| RECCLK    | Internal | Recovered clock from encoded data by CDR of sysHSI block |

| CSLOCK    | Internal | Lock output of the PLL associated with sysHSI block      |

### Table 6. SERDES Signal Descriptions

1. "E-Series" does not support sysHSI.

Figure 15. Operation in SERDES Only Mode<sup>1, 2</sup>

latches and held in pass through.

Figure 16. Operation in SERDES with FIFO Mode

# IEEE 1149.1-Compliant Boundary Scan Testability

All ispGDX2 devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for more board-level testing. The test access port has its own supply voltage that can operate with LVCMOS3.3, 2.5 and 1.8 standards.

## sysIO Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The ispGDX2 family of devices allows this by offering the user the ability to quickly configure the physical nature of the sysIO cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM<sup>™</sup> System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

# IEEE 1532-Compliant In-System Programming

In-system programming of devices provides a number of significant benefits including rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispGDX2 devices provide In-System Programming (ISP) capability through their Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains compliant to the IEEE 1532 standard. By using IEEE 1532 as the communication interface through which ISP is achieved, designers get the benefit of a standard, well defined interface.

The ispGDX2 devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispGDX2 devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program ispGDX2 devices during the testing of a circuit board.

# Security Scheme

A programmable security scheme is provided on the ispGDX2 devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this scheme prevents readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. The security scheme also prevents programming and verification. The entire device must be erased in order to reset the security scheme.

# **Hot Socketing**

The ispGDX2 devices are well suited for those applications that require hot socketing capability. Hot socketing a device requires that the device, when powered down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of the powered-down device be minimal on active signals.

# Absolute Maximum Ratings 1, 2, 3

|                                                                | ispGDX2C (1.8V) | ispGDX2B/V (2.5/3.3V) |

|----------------------------------------------------------------|-----------------|-----------------------|

| Supply Voltage V <sub>CC</sub>                                 | 0.5 to 2.5V     |                       |

| PLL Supply Voltage V <sub>CCP</sub>                            | 0.5 to 2.5V     |                       |

| Output Supply Voltage V <sub>CCO</sub>                         | 0.5 to 4.5V     |                       |

| JTAG Supply Voltage (V <sub>CCJ</sub> )                        | 0.5 to 4.5V     | 0.5 to 4.5∨           |

| Input or I/O Tristate Voltage Applied 4,5                      | 0.5 to 5.5V     |                       |

| Storage Temperature                                            | 65 to 150°C     | 65 to 150°C           |

| Junction Temp. (T <sub>J</sub> ) with Power Applied $\ldots$ . | 55 to 150°C     |                       |

1. Stress above those listed under the Absolute Maximum Ratings may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied (while programming, following the programming specifications).

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2V to (V<sub>IH</sub> (MAX)+2) volts is permitted for a duration of <20ns.

5. A maximum of 64 I/Os per device with  $V_{IN}$  > 3.6V is allowed.

# **Recommended Operating Conditions**

| Symbol               | Parameter                                                           | Min. | Max. | Units |

|----------------------|---------------------------------------------------------------------|------|------|-------|

|                      | Supply Voltage for 1.8V Devices <sup>1</sup>                        | 1.65 | 1.95 | V     |

| V <sub>CC</sub>      | Supply Voltage for 2.5V Devices                                     | 2.3  | 2.7  | V     |

|                      | Supply Voltage for 3.3V Devices                                     | 3    | 3.6  | V     |

|                      | Supply Voltage for PLL and sysHSI Blocks, 1.8V Devices <sup>1</sup> | 1.65 | 1.95 | V     |

| V <sub>CCP</sub>     | Supply Voltage for PLL and sysHSI Blocks, 2.5V Devices              | 2.3  | 2.7  | V     |

|                      | Supply Voltage for PLL and sysHSI Blocks, 3.3V Devices              | 3    | 3.6  | V     |

|                      | Power Supply Voltage for JTAG Programming 1.8V Operation            | 1.65 | 1.95 | V     |

| V <sub>CCJ</sub>     | Power Supply Voltage for JTAG Programming 2.5V Operation            | 2.3  | 2.7  | V     |

|                      | Power Supply Voltage for JTAG Programming 3.3V Operation            | 3    | 3.6  | V     |

| T <sub>J</sub> (COM) | Junction Commercial Operation                                       | 0    | 90   | °C    |

| T <sub>J</sub> (IND) | Junction Industrial Operation                                       | -40  | 105  | °C    |

1. sysHSI specification is valid for  $V_{CC}$  and  $V_{CCP} = 1.7V$  to 1.9V.

# Erase Reprogram Specifications

|                       |  | Parameter | Min   | Max | Units  |

|-----------------------|--|-----------|-------|-----|--------|

| Erase/Reprogram Cycle |  |           | 1,000 | —   | Cycles |

Note: Valid over commercial temperature range.

# Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol                       | Parameter                              | Condition               | Min | Тур   | Max    | Units |

|------------------------------|----------------------------------------|-------------------------|-----|-------|--------|-------|

| I <sub>DK</sub> <sup>4</sup> | Input or Tristated I/O Leakage Current | $0 \le V_{IN} \le 3.0V$ |     | +/-50 | +/-800 | μΑ    |

1. Insensitive to sequence of V<sub>CC</sub> and V<sub>CCO</sub>. However, assumes monotonic rise/fall rates for V<sub>CC</sub> and V<sub>CCO</sub>, provided (V<sub>IN</sub> - V<sub>CCO</sub>)  $\leq$  3.6V.

2. LVTTL, LVCMOS only.

3.  $0 < V_{CC} \le V_{CC}$  (MAX),  $0 < V_{CCO} \le V_{CCO}$  (MAX).

4.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ . Device defaults to pull-up until fuse circuitry is active.

# **DC Electrical Characteristics**

| Symbol                       | Parameter                             | Condition                                                   | Min.                    | Тур. | Max.                    | Units |

|------------------------------|---------------------------------------|-------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| I I 1                        | Input or I/O Low Leakage              | $0 \le V_{IN} \le (V_{CCO} - 0.2V)$                         | —                       |      | 10                      | μA    |

| $I_{\rm IL}, I_{\rm IH}^{1}$ |                                       | $(V_{CCO} - 0.2V) < V_{IN} \le 3.6V$                        | —                       | -    | 30                      | μA    |

| I <sub>IH</sub> ³            | Input High Leakage Current            | $3.6V < V_{IN} \le 5.5V$ and<br>$3.0V \le V_{CCO} \le 3.6V$ | —                       |      | 3                       | mA    |

| I <sub>PU</sub>              | I/O Active Pull-up Current            | $0 \le V_{IN} \le 0.7 V_{CCO}$                              | -30                     |      | -150                    | μA    |

| I <sub>PD</sub>              | I/O Active Pull-down Current          | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)              | 30                      |      | 150                     | μΑ    |

| I <sub>BHLS</sub>            | Bus Hold Low Sustaining Current       | $V_{IN} = V_{IL}$ (MAX)                                     | 30                      |      | —                       | μΑ    |

| I <sub>BHHS</sub>            | Bus Hold High Sustaining Current      | $V_{IN} = 0.7 V_{CCO}$                                      | -30                     |      |                         | μΑ    |

| I <sub>BHLO</sub>            | Bus Hold Low Overdrive Current        | $0 \le V_{IN} \le V_{IH} (MAX)$                             |                         | —    | 150                     | μΑ    |

| I <sub>BHLH</sub>            | Bus Hold High Overdrive Current       | $0 \le V_{IN} \le V_{IH} (MAX)$                             |                         | —    | -150                    | μΑ    |

| V <sub>BHT</sub>             | Bus Hold Trip Points                  |                                                             | V <sub>CCO</sub> * 0.35 | Ι    | V <sub>CCO</sub> * 0.65 | V     |

| C <sub>1</sub>               | I/O Capacitance <sup>2</sup>          | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                         | <u> </u>                | 8    |                         | pf    |

|                              |                                       | $V_{CC} = 1.8V, V_{IO} = 0$ to $V_{IH}$ (MAX)               | —                       |      | -                       | P     |

| C <sub>2</sub>               | Clock Capacitance <sup>2</sup>        | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                         | -                       | 6    | <b>—</b>                | pf    |

| 02                           |                                       | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX)            |                         | J    | —                       | Р     |

| C <sub>3</sub>               | Global Input Capacitance <sup>2</sup> | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                         | _                       | 6    | _                       | pf    |

| <b>C</b> 3                   |                                       | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX)            |                         | 5    | _                       | 191   |

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2.  $T_A = 25^{\circ}C$ , f = 1.0MHz.

3. 5V tolerant inputs and I/Os should be placed in banks where 3.0V ≤ V<sub>CCO</sub> ≤ 3.6V. The JTAG ports are not included for the 5V tolerant interface.

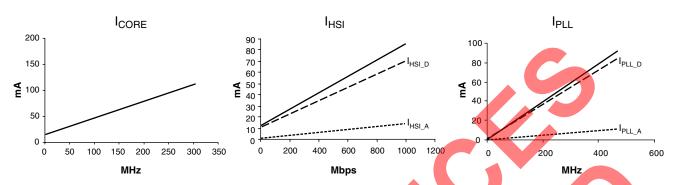

# **Supply Current**

### Over Recommended Operating Conditions (ispGDX2-256)<sup>4</sup>

| Symbol                         | Description                               | Power Pins       | Vcc (V) | Min. | Тур.  | Max. | Units |

|--------------------------------|-------------------------------------------|------------------|---------|------|-------|------|-------|

|                                |                                           |                  | 3.3     | —    | 59.6  | _    | mA    |

|                                | Core Logic Power Supply Current           |                  | 2.5     | —    | 58.7  | _    | mA    |

| I <sub>CC</sub> <sup>1,2</sup> |                                           | Vaa              | 1.8     | _    | 60.0  | _    | mA    |

| l'CC                           |                                           | V <sub>cc</sub>  | 3.3     | —    | 118.7 | _    | mA    |

|                                | GPLL/sysHSI Logic Power Supply<br>Current |                  | 2.5     | _    | 118.7 |      | mA    |

|                                |                                           |                  | 1.8     | _    | 117.5 | —    | mA    |

|                                | GPLL/sysHSI CSPLL Power<br>Supply Current | V <sub>CCP</sub> | 3.3     | _    | 14.7  |      | mA    |

| I <sub>CCP</sub> <sup>2</sup>  |                                           |                  | 2.5     | _    | 14.7  |      | mA    |

|                                |                                           |                  | 1.8     | _    | 17.4  | —    | mA    |

|                                |                                           |                  | 3.3     | —    | 35    | _    | mA    |

| I <sub>CCO<sup>3</sup></sub>   | Bank Power Supply Current                 | V <sub>CCO</sub> | 2.5     | _    | 35    |      | mA    |

|                                |                                           |                  | 1.8     | _    | 25    | —    | mA    |

|                                |                                           | V <sub>CCJ</sub> | 3.3     |      | 1.5   |      | mA    |

| I <sub>CCJ</sub>               | JTAG Programming Current                  |                  | 2.5     | _    | 1.0   |      | mA    |

|                                |                                           |                  | 1.8     | —    | 800   | —    | μΑ    |

1. 64-input switching frequency at 20 MHz, with one GRP fanout.

2. One GPLL with f<sub>VCO</sub> = 400 MHz and one sysHSI Block (two receivers and two transmitters) at 622 MHz data rate.

3. All 8-bank reference circuit currents, all I/Os in tristate, inputs held at valid logic levels, and bus maintenance circuits disabled.

4.  $T_A = 25^{\circ}C$

# sysIO Recommended Operating Conditions

|                         |      | V <sub>CCO</sub> (V) <sup>1</sup> |      | V <sub>REF</sub> (V) |      |       |  |  |  |  |

|-------------------------|------|-----------------------------------|------|----------------------|------|-------|--|--|--|--|

| Standard                | Min. | Тур.                              | Max. | Min.                 | Тур. | Max.  |  |  |  |  |

| LVCMOS 3.3              | 3.0  | 3.3                               | 3.6  | -                    | -    | -     |  |  |  |  |

| LVCMOS 2.5              | 2.3  | 2.5                               | 2.7  | -                    |      | -     |  |  |  |  |

| LVCMOS 1.8 <sup>2</sup> | 1.65 | 1.8                               | 1.95 | -                    |      | -     |  |  |  |  |

| LVTTL                   | 3.0  | 3.3                               | 3.6  | -                    |      | -     |  |  |  |  |

| PCI 3.3                 | 3.0  | 3.3                               | 3.6  | -                    | -    | -     |  |  |  |  |

| PCI-X                   | 3.0  | 3.3                               | 3.6  | -                    | -    | -     |  |  |  |  |

| AGP-1X                  | 3.15 | 3.3                               | 3.45 | -                    | -    | -     |  |  |  |  |

| SSTL 2                  | 2.3  | 2.5                               | 2.7  | 1.15                 | 1.25 | 1.35  |  |  |  |  |

| SSTL 3                  | 3.0  | 3.3                               | 3.6  | 1.3                  | 1.5  | 1.7   |  |  |  |  |

| CTT 3.3                 | 3.0  | 3.3                               | 3.6  | 1.35                 | 1.5  | 1.65  |  |  |  |  |

| CTT 2.5                 | 2.3  | 2.5                               | 2.7  | 1.35                 | 1.5  | 1.65  |  |  |  |  |

| HSTL Class I            | 1.4  | 1.5                               | 1.6  | 0.68                 | 0.75 | 0.9   |  |  |  |  |

| HSTL Class III          | 1.4  | 1.5                               | 1.6  | -                    | 0.9  | -     |  |  |  |  |

| HSTL Class IV           | 1.4  | 1.5                               | 1.6  | -                    | 0.9  | -     |  |  |  |  |

| GTL+                    | 1.4  | -                                 | 3.6  | 0.882                | 1.0  | 1.122 |  |  |  |  |

| LVPECL                  | 3.0  | 3.3                               | 3.6  |                      | -    | -     |  |  |  |  |

| LVDS                    | 2.3  | 2.5/3.3                           | 3.6  |                      | -    | -     |  |  |  |  |

| BLVDS                   | 2.3  | 2.5/3.3                           | 3.6  | -                    | -    | -     |  |  |  |  |

Inputs are independent of V<sub>CCO</sub> setting. However, V<sub>CCO</sub> must be set within the valid operating range for one of the supported standards.

Software default setting.

# sysIO Single Ended DC Electrical Characteristics

| I                          | v       | /IL                     | v                       | IH                | v                          |                            | . 2                       | . 2                             |

|----------------------------|---------|-------------------------|-------------------------|-------------------|----------------------------|----------------------------|---------------------------|---------------------------------|

| Input/Output<br>Standard   | Min (V) | Max (V)                 | Min (V)                 | Max (V)           | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V) | l <sub>OL</sub> ²<br>(mA) | I <sub>OH</sub> ²<br>(mA)       |

| LVCMOS 3.3                 | -0.3    | 0.8                     | 2.0                     | 5.5               | 0.4                        | 2.4                        | 20, 16, 12,<br>8, 5.33, 4 | -20, -16, -12,<br>-8, -5.33, -4 |

|                            |         |                         |                         |                   | 0.2                        | V <sub>CCO</sub> - 0.2     | 0.1                       | -0.1                            |

| LVTTL                      | -0.3    | 0.8                     | 2.0                     | 5.5               | 0.4                        | 2.4                        | 4                         | -4                              |

|                            | -0.5    | 0.0                     | 2.0                     | 5.5               | 0.2                        | V <sub>CCO</sub> - 0.2     | 0.1                       | -0.1                            |

| LVCMOS 2.5                 | -0.3    | 0.7                     | 1.7                     | 3.6               | 0.4                        | V <sub>CCO</sub> - 0.4     | 16, 12, 8,<br>5.33, 4     | -16, -12, -8,<br>-5.33, -4      |

|                            |         |                         |                         |                   | 0.2                        | V <sub>CCO</sub> - 0.2     | 0.1                       | -0.1                            |

| LVCMOS 1.8 <sup>1, 3</sup> | -0.3    | 0.68                    | 1.07                    | 3.6               | 0.4                        | V <sub>CCO</sub> - 0.4     | 8                         | -8                              |

| LVCMOS 1.8 <sup>3</sup>    | -0.3    | 0.68                    | 1.07                    | 3.6               | 0.4                        | V <sub>CCO</sub> -0.4      | 12, 5.33, 4               | -12, -5.33, -4                  |

|                            | -0.5    | 0.00                    | 1.07                    | 0.0               | 0.2                        | V <sub>CCO</sub> - 0.2     | 0.1                       | -0.1                            |

| PCI 3.34                   | -0.3    | 1.08                    | 1.5                     | 3.6               | 0.1 V <sub>CCO</sub>       | 0.9 V <sub>CCO</sub>       | 1.5                       | -0.5                            |

| PCI -X <sup>5</sup>        | -0.3    | 1.26                    | 1.5                     | 3.6               | 0.1 V <sub>CCO</sub>       | 0.9 V <sub>CCO</sub>       | 1.5                       | -0.5                            |

| AGP-1X <sup>4</sup>        | -0.3    | 1.08                    | 1.5                     | 3.6               | 0.1 V <sub>CCO</sub>       | 0.9 V <sub>CCO</sub>       | 1.5                       | -0.5                            |

| SSTL3 class I              | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6               | 0.7                        | V <sub>CCO</sub> - 1.1     | 8                         | -8                              |

| SSTL3 class II             | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | <mark>3</mark> .6 | 0.5                        | V <sub>CCO</sub> - 0.9     | 16                        | -16                             |

| SSTL2 class I              | -0.3    | V <sub>REF</sub> - 0.18 | V <sub>REF</sub> + 0.18 | 3.6               | 0.54                       | V <sub>CCO</sub> - 0.62    | 7.6                       | -7.6                            |

| SSTL2 class II             | -0.3    | V <sub>REF</sub> - 0.18 | V <sub>REF</sub> + 0.18 | 3.6               | 0.35                       | V <sub>CCO</sub> - 0.43    | 15.2                      | -15.2                           |

| CTT 3.3                    | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6               | V <sub>REF</sub> - 0.4     | V <sub>REF</sub> + 0.4     | 8                         | -8                              |

| CTT 2.5                    | -0.3    | V <sub>REF</sub> - 0.3  | V <sub>REF</sub> + 0.2  | 3.6               | V <sub>REF</sub> - 0.4     | V <sub>REF</sub> + 0.4     | 8                         | -8                              |

| HSTL class I               | -0.3    | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6               | 0.4                        | V <sub>CCO</sub> - 0.4     | 8                         | -8                              |

| HSTL class III             | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.1  | 3.6               | 0.4                        | V <sub>CCO</sub> - 0.4     | 24                        | -8                              |

| HSTL class IV              | -0.3    | V <sub>REF</sub> - 0.3  | V <sub>REF</sub> + 0.1  | 3.6               | 0.4                        | V <sub>CCO</sub> - 0.4     | 48                        | -8                              |

| GTL+                       | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6               | 0.6                        | n/a                        | 36                        | n/a                             |

**Over Recommended Operating Conditions**

1. Software default setting.

2. The average DC current drawn by I/Os between adjacent bank GND connections, or between the last GND in an I/O bank and the end of the I/O bank, as shown in the logic signals connection table, shall not exceed n\*8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

3. For 1.8V devices (ispGDX2C) these specifications are  $V_{IL} = 0.35 V_{CC}$  and  $V_{IH} = 0.65V_{CC}$ 4. For 1.8V power supply devices these specifications are  $V_{IL} = 0.3 * V_{CC} * 3.3/1.8$ ,  $V_{IH} = 0.5 * V_{CC} * 3.3/1.8$ 5. For 1.8V power supply devices these specifications are  $V_{IL} = 0.35 * V_{CC} * 3.3/1.8$  and  $V_{IH} = 0.5 * V_{CC} * 3.3/1.8$

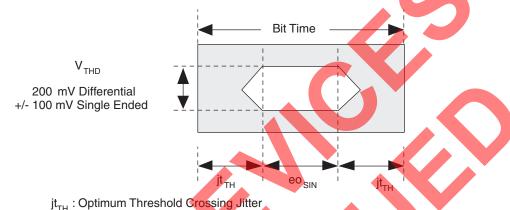

# sysIO Differential DC Electrical Characteristics

| Parameter<br>Symbol               | Parameter Description                                     | Test Conditions                                               | Min.     | Тур. | Max.  | Units |

|-----------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|----------|------|-------|-------|

| LVDS                              |                                                           |                                                               |          |      |       |       |

| V <sub>INP</sub> V <sub>INM</sub> | Input Voltage                                             | —                                                             | 0        |      | 2.4   | V     |

| V <sub>THD</sub>                  | Differential Input Threshold                              | $0.2V \le V_{CM} \le 1.8V$                                    | +/-100   |      |       | mV    |

| I <sub>IN</sub>                   | Input Current                                             | Power On                                                      |          |      | +/-10 | μA    |

| V <sub>OH</sub>                   | Output High Voltage for $V_{OP}$ or $V_{OM}$              | R <sub>T</sub> = 100Ω                                         |          | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                   | Output Low Voltage for V <sub>OP</sub> or V <sub>OM</sub> | R <sub>T</sub> = 100Ω                                         | 0.9      | 1.03 | —     | V     |

| V <sub>OD</sub>                   | Output Voltage Differential                               | $(V_{OP} - V_{OM}), R_{T} = 100\Omega$                        | 250      | 350  | 450   | mV    |

| $\Delta V_{OD}$                   | Change in V <sub>OD</sub> Between High and Low            | -                                                             |          | —    | 50    | mV    |

| V <sub>OS</sub>                   | Output Voltage Offset                                     | (V <sub>OP</sub> - V <sub>OM</sub> )/2, R <sub>T</sub> = 100Ω | 1.125    | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$                   | Change in VOS Between H and L                             | -                                                             | —        |      | 50    | mV    |

| I <sub>OSD</sub>                  | Output Short Circuit Current                              | V <sub>OD</sub> = 0V. Driver Outputs<br>Shorted.              | -        | Y    | 24    | mA    |

| Bus LVDS <sup>1</sup>             |                                                           |                                                               |          |      |       |       |

| V <sub>OH</sub>                   | Output High Voltage for $V_{OP}$ or $V_{OM}$              | $R_T = 27\Omega$                                              |          | 1.4  | 1.80  | V     |

| V <sub>OL</sub>                   | Output Low Voltage for V <sub>OP</sub> or V <sub>OM</sub> | $R_{T} = 27\Omega$                                            | 0.95     | 1,1  | —     | V     |

| V <sub>OD</sub>                   | Output Voltage Differential                               | $ V_{OP} - V_{OM} , RT = 27\Omega$                            | 240      | 300  | 460   | mV    |

| $\Delta V_{OD}$                   | Change in V <sub>OD</sub> Between H and L                 |                                                               |          | —    | 27    | mV    |

| V <sub>OS</sub>                   | Output Voltage Offset                                     | $ V_{OP} - VOM  / 2, RT = 27\Omega$                           | 1.1      | 1.3  | 1.5   | V     |

| $\Delta V_{OS}$                   | Change in V <sub>OS</sub> Between H and L                 |                                                               | <b>—</b> | —    | 27    | mV    |

| I <sub>OSD</sub>                  | Output Short Circuit Current                              | V <sub>OD</sub> = 0. Driver Outputs<br>Shorted.               | _        | 36   | 65    | mA    |

1. V<sub>OP</sub> and V<sub>OM</sub> are the two outputs of the LVDS output buffer.

## LVPECL<sup>1</sup>

| DC Parameter                   | Parameter Description      | Min. | Max.  | Min. | Max.  | Min. | Max.  | Units |

|--------------------------------|----------------------------|------|-------|------|-------|------|-------|-------|

| V <sub>CCO</sub>               | Output Supply Voltage      | 3    | .0    | 3    | .3    | 3    | V     |       |

| V <sub>IH</sub>                | Input Voltage High         | 1.49 | 2.72  | 1.49 | 2.72  | 1.49 | 2.72  | V     |

| V <sub>IL</sub>                | Input Voltage Low          | 0.86 | 2.125 | 0.86 | 2.125 | 0.86 | 2.125 | V     |

| V <sub>OH</sub>                | Output Voltage High        | 1.7  | 2.11  | 1.92 | 2.28  | 2.03 | 2.41  | V     |

| VOL                            | Output Voltage Low         | 0.96 | 1.27  | 1.06 | 1.43  | 1.25 | 1.57  | V     |

| V <sub>DIFF</sub> <sup>2</sup> | Differential Input voltage | 0.3  |       | 0.3  |       | 0.3  |       | V     |

These values are valid at the output of the source termination pack as shown above with 100-ohm differential load only (see Figure 17). The V<sub>OH</sub> levels are 200mV below the standard LVPECL levels and are compatible with devices tolerant of the lower common mode ranges.

Valid for 0.2V ≤ V<sub>CM</sub> ≤ 1.8V.

### Figure 17. LVPECL Driver with Three Resistor Pack

# ispGDX2V/B/C, ispGDX2EV/EB/EC External Switching Characteristics Over Recommended Operating Conditions

|                                   |                                                               | -    | ·3   | -3   | 32   | -:   | 35       | -5   |      |       |

|-----------------------------------|---------------------------------------------------------------|------|------|------|------|------|----------|------|------|-------|

| Parameter                         | Description                                                   | Min. | Max. | Min. | Max. | Min. | Max.     | Min. | Max. | Units |

| Output Pat                        | hs                                                            |      |      |      |      |      |          |      |      |       |

| t <sub>PD</sub>                   | Data From Input Pin to Output Pin                             | _    | 3.0  | _    | 3.2  | —    | 3.5      |      | 5.0  | ns    |

| t <sub>PD_SEL</sub>               | Data From Global Select Pin to Output Pin                     | _    | 2.8  | _    | 3.0  | -    | 3.3      |      | 4.7  | ns    |

| t <sub>CO</sub>                   | Global Clock to Output                                        | —    | 2.9  | —    | 3.1  |      | 3.2      | _    | 5.4  | ns    |

| t <sub>OPS</sub>                  | Set-up Time Before Global Clock                               | 2.0  | _    | 2.0  | _    | 2.0  | <b>—</b> | 3.0  | —    | ns    |

| t <sub>OPH</sub>                  | Hold Time After Global Clock                                  | 0.0  | —    | 0.0  |      | 0.0  |          | 0.0  | _    | ns    |

| t <sub>OPCES</sub>                | PT Clock Enable Setup Time Before<br>Global Clock             | 3.0  | _    | 3.0  |      | 4.1  | _        | 6.9  |      | ns    |

| t <sub>OPCEH</sub>                | PT Clock Enable Hold Time After<br>Global Clock               | 0.0  | _    | 0.0  |      | 0.0  | _        | 0.0  |      | ns    |

| t <sub>OPRSTO</sub>               | External Reset Pin to Output Delay                            | _    | 5.3  |      | 6.0  | —    | 6.0      | 7    | 10.0 | ns    |

| Input Paths                       |                                                               |      |      |      |      |      |          |      | 7    | •     |

| t <sub>IPS</sub>                  | Set-up Time Before Global Clock                               | 0.5  |      | 0.5  | —    | 0.5  |          | 0.9  | —    | ns    |

| t <sub>IPSZ</sub>                 | Set-up Time Before Global Clock<br>(Zero Hold Time)           | 2.0  |      | 2.0  | -    | 2.0  | -        | 3.0  | _    | ns    |

| t <sub>IPH</sub>                  | Hold Time After Global Clock                                  | 1.0  |      | 1.0  | _    | 1.0  |          | 1.7  | —    | ns    |

| t <sub>IPHZ</sub>                 | Hold Time After Global Clock<br>(Zero Hold Time)              | 0.0  | _    | 0.0  | -    | 0.0  | _        | 0.0  | _    | ns    |

| t <sub>IPCES</sub>                | PT Clock Enable Setup Time Before<br>Global Clock             | 3.1  | -    | 3.1  |      | 3.1  | _        | 5.1  | _    | ns    |

| t <sub>IPCEH</sub>                | PT Clock Enable Hold Time After Global<br>Clock               | 0.0  |      | 0.0  | _    | 0.0  | _        | 0.0  | _    | ns    |

| t <sub>IPRSTO</sub>               | External Reset Pin to Output Delay                            |      | 5.6  | —    | 6.5  | —    | 7.5      | -    | 12.5 | ns    |

| Output Ena                        | ble Paths                                                     |      |      |      |      |      | •        |      |      |       |

| t <sub>OECO</sub>                 | Global Clock to Output Enabled Pin                            |      | 4.2  | _    | 4.5  | _    | 5.5      | -    | 9.1  | ns    |

| t <sub>OES</sub>                  | Output Enable Register Set-up Time<br>Before Global Clock     | 1.6  | -    | 1.6  | _    | 2.0  | _        | 3.4  | _    | ns    |

| t <sub>OEH</sub>                  | Hold Time After Global Clock                                  | 0.0  | _    | 0.0  | —    | 0.0  |          | 0.0  | —    | ns    |

| t <sub>OECES</sub>                | PT Clock Enable Setup Time Before<br>Global Clock             | 3.5  | _    | 3.5  | _    | 4.1  | _        | 6.9  | _    | ns    |

| t <sub>OECEH</sub>                | PT Clock Enable Hold Time After Global<br>Clock               | 0.0  | _    | 0.0  | _    | 0.0  | _        | 0.0  | _    | ns    |

| t <sub>GOE/DIS</sub>              | Global OE Input to Output Enable/Disable                      |      | 3.5  | —    | 3.8  | —    | 4.5      | -    | 7.5  | ns    |

| t <sub>TOE/DIS</sub>              | Test OE Input to Output Enable/Disable                        |      | 5.2  | —    | 5.5  | —    | 6.2      | -    | 10.3 | ns    |

| t <sub>EN/DIS</sub>               | Input to Output Enable/Disable                                | _    | 5.2  | _    | 5.5  | _    | 6.2      | -    | 10.3 | ns    |

| Clock and I                       | Reset Paths                                                   |      |      |      |      |      |          |      |      |       |

| t <sub>RW</sub>                   | Width of Reset Pulse                                          | 2.5  | —    | 2.5  | —    | 2.5  | —        | 4.1  | —    | ns    |

| t <sub>CW</sub>                   | Clock Width                                                   | 1.3  | _    | 1.5  | —    | 1.6  | —        | 2.7  | —    | ns    |

| t <sub>GW</sub>                   | Clock Width                                                   | 1.5  |      | 1.6  | —    | 1.6  | -        | 2.7  | —    | ns    |

| f <sub>MAX</sub> (Ext)            | Clock Frequency with External Feedback $1/(t_{OPS} + t_{CO})$ | —    | 204  | _    | 196  |      | 192      | _    | 119  | MHz   |

| f <sub>MAX</sub> (Tog,<br>No PLL) | Clock Frequency Maximum Toggle<br>(No PLL)                    | _    | 360  | _    | 330  | _    | 300      | _    | 180  | MHz   |

# ispGDX2V/B/C, ispGDX2EV/EB/EC External Switching Characteristics Over Recommended Operating Conditions

|                  |                                              | -    | -3   |      | 32   |      | 35   | -    | -5   |            |

|------------------|----------------------------------------------|------|------|------|------|------|------|------|------|------------|

| Parameter        |                                              | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Units      |

| иах<br>Год, PLL) | Clock Frequency Maximum Toggle<br>(With PLL) | _    | 360  | -    | 330  | -    | 300  |      | 180  | MHz        |

|                  |                                              |      |      |      |      |      |      |      |      | ming v.2.2 |

|                  |                                              |      |      |      |      |      |      |      |      |            |

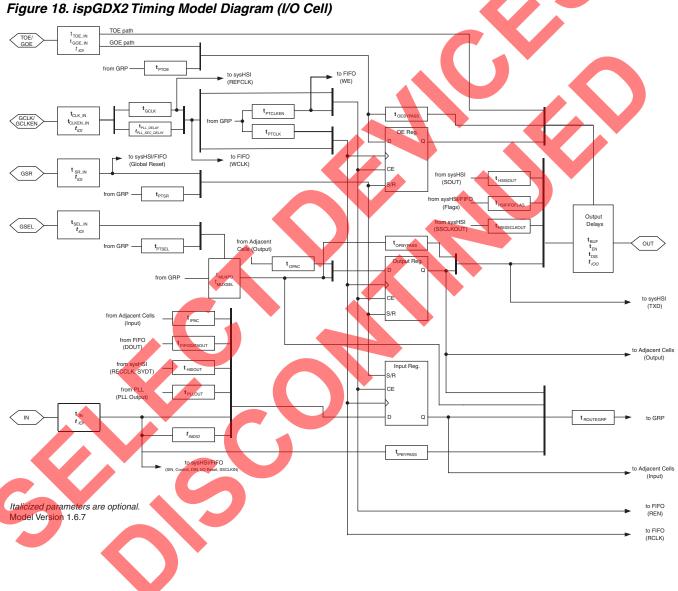

# **Timing Model**

The task of determining the timing through the ispGDX2 family is relatively simple. The timing model provided in Figure 18 shows the specific delay paths. Once the implementation of a given function is determined either conceptually or from the software report file, the delay path of the function can easily be determined from the timing model. The Lattice design tools report the timing delays based on the same timing model for a particular design. Note that the internal timing parameters are given for reference only, and are not tested. The external timing parameters are tested and guaranteed for every device.

# eters are tested and guaranteed for every dev

### Lattice Semiconductor

### Figure 19. ispGDX2 Timing Model Diagram (with sysHSI and FIFO Receive Mode)

# **Sample External Timing Calculations**

The following equations illustrate the task of determining the timing through the ispGDX2 family. These are only a sample of equations to calculate the timing through the ispGDX2.

Figure 18 shows the specific delay paths and the Internal Timing Parameters table provides the parameter values. Note that the internal timing parameters are given for reference only and are not tested. The external timing parameters are tested and guaranteed for every device.

Data from global select pin to output pin:  $t_{PD\_SEL} = t_{SEL\_IN} + t_{MUXSEL} + t_{OPBYPASS} + t_{BUF}$

Global clock to output:  $t_{CO} = t_{CLK_IN} + t_{GCLK} + t_{OPCOi} + t_{BUF}$

Input register or latch set-up time before global clock:  $t_{IPS} = t_{IN} + t_{IPS} - (t_{CLK} + t_{GCLK})$

Input register or latch hold time after global clock:  $t_{IPH} = (t_{CLK} IN + t_{GCLK}) + t_{IPHi} - t_{IN}$

Data from product term select to output pin: tPD\_PTSEL = tIN + tIPBYPASS + tROUTEGRP + tPTSEL + tMUXSEL + tOPBYPASS + tBUF

Product term clock to output: t<sub>CO\_PT</sub> = t<sub>IN</sub> + t<sub>IPBYPASS</sub> + t<sub>ROUTEGRP</sub> + t<sub>PTCLK</sub> + t<sub>OPCOi</sub> + t<sub>BUF</sub>

Input register or latch set-up time before product term clock:  $t_{IPS_PT} = t_{IN} + t_{IPSi_PT} - (t_{IN} + t_{IPBYPASS} + t_{ROUTEGRP} + t_{PTCLK})$

Input register or latch hold time after product term clock:  $t_{IPH_PT} = (t_{IN} + t_{IPBYPASS} + t_{ROUTEGRP} + t_{PTCLK}) + t_{IPHI} - t_{IN}$

Global OE input to output enable/disable: t<sub>GOE/DIS</sub> = t<sub>GOE\_IN</sub> + t<sub>OEBYPASS</sub> + t<sub>EN</sub>

External reset pin to output delay: toprsto = t<sub>SR IN</sub> + t<sub>OPASROI</sub> + t<sub>BUF</sub>

# ispGDX2V/B/C, ispGDX2EV/EB/EC Internal Timing Parameters<sup>1</sup>

|                          | Over Recommende                                                 | d Oper | ating | Condi    | ions |      |      |      |          |       |

|--------------------------|-----------------------------------------------------------------|--------|-------|----------|------|------|------|------|----------|-------|

|                          |                                                                 | -3 -32 |       |          | 32   | -:   | 35   | -5   |          |       |

| Parameter                | Description                                                     | Min.   | Max.  | Min.     | Max. | Min. | Max. | Min. | Max.     | Units |

| Input/Output D           | belays                                                          |        | 1     |          |      |      |      |      | 1        |       |

| t <sub>BUF</sub>         | Output Buffer Delay                                             | —      | 0.80  | —        | 0.80 | _    | 0.80 |      | 1.14     | ns    |

| t <sub>CLK_IN</sub>      | Global Clock Input Delay                                        | _      | 1.00  | —        | 1.00 |      | 1.00 | -    | 1.67     | ns    |

| t <sub>CLKEN_IN</sub>    | Global Clock Enable Input Delay                                 | _      | 1.80  | —        | 1.80 | -    | 1.80 | -    | 3.00     | ns    |

| t <sub>DIS</sub>         | Output Disable Delay                                            | _      | 1.80  | —        | 1.80 | X    | 2.50 | _    | 4.17     | ns    |

| t <sub>EN</sub>          | Output Enable Delay                                             | _      | 1.50  | -        | 1.80 | _    | 2.50 | _    | 4.17     | ns    |

| t <sub>GOE_IN</sub>      | Global Output Enable Path Delay                                 | -      | 2.00  | _        | 2.00 | 1    | 2.00 | -    | 3.33     | ns    |

| t <sub>IN</sub>          | Input Pin Delay                                                 | _      | 0.40  |          | 0.40 | 7-   | 0.40 | K    | 0.57     | ns    |

| t <sub>SEL_IN</sub>      | Global MUX Select Input Delay                                   | _      | 1.60  | _        | 1.60 | -    | 1.60 |      | 2.29     | ns    |

| t <sub>SR_IN</sub>       | Global Set/Reset Path Delay                                     | —      | 2.00  | -        | 2.70 | —    | 2.70 |      | 4.50     | ns    |

| t <sub>TOE_IN</sub>      | Test Output Enable Path Delay                                   |        | 3.70  |          | 3.70 |      | 3.70 |      | 6.17     | ns    |

| _                        | and MUX Delays                                                  |        |       |          |      |      |      |      |          |       |

| t <sub>IPAC</sub>        | Input Path Adjacent I/O Cell Delay<br>(Shift Register)          | K      | 0.80  | _        | 0.80 | -    | 0.80 | -    | 1.33     | ns    |

| t <sub>OPAC</sub>        | Output Path Adjacent I/O Cell Delay (Shift Register)            | -      | 1.30  |          | 1.30 | _    | 1.30 |      | 2.17     | ns    |

| t <sub>MUXPD</sub>       | MUX Data Path Delay                                             | -      | 0.90  | <b>_</b> | 0.90 |      | 0.90 | —    | 1.29     | ns    |