## Pin Diagram

**TOP VIEW**

| _ | 1         | 2         | 3         | 4         | 5        | 6      | 7          | 8        | 9         | 10        | 11        | 12        |

|---|-----------|-----------|-----------|-----------|----------|--------|------------|----------|-----------|-----------|-----------|-----------|

| Α | hpdiff0_p | VDD0      | O<br>NC   | VDD1      | osco_1V8 | VDD2   | osco_3V3   | osci_3V3 | VDD3      | O<br>NC   | VDD4      | hpdiff2_p |

| В | hpdiff0_n | VSS       | O<br>NC   | VSS       | osci_1V8 | Vss    | XOin       | VCORE0   | Vss       | NC        | VSS       | hpdiff2_n |

| С | hpdiff1_p | hpdiff1_n | VDD5      | Vss       | VSS      | VCORE1 | VSS        | VSS      | VSS       | VDD6      | hpdiff3_n | hpdiff3_p |

| D | VDD7      | VSS       | hpoutclk0 | hpoutclk1 | VSS      | VSS    | VSS        | VSS      | hpoutclk3 | hpoutclk2 | VSS       | VDD8      |

| E | O<br>NC   | VDD9      | VDD10     | VSS       | VSS      | VSS    | Vss        | Vss      | Vss       | VDD11     | O<br>IC1  | O<br>NC   |

| F | O<br>NC   | trst_b    | hpoutclk4 | hpoutclk5 | VSS      | VSS    | Vss        | VSS      | NC        | O<br>NC   | pwr_b     | O<br>NC   |

| G | tdi       | tdo       | tms       | VSS       | VSS      | VSS    | VSS        | VSS      | VDD12     | gpio1     | gpio0     | O<br>IC2  |

| Н | hpdiff4_p | hpdiff4_n | tck       | VSS       | VSS      | VSS    | Vss        | VSS      | VCORE2    | gpio2     | NC NC     | O<br>NC   |

| J | VDD13     | VSS       | gpio4     | VSS       | VSS      | VSS    | Vss        | VSS      | VCORE3    | gpio3     | VSS       | VDD14     |

| K | hpdiff5_p | hpdiff5_n | gpio5     | gpio6     | VSS      | VCORE4 | cs_b_asel0 | sck_scl  | si_sda    | so_asel1  | NC        | O<br>NC   |

| L | VDD15     | Vss       | ref1_p    | ref1_n    | ref3_p   | ref3_n | ref5_p     | ref5_n   | ref6_n    | ref8_p    | ref8_n    | ref10     |

| М | VCORE5    | VSS       | ref0_p    | ref0_n    | ref2_p   | ref2_n | ref4_p     | ref4_n   | ref6_p    | ref7_p    | ref7_n    | ref9      |

- A1 corner is identified by metallized markings.

Figure 2 - Pin Diagram

## 2.0 Pin Description

All device inputs and outputs are LVCMOS unless it is specifically stated to be differential. For the I/O column, there are digital inputs (I), digital outputs (O), analog inputs (A-I) and analog outputs (A-O).

| Ball #                                                                                                       | Name                                                                                                                    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Ref                                                                                                    | erence                                                                                                                  | I   |                                                                                                                                                                                                                                                                                                                                                                                    |

| M3<br>M4<br>L3<br>L4<br>M5<br>M6<br>L5<br>L6<br>M7<br>M8<br>L7<br>L8<br>M9<br>L9<br>M10<br>M11<br>L10<br>L11 | ref0_p ref0_n ref1_p ref1_n ref2_p ref2_n ref3_p ref3_n ref4_p ref4_n ref5_p ref5_n ref6_n ref6_n ref7_p ref8_n ref8_n  | I   | Input References 0 to 8. Input reference sources used for synchronization. The positive and negative pair of these inputs accepts a differential input signal. The refx_p input terminal accepts a CMOS input reference. These inputs can be used as an external feedback input.  Maximum frequency limit on single ended inputs is 177.5 MHz, and 750 MHz on differential inputs. |

| M12<br>L12                                                                                                   | ref9<br>ref10                                                                                                           | I   | Input References 9 and 10. Input reference sources used for synchronization. These inputs are the same as inputs 0 to 8, but only single ended. These inputs can be used as an external feedback input.  Maximum frequency limit is 177.5 MHz                                                                                                                                      |

| Output C                                                                                                     | locks                                                                                                                   |     | Waxing in requestey innic is 177.5 Wi12                                                                                                                                                                                                                                                                                                                                            |

| D3<br>D4<br>D10<br>D9<br>F3<br>F4                                                                            | hpoutclk0<br>hpoutclk1<br>hpoutclk2<br>hpoutclk3<br>hpoutclk4<br>hpoutclk5                                              | 0   | High Performance Output Clocks 0 to 5. These outputs can be configured to provide any one of the single ended high performance clock outputs.  Maximum frequency limit on single ended LVCMOS outputs is 177.5 MHz.                                                                                                                                                                |

| A1<br>B1<br>C1<br>C2<br>A12<br>B12<br>C12<br>C11<br>H1<br>H2<br>K1                                           | hpdiff0_p hpdiff0_n hpdiff1_p hpdiff1_n hpdiff2_p hpdiff2_n hpdiff3_p hpdiff3_n hpdiff4_p hpdiff4_n hpdiff5_p hpdiff5_n | 0   | High Performance Differential Output Clocks 0 to 5 (LVPECL). These outputs can be configured to provide any one of the available high performance differential output clocks.  Maximum frequency limit on differential outputs is 750 MHz.                                                                                                                                         |

**Table 1 - Pin Description**

| Ball #                                     | Name                                                        | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------|-------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control a                                  | nd Status                                                   | •   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| F11                                        | pwr_b                                                       | I   | <b>Power-on Reset.</b> A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. The <b>pwr_b</b> pin should be held low for 2 ms after all power supplies are stabilized. This pin is internally pulled-up to V <sub>DD</sub> . User can access device registers either 125 ms after <b>pwr_b</b> goes high, or after bit 7 in register at address 0x000 goes high (which can be determined by polling).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| G11<br>G10<br>H10<br>J10<br>J3<br>K3<br>K4 | gpio0<br>gpio1<br>gpio2<br>gpio3<br>gpio4<br>gpio5<br>gpio6 | 1/O | General Purpose Input and Output pins. These are general purpose I/O pins.  Example GPIO functions include:  DPLL lock indicators  Reference fail indicators  Reference select control or monitor  Differential output clock enable  High performance LVCMOS outputs enable  Host Interrupt Output to flag status changes.  All GPIO functions are listed in section 5.2, "GPIO Configuration".  Pins 5:0 are internally pulled down to GND and pin 6 is internally pulled up to V <sub>DD</sub> .  Unused GPIO pins can be left unconnected.  After power on reset, device GPIO[0,1,3,4] configure basic device function. GPIO3 sets I <sup>2</sup> C or SPI control mode, GPIO[1,0] sets master clock rate selection. The GPIO[0,1,3] pins must be either pulled low or high with an external 1 kohms resistor for their assigned functions at reset; or they must be driven low or high for 125 ms after reset, and released and then used for normal GPIO functions.  The GPIO4 pin must be either pulled low with an external 1 kohms resistor; or it must be driven low for 125 ms after reset, and then released and used for normal GPIO functions.  GPIO[5,6] are not used during power up. |

| Host Inte                                  | rface                                                       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| K8                                         | sck_scl                                                     | I/O | Clock for Serial Interface. Provides clock for serial micro-port interface. This pin is also the serial clock line (SCL) when the host interface is configured for $I^2C$ mode. As an input this pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| K9                                         | si_sda                                                      | I/O | <b>Serial Interface Input.</b> The serial data stream holds the access command, the address and the write data bits. This pin is also the serial data line (SDA) when host interface is configured for $I^2C$ mode. This pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| K10                                        | so_asel1                                                    | I/O | <b>Serial Interface Output.</b> As an output, the serial stream holds the read data bits. This pin is also the I <sup>2</sup> C address select when host interface is configured for I <sup>2</sup> C mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

**Table 1 - Pin Description (continued)**

| Ball #                                | Name               | I/O        | Description                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|--------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K7 cs_b_asel0                         |                    | I          | Chip Select for Serial Interface. Serial interface chip select, this is an active low signal. This pin is also the $I^2C$ address select when host interface is configured for $I^2C$ mode. This pin is internally pulled up to $V_{DD}$ .                                                                                                       |

| JTAG (IEE                             | E 1149.1) and Test |            |                                                                                                                                                                                                                                                                                                                                                  |

| G12                                   | IC2                | 1          | Internal Connection. Connect this pin to GND.                                                                                                                                                                                                                                                                                                    |

| E11                                   | IC1                | A-I/O      | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                          |

| G2                                    | tdo                | 0          | <b>Test Serial Data Out.</b> JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.                                                                                                                                                                          |

| G1                                    | tdi                | I          | <b>Test Serial Data In.</b> JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                                        |

| F2                                    | trst_b             | I          | <b>Test Reset.</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be held low or pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be connected to GND. |

| H3                                    | tck                | I          | <b>Test Clock.</b> Provides the clock for the JTAG test logic. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be connected to GND.                                                                                                                                                                        |

| G3                                    | tms                | I          | <b>Test Mode Select.</b> JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                                       |

| Master Clo<br>Note: The os<br>oscilla |                    | e preferre | ed to connect a crystal to the device. The <b>XOin</b> pin is preferred to connect a crystal                                                                                                                                                                                                                                                     |

| A7                                    | osco_3V3           | A-O        | <b>3.3V Crystal Master Clock Output.</b> For the alternative connection method for a crystal, the crystal is connected from this pin to <b>osci_3V3</b> . Not suitable for driving other devices. For clock oscillator operation or the use of a crystal between <b>osci_1V8</b> and <b>osco_1V8</b> , this pin should be left unconnected.      |

| A8                                    | osci_3V3           | I          | <b>3.3V Crystal Master Clock Input.</b> For the alternative connection method for a crystal, the crystal is connected from this pin to <b>osco_3V3</b> . For clock oscillator operation or the use of a crystal between <b>osci_1V8</b> and <b>osco_1V8</b> , this pin should be grounded.                                                       |

| A5                                    | osco_1V8           | A-O        | <b>1.8V Crystal Master Clock Output.</b> For the primary connection method for a crystal, the crystal is connected from this pin to <b>osci_1V8</b> . Not suitable for driving other devices. For clock oscillator operation or the use of a crystal between <b>osci_3V3</b> and <b>osco_3V3</b> , this pin should be left unconnected.          |

| B5                                    | osci_1V8           | I          | 1.8V Crystal Master Clock Input. For the primary connection method for a crystal, the crystal is connected from this pin to osco_1V8. For clock oscillator operation or the use of a crystal between osci_3V3 and osco_3V3, this pin should be grounded.                                                                                         |

Table 1 - Pin Description (continued)

| Ball #                                                                                            | Name                                                                                                                                                                                                                                                                                  | I/O | Description                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7                                                                                                | XOin                                                                                                                                                                                                                                                                                  | I   | XO Master Clock Output. For clock oscillator operation, this pin is connected to the output of the oscillator. For crystal operation using either method, this pin should be grounded. |

| Power and                                                                                         | d Ground                                                                                                                                                                                                                                                                              |     |                                                                                                                                                                                        |

| B8<br>C6<br>H9<br>J9<br>K6<br>M1                                                                  | VCORE0<br>VCORE1<br>VCORE2<br>VCORE3<br>VCORE4<br>VCORE5                                                                                                                                                                                                                              |     | Positive Supply Voltage. +1.8V <sub>DC</sub> nominal.  These pins should not be connected together on the board. Please refer to ZLAN-327 for recommendations                          |

| A2<br>A4<br>A6<br>A9<br>A11<br>C3<br>C10<br>D1<br>D12<br>E2<br>E3<br>E10<br>G9<br>J1<br>J12<br>L1 | V <sub>DD0</sub> V <sub>DD1</sub> V <sub>DD2</sub> V <sub>DD3</sub> V <sub>DD4</sub> V <sub>DD5</sub> V <sub>DD6</sub> V <sub>DD7</sub> V <sub>DD8</sub> V <sub>DD9</sub> V <sub>DD10</sub> V <sub>DD11</sub> V <sub>DD12</sub> V <sub>DD13</sub> V <sub>DD14</sub> V <sub>DD15</sub> |     | Positive Supply Voltage. +3.3V <sub>DC</sub> nominal.  These pins should not be connected together on the board. Please refer to ZLAN-327 for recommendations                          |

Table 1 - Pin Description (continued)

| Ball #                                                                                                                                                                                                                                                                                                                                                                                                                                         | Name            | I/O | Description      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|------------------|

| B2<br>B4<br>B6<br>B9<br>B11<br>C4<br>C5<br>C7<br>C8<br>D2<br>D11<br>E4<br>E9<br>G4<br>H4<br>H5<br>H6<br>H7<br>H8<br>J4<br>J5<br>D6<br>D7<br>D8<br>E5<br>E6<br>F7<br>F8<br>G6<br>G7<br>G8<br>G7<br>G8<br>G7<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>G7<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8 | V <sub>SS</sub> |     | Ground. 0 Volts. |

Table 1 - Pin Description (continued)

| Ball # | Name | I/O | Description                                 |

|--------|------|-----|---------------------------------------------|

| A3     | NC   |     | No Connect. These pins should be left open. |

| A10    |      |     |                                             |

| B3     |      |     |                                             |

| B10    |      |     |                                             |

| E1     |      |     |                                             |

| E12    |      |     |                                             |

| F1     |      |     |                                             |

| F9     |      |     |                                             |

| F10    |      |     |                                             |

| F12    |      |     |                                             |

| H11    |      |     |                                             |

| H12    |      |     |                                             |

| K12    |      |     |                                             |

| K11    |      |     |                                             |

Table 1 - Pin Description (continued)

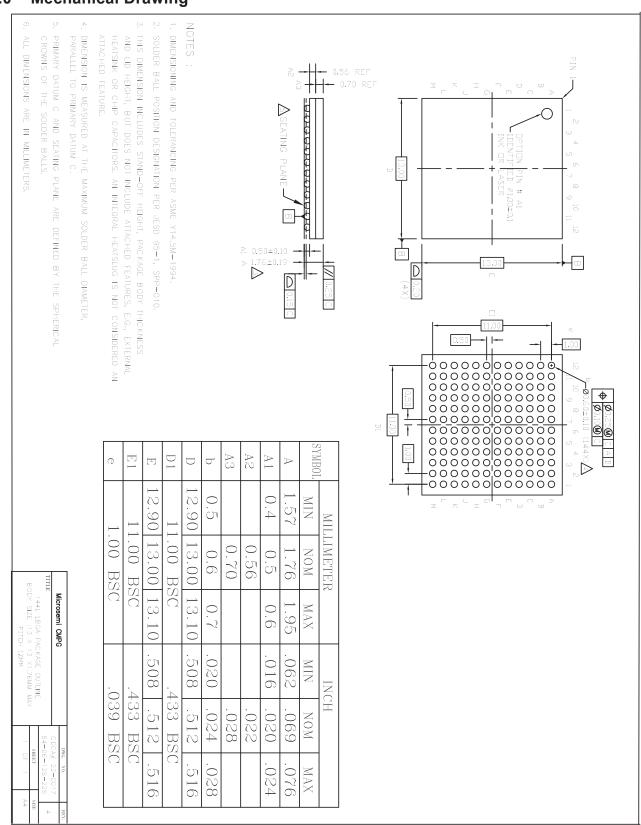

## 3.0 Mechanical Drawing

Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively "Microsemi") is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.

This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi's conditions of sale which are available on request.

For more information about all Microsemi products visit our website at www.microsemi.com/timing-and-synchronization

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2013 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.