12-channel power management integrated circuit for high performance applications

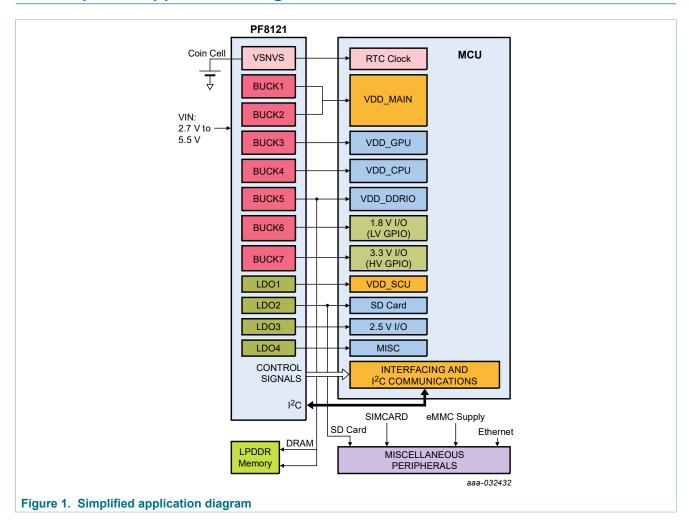

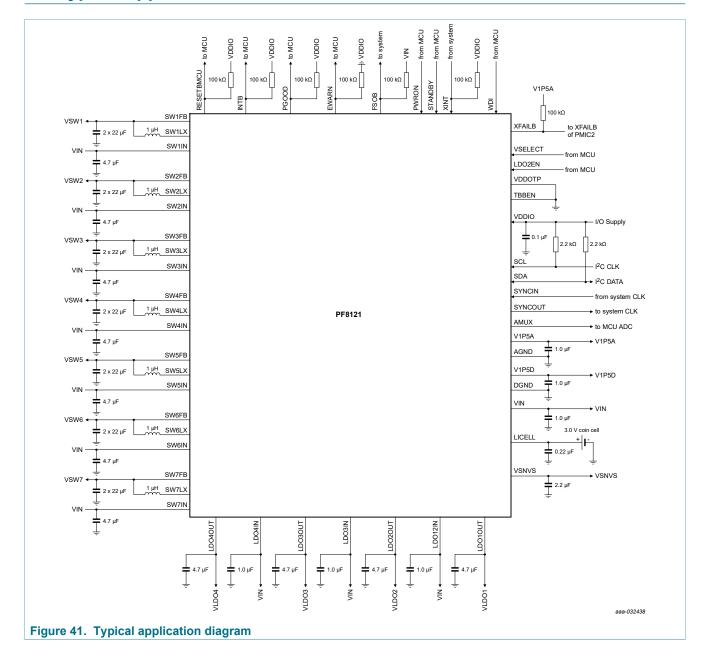

# 3 Simplified application diagram

# 4 Ordering information

### Table 1. Device options

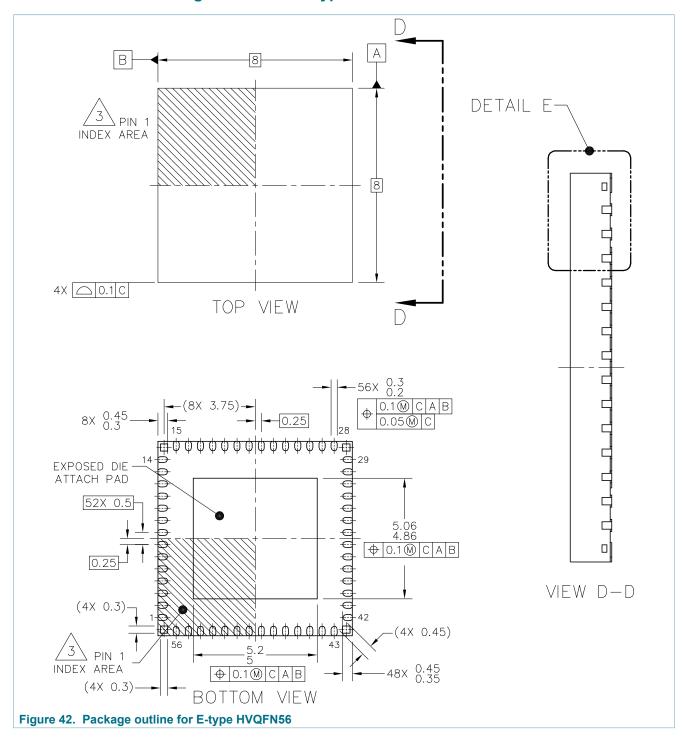

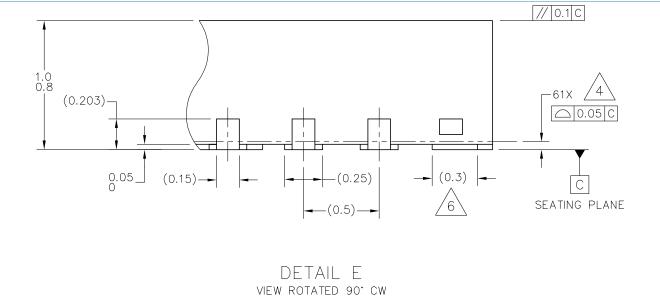

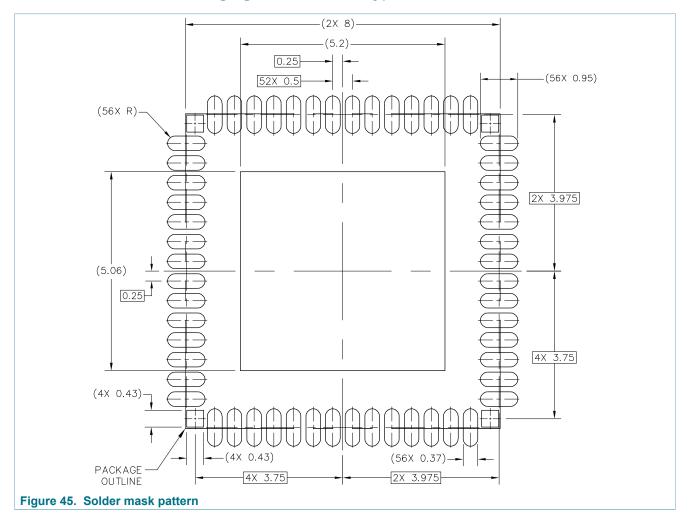

| Туре   | Package |                                                                                                                                      |           |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------|-----------|

|        | Name    | Description                                                                                                                          | Version   |

| PF8121 |         | HVQFN56, plastic, thermally enhanced very thin quad; flat non-leaded package, 56 terminals; 0.5 mm pitch; 8 mm x 8 mm x 0.85 mm body | SOT684-21 |

**Table 2. Ordering information**

| Part number [1] | Target market | NXP<br>processor | System comments                                 | Safety grade | OTP ID                                       |

|-----------------|---------------|------------------|-------------------------------------------------|--------------|----------------------------------------------|

| MC32PF8121A0EP  | Consumer      | i.MX8M Mini      | Not programmed                                  | n/a          | n/a                                          |

| MC32PF8121EUEP  | Consumer      | i.MX8M Mini      | LPDDR4 (Vin > 4.0 V, SW7 = 3.3 V, SW4 = 1.8 V)  | n/a          | http://www.nxp.com/MC32PF8121EUEP-OTP-Report |

| MC32PF8121F1EP  | Consumer      | i.MX8M Mini      | LPDDR4 memory                                   | n/a          | http://www.nxp.com/MC32PF8121F1EP-OTP-Report |

| MC32PF8121F2EP  | Consumer      | i.MX8M Mini      | DDR3L (external VTT)                            | n/a          | http://www.nxp.com/MC32PF8121F2EP-OTP-Report |

| MC32PF8121G5EP  | Consumer      | i.MX8M Mini      | LPDDR4 (Vin > 4.0 V, SW7 = 3.3 V, SW4 = 0.85 V) | n/a          | http://www.nxp.com/MC32PF8121G5EP-OTP-Report |

PF8121

All information provided in this document is subject to legal disclaimers.

# 12-channel power management integrated circuit for high performance applications

[1] To order parts in tape and reel, add the R2 suffix to the part number.

# 5 Applications

- IoT devices

- Industrial

## 12-channel power management integrated circuit for high performance applications

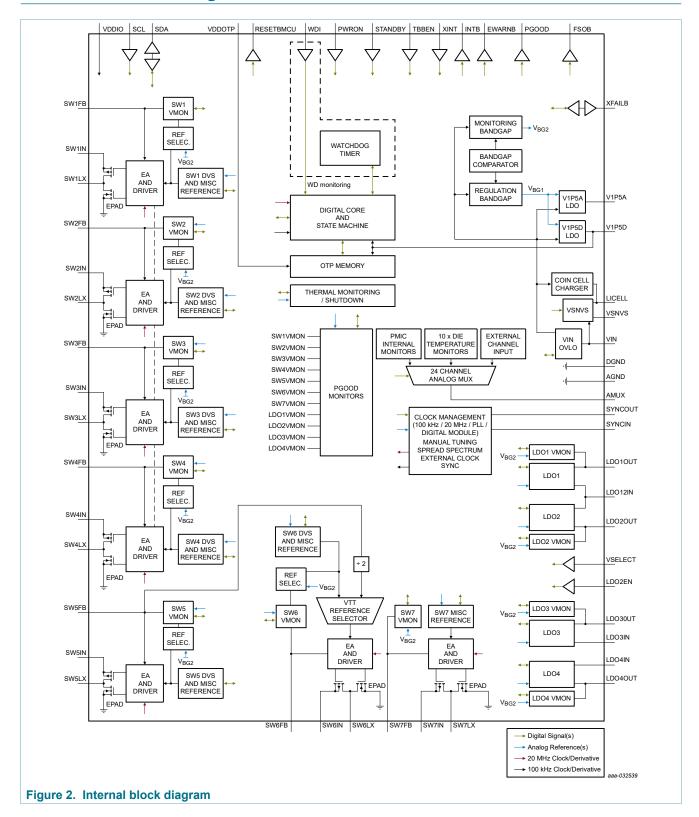

# 6 Internal block diagram

PF812

All information provided in this document is subject to legal disclaimers.

12-channel power management integrated circuit for high performance applications

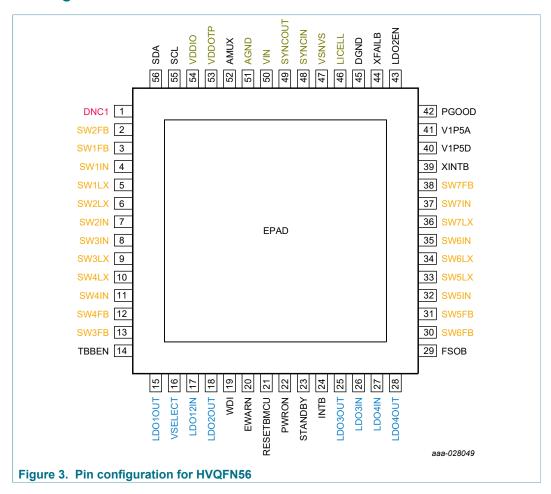

# 7 Pinning information

## 7.1 Pinning

## 7.2 Pin description

Table 3. HVQFN56 pin description

| Pin number | Symbol    | Application description        | Pin type | Min  | Max | Units |

|------------|-----------|--------------------------------|----------|------|-----|-------|

| 1          | DNC1      | Do not connect                 | _        | _    | _   | V     |

| 2          | SW2FB     | Buck 2 output voltage feedback | I        | -0.3 | 6.0 | V     |

| 3          | SW1FB     | Buck 1 output voltage feedback | I        | -0.3 | 6.0 | V     |

| 4          | SW1IN     | Buck 1 input supply            | I        | -0.3 | 6.0 | V     |

| 5          | SW1LX [1] | Buck 1 switching node          | 0        | -0.3 | 6.0 | V     |

| 6          | SW2LX [1] | Buck 2 switching node          | 0        | -0.3 | 6.0 | V     |

| 7          | SW2IN     | Buck 2 input supply            | I        | -0.3 | 6.0 | V     |

| 8          | SW3IN     | Buck 3 input supply            | ı        | -0.3 | 6.0 | V     |

| 9          | SW3LX [1] | Buck 3 switching node          | 0        | -0.3 | 6.0 | V     |

| 10         | SW4LX [1] | Buck 4 switching node          | 0        | -0.3 | 6.0 | V     |

| 11         | SW4IN     | Buck 4 input supply            | I        | -0.3 | 6.0 | V     |

PF8121

All information provided in this document is subject to legal disclaimers.

# 12-channel power management integrated circuit for high performance applications

| Pin number | Symbol    | Application description                         | Pin type | Min  | Max | Units |

|------------|-----------|-------------------------------------------------|----------|------|-----|-------|

| 12         | SW4FB     | Buck 4 output voltage feedback                  | I        | -0.3 | 6.0 | V     |

| 13         | SW3FB     | Buck 3 output voltage feedback                  | ı        | -0.3 | 6.0 | V     |

| 14         | TBBEN     | Try Before Buy enable pin                       | I        | -0.3 | 6.0 | V     |

| 15         | LDO10UT   | LDO1 output                                     | 0        | -0.3 | 6.0 | V     |

| 16         | VSELECT   | LDO2 voltage select input                       | I        | -0.3 | 6.0 | V     |

| 17         | LDO12IN   | LDO1 and LDO2 input supply                      | I        | -0.3 | 6.0 | V     |

| 18         | LDO2OUT   | LDO2 output                                     | 0        | -0.3 | 6.0 | V     |

| 19         | WDI       | Watchdog Input from MCU                         | I        | -0.3 | 6.0 | V     |

| 20         | EWARN     | Early warning to MCU                            | 0        | -0.3 | 6.0 | V     |

| 21         | RESETBMCU | RESETBMCU open-drain output                     | 0        | -0.3 | 6.0 | V     |

| 22         | PWRON     | PWRON input                                     | I        | -0.3 | 6.0 | V     |

| 23         | STANDBY   | STANDBY input                                   | I        | -0.3 | 6.0 | V     |

| 24         | INTB      | INTB open-drain output                          | 0        | -0.3 | 6.0 | V     |

| 25         | LDO3OUT   | LDO3 output                                     | 0        | -0.3 | 6.0 | V     |

| 26         | LDO3IN    | LDO3 input supply                               | I        | -0.3 | 6.0 | V     |

| 27         | LDO4IN    | LDO4 input supply                               | I        | -0.3 | 6.0 | V     |

| 28         | LDO4OUT   | LDO4 output                                     | 0        | -0.3 | 6.0 | V     |

| 29         | FSOB      | Fault notification output                       | 0        | -0.3 | 6.0 | V     |

| 30         | SW6FB     | Buck 6 output voltage feedback                  | I        | -0.3 | 6.0 | V     |

| 31         | SW5FB     | Buck 5 output voltage feedback                  | I        | -0.3 | 6.0 | V     |

| 32         | SW5IN     | Buck 5 input supply                             | I        | -0.3 | 6.0 | V     |

| 33         | SW5LX [1] | Buck 5 switching node                           | 0        | -0.3 | 6.0 | V     |

| 34         | SW6LX [1] | Buck 6 switching node                           | 0        | -0.3 | 6.0 | V     |

| 35         | SW6IN     | Buck 6 input supply                             | I        | -0.3 | 6.0 | V     |

| 36         | SW7LX [1] | Buck 7 switching node                           | 0        | -0.3 | 6.0 | V     |

| 37         | SW7IN     | Buck 7 input supply                             | I        | -0.3 | 6.0 | V     |

| 38         | SW7FB     | Buck 7 output voltage feedback                  | I        | -0.3 | 6.0 | V     |

| 39         | XINTB     | External interrupt input                        | I        | -0.3 | 6.0 | V     |

| 40         | V1P5D     | 1.6 V digital core supply                       | 0        | -0.3 | 2.0 | V     |

| 41         | V1P5A     | 1.6 V analog core supply                        | 0        | -0.3 | 2.0 | V     |

| 42         | PGOOD     | PGOOD open-drain output                         | 0        | -0.3 | 6.0 | V     |

| 43         | LDO2EN    | LDO2 enable pin                                 | I        | -0.3 | 6.0 | V     |

| 44         | XFAILB    | External Synchronization pin                    | I/O      | -0.3 | 6.0 | V     |

| 45         | DGND      | Digital ground                                  | GND      | -0.3 | 0.3 | V     |

| 46         | LICELL    | Coin cell input                                 | I        | -0.3 | 5.5 | V     |

| 47         | VSNVS     | VSNVS regulator output                          | 0        | -0.3 | 6.0 | V     |

| 48         | SYNCIN    | External clock input pin for synchronization    | I        | -0.3 | 6.0 | V     |

| 49         | SYNCOUT   | Clock out pin for external part synchronization | 0        | -0.3 | 6.0 | V     |

| 50         | VIN       | Main input voltage to PMIC                      | I        | -0.3 | 6.0 | V     |

| 51         | AGND      | Analog ground                                   | GND      | -0.3 | 0.3 | V     |

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

| Pin number | Symbol | Application description                                             | Pin type | Min  | Max | Units |

|------------|--------|---------------------------------------------------------------------|----------|------|-----|-------|

| 52         | AMUX   | Analog multiplexer output                                           | 0        | -0.3 | 6.0 | V     |

| 53         | VDDOTP | OTP selection input                                                 | I        | -0.3 | 10  | V     |

| 54         | VDDIO  | I/O supply voltage. Connect to voltage rail between 1.6 V and 3.3 V | I        | -0.3 | 6.0 | V     |

| 55         | SCL    | I <sup>2</sup> C clock signal                                       | I        | -0.3 | 6.0 | V     |

| 56         | SDA    | I <sup>2</sup> C data signal                                        | I/O      | -0.3 | 6.0 | V     |

| 57         | EPAD   | Exposed pad Connect to ground                                       | GND      | -0.3 | 0.3 | V     |

<sup>[1]</sup> Minimum voltage specification is given for DC voltage condition. While the regulator is switching, the LX pin may experience transient voltage spikes as low as -3.0 V during the dead band time(<5 ns). The LX pins are tolerant to such transient spikes, however, it is responsibility of the hardware designer to follow proper layout design guidelines to minimize the impact of parasitic inductance in the power path of the switching regulator, thus keeping the magnitude of the negative voltage spike at the LX pin below 3.0 V.

# 8 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol             | Parameter                            | Min  | Тур | Max | Unit |

|--------------------|--------------------------------------|------|-----|-----|------|

| VIN                | Main input supply voltage [1]        | -0.3 | _   | 6.0 | V    |

| SWxVIN,<br>LDOxVIN | Regulator input supply voltage [1]   | -0.3 | _   | 6.0 | V    |

| VDDOTP             | OTP programming input supply voltage | -0.3 | _   | 10  | V    |

| VLICELL            | Coin cell voltage                    | -0.3 | _   | 5.5 | V    |

<sup>[1]</sup> Pin reliability may be affected if system voltages are above the maximum operating range of 5.5 V for extended periods of time. To minimize system reliability impact, system must not operate above 5.5 V for more than 1800 sec over the lifetime of the device.

# 9 ESD ratings

#### Table 5. ESD ratings

All ESD specifications are compliant with AEC-Q100 specification.

| Symbol               | Parameter                                   |     | Min | Тур | Max  | Unit |

|----------------------|---------------------------------------------|-----|-----|-----|------|------|

| V <sub>ESD</sub>     | Human Body Model                            | [1] | _   | _   | 2000 | V    |

| V <sub>ESD</sub>     | Charge Device Model  QFN package - all pins | [1] | _   | _   | 500  | V    |

| I <sub>LATCHUP</sub> | Latch-up current                            |     | _   | _   | 100  | mA   |

<sup>[1]</sup> ESD testing is performed in accordance with the human body model (HBM) (CZAP = 100 pF, RZAP = 1500 Ω), and the charge device model (CDM), robotic (CZAP = 4.0 pF)

## 10 Thermal characteristics

#### Table 6. Thermal characteristics

| Symbol          | Parameter                         | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|-----|-----|-----|------|

| T <sub>A</sub>  | Ambient operating temperature [1] | -40 | _   | 85  | °C   |

| TJ              | Junction temperature              | -40 | _   | 150 | °C   |

| T <sub>ST</sub> | Storage temperature range         | -55 | _   | 150 | °C   |

PF8121

All information provided in this document is subject to legal disclaimers.

### 12-channel power management integrated circuit for high performance applications

| Symbol            | Parameter                       | Min | Тур | Max | Unit |

|-------------------|---------------------------------|-----|-----|-----|------|

| T <sub>PPRT</sub> | Peak package reflow temperature | _   | _   | 260 | °C   |

<sup>[1]</sup> All parameters are specified up to a junction temperature of 150 °C. All parameters are tested at T<sub>A</sub> from -40°C to 85 °C to allow headroom for self heating during operation. If higher T<sub>A</sub> operation is required, proper thermal and loading consideration must be made to ensure device operation below the maximum T<sub>J</sub> = 150 °C.

Table 7. QFN56 thermal resistance and package dissipation ratings

| Symbol           | Parameter                                                          |         | Min | Max | Unit |

|------------------|--------------------------------------------------------------------|---------|-----|-----|------|

| $R_{\theta JA}$  | Junction to Ambient Natural Convection Single Layer Board (1s)     | [1] [2] | _   | 81  | °C/W |

| $R_{\theta JA}$  | Junction to Ambient Natural Convection<br>Four Layer Board (2s2p)  | [1] [2] | _   | 27  | °C/W |

| $R_{\theta JA}$  | Junction to Ambient Natural Convection<br>Eight Layer Board (2s6p) |         | _   | 22  | °C/W |

| $R_{\theta JMA}$ | Junction to Ambient (@200ft/min) Single Layer Board (1s)           | [1] [3] | _   | 66  | °C/W |

| $R_{\theta JMA}$ | Junction to Ambient (@200ft/min) Four Layer Board (2s2p)           | [1] [3] | _   | 22  | °C/W |

| $R_{\theta JB}$  | Junction to Board                                                  | [4]     | _   | 11  | °C/W |

| R <sub>θJC</sub> | Junction to Case (bottom)                                          | [5]     | _   | 0.6 | °C/W |

| ΨJT              | Junction to package (top)                                          | [6]     | _   | 1   | °C/W |

- [1] Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- [2] Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board

- near the package.

[5] Thermal resistance between the die and the solder pad on the bottom of the package. Interface resistance is ignored.

- [6] Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

# 11 Operating conditions

**Table 8. Operating conditions**

| - table of operating contained |                            |       |     |     |      |  |  |  |  |

|--------------------------------|----------------------------|-------|-----|-----|------|--|--|--|--|

| Symbol                         | Parameter                  | Min   | Тур | Max | Unit |  |  |  |  |

| V <sub>IN</sub>                | Main input supply voltage  | UVDET | _   | 5.5 | V    |  |  |  |  |

| V <sub>LICELL</sub>            | LICELL input voltage range | _     | _   | 4.2 | V    |  |  |  |  |

# 12 General description

#### 12.1 Features

The PF8121 is a power management integrated circuit (PMIC) designed to be the primary power management building block for NXP high-end multimedia application processors. It is also capable of providing power solution to the high end i.MX 6 series as well as several non-NXP processors.

- Buck regulators

- SW1, SW2, SW3, SW4, SW5, SW6: 0.4 V to 1.8 V; 2500 mA; up to 1.5 % accuracy

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

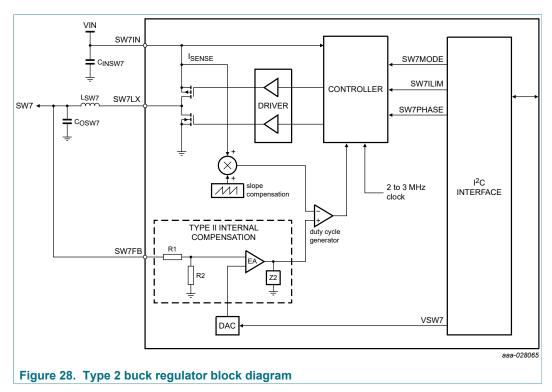

- SW7; 1.0 V to 4.1 V; 2500 mA; 2 % accuracy

- Dynamic voltage scaling on SW1, SW2, SW3, SW4, SW5, and SW6

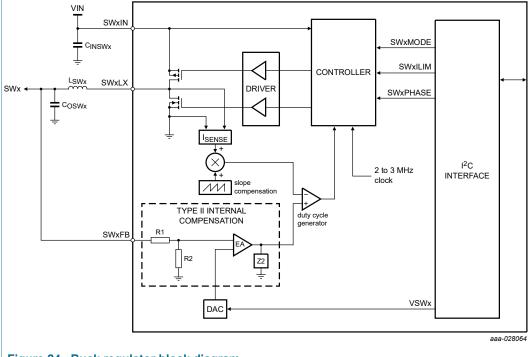

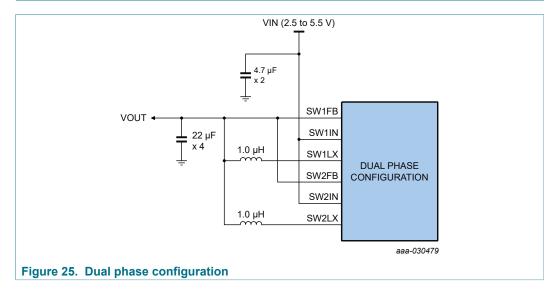

- SW1, SW2 configurable as a dual phase regulator

- SW3, SW4 configurable as a dual phase regulator

- SW5, SW6 configurable as a dual phase regulator

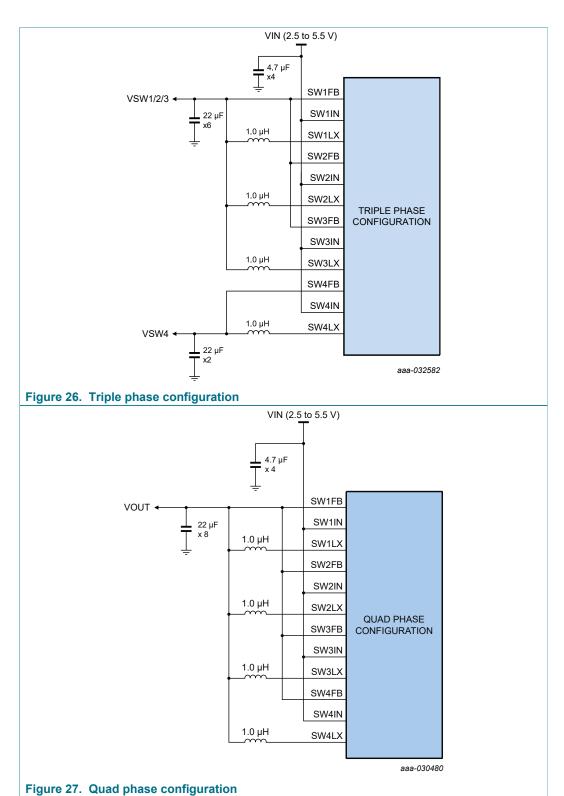

- SW1, SW2 and SW3 configurable as a triple phase regulator with up to 7.5 A current capability

- SW1, SW2, SW3 and SW4 configurable as a quad phase regulator with up to 10 A current capability

- VTT termination mode on SW6

- Programmable current limit

- Spread-spectrum and manual tuning of switching frequency

- LDO regulators

- LDO1, 1.5 V to 5.0 V, 400 mA: 3 % accuracy with optional load switch mode

- LDO2, 1.5 V to 5.0 V, 400 mA; 3 % accuracy with optional load switch mode and selectable hardware/software control

- LDO3, 1.5 V to 5.0 V, 400 mA; 3 % accuracy with optional load switch mode

- LDO4, 1.5 V to 5.0 V, 400 mA; 3 % accuracy with optional load switch mode

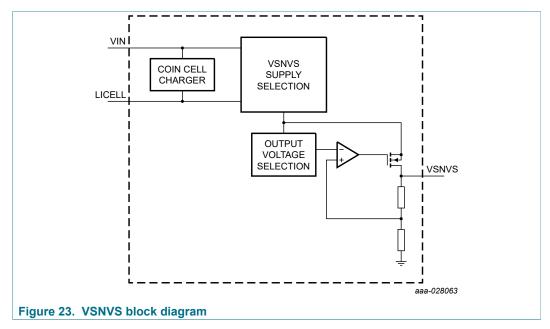

- RTC LDO/Switch supply from system supply or coin cell

- RTC supply VSNVS 1.8 V/3.0 V/3.3 V, 10 mA

- Battery backed memory including coin cell charger with programmable charge current and voltage

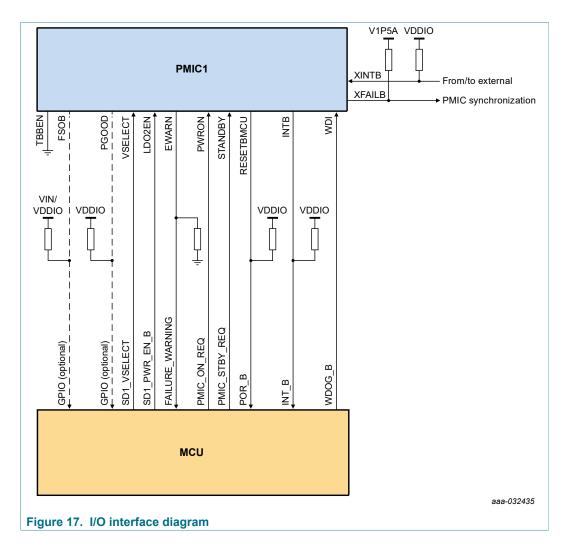

- · System features

- Fast PMIC startup

- Advanced state machine for seamless processor interface

- High speed I<sup>2</sup>C interface support (up to 3.4 MHz)

- PGOOD monitor

- User programmable standby and off modes

- Programmable soft start sequence and power down sequence

- Programmable regulator configuration

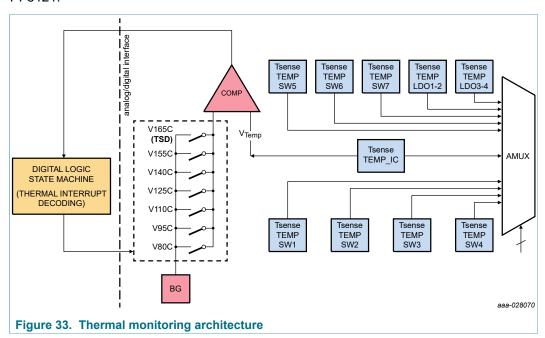

- 24 channel analog multiplexer for smart system monitoring/diagnostic

- OTP (One time programmable) memory for device configuration

- · Voltage and system monitoring

- Independent voltage monitoring with programmable fault protection

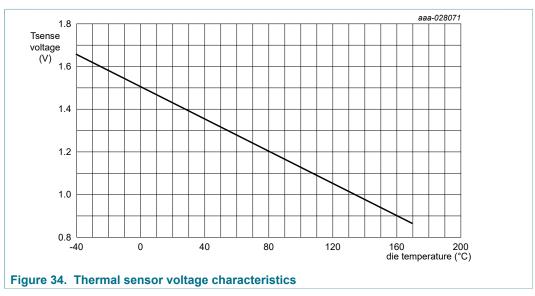

- Advance thermal monitoring and protection

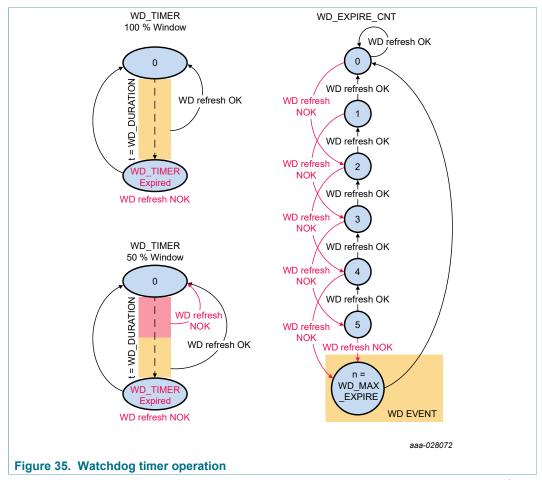

- External watchdog monitoring and programmable internal watchdog counter

- I<sup>2</sup>C cyclic redundancy check (CRC)

12-channel power management integrated circuit for high performance applications

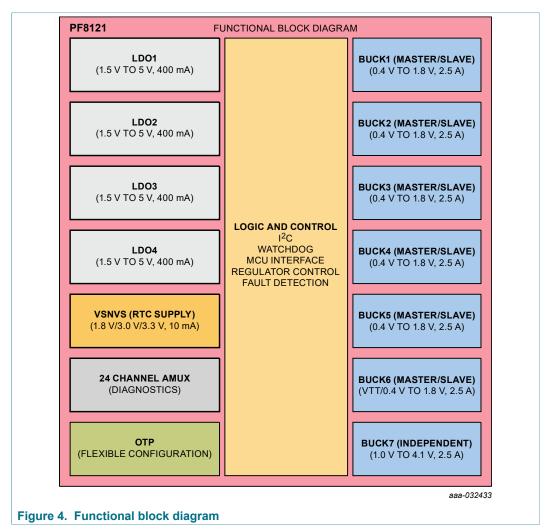

# 12.2 Functional block diagram

# 12.3 Power tree summary

The following table shows a summary of the voltage regulators in the PF8121.

Table 9. Voltage supply summary

| Regulator | Туре            | Input supply | Regulated output range (V) | VOUT programmable step (mV) | IRATED (mA) |

|-----------|-----------------|--------------|----------------------------|-----------------------------|-------------|

| SW1       | Buck            | SW1IN        | 0.4 V to 1.8 V             | 6.25                        | 2500        |

| SW2       | Buck            | SW2IN        | 0.4 V to 1.8 V             | 6.25                        | 2500        |

| SW3       | Buck            | SW3IN        | 0.4 V to 1.8 V             | 6.25                        | 2500        |

| SW4       | Buck            | SW4IN        | 0.4 V to 1.8 V             | 6.25                        | 2500        |

| SW5       | Buck            | SW5IN        | 0.4 V to 1.8 V             | 6.25                        | 2500        |

| SW6       | Buck            | SW6IN        | VTT/0.4 V to 1.8 V         | 6.25                        | 2500        |

| SW7       | Buck            | SW7IN        | 1.0 V to 4.1 V             | _                           | 2500        |

| LDO1      | Linear (P-type) | LDO12IN      | 1.5 V to 5.0 V             | _                           | 400         |

PF8121

All information provided in this document is subject to legal disclaimers.

# 12-channel power management integrated circuit for high performance applications

| Regulator | Туре            | Input supply | Regulated output range (V) | VOUT programmable step (mV) | IRATED (mA) |

|-----------|-----------------|--------------|----------------------------|-----------------------------|-------------|

| LDO2      | Linear (P-type) | LDO12IN      | 1.5 V to 5.0 V             | _                           | 400         |

| LDO3      | Linear (P-type) | LDO3IN       | 1.5 V to 5.0 V             | _                           | 400         |

| LDO4      | Linear (P-type) | LDO4IN       | 1.5 V to 5.0 V             | _                           | 400         |

| VSNVS     | LDO/Switch      | VIN/LICELL   | 1.8 V/3.0 V/3.3 V          | _                           | 10          |

12-channel power management integrated circuit for high performance applications

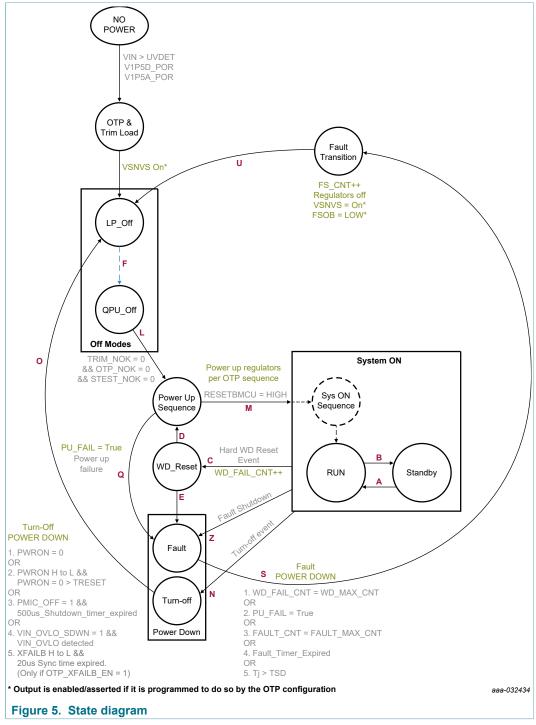

# 13 State machine

The PF8121 features a state of the art state machine for seamless processor interface. The state machine handles the IC start up, provides fault monitoring and reporting, and protects the IC and the system during fault conditions.

Table 10 lists the conditions for the different state machine transitions.

PF8121

All information provided in this document is subject to legal disclaimers.

# 12-channel power management integrated circuit for high performance applications

Table 10. State machine transition definition

| Symbol                         | Description                    | Conditions                                                                                                                                                                                                                      |

|--------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T:4: A                         | Character was                  | 1. STANDBY = 0 && STANDBYINV bit = 0                                                                                                                                                                                            |

| Transition A                   | Standby to run                 | 2. STANDBY = 1 && STANDBYINV bit = 1                                                                                                                                                                                            |

| - ···                          |                                | 1. STANDBY = 1 && STANDBYINV bit = 0                                                                                                                                                                                            |

| Transition B                   | Run to standby                 | 2. STANDBY = 0 && STANDBYINV bit = 1                                                                                                                                                                                            |

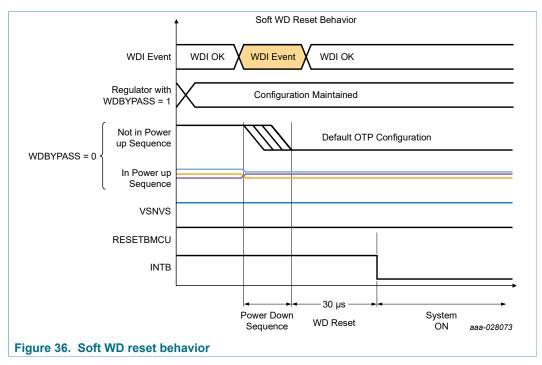

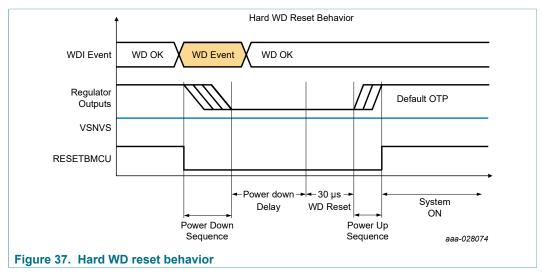

| Transition C                   | System on to WD reset          | 1. Hard WD Reset event                                                                                                                                                                                                          |

| Transition D                   | WD reset to system on          | 1. 30 µs delay passed && WD_EVENT_CNT < WD_MAX_CNT                                                                                                                                                                              |

| Transition E                   | WD reset to power down (fault) | 1. WD_EVENT_CNT = WD_MAX_CNT                                                                                                                                                                                                    |

|                                |                                | Transitory Off state: device pass through LP_Off to QPU_Off (no power up event present)  1. LPM_OFF = 1  && TBBEN = Low                                                                                                         |

| Transition F LP_Off to QPU_Off |                                | Power up event from LP_Off state  2. LPM_OFF = 0  && TBBEN = Low  && (PWRON = 1 && OTP_PWRON_MODE = 0)  && UVDET< VIN < VIN_OVLO (or VIN_OVLO disabled)  && T <sub>J</sub> < T <sub>SD</sub> && TRIM_NOK = 0 && OTP_NOK = 0     |

|                                |                                | Power up event from LP_Off state  3. LPM_OFF = 0  && TBBEN = Low  && (PWRON H to L && OTP_PWRON_MODE = 1)  && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled)  && T <sub>J</sub> < T <sub>SD</sub> && TRIM_NOK = 0 && OTP_NOK = 0 |

|                                |                                | Transitory Off state: device pass through LP_Off to QPU_Off (no power up event present) 4. TBBEN = High (V1P5D)                                                                                                                 |

# 12-channel power management integrated circuit for high performance applications

| Symbol       | Description                                                                                                                                                                                                                                 | Conditions                                                                                                                                                                                                                                                                          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                                                                                                                                                                                                             | Transitory QPU_Off state, power on event occurs from LP_Off state, after self-test is passed, QPU_Off is just a transitory state until power up sequence starts.  1. LPM_OFF = 0  && TBBEN = Low  && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0                                   |

|              |                                                                                                                                                                                                                                             | Power up event from QPU_Off state  2. LPM_OFF = 1  && (PWRON = 1 && OTP_PWRON_MODE = 0)  && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled  && T_J < T_{SD}  && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0                                                                          |

|              |                                                                                                                                                                                                                                             | Power up event from QPU_Off state  3. LPM_OFF = 1  && (PWRON H to L && OTP_PWRON_MODE = 1)  && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled)  && T <sub>J</sub> < T <sub>SD</sub> && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0                                                   |

|              |                                                                                                                                                                                                                                             | Power up event from QPU_Off state  4. TBBEN = High  && (PWRON = 1 && OTP_PWRON_MODE = 0)  && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled  && T <sub>J</sub> < T <sub>SD</sub> && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0                                                      |

| Transition L | QPU_Off to power up                                                                                                                                                                                                                         | Power up event from QPU_Off state  5. TBBEN = High  && (PWRON H to L && OTP_PWRON_MODE = 1)  && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled)  && T <sub>J</sub> < T <sub>SD</sub> && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK=0                                                    |

|              |                                                                                                                                                                                                                                             | Transitory QPU_Off state, Power on event occurs from LP_Off state, after self-test is passed, QPU_Off is just a transitory state until power up sequence starts 6. LPM_OFF = 0 && TBBEN = Low && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0 && OTP_XFAILB_EN = 1 && XFAILB = HIGH |

|              | Power up event from QPU_Off state 7. LPM_OFF = 1 && (PWRON = 1 && OTP_PWRON_MODE = 0) && T_J < T_{SD} && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0 && OTP_XFAILB_EN = 1 && XFAILB = HIGH |                                                                                                                                                                                                                                                                                     |

|              |                                                                                                                                                                                                                                             | Power up event from QPU_Off state  8. LPM_OFF = 1  && (PWRON H to L && OTP_PWRON_MODE = 1)  && T <sub>J</sub> < T <sub>SD</sub> && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled)  && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0  && OTP_XFAILB_EN = 1 && XFAILB = HIGH            |

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

| Symbol       | Description                            | Conditions                                                                                                                                                                                                                                                                              |

|--------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                        | Power up event from QPU_Off state during TBB mode  9. TBBEN =1  && (PWRON = 1 && OTP_PWRON_MODE = 0)  && T <sub>J</sub> < T <sub>SD</sub> && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled)  && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0  && OTP_XFAILB_EN = 1 && XFAILB = HIGH      |

|              |                                        | Power up event from QPU_Off state during TBB mode  10. TBBEN = 1  && (PWRON H to L && OTP_PWRON_MODE = 1)  && T <sub>J</sub> < T <sub>SD</sub> && UVDET < VIN < VIN_OVLO (or VIN_OVLO disabled)  && TRIM_NOK = 0 && OTP_NOK = 0 && STEST_NOK = 0  && OTP_XFAILB_EN = 1 && XFAILB = HIGH |

| Transition M | Power up sequence to system on         | RESETBMCU is released as part of the power up sequence                                                                                                                                                                                                                                  |

|              |                                        | Requested turn off event  1. OTP_PWRON_MODE = 0 && PWRON = 0                                                                                                                                                                                                                            |

|              |                                        | Requested turn off event  2. OTP_PWRON_MODE = 1 && (PWRON H to L && PWRON = low for t > TRESET)                                                                                                                                                                                         |

| Transition N | System on to power down (turn off)     | Requested turn off event 3. PMIC_OFF = 1 && 500µs_Shutdown_Timer_Expired                                                                                                                                                                                                                |

|              |                                        | Protective turn off event (no PMIC fault) 4. VIN_OVLO_SDWN = 1 && VIN_OVLO detected for longer than VIN_OVLO_DBNC time                                                                                                                                                                  |

|              |                                        | External turn off event (no PMIC fault)  5. OTP_XFAILB_EN = 1  && XFAILB → Low && 20 µs synchronization time is expired                                                                                                                                                                 |

|              |                                        | Turn off event due to PMIC fault  1. Fault Timer expired                                                                                                                                                                                                                                |

| Transition Z | System on to power down (fault)        | Turn off event due to PMIC fault 2. FAULT_CNT = FAULT_MAX_CNT                                                                                                                                                                                                                           |

|              |                                        | Turn off event due to PMIC fault<br>3. Thermal shutdown $T_J > T_{SD}$                                                                                                                                                                                                                  |

| Transition O | Power down (turn off) to LP_Off        | Requested turn off event moves directly to LP_Off  1. Power down sequences finished                                                                                                                                                                                                     |

| Transition Q | Power up to power down (fault)         | Power up failure  1. Failure during power up sequence                                                                                                                                                                                                                                   |

| Transition S | Power down (fault) to fault transition | Turn off event due to a fault condition moves to fault transition  1. Power down sequence is finished                                                                                                                                                                                   |

| Transition U | Fault transition to LP_Off             | Transitory fault transition  Moves automatically to LP_Off state after increasing the FS_CNT system fault counter                                                                                                                                                                       |

## 13.1 States description

### 13.1.1 OTP/TRIM load

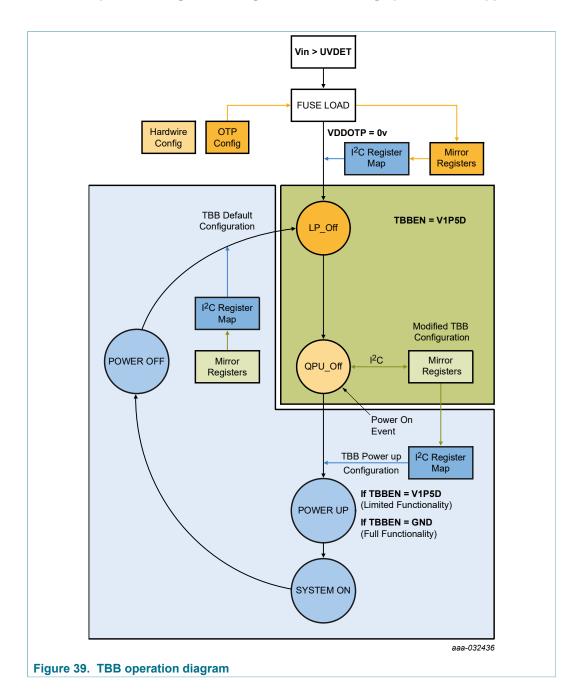

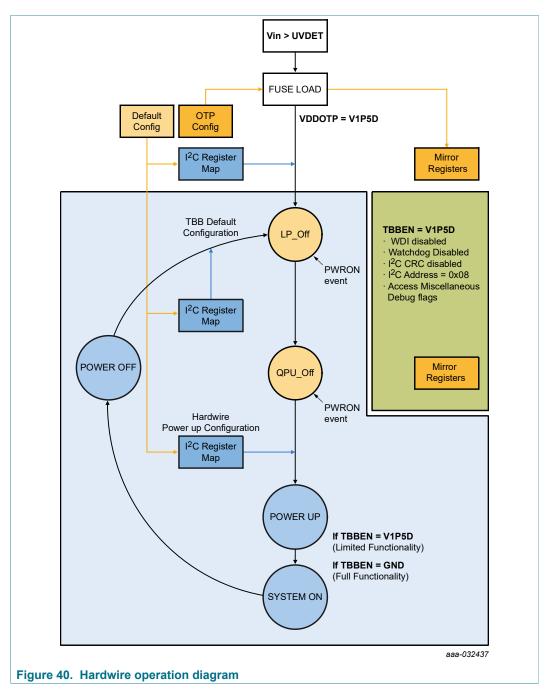

Upon VIN application V1P5D and V1P5A regulators are turned on automatically. Once the V1P5D and V1P5A cross their respective POR thresholds, the fuses (for trim and OTP) are loaded into the mirror registers and into the functional I<sup>2</sup>C registers if configured by the voltage on the VDDOTP pin.

The fuse circuits have a CRC error check routine which reports and protects against register loading errors on the mirror registers. If a register loading error is detected, the

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

corresponding TRIM\_NOK or OTP\_NOK flag is asserted. See <u>Section 17 "OTP/TBB and default configurations"</u> for details on handling fuse load errors.

If no fuse load errors are present, VSNVS is configured as indicated in the OTP configuration bits, and the state machine moves to the LP\_OFF state.

## 13.1.2 LP\_Off state

The LP\_Off state is a low power off mode selectable by the LPM\_OFF bit during the system on modes. By default, the LPM\_OFF = 0 when VIN crosses the UVDET threshold, therefore the state machine stops at the LP\_Off state until a valid power up event is present. When LPM\_OFF= 1, the state machine transitions automatically to the QPU\_Off state if no power up event has been present and waits in the QPU\_Off until a valid power up event is present.

The selection of the LPM\_OFF bit is based on whether prioritizing low quiescent current (stay in LP\_Off) or quick power up (move to QPU\_Off state).

If a power up event is started in LP\_Off state with LPM\_OFF = 0 and a fuse loading error is detected, the PF8121 ignores the power up event and remains in the LP\_Off state to avoid any potential damage to the system.

To be in LP\_Off state, it is necessary to have VIN present. If a valid LICELL is present, but VIN is below the UVDET, the PF8121 enters the coin cell state.

## 13.1.3 QPU\_Off state

The QPU\_Off state is a higher power consumption off mode, in which all internal circuitry required for a power on is biased and ready to start a power up sequence.

If LPM\_OFF = 1 and no turn on event is present, the device stops at the QPU\_Off state, and waits until a valid turn on event is present.

In this state, if VDDIO supply is provided externally, the device is able to communicate through I<sup>2</sup>C to access and modify the mirror registers in order to operate the device in TBB mode or to program the OTP registers as described in <u>Section 17 "OTP/TBB and default configurations"</u>.

By default, the coin cell charger is disabled during the QPU\_Off state when VIN crosses the UVDET threshold, but it may be turned on or off in this state once it is programmed by COINCHG OFF during the system-on states.

If a power up event is started and any of the TRIM\_NOK or OTP\_NOK flags are asserted, the device ignores the power up event and remains in the QPU\_Off state. See Section 17 "OTP/TBB and default configurations" for more details on debugging a fuse loading failure.

Upon a power up event, the default configuration from OTP or hardwire is loaded into their corresponding I<sup>2</sup>C functional register in the transition from QPU\_Off to power up state.

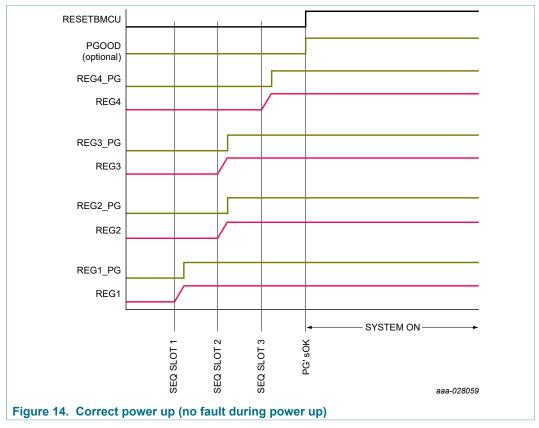

### 13.1.4 Power up sequence

During the power up sequence, the external regulators are turned on in a predefined order as programmed by the default (OTP or hardwire) sequence.

If PGOOD is used as a GPO, it can also be set high as part of the power up sequence in order to allow sequencing of any external supply/device controlled by the PGOOD pin.

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

The RESETBMCU is also programmed as part of the power up sequence, and it is used as the condition to enter system-on states. The RESETBMCU may be released in the middle of the power up sequence, in this case, the remaining supplies in the power up continues to power up as the device is in the run state. See <u>Section 14.5.2 "Power up sequencing"</u> for details.

## 13.1.5 System-on states

During the system-on states, the MCU is powered and out of reset and the system is fully operational.

The system on is a virtual state composed by two modes of operations:

- · Run state

- · Standby state

Register to control the regulators output voltage, regulator enable, interrupt masks, and other miscellaneous functions can be written to or read from the functional I<sup>2</sup>C register map during the system-on states.

#### 13.1.5.1 Run state

If the power up state is successfully completed, the state machine transitions to the run state. In this state, RESETBMCU is released high, and the MCU is expected to boot up and set up specific registers on the PMIC as required during the system boot up process.

The run mode is intended to be used as the normal mode of operation for the system.

Each regulator has specific registers to control its output voltage, operation mode and/or enable/disable state during the run state.

By default, the VSWx\_RUN[7:0] / VLDOx\_RUN[3:0] registers are loaded with the data stored in the OTP\_VSWx[7:0] or OTP\_VLDOx[3:0] bits respectively.

SW7 uses only one global register to configure the output voltage during run or standby mode. Upon power up the VSW7[4:0] bits are loaded with the values of the OTP VSW7[4:0].

Upon power up, if the switching regulator is part of the power up sequence, the SWx RUN MODE[1:0] bits will be loaded as needed by the system:

- When OTP\_SYNCIN\_EN = 1, default SWx\_RUN\_MODE at power up is always set to PWM (0b01)

- When OTP\_SYNCOUT\_EN = 1, default SWx\_RUN\_MODE at power up is always set to PWM (0b01)

- When OTP\_FSS\_EN = 1, default SWx\_RUN\_MODE at power up shall always set to PWM (0b01)

- If none of the above conditions are met, the default value of the SWx\_RUN\_MODE bits at power up will be set by the OTP\_SW\_MODE bits.

When OTP\_SW\_MODE = 0, the default value of the SWx\_RUN\_MODE bits are set to 0b11 (autoskip).

When OTP\_SW\_MODE = 1, the default value of the SWx\_RUN\_MODE bits are set to 0b01 (PWM).

If the switching regulator is not part of the power up sequence, the SWx\_RUN\_MODE[1:0] bits are loaded with 0b00 (OFF mode).

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

Likewise, if the LDO is part of the power up sequence, the LDOx\_RUN\_EN bit is set to 1 (enabled) by default. If the LDO is not selected as part of the power up sequence, the LDOx\_RUN\_EN bit is set to 0 (disabled) by default.

In a typical system, each time the processor boots up (PMIC transitions from off mode to run state), all output voltage configurations are reset to the default OTP configuration, and the MCU should configure the PMIC to its desired usage in the application.

#### 13.1.5.2 Standby state

The standby state is intended to be used as a low power (state retention) mode of operation. In this state, the voltage regulators can be preset to a specific low power configuration in order to reduce the power consumption during system's sleep or state retention modes of operations.

The standby state is entered when the STANDBY pin is pulled high or low as defined by the STANBYINV bit. The STANDBY pin is pulled high/low by the MCU to enter/exit system low power mode. See <a href="Section 14.9.2"STANDBY">Section 14.9.2 "STANDBY"</a> for detailed configuration of the STANDBY pin.

Each regulator has specific registers to control its output voltage, operation mode and/or enable/disable state during the standby state.

By default, the VSWx\_STBY[7:0] / VLDOx\_STBY[3:0] registers are loaded with the data stored in the OTP\_VSWx[7:0] or OTP\_VLDOx[3:0] bits respectively.

Upon power up, if the switching regulator is part of the power up sequence, the SWx\_STBY\_MODE[1:0] bits will be loaded as needed by the system:

- When OTP\_SYNCIN\_EN = 1, default SWx\_STBY\_MODE at power up is always set to PWM (0b01)

- When OTP\_SYNCOUT\_EN = 1, default SWx\_STBY\_MODE at power up is always set to PWM (0b01)

- When OTP\_FSS\_EN = 1, default SWx\_STBY\_MODE at power up shall always set to PWM (0b01)

- If none of the conditions above are met, the default value of the SWx\_STBY\_MODE bits at power up will be set by the OTP\_SW\_MODE bits.

When OTP\_SW\_MODE = 0, the default value of the SWx\_STBY\_MODE bits are set to 0b11 (autoskip).

When OTP\_SW\_MODE = 1, the default value of the SWx\_STBY\_MODE bits are set to 0b01 (PWM).

If the switching regulator is not part of the power up sequence, the SWx STBY MODE[1:0] bits are loaded with 0b00 (OFF mode).

Likewise, if the LDO is part of the power up sequence, the LDOx\_RUN\_EN bit is set to 1 (enabled) by default. If the LDO is not selected as part of the power up sequence, the LDOx\_RUN\_EN bit is set to 0 (disabled) by default.

Upon power up, the standby registers are loaded with the same default OTP values as the run mode. The MCU is expected to program the desired standby values during boot up.

If any of the external regulators are disabled in the standby state, the power down sequencer is engaged as described in <u>Section 14.6.2 "Power down sequencing"</u>.

PF8121

All information provided in this document is subject to legal disclaimers.

### 12-channel power management integrated circuit for high performance applications

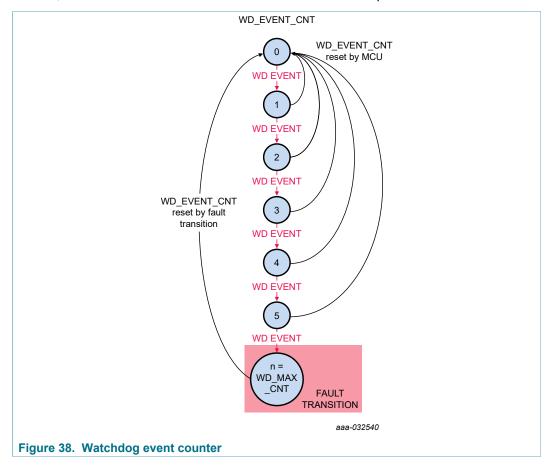

## 13.1.6 WD\_Reset

When a hard watchdog reset is present, the state machine increments the WD\_EVENT\_CNT[3:0] register and compares against the WD\_MAX\_CNT[3:0] register. If WD\_EVENT\_CNT[3:0] = WD\_MAX\_CNT[3:0], the state machine detects a cyclic watchdog failure, it powers down the external regulators and proceeds to the fault transition.

If WD\_EVENT\_CNT[3:0] < WD\_MAX\_CNT[3:0], the state machine performs a hard WD reset.

A hard WD reset can be generated from either a transition in the WDI pin or a WD event initiated by the internal watchdog counter as described in <a href="Section 15.11.2">Section 15.11.2</a> "Watchdog reset behaviors".

### 13.1.7 Power down state

During power down state, all regulators except VSNVS are disabled as configured in the power down sequence. The power down sequence is programmable as defined in Section 14.6.2 "Power down sequencing".

Two types of events may lead to the power down sequence:

- Non faulty turn off events: move directly into LP\_Off state as soon as power down sequence is finalized

- Turn off events due to a PMIC fault: move to the fault transition as soon as the power down sequence is finalized

#### 13.1.8 Fault transition

The fault transition is entered if the PF8121 initiates a turn off event due to a PMIC fault.

If the fault transition is entered, the PF8121 provides four FAIL bits to indicate the source of the failure:

- The PU FAIL is set to 1 when the device shuts down due to a power up failure

- The WD\_FAIL is set to 1 when the device shuts down due to a watchdog event counter max out

- The REG\_FAIL is set to 1 when the device shuts down due to a regulator failure (fault counter maxed out or fault timer expired)

- The TSD FAIL is set to 1 when the device shuts down due to a thermal shutdown

The value of the FAIL bits is retained as long as VIN > UVDET.

The MCU can read the FAIL bits during the system-on states in order to obtain information about the previous failure and can clear them by writing a 1 to them, provided the state machine is able to power up successfully after such failure.

#### 13.1.9 Coin cell state

When VIN is not present and LICELL pin has a valid voltage, the device is placed into a coin cell state. In such state, only VSNVS remains on (if programmed to do so by the OTP\_VSNVSVOTL[1:0] bits) and is expected to provide power to the SNVS domain on the MCU as long as the LICELL pin has a valid input suitable to supply the configured VSNVS output voltage.

PF8121

All information provided in this document is subject to legal disclaimers.

12-channel power management integrated circuit for high performance applications

# 14 General device operation

## **14.1 UVDET**

UVDET works as the main operation threshold for the PF8121. Crossing UVDET on the rising edge is a mandatory condition for OTP fuses to be loaded into the mirror registers and allows the main PF8121 operation.

If VIN is below the UVDET threshold, the device remains in an unpowered state if no valid LICELL is present, or in the LICELL mode if a valid LICELL voltage is present. A 200 mV hysteresis is implemented on the UVDET comparator to set the falling threshold.

Table 11. UVDET threshold

| Symbol | Parameter     | Min | Тур | Max | Unit |

|--------|---------------|-----|-----|-----|------|

| UVDET  | Rising UVDET  | 2.7 | 2.8 | 2.9 | V    |

| UVDET  | Falling UVDET | 2.5 | 2.6 | 2.7 | V    |

### 14.2 VIN OVLO condition

The VIN\_OVLO circuit monitors the main input supply of the PF8121. When this block is enabled, the PF8121 monitors its input voltage and can be programmed to react to an overvoltage in two ways:

- When the VIN\_OVLO\_SDWN = 0, the VIN\_OVLO event triggers an OVLO interrupt but does not turn off the device

- When the VIN\_OVLO\_SDWN = 1, the VIN\_OVLO event initiates a power down sequence

When the VIN\_OVLO\_EN = 0, the OVLO monitor is disabled and when the VIN\_OVLO\_EN = 1, the OVLO monitor is enabled. The default configuration of the VIN\_OVLO\_EN bit is set by the OTP\_VIN\_OVLO\_EN bit in OTP. Likewise, the default value of the VIN\_OVLO\_SDWN bit is set by the OTP\_VIN\_OVLO\_SDWN upon power up.

During a power up transition, if the OTP\_VIN\_OVLO\_SDWN = 0 the device allows the external regulators to come up and the PF8121 announces the VIN\_OVLO condition through an interrupt. If the OTP\_VIN\_OVLO\_SDWN = 1, the device stops the power up sequence and returns to the corresponding off mode.

Debounce on the VIN\_OVLO comparator is programmable to 10  $\mu$ s, 100  $\mu$ s or 1.0 ms, by the VIN\_OVLO\_DBNC[1:0] bits. The default value for the VIN\_OVLO debounce is set by the OTP\_VIN\_OVLO\_DBNC[1:0] bits upon power up.

Table 12. VIN\_OVLO debounce configuration

| VIN_OVLO_DBNC[1:0] | VIN OVLO debounce value (µs) |

|--------------------|------------------------------|

| 00                 | 10                           |

| 01                 | 100                          |

| 10                 | 1000                         |

| 11                 | Reserved                     |

PF8121

### 12-channel power management integrated circuit for high performance applications

Table 13. VIN\_OVLO specifications

| Symbol       | Parameter                          |     | Min  | Тур | Max | Unit |

|--------------|------------------------------------|-----|------|-----|-----|------|

| VIN_OVLO     | VIN overvoltage lockout rising     | [1] | 5.55 | 5.8 | 6.0 | V    |

| VIN_OVLO_HYS | VIN overvoltage lockout hysteresis | [1] | _    | _   | 200 | mV   |

<sup>[1]</sup> Operating the device above the maximum VIN = 5.5 V for extended periods of time may degrade and cause permanent damage to the device.

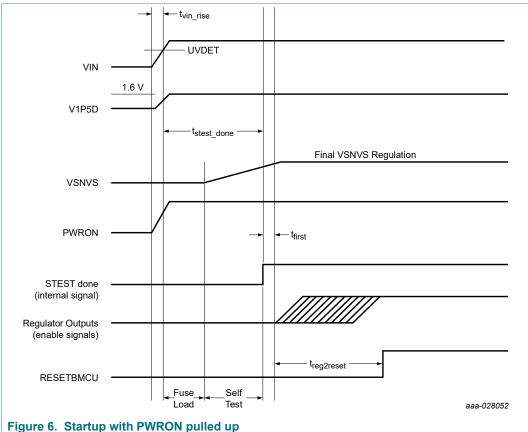

## 14.3 IC startup timing with PWRON pulled up

The PF8121 features a fast internal core power up sequence to fulfill system power up timings of 5.0 ms or less, from power application until MCU is out of reset. Such requirement needs a maximum ramp up time of 1.5 ms for VIN to cross the UVDET threshold in the rising edge.

A maximum core biasing time of 1.5 ms from VIN crossing to UVDET until the beginning of the power up sequence is ensured to allow up to 1.5 ms time frame for the voltage regulators power up sequence.

Timing for the external regulators to start up is programmed by default in the OTP fuses.

The 5.0 ms power up timing requirement is only applicable when the PWRON pin operates in level sensitive mode OTP\_PWRON\_MODE = 0, however turn on timing is expected to be the same for both level or edge sensitive modes after the power on event is present.

In applications using the VSNVS regulator, if VSNVS is required to reach regulation before system regulators come up, the system should use the SEQ[7:0] bits to delay the system regulators to allow enough time for VSNVS to reach regulation before the power up sequence is started.

### 12-channel power management integrated circuit for high performance applications

Table 14. Startup timing requirements (PWRON pulled up)

| Symbol                  | Parameter                                                                                     | Min | Тур | Max  | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>vin_rise</sub>   | Rise time of VIN from VPWR application to UVDET (system dependent)                            | 10  | _   | 1500 | μs   |

| t <sub>stest_done</sub> | Time from VIN crossing UVDET to STEST_<br>done going high (self-test performed and<br>passed) | _   | _   | 1.4  | ms   |

| t <sub>first</sub>      | Time from STEST_done to first slot of power up sequence                                       | _   | _   | 100  | μs   |

| t <sub>reg2reset</sub>  | Time from first regulator enabled to RESETBMCU asserted to guarantee 5.0 ms PMIC boot up      | [1] | _   | 1.5  | ms   |

External regulators power up sequence time (t<sub>rea2reset</sub>) is programmed by OTP and may be longer than 1.5 ms. However, 1.5 ms is the maximum allowed time to ensure power up within 5.0 ms.

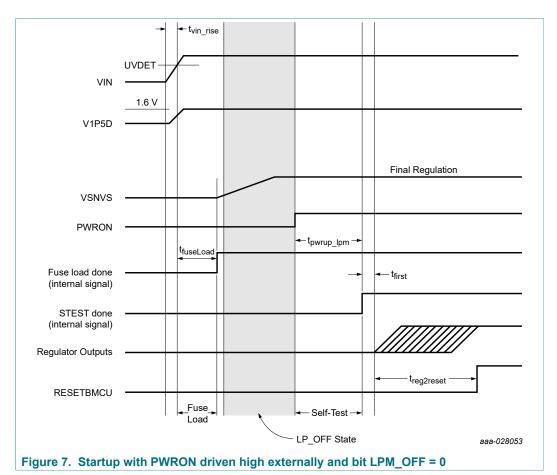

# 14.4 IC startup timing with PWRON pulled low during VIN application

It is possible that PWRON is held low when VIN is applied. By default, LPM OFF bit is reset to 0 upon crossing UVDET, therefore the PF8121 remains in the LP\_Off state as described in Section 13.1.2 "LP Off state". In this scenario, quiescent current in the LP\_Off state is kept to a minimum. When PWRON goes high with LPM\_OFF = 0, the PMIC startup is expected to take longer, since it has to enable most of the internal circuits and perform the self-test before starting a power up sequence.

Figure 7 shows startup timing with LPM\_OFF = 0.

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

Table 15. Startup with PWRON driven high externally and LPM OFF = 0

| Symbol                 | Parameter                                                                                | Min | Тур | Max  | Unit |

|------------------------|------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>vin_rise</sub>  | Rise time of VIN from VPWR application to UVDET (system dependent)                       | 10  | _   | 1500 | μs   |

| t <sub>fuseload</sub>  | Time from VIN crossing UVDET to Fuse_Load_ done (fuse loaded correctly)                  | _   | _   | 600  | μs   |

| t <sub>pwrup_lpm</sub> | Time from PWRON going high to the STEST_<br>done (self-test performed and passed)        | _   | _   | 700  | μs   |

| t <sub>first</sub>     | Time from STEST_done to first slot of power up sequence                                  | _   | _   | 100  | μs   |

| t <sub>reg2reset</sub> | Time from first regulator enabled to RESETBMCU asserted to guarantee 5.0 ms PMIC boot up | [1] | -   | 1.5  | ms   |

<sup>[1]</sup> External regulators power up sequence time ( $t_{reg2reset}$ ) is programmed by OTP and may be longer than 1.5 ms.

## 14.5 Power up

## 14.5.1 Power up events

Upon a power cycle (VIN > UVDET), the LPM\_OFF bit is reset to 0, therefore the device moves to the LP\_Off state by default. The actual value of the LPM\_OFF bit can be changed during the run mode and is maintained until VIN crosses the UVDET threshold.

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

In either one of the off modes, the PF8121 can be enabled by the following power up events:

- 1. When OTP\_PWRON\_MODE = 0, PWRON pin is pulled high.

- 2. When OTP\_PWRON\_MODE = 1, PWRON pin experiences a high to low transition and remains low for as long as the PWRON\_DBNC timer.

A power up event is valid only if:

- VIN > UVDET

- VIN < VIN\_OVLO (unless the OVLO is disabled or OTP\_VIN\_OVLO\_SDWN = 0)</li>

- Tj < thermal shutdown threshold

- TRIM\_NOK = 0 && OTP\_NOK = 0

### 14.5.2 Power up sequencing

The power up sequencer controls the time and order in which the voltage regulators and other controlling I/O are enabled when going from the off mode into the run state.

The OTP\_SEQ\_TBASE[1:0] bits set the default time base for the power up and power down sequencer.

The SEQ\_TBASE[1:0] bits can be modified during the system-on states in order to change the sequencer timing during run/standby transitions as well as the power down sequence.

Table 16. Power up time base register

| OTP bits OTP_SEQ_TBASE[1:0] | Functional bits<br>SEQ_TBASE[1:0] | Sequencer time base (µs) |

|-----------------------------|-----------------------------------|--------------------------|

| 00                          | 00                                | 30                       |

| 01                          | 01                                | 120                      |

| 10                          | 10                                | 250                      |

| 11                          | 11                                | 500                      |

The power up sequence may include any of the following:

- Switching regulators

- LDO Regulators

- PGOOD pin if programmed as a GPO

- RESETBMCU

The default sequence slot for each one of these signals is programmed via the OTP configuration registers. And they can be modified in the functional I<sup>2</sup>C register map to change the order in which the sequencer behaves during the run/standby transitions as well as the power down sequence.

The \_SEQ[7:0] bits set the regulator/pin sequence from 0 to 254. Sequence code 0x00 indicates that the particular output is not part of the startup sequence and remains in off (in case of a regulator) or remains low/disabled (in case of PGOOD pin used as a GPO).

### 12-channel power management integrated circuit for high performance applications

Table 17. Power up sequence registers

|                                                                                          |                                                                                 |               | i e e e e e e e e e e e e e e e e e e e        |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------|------------------------------------------------|

| OTP bits OTP_SWx_SEQ[7:0]/ OTP_LDOx_SEQ[7:0]/ OTP_PGOOD_SEQ[7:0]/ OTP_RESETBMCU_SEQ[7:0] | Functional bits SWx_SEQ[7:0]/ LDOx_SEQ[7:0]/ PGOOD_SEQ[7:0]/ RESETBMCU_SEQ[7:0] | Sequence slot | Startup time (µs)                              |

| 0000000                                                                                  | 00000000                                                                        | Off           | Off                                            |

| 0000001                                                                                  | 00000001                                                                        | 0             | SLOT0<br>(right after PWRON event is<br>valid) |

| 0000010                                                                                  | 0000010                                                                         | 1             | SEQ_TBASE x SLOT1                              |

|                                                                                          |                                                                                 |               |                                                |

|                                                                                          |                                                                                 |               |                                                |

|                                                                                          |                                                                                 |               | 050 70405 0107054                              |

| 11111111                                                                                 | 11111111                                                                        | 254           | SEQ_TBASE x SLOT254                            |

If RESETBMCU is not programmed in the OTP sequence, it will be enabled by default after the last regulator programmed in the power up sequence.

When the \_SEQ[7:0] bits of all regulators and PGOOD used as a GPIO are set to 0x00 (off) and a power on event is present, the device moves to the run state in slave mode. In this mode, the device is enabled without any voltage regulator or GPO enabled. If the RESETBMCU is not programed in a power up sequence slot, it is released when the device enters the run state.

The slave mode is a special case of the power up sequence to address the scenario where the PF8121 is working as a slave PMIC, and supplies are meant to be enabled by the MCU during the system operation. In this scenario, if RESETBMCU is used, it is connected to the master RESETBMCU pin.

The PWRUP\_I interrupt bit is asserted at the end of the power up sequence when the time slot of the last regulator in the sequence has ended.

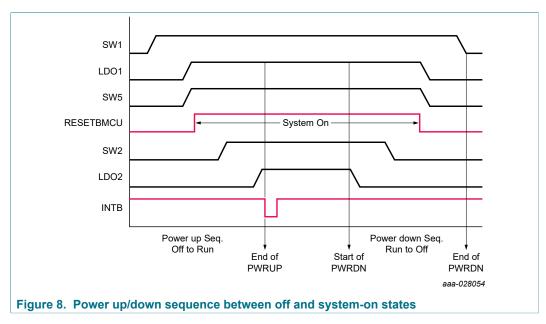

<u>Figure 8</u> provides an example of the power up/down sequence coming from the off modes.

PF812

All information provided in this document is subject to legal disclaimers

## 12-channel power management integrated circuit for high performance applications

When transitioning from standby mode to run mode, the power up sequencer is activated only if any of the external regulators is re-enabled during this transition. If none of the regulators toggle from off to on and only voltage changes are being performed when entering or exiting standby mode, the changes for the voltage regulators are made simultaneously rather than going through the power up sequencer.

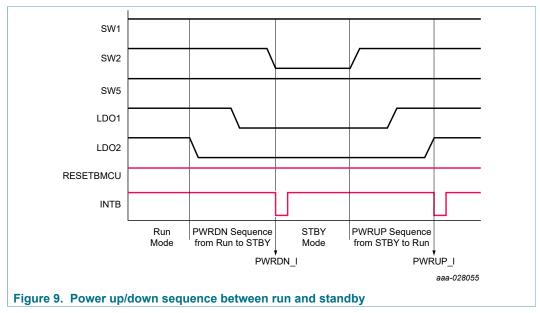

<u>Figure 9</u> shows an example of the power up/down sequence when transitioning between run and standby modes.

The PWRUP\_I interrupt is set while transitioning from standby to run, even if the sequencer is not used. This is used to indicate that the transition is complete and device is ready to perform proper operation.

### 14.6 Power down

#### 14.6.1 Turn off events

Turn off events may be requested by the MCU (non-PMIC fault related) or due to a critical failure of the PMIC (hard fault condition).

The following are considered non-PMIC failure turn off events:

- 1. When OTP\_PWRON\_MODE = 0, the device starts a power down sequence when the PWRON pin is pulled low.

- 2. When OTP\_PWRON\_MODE = 1, the device starts a power down sequence when the PWRON pin sees a transition from high to low and remains low for longer than TRESET.

- 3. When bit PMIC\_OFF is set to 1, the device starts a 500 µs shutdown timer. When the shutdown timer is started, the PF8121 sets the SDWN\_I interrupt and asserts the INTB pin provided it is not masked. At this point, the MCU can read the interrupt and decide whether to continue with the turn off event or stop it in case it was sent by mistake.

If the SDWN\_I bit is cleared before the 500 µs shutdown timer is expired, the shutdown request is cancelled and the shutdown timer is reset; otherwise, if the shutdown timer is expired, the PF8121 starts a power down sequence.

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

The PMIC\_OFF bit self-clears after SDWN\_I flag is cleared.

4. When VIN\_OVLO\_EN = 1 and VIN\_OVLO\_SDWN = 1, and a VIN\_OVLO event is present.

Turn off events due to a hard fault condition:

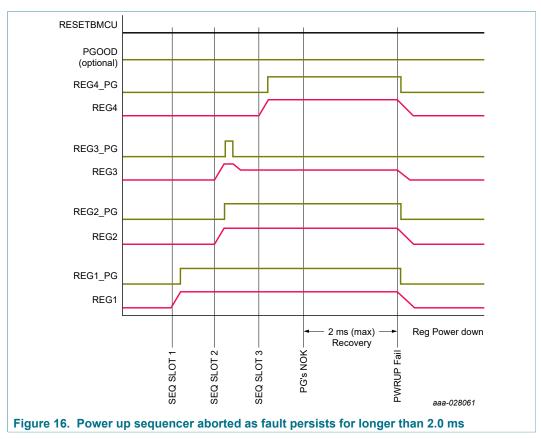

- 1. If an OV, UV or ILIM condition is present long enough for the fault timer to expire.

- 2. In the event that an OV, UV or ILIM condition appears and clears cyclically, and the FAULT\_CNT[3:0] = FAULT\_MAX\_CNT[3:0].

- 3. If the watchdog fail counter is overflown, that is WD\_EVENT\_CNT = WD\_MAX\_CNT.

- 4. When Tj crosses the thermal shutdown threshold as the temperature rises.

When the PF8121 experiences a turn off event due to a hard fault condition, the device passes through the fault transition after regulators have been powered down.

## 14.6.2 Power down sequencing

During a power down sequence, output voltage regulators can be turned off in two different modes as defined by the PWRDWN MODE bit.

- 1. When PWRDWN MODE = 0, the regulators power down in sequential mode.

- 2. When PWRDWN MODE = 1, the regulators power down by groups.

During transition from run to standby, the power down sequencer is activated in the corresponding mode. If any of the external regulators are turned off in the standby configuration. If external regulators are not turned off during this transition, the power down sequencer is bypassed and the transition happens at once (any associated DVS transitions could still take time).

The PWRDN\_I interrupt is set at the end of the transition from run to standby when the last regulator has reached its final state, even if external regulators are not turned off during this transition.

## 14.6.2.1 Sequential power down

When the device is set to the sequential power down, it uses the same \_SEQ[7:0] registers as the power up sequence to power down in reverse order.

All regulators with the \_SEQ[7:0] bits set to 0x00, power down immediately and the remaining regulators power down one OTP\_SEQ\_TBASE[1:0] delay after, in reverse order as defined in the \_SEQ[7:0] bits.

If PGOOD pin is used as a GPO, it is de-asserted as part of the power down sequence as indicated by the PGOOD\_SEQ[7:0] bits.

If the MCU requires a different power down sequence, it can change the values of the SEQ\_TBASE[1:0] and the \_SEQ[7:0] bits during the system-on states.

When the state machine pass through any of the off modes, the contents of the SEQ\_TBASE[1:0] and \_SEQ[7:0] bits are reloaded with the corresponding mirror register (OTP) values before it starts the next power up sequence.

#### 14.6.2.2 Group power down

When the device is configured to power down in groups, the regulators are assigned to a specific power down group. All regulators assigned to the same group are disabled at the same time when the corresponding group is due to be disabled.

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

Power down groups shut down in decreasing order starting from the lowest hierarchy group with a regulator shutting down (for instance, Group 4 being the lowest hierarchy and Group 1 the highest hierarchy group). If no regulators are set to the lowest hierarchy group, the power down sequence timer starts off the next available group that contains a regulator to power down.

Each regulator has its own \_PDGRP[1:0] bits to set the power down group it belongs to as shown in Table 18.

Table 18. Power down regulator group bits

| OTP_SWx_PDGRP[1:0] OTP_LDOX_PDGRP[1:0] OTP_PGOOD_PDGRP[1:0] OTP_RESETBMCU_PDGRP[1:0] | SWx_PDGRP[1:0]<br>LDOx_PDGRP[1:0]<br>PGOOD_PDGRP[1:0]<br>RESETBMCU_PDGRP[1:0] | Description                  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------|

| 00                                                                                   | 00                                                                            | Regulator belongs to Group 4 |

| 01                                                                                   | 01                                                                            | Regulator belongs to Group 3 |

| 10                                                                                   | 10                                                                            | Regulator belongs to Group 2 |

| 11                                                                                   | 11                                                                            | Regulator belongs to Group 1 |

If PGOOD pin is used as a GPO, the PGOOD\_PDGRP[1:0] is used to turn off the PGOOD pin in a specific group during the power down sequence. If PGOOD pin is used in power good mode, it is recommended that the OTP\_PGOOD\_PDGRP bits are set to 11 to ensure the group power down sequencer does not detect these bits as part of Group 4.

Each one of power down groups have programmable time delay registers to set the time delay after the regulators in this group have been turned off, and the next group can start to power down.

Table 19. Power down counter delay

| OTP bits OTP_GRPx_DLY[1:0] | Functional bits<br>GRPx_DLY[1:0] | Power down delay (µs) |

|----------------------------|----------------------------------|-----------------------|

| 00                         | 00                               | 120                   |

| 01                         | 01                               | 250                   |

| 10                         | 10                               | 500                   |

| 11                         | 11                               | 1000                  |

If RESETBMCU is required to be asserted first before any of the external regulators from the corresponding group, the RESETBMCU\_DLY provides a selectable delay to disable the regulators after RESETBMCU is asserted.

Table 20. Programmable delay after RESETBMCU is asserted

| OTP bits OTP_RESETBMCU_DLY[1:0] | Functional bits RESETBMCU_DLY[1:0] | RESETBMCU delay (µs) |

|---------------------------------|------------------------------------|----------------------|

| 00                              | 00                                 | No delay             |

| 01                              | 01                                 | 10                   |

| 10                              | 10                                 | 100                  |

| 11                              | 11                                 | 500                  |

If RESETBMCU\_DLY is set to 0x00, all regulators in the same power down group as RESETBMCU is disabled at the same time RESETBMCU is asserted.

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

PDWN\_GRP1 PDWN\_GRP2 PDWN\_GRP3 PDWN\_GRP4 GPR1\_DLY = 120 μs GPR2\_DLY = 120 μs GPR3\_DLY = 120 μs SW2 LDO2 SW1 NA LDO1 SW3 LDO3 RESETBMCU\_DLY = 10 µS SW4 I DO4 **PWRON** LDO2 LDO3 LDO4 SW2 SW3 SW4 RESETBMCU SW1 LDO1 120 µs GRP1\_DLY 120 μs GRP3\_DLY 120 μs GRP2\_DLY 10 µs RESETBMCU asserted End of Power Down GRP1 SDWN SUPPLIES **GRP2 SDWN** PWRDN EVENT aaa-028056

Figure 10 shows an example of the power down sequence when PWRDWN MODE = 1.

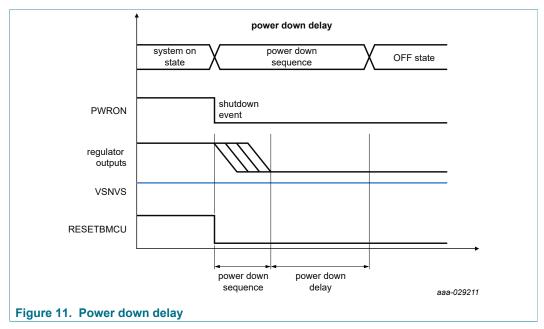

## 14.6.2.3 Power down delay

After a power down sequence is started, the PWRON pin shall be masked until the sequence is finished and the programmable power down delay is reached, then the device can power up again if a power-up event is present. The power down delay time can be programed on OTP via the OTP\_PD\_SEQ\_DLY[1:0] bits.

Table 21. Power down delay selection

Figure 10. Group power down sequence example

| OTP_PD_SEQ_DLY[1:0] | Delay after power down sequence |

|---------------------|---------------------------------|

| 00                  | No delay                        |

| 01                  | 1.5 ms                          |

| 10                  | 5.0 ms                          |

| 11                  | 10 ms                           |

### 12-channel power management integrated circuit for high performance applications

The default value of the OTP\_PD\_SEQ\_DLY[1:0] bits on an unprogrammed OTP device shall be 00.

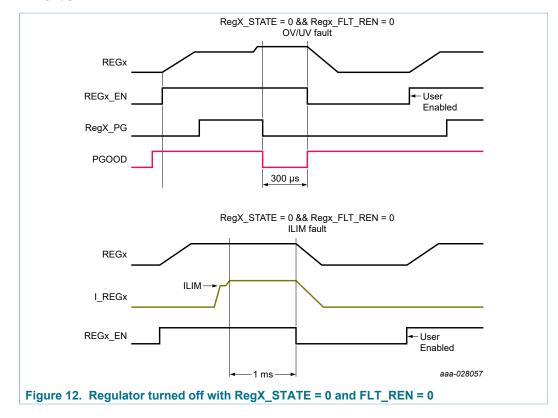

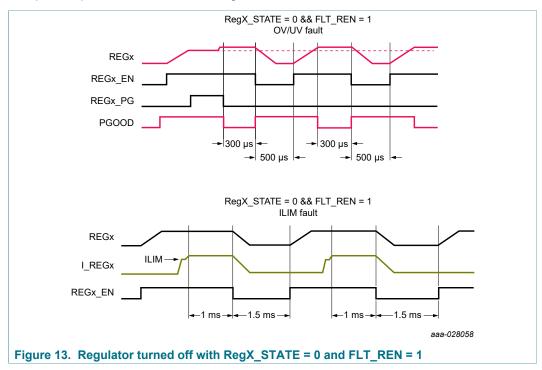

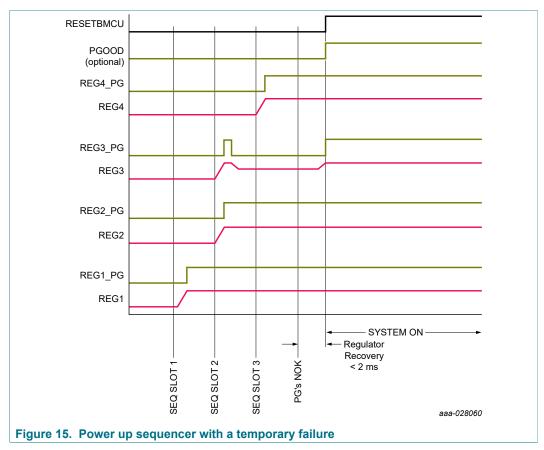

#### 14.7 Fault detection

Three types of faults are monitored per regulator: UV, OV and ILIM. Faults are monitored during power up sequence, run, standby and WD reset states. A fault event is notified to the MCU through the INTB pin if the corresponding fault is not masked.

The fault configuration registers are reset to their default value after the power up sequences, and system must configure them as required during the boot-up process via  $I^2C$  commands.

For each type of fault, there is an I<sup>2</sup>C bit that is used to select whether the regulator is kept enabled or disabled when the corresponding regulator experience a fault event.

SWx\_ILIM\_STATE / LDOx\_ILIM\_STATE

- 0 = regulator disable upon an ILIM fault event

- 1 = regulator remains on upon an ILIM fault event

SWx OV STATE/LDOx OV STATE

- 0 = regulator disable upon an OV fault event

- 1 = regulator remains on upon an OV fault event

SWx\_UV\_STATE / LDOx\_UV\_STATE

- 0 = regulator disable upon an UV fault event

- 1 = regulator remains on upon an UV fault event

The following table lists the functional bits associated with enabling/disabling the external regulators when they experience a fault.

PF8121

All information provided in this document is subject to legal disclaimers.

## 12-channel power management integrated circuit for high performance applications

Table 22. Regulator control during fault event bits

| Regulator | Bit to disable the regulator during current limit | Bit to disable the regulator during undervoltage | Bit to disable the regulator during overvoltage |

|-----------|---------------------------------------------------|--------------------------------------------------|-------------------------------------------------|

| SW1       | SW1_ILIM_STATE                                    | SW1_UV_STATE                                     | SW1_OV_STATE                                    |

| SW2       | SW2_ILIM_STATE                                    | SW2_UV_STATE                                     | SW2_OV_STATE                                    |

| SW3       | SW3_ILIM_STATE                                    | SW3_UV_STATE                                     | SW3_OV_STATE                                    |

| SW4       | SW4_ILIM_STATE                                    | SW4_UV_STATE                                     | SW4_OV_STATE                                    |

| SW5       | SW5_ILIM_STATE                                    | SW5_UV_STATE                                     | SW5_OV_STATE                                    |

| SW6       | SW6_ILIM_STATE                                    | SW6_UV_STATE                                     | SW6_OV_STATE                                    |

| SW7       | SW7_ILIM_STATE                                    | SW7_UV_STATE                                     | SW7_OV_STATE                                    |

| LDO1      | LDO1_ILIM_STATE                                   | LDO1_UV_STATE                                    | LDO1_OV_STATE                                   |

| LDO2      | LDO2_ILIM_STATE                                   | LDO2_UV_STATE                                    | LDO2_OV_STATE                                   |

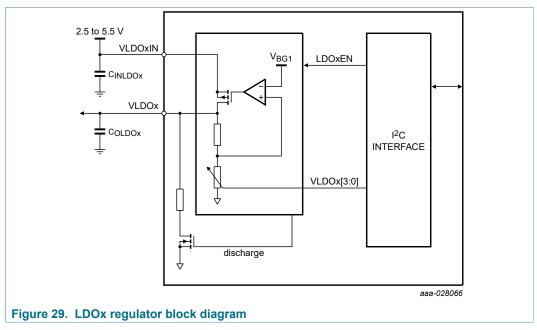

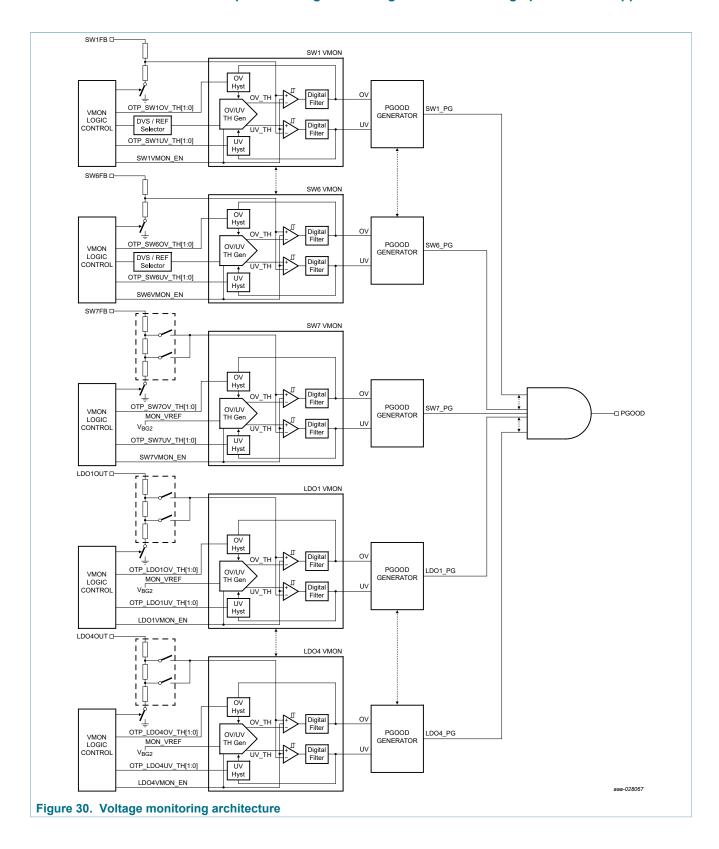

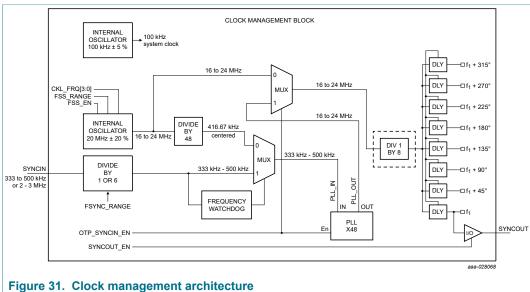

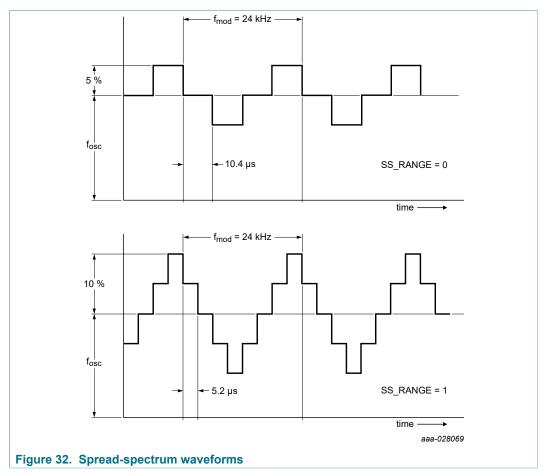

| LDO3      | LDO3_ILIM_STATE                                   | LDO3_UV_STATE                                    | LDO3_OV_STATE                                   |