# **ABSOLUTE MAXIMUM RATINGS**

## (Note 1)

| SW (Note 2) 65                                    | 5V  |

|---------------------------------------------------|-----|

| V <sub>IN</sub>                                   |     |

| EN/UVLOV                                          | 'IN |

| $R_{FB}$ $V_{IN}$ – 0.5V to V                     | 'IN |

| Current into R <sub>FB</sub> 200µ                 | ιÄ  |

| Operating Junction Temperature Range (Notes 3, 4) |     |

| LT3001E, LT3001I40°C to 125°                      | °C  |

| Storage Temperature Range65°C to 150°             | °C  |

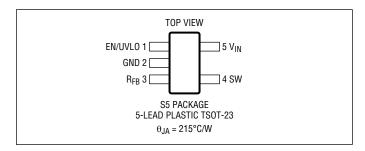

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION    | TEMPERATURE RANGE |

|------------------|-----------------|---------------|------------------------|-------------------|

| LT3001ES5#TRMPBF | LT3001ES5#TRPBF | LTHMF         | 5-Lead Plastic TSOT-23 | -40°C to 125°C    |

| LT3001IS5#TRMPBF | LT3001IS5#TRPBF | LTHMF         | 5-Lead Plastic TSOT-23 | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{IN} = 5V$ , $V_{EN/UVLO} = V_{IN}$ unless otherwise noted.

| SYMBOL                     | PARAMETER                          | CONDITIONS                                   |   | MIN         | TYP            | MAX        | UNIT     |

|----------------------------|------------------------------------|----------------------------------------------|---|-------------|----------------|------------|----------|

| $\overline{V_{\text{IN}}}$ | Input Voltage Range                |                                              |   | 4           |                | 36         | V        |

| IQ                         | V <sub>IN</sub> Quiescent Current  | V <sub>EN/UVLO</sub> = 0.2V<br>Active Mode   |   |             | 0.8<br>350     | 2          | μA<br>μA |

|                            | EN/UVLO Shutdown Threshold         | For Lowest Off IQ                            |   | 0.2         | 0.55           |            | V        |

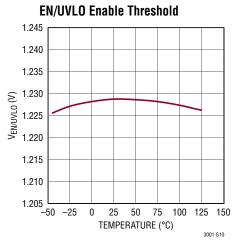

|                            | EN/UVLO Enable Threshold           | Falling<br>Hysteresis                        |   | 1.204       | 1.228<br>0.014 | 1.248      | V        |

| I <sub>HYS</sub>           | EN/UVLO Hysteresis Current         | $V_{EN/UVLO} = 1.1V$<br>$V_{EN/UVLO} = 1.3V$ |   | 2.2<br>-0.1 | 2.5<br>0       | 2.8<br>0.1 | μA<br>μA |

| f <sub>MIN</sub>           | Minimum Switching Frequency        |                                              |   | 9.4         | 10             | 10.6       | kHz      |

| t <sub>ON(MIN)</sub>       | Minimum Switch-On Time             |                                              |   |             | 170            |            | ns       |

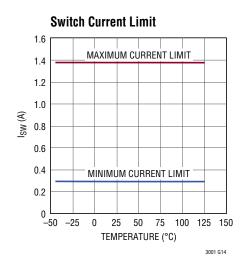

| I <sub>SW(MAX)</sub>       | Maximum SW Current Limit           |                                              |   | 1.200       | 1.375          | 1.550      | A        |

| I <sub>SW(MIN)</sub>       | Minimum SW Current Limit           |                                              |   | 0.22        | 0.29           | 0.36       | A        |

| R <sub>DS(ON)</sub>        | Switch On-Resistance               | I <sub>SW</sub> = 500mA                      |   |             | 0.4            |            | Ω        |

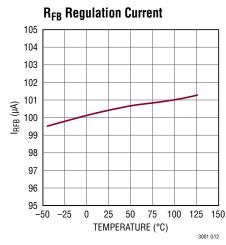

| I <sub>RFB</sub>           | R <sub>FB</sub> Regulation Current |                                              | • | 97.5        | 100            | 102.5      | μA       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The SW pin is rated to 65V for transients. Depending on the leakage inductance voltage spike, operating waveforms of the SW pin should be derated to keep the flyback voltage spike below 65V.

**Note 3:** The LT3001E is guaranteed to meet performance specifications from 0°C to 125°C operating junction temperature. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT3001I is guaranteed over the full –40°C to 125°C operating junction temperature range.

**Note 4:** The LT3001 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

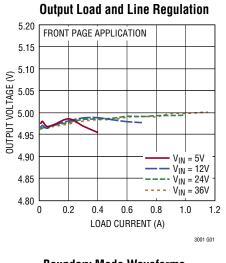

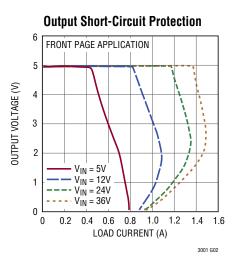

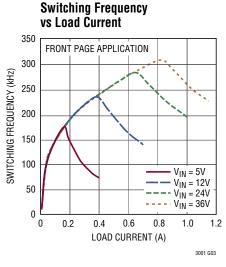

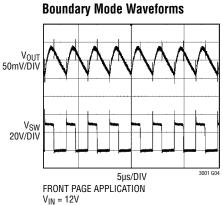

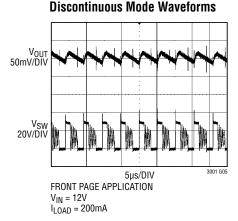

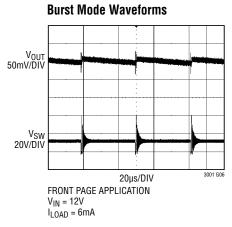

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

$I_{LOAD} = 600 \text{mA}$

Rev. 0

# PIN FUNCTIONS

**EN/UVLO** (**Pin 1**): Enable/Undervoltage Lockout. The EN/UVLO pin is used to enable the LT3001. Pull the pin below 0.2V to shut down the LT3001. This pin has an accurate 1.228V threshold and can be used to program a  $V_{IN}$  undervoltage lockout (UVLO) threshold using a resistor divider from  $V_{IN}$  to ground. A 2.5 $\mu$ A current hysteresis allows the programming of  $V_{IN}$  UVLO hysteresis. If neither function is used, tie this pin directly to  $V_{IN}$ .

**GND (Pin 2):** Ground. Tie this pin directly to local ground plane.

**R<sub>FB</sub> (Pin 3):** Input Pin for External Feedback Resistor. Connect a resistor from this pin to the transformer primary

SW pin. The ratio of the R<sub>FB</sub> resistor to an internal 10k resistor, times a trimmed 1.0V reference voltage, determines the output voltage (plus the effect of any non-unity transformer turns ratio). Minimize trace area at this pin.

**SW** (Pin 4): Drain of the 65V Internal DMOS Power Switch. Minimize trace area at this pin to reduce EMI and voltage spikes.

$V_{IN}$  (Pin 5): Input Supply. The  $V_{IN}$  pin supplies current to internal circuitry and serves as a reference voltage for the feedback circuitry connected to the  $R_{FB}$  pin. Locally bypass this pin to ground with a capacitor.

# **OPERATION**

The LT3001 is a current mode switching regulator IC designed specially for the isolated flyback topology. The key problem in isolated topologies is how to communicate the output voltage information from the isolated secondary side of the transformer to the primary side for regulation. Historically, opto-isolators or extra transformer windings communicate this information across the isolation boundary. Opto-isolator circuits waste output power, and the extra components increase the cost and physical size of the power supply. Opto-isolators can also cause system issues due to limited dynamic response, nonlinearity, unit-to-unit variation and aging over lifetime. Circuits employing extra transformer windings also exhibit deficiencies, as using an extra winding adds to the transformer's physical size and cost, and dynamic response is often mediocre.

The LT3001 samples the isolated output voltage through the primary-side flyback pulse waveform. In this manner, neither opto-isolator nor extra transformer winding is required for regulation. Since the LT3001 operates in either boundary conduction mode or discontinuous conduction mode, the output voltage is always sampled on the SW pin when the secondary current is zero. This method improves load regulation without the need of external load compensation components.

#### **Output Voltage**

The R<sub>FB</sub> resistor is the only external resistor used to program the output voltage.

The output voltage is set by:

$$V_{OUT} = 100\mu A \bullet \left(\frac{R_{FB}}{N_{PS}}\right) - V_F$$

V<sub>F</sub> = Output diode forward voltage

N<sub>PS</sub> = Transformer effective primary-to-secondary turns ratio

#### **Primary Inductance Requirement**

The LT3001 obtains output voltage information from the reflected output voltage on the SW pin. The conduction of secondary current reflects the output voltage on the primary SW pin. The sample-and-hold error amplifier needs a minimum 450ns to settle and sample the reflected output voltage. In order to ensure proper sampling, the secondary winding needs to conduct current for a minimum of 450ns. The following equation gives the minimum value for primary-side magnetizing inductance:

$$L_{PRI} \ge \frac{t_{OFF(MIN)} \cdot N_{PS} \cdot (V_{OUT} + V_F)}{I_{SW(MIN)}}$$

t<sub>OFF(MIN)</sub> = Minimum switch-off time = 450ns

$I_{SW(MIN)}$  = Minimum switch current limit = 290mA (typ)

In addition to the primary inductance requirement for the minimum switch-off time, the LT3001 has minimum switch-on time that prevents the chip from turning on the power switch shorter than approximately 170ns. This minimum switch-on time is mainly for leading-edge blanking the initial switch turn-on current spike. If the inductor current exceeds the desired current limit during that time, oscillation may occur at the output as the current control loop will lose its ability to regulate. Therefore, the following equation relating to maximum input voltage

must also be followed in selecting primary-side magnetizing inductance:

$$L_{PRI} \ge \frac{t_{ON(MIN)} \cdot V_{IN(MAX)}}{I_{SW(MIN)}}$$

$t_{ON(MIN)}$  = Minimum switch-on time = 170ns

#### **Undervoltage Lockout (UVLO)**

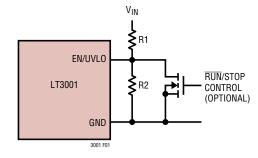

A resistive divider from  $V_{IN}$  to the EN/UVLO pin implements undervoltage lockout (UVLO). The EN/UVLO pin falling threshold is set at 1.228V with 14mV hysteresis. In addition, the EN/UVLO pin sinks 2.5 $\mu$ A when the voltage at the pin is below 1.228V. This current provides user programmable hysteresis based on the value of R1. The programmable UVLO thresholds are:

$$V_{IN(UVLO+)} = \frac{1.242V \cdot (R1+R2)}{R2} + 2.5\mu A \cdot R1$$

$$V_{IN(UVLO-)} = \frac{1.228V \cdot (R1+R2)}{R2}$$

Figure 1 shows the implementation of external shutdown control while still using the UVLO function. The NMOS grounds the EN/UVLO pin when turned on, and puts the LT3001 in shutdown with quiescent current less than  $2\mu$ A.

Figure 1. Undervoltage Lockout (UVLO)

#### **Minimum Load Requirement**

The LT3001 samples the isolated output voltage from the primary-side flyback pulse waveform. The flyback pulse occurs once the primary switch turns off and the secondary winding conducts current. In order to sample the output voltage, the LT3001 has to turn on and off at least for a minimum amount of time and with a minimum frequency. The LT3001 delivers a minimum amount of energy even during light load conditions to ensure accurate output voltage information. The minimum energy delivery creates a minimum load requirement, which can be approximately estimated as:

$$I_{LOAD(MIN)} = \frac{L_{PRI} \bullet I_{SW(MIN)}^{2} \bullet f_{MIN}}{2 \bullet V_{OUT}}$$

L<sub>PRI</sub> = Transformer primary inductance

I<sub>SW(MIN)</sub> = Minimum switch current limit = 360mA (max)

f<sub>MIN</sub> = Minimum switching frequency = 10.6kHz (max)

The LT3001 typically needs less than 0.5% of its full output power as minimum load. Alternatively, a Zener diode with its breakdown of 20% higher than the output voltage can serve as a minimum load if pre-loading is not acceptable. For a 5V output, use a 6V Zener with cathode connected to the output.

# **Design Example**

Use the following design example as a guide to design applications for the LT3001. The design example involves designing a 5V output with a 500mA load current and an input range from 8V to 32V.

$$\begin{array}{l} V_{IN(MIN)}=8V,\,V_{IN(NOM)}=12V,\,V_{IN(MAX)}=32V,\\ V_{OUT}=5V,\,I_{OUT}=500mA \end{array}$$

## Step 1: Select the Transformer Turns Ratio.

$$N_{PS} < \frac{65V - V_{IN(MAX)} - V_{LEAKAGE}}{V_{OUT} + V_F}$$

$V_{LEAKAGE}$  = Margin for transformer leakage spike = 15V  $V_{F}$  = Output diode forward voltage = ~0.3V

#### Example:

$$N_{PS} < \frac{65V - 32V - 15V}{5V + 0.3V} = 3.4$$

The choice of transformer turns ratio is critical in determining output current capability of the converter. Table 1 shows the switch voltage stress and output current capability at different transformer turns ratio.

Table 1. Switch Voltage Stress and Output Current Capability vs Turns Ratio

| N <sub>PS</sub> | V <sub>SW(MAX)</sub> at<br>V <sub>IN(MAX)</sub> (V) | I <sub>OUT(MAX)</sub> at<br>V <sub>IN(MIN)</sub> (mA) | DUTY CYCLE (%) |

|-----------------|-----------------------------------------------------|-------------------------------------------------------|----------------|

| 1:1             | 37.3                                                | 330                                                   | 14-40          |

| 2:1             | 42.6                                                | 470                                                   | 25-57          |

| 3:1             | 47.9                                                | 540                                                   | 33-67          |

Since only  $N_{PS} = 3$  can meet the 500mA output current requirement,  $N_{PS} = 3$  is chosen in this example.

#### Step 2: Determine the Primary Inductance.

Primary inductance for the transformer must be set above a minimum value to satisfy the minimum switch-off and switch-on time requirements:

$$L_{PRI} \ge \frac{t_{OFF(MIN)} \cdot N_{PS} \cdot (V_{OUT} + V_F)}{I_{SW(MIN)}}$$

$$L_{PRI} \ge \frac{t_{ON(MIN)} \cdot V_{IN(MAX)}}{I_{SW(MIN)}}$$

$t_{OFF(MIN)} = 450$ ns

$t_{ON(MIN)} = 170$ ns

$I_{SW(MIN)} = 290mA (typ)$

#### Example:

$$L_{PRI} \ge \frac{450 \text{ns} \cdot 3 \cdot (5 \text{V} + 0.3 \text{V})}{290 \text{mA}} = 25 \mu \text{H}$$

$$L_{PRI} \ge \frac{170 \text{ns} \cdot 32 \text{V}}{290 \text{mA}} = 19 \mu \text{H}$$

Most transformers specify primary inductance with a tolerance of  $\pm 20\%$ . With other component tolerance considered, choose a transformer with its primary inductance 30% larger than the minimum values calculated above.  $L_{PRI} = 40\mu H$  is then chosen in this example.

Once the primary inductance has been determined, the maximum load switching frequency can be calculated as:

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}} = \frac{1}{\frac{L_{PRI} \bullet I_{SW}}{V_{IN}} + \frac{L_{PRI} \bullet I_{SW}}{N_{PS} \bullet (V_{OLIT} + V_{E})}}$$

$$I_{SW} = \frac{V_{OUT} \cdot I_{OUT} \cdot 2}{\eta \cdot V_{IN} \cdot D}$$

Example:

$$D = \frac{(5V + 0.3V) \cdot 3}{(5V + 0.3V) \cdot 3 + 12V} = 0.57$$

$$I_{SW} = \frac{5V \cdot 0.5A \cdot 2}{0.85 \cdot 12V \cdot 0.57} = 0.86A$$

$$f_{SW}=199kHz$$

The transformer also needs to be rated for the correct saturation current level across line and load conditions. A saturation current rating larger than 2A is necessary to work with the LT3001. The 750313974 from Würth is chosen as the flyback transformer.

# Step 3: Choose the Output Diode.

Two main criteria for choosing the output diode include forward current rating and reverse voltage rating. The maximum load requirement is a good first-order guess as the average current requirement for the output diode. A conservative metric is the maximum switch current limit multiplied by the turns ratio,

$$I_{DIODE(MAX)} = I_{SW(MAX)} \cdot N_{PS}$$

Example:

$$I_{DIODE(MAX)} = 4.125A$$

Next calculate reverse voltage requirement using maximum  $V_{\text{IN}}$ :

$$V_{REVERSE} = V_{OUT} + \frac{V_{IN(MAX)}}{N_{PS}}$$

Example:

$$V_{REVERSE} = 5V + \frac{32V}{3} = 15.6V$$

The CMSH5-20 (5A, 20V diode) from Central Semiconductor is chosen.

#### Step 4: Choose the Output Capacitor.

The output capacitor should be chosen to minimize the output voltage ripple while considering the increase in size and cost of a larger capacitor. Use the equation below to calculate the output capacitance:

$$C_{OUT} = \frac{L_{PRI} \cdot I_{SW}^2}{2 \cdot V_{OUT} \cdot \Delta V_{OUT}}$$

Example:

Design for output voltage ripple less than 1% of  $V_{OUT}$ , i.e., 50mV.

$$C_{OUT} = \frac{40\mu H \cdot (0.86A)^2}{2 \cdot 5V \cdot 0.05V} = 60\mu F$$

Remember ceramic capacitors lose capacitance with applied voltage. The capacitance can drop to 40% of quoted capacitance at the maximum voltage rating. So a 100µF, 10V rating ceramic capacitor is chosen.

## Step 5: Design Snubber Circuit.

The snubber circuit protects the power switch from leakage inductance voltage spike. A DZ snubber is recommended for this application because of lower leakage inductance and larger voltage margin. The Zener and the diode need to be selected.

The maximum Zener breakdown voltage is set according to the maximum  $V_{IN}$ :

$$V_{ZENER(MAX)} \le 65V - V_{IN(MAX)}$$

Rev. 0

Example:

$$V_{ZENER(MAX)} \le 65V - 32V = 33V$$

A 20V Zener with a maximum of 21V will provide optimal protection and minimize power loss. So a 20V, 0.25W Zener from Central Semiconductor (CMDZ5250B) is chosen.

Choose a diode that is fast and has sufficient reverse voltage breakdown:

$V_{REVERSE} > V_{SW(MAX)}$

$V_{SW(MAX)} = V_{IN(MAX)} + V_{ZENER(MAX)}$

Example:

$V_{RFVFRSF} > 53V$

A 100V, 0.25A diode from Central Semiconductor (CMHD4448) is chosen.

## Step 6: Select the R<sub>FB</sub> Resistor.

Use the following equation to calculate the starting value for  $R_{\text{FB}}$ :

$$R_{FB} = \frac{N_{PS} \bullet (V_{OUT} + V_F)}{100 \mu A}$$

Example:

$$R_{FB} = \frac{3 \cdot (5V + 0.3V)}{100 \mu A} = 159k$$

Depending on the tolerance of standard resistor values, the precise resistor value may not exist. For 1% standard values, a 158k resistor should be close enough. The final  $R_{FB}$  value should be adjusted on the measured output voltage.

#### Step 7: Select the EN/UVLO Resistors.

Determine the amount of hysteresis required and calculate R1 resistor value:

$$V_{IN(HYS)} = 2.5 \mu A \cdot R1$$

Example:

Choose 2V of hysteresis,

$$R1 = 806k$$

Determine the UVLO thresholds and calculate R2 resistor value:

$$V_{IN(UVLO+)} = \frac{1.242V \cdot (R1+R2)}{R2} + 2.5\mu A \cdot R1$$

Example:

Set V<sub>IN</sub> UVLO rising threshold to 7.5V,

$$R2 = 232k$$

$$V_{IN(IJVI O+)} = 7.5V$$

$$V_{IN(UVLO-)} = 5.5V$$

#### Step 8: Ensure minimum load.

The theoretical minimum load can be approximately estimated as:

$$I_{LOAD(MIN)} = \frac{40\mu H \cdot (360mA)^2 \cdot 10.6kHz}{2 \cdot 5V} = 5.5mA$$

Remember to check the minimum load requirement in real application. The minimum load occurs at the point where the output voltage begins to climb up as the converter delivers more energy than what is consumed at the output. The real minimum load for this application is about 6mA. In this example, a  $820\Omega$  resistor is selected as the minimum load.

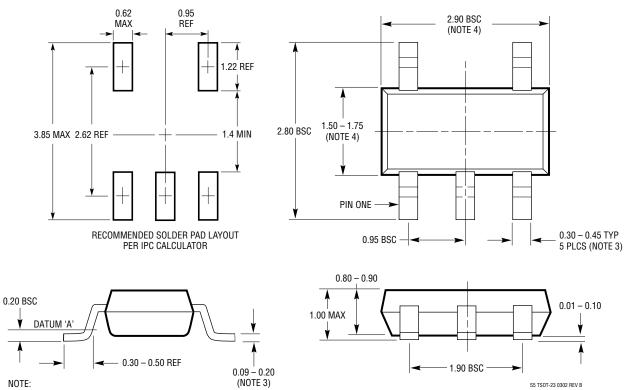

# PACKAGE DESCRIPTION

#### S5 Package 5-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1635 Rev B)

- 1. DIMENSIONS ARE IN MILLIMETERS

- 1. DIMENSIONS ARE IN MILLIMETERS

2. DRAWING NOT TO SCALE

3. DIMENSIONS ARE INCLUSIVE OF PLATING

4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

5. MOLD FLASH SHALL NOT EXCEED 0.254mm

6. JEDEC PACKAGE REFERENCE IS MO-193