#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

|    | •      | n This Document                                                                              |    |

|----|--------|----------------------------------------------------------------------------------------------|----|

| 1. | Gener  | al Description                                                                               | 6  |

|    | 1.1.   | Features                                                                                     | 6  |

| 2. | Produ  | ct Family                                                                                    | 7  |

|    | 2.1.   | Overview                                                                                     | 7  |

| 3. | Archit | ecture                                                                                       | 8  |

|    | 3.1.   | Architecture Overview                                                                        | 8  |

|    | 3.1.1. | PLB Blocks                                                                                   | 9  |

|    | 3.1.2. | Routing                                                                                      |    |

|    | 3.1.3. | Clock/Control Distribution Network                                                           |    |

|    | 3.1.4. | sysCLOCK Phase Locked Loops (PLLs) (sysCLOCK PLL is only supported in 36-ball ucBGA package) |    |

|    | 3.1.5. | sysMEM Embedded Block RAM Memory                                                             |    |

|    | 3.1.6. | sysI/O Buffer Banks                                                                          | 14 |

|    | 3.1.7. | sysIO Buffer                                                                                 | 16 |

|    | 3.1.8. | On-Chip Strobe Generators                                                                    |    |

|    | 3.1.9. | User I <sup>2</sup> C IP                                                                     |    |

|    | 3.1.10 |                                                                                              |    |

|    | 3.1.11 | 0 - 7                                                                                        |    |

|    | 3.1.12 |                                                                                              |    |

|    |        | CE40LM Configuration                                                                         |    |

|    | 3.2.1. | Device Configuration                                                                         |    |

|    | 3.2.2. | 0 -                                                                                          |    |

| 4. |        | d Switching Characteristics                                                                  |    |

|    |        | Absolute Maximum Ratings                                                                     |    |

|    |        | Recommended Operating Conditions                                                             |    |

|    |        | Power Supply Ramp Rates                                                                      |    |

|    |        | Power-On-Reset Voltage Levels                                                                |    |

|    |        | Power-up Sequence                                                                            |    |

|    |        | ESD Performance                                                                              |    |

|    |        | DC Electrical Characteristics                                                                |    |

|    |        | Supply Current                                                                               |    |

|    |        | ·                                                                                            |    |

|    |        | User SPI SpecificationssysI/O Recommended Operating Conditions                               |    |

|    |        | syst/O Single-Ended DC Electrical Characteristics                                            |    |

|    |        | Typical Building Block Performance <sup>1, 2</sup>                                           |    |

|    | 4.13.1 |                                                                                              |    |

|    | 4.13.1 | ,                                                                                            |    |

|    | _      | Derating Logic Timing                                                                        |    |

|    |        | Maximum sysI/O Buffer Performance                                                            |    |

|    |        | CE40LM Family Timing Adders                                                                  |    |

|    |        | CE40LM External Switching Characteristics                                                    |    |

|    |        | sysCLOCK PLL Timing – Preliminary                                                            |    |

|    |        | SPI Master Configuration Time                                                                |    |

|    |        | sysCONFIG Port Timing Specifications                                                         |    |

|    |        | Switching Test Conditions                                                                    |    |

| 5. |        | Information                                                                                  |    |

|    |        | Signal Descriptions                                                                          |    |

|    | 5.1.1. | Power Supply Pins                                                                            |    |

|    | 5.1.2. | Configuration Pins                                                                           |    |

|    | 5.1.3. | Configuration SPI Pins                                                                       | 29 |

|    | 5.1.4. | Global Signal Pins                                                                           | 30 |

|    |        |                                                                                              |    |

| 5.1.5. LED Signal Pins                                                   |    |

|--------------------------------------------------------------------------|----|

| 5.2. Pin Information Summary                                             |    |

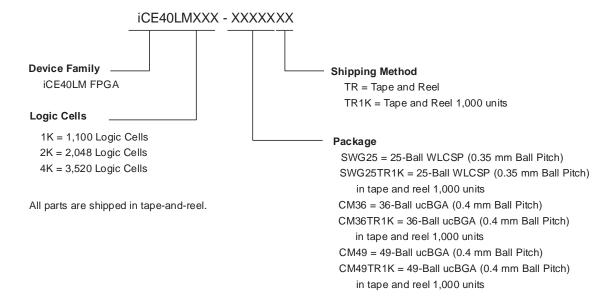

| 5.3. iCE40LM Part Number Description                                     |    |

| 5.4.1. Industrial                                                        |    |

| Supplemental Information                                                 |    |

| Technical Support                                                        |    |

| Revision History                                                         |    |

| ,                                                                        |    |

| Figures                                                                  |    |

| Figure 3.1. iCE40LM4K Device, Top View                                   | 8  |

| Figure 3.2. PLB Block Diagram                                            | 9  |

| Figure 3.3. PLL Diagram                                                  | 11 |

| Figure 3.4. sysMEM Memory Primitives                                     | 13 |

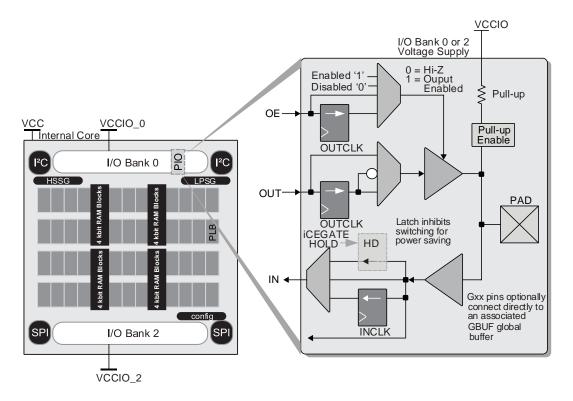

| Figure 3.5. I/O Bank and Programmable I/O Cell                           | 14 |

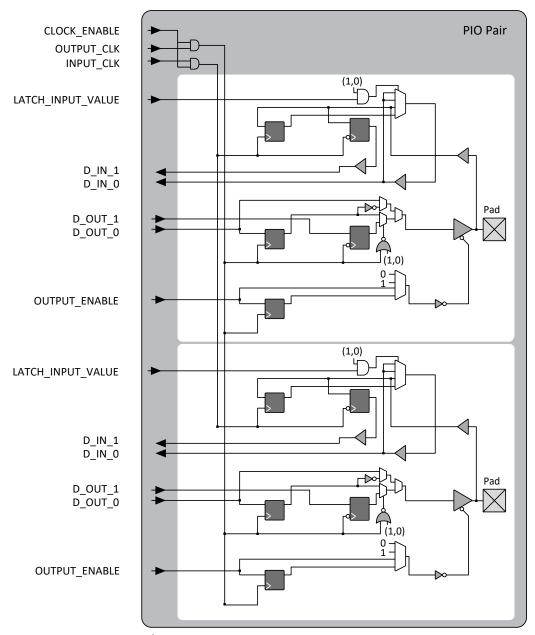

| Figure 3.6. iCE40 I/O Register Block Diagram                             | 15 |

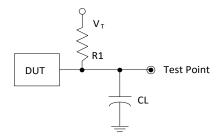

| Figure 4.1. Output Test Load, LVCMOS Standards                           | 28 |

| Tables                                                                   |    |

| Table 2.1. iCE40LM Family Selection Guide                                | 7  |

| Table 3.1. Logic Cell Signal Descriptions                                |    |

| Table 3.2. Global Buffer (GBUF) Connections to Programmable Logic Blocks |    |

| Table 3.3. PLL Signal Descriptions                                       |    |

| Table 3.4. sysMEM Block Configurations                                   |    |

| Table 3.5. EBR Signal Descriptions                                       |    |

| Table 3.6. PIO Signal List                                               | 15 |

| Table 3.7. Supported Input Standards                                     | 16 |

| Table 3.8. Supported Output Standards                                    | 16 |

| Table 3.9. iCE40LM Power Saving Features Description                     | 18 |

| Table 4.1. Absolute Maximum Ratings                                      | 19 |

| Table 4.2. Recommended Operating Conditions                              | 19 |

| Table 4.3. Power Supply Ramp Rates                                       | 19 |

| Table 4.4. Power-On-Reset Voltage Levels                                 | 20 |

| Table 4.5. DC Electrical Characteristics                                 | 21 |

| Table 4.6. Supply Current <sup>1, 2, 3, 4</sup>                          |    |

| Table 4.7. User I <sup>2</sup> C Specifications                          |    |

| Table 4.8. User SPI Specifications                                       |    |

| Table 4.9. sysI/O Recommended Operating Conditions                       |    |

| Table 4.10. sysI/O Single-Ended DC Electrical Characteristics            |    |

| Table 4.11. Pin-to-Pin Performance (LVCMOS25)                            |    |

| Table 4.12. Register-to-Register Performance                             |    |

| Table 4.13. Maximum sysI/O Buffer Performance                            |    |

| Table 4.14. iCE40LM Family Timing Adders                                 |    |

| Table 4.15. iCE40LM External Switching Characteristics                   |    |

| Table 4.16. sysCLOCK PLL Timing – Preliminary                            |    |

| Table 4.17. SPI Master Configuration Time                                |    |

| Table 4.18. sysCONFIG Port Timing Specifications                         |    |

| Table 4.19. Test Fixture Required Components, Non-Terminated Interfaces  | 28 |

5

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym          | Definition                                          |  |

|------------------|-----------------------------------------------------|--|

| DFF              | D-style Flip-Flop                                   |  |

| EBR              | Embedded Block RAM                                  |  |

| HFOSC            | High Frequency Oscillator                           |  |

| I <sup>2</sup> C | Inter-Integrated Circuit                            |  |

| LFOSC            | Low Frequency Oscillator                            |  |

| LUT              | Look Up Table                                       |  |

| LVCMOS           | Low-Voltage Complementary Metal Oxide Semiconductor |  |

| NVCM             | Non Volatile Configuration Memory                   |  |

| PFU              | Programmable Functional Unit                        |  |

| PLB              | Programmable Logic Blocks                           |  |

| PLL              | Phase Locked Loops                                  |  |

| SPI              | Serial Peripheral Interface                         |  |

| WLCSP            | Wafer Level Chip Scale Packaging                    |  |

## **General Description**

iCE40LM™ is an ultra-low power FPGA and sensor manager designed for ultra-low power mobile applications, such as smartphones, tablets and handheld devices. The iCE40LM family includes integrated SPI and I<sup>2</sup>C blocks to interface with virtually all mobile sensors and application processors. The iCE40LM family also features two Strobe Generators that can generate strobes in microsecond ranges with the Low-Power Strobe Generator and in nanosecond ranges with the High-Speed Strobe Generator.

In addition, the iCE40LM family of devices includes logic to perform other functions such as mobile bridging, antenna tuning, GPIO expansion, motion/gesture recognition, IR remote control, bar code emulation, and other custom functions.

The iCE40LM family features three device densities, from 1100 to 3520 Look Up Tables (LUTs) of logic with programmable I/Os that can be used as either SPI/I<sup>2</sup>C interface ports or general purpose I/Os. It also has up to 80 kbit of Block RAMs to work with user logic.

### 1.1. Features

- Flexible Logic Architecture

- Three devices with 1100 to 3520 LUTs

- 18 I/O pins for 25-pin WLCSP

- **Ultra-low Power Devices**

- Advanced 40 nm low power process

- As low as 120 µW standby power typical

- **Embedded and Distributed Memory**

- Two Hardened I<sup>2</sup>C Interfaces

- Two Hardened SPI Interfaces

- Two On-Chip Strobe Generators

- Low-Power Strobe Generator (Microsecond

- High-Speed Strobe Generator (Nanosecond ranges)

- High Current Drive Outputs for LED

- Three High Drive (HD) output in each device

- Source/sink nominal 24 mA

- Flexible On-Chip Clocking

- Six low-skew global signal resource

- Flexible Device Configuration

- SRAM is configured through SPI

- **Ultra-Small Form Factor**

- As small as 25-pin WLCSP package 1.71 mm × 1.71 mm

- **Applications**

- **Smartphones**

- **Tablets and Consumer Handheld Devices**

- Handheld Commercial and Industrial Devices

- Multi Sensor Management Applications

- Sensor Pre-processing and Sensor Fusion

- Always-On Sensor Applications

## **Product Family**

Table 2.1 lists device information and packages of the iCE40LM family.

Table 2.1. iCE40LM Family Selection Guide

| Part Number                              | iCE40LM1K | iCE40LM2K              | iCE40LM4K |

|------------------------------------------|-----------|------------------------|-----------|

| Logic Cells (LUT + Flip-Flop)            | 1100      | 2048                   | 3520      |

| RAM4K Memory Blocks                      | 16        | 20                     | 14        |

| RAM4K RAM Bits                           | 64 K      | 80 K                   | 80 K      |

| Package                                  |           | Programmable I/O Count |           |

| 16-pin WLCSP, 1.71 mm x 1.71 mm, 0.35 mm | 18        | 18                     | 18        |

| 36-pin ucBGA, 2.5 mm x 2.5 mm, 0.40 mm   | 28        | 28                     | 28        |

| 49-pin ucBGA, 3 mm x 3 mm, 0.40 mm       |           |                        |           |

### 2.1. Overview

The iCE40LM family of ultra-low power FPGAs has three devices with densities ranging from 1100 to 3520 Look- Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic, these devices also feature Embedded Block RAM (EBR), two Strobe Generators (LPSG, HSSG), two hardened I<sup>2</sup>C Controllers and two hardened SPI Controllers. These features allow the devices to be used in low-cost, high-volume consumer and mobile applications.

The iCE40LM devices are fabricated on a 40 nm CMOS low power process. The device architecture has several features such as user configurable I<sup>2</sup>C and SPI Controllers, either as master or as slave, and two Strobe Generators.

The iCE40LM FPGAs are available in very small form factor packages, with the smallest in 25-pin WLCSP. The 25-pin WLCSP package has a 0.35 mm ball pitch, resulting to an overall package size of 1.71 mm x 1.71 mm that easily fits into a lot of mobile applications. Table 2.1 shows the LUT densities, package and I/O pin count.

The iCE40LM devices offer enhanced I/O features such as pull-up resistors. Pull-up features are controllable on a perpin basis.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the iCE40LM family of devices. Popular logic synthesis tools provide synthesis library support for iCE40LM. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the iCE40LM device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules, including a number of reference designs, licensed free of charge, optimized for the iCE40LM FPGA family. Lattice also can provide fully verified bit-stream for some of the widely used target functions in mobile device applications, such as ultra-low power sensor management, gesture recognition, IR remote, barcode emulator functions. You can use these functions as offered by Lattice, or they can use the design to create their own unique required functions. For more information regarding Lattice's Reference Designs or fully-verified bitstreams, please contact your local Lattice representative.

FPGA-DS-02043-1 8 Downloaded from **Arrow.com**.

## 3. Architecture

### 3.1. Architecture Overview

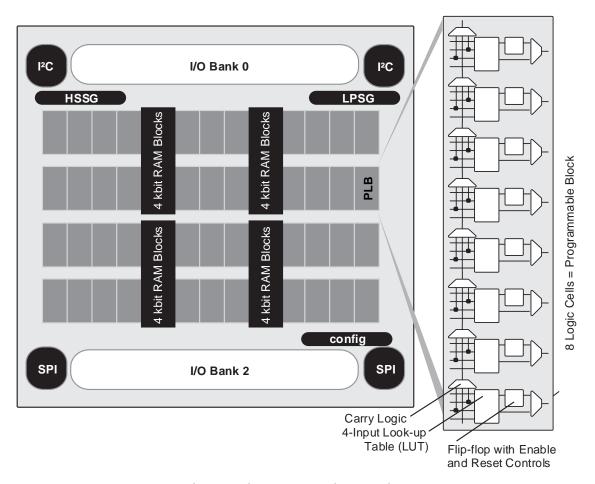

The iCE40LM family architecture contains an array of Programmable Logic Blocks (PLB), two Strobe Generators, two user configurable I<sup>2</sup>C controllers, two user configurable SPI controllers, and blocks of sysMEM™ Embedded Block RAM (EBR) surrounded by Programmable I/O (PIO). Figure 3.1 shows the block diagram of the iCE40LM4K device.

Figure 3.1. iCE40LM4K Device, Top View

The logic blocks, Programmable Logic Blocks (PLB) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each column has either logic blocks or EBR blocks. The PIO cells are located at the top and bottom of the device, arranged in banks. The PLB contains the building blocks for logic, arithmetic, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysI/O buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the iCE40LM family, There are two sysI/O banks, one on top and one on bottom. You can connect both  $V_{\text{CCIOS}}$  together, if all the I/Os are using the same voltage standard. Refer to the details in later sections of this document. The sysMEM EBRs are large 4 kbit, dedicated fast memory blocks. These blocks can be configured as RAM, ROM, or FIFO with user logic using PLBs.

Every device in the family has two user SPI ports, one of these (right side) SPI ports also supports programming and configuration of the device. The iCE40LM also includes two user I<sup>2</sup>C ports, and two Strobe Generators.

9

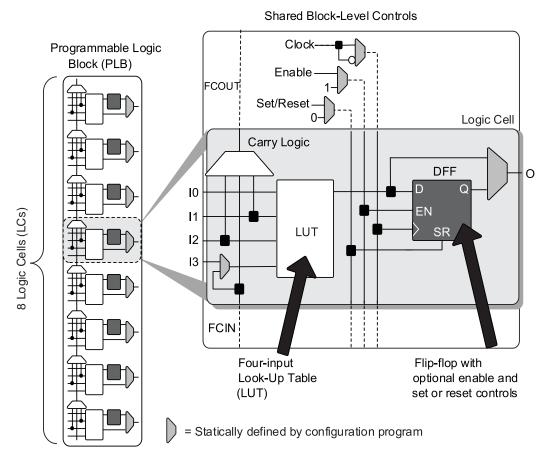

#### 3.1.1. PLB Blocks

The core of the iCE40LM device consists of Programmable Logic Blocks (PLB) which can be programmed to perform logic and arithmetic functions. Each PLB consists of eight interconnected Logic Cells (LC) as shown in Figure 3.2. Each LC contains one LUT and one register.

Figure 3.2. PLB Block Diagram

### 3.1.1.1. Logic Cells

Each Logic Cell includes three primary logic elements shown in Figure 3.2.

- A four-input Look-Up Table (LUT) builds any combinational logic function, of any complexity, requiring up to four

inputs. Similarly, the LUT element behaves as a 16x1 Read-Only Memory (ROM). Combine and cascade multiple

LUTs to create wider logic functions.

- A D-style Flip-Flop (DFF), with an optional clock-enable and reset control input, builds sequential logic functions. Each DFF also connects to a global reset signal that is automatically asserted immediately following device configuration.

- Carry Logic boosts the logic efficiency and performance of arithmetic functions, including adders, subtracters, comparators, binary counters and some wide, cascaded logic functions.

Table 3.1 lists the logic cell signals.

**Table 3.1. Logic Cell Signal Descriptions**

| Function | Туре           | Signal Name    | Description                                                               |

|----------|----------------|----------------|---------------------------------------------------------------------------|

| Input    | Data signal    | 10, 11, 12, 13 | Inputs to LUT                                                             |

| Input    | Control signal | Enable         | Clock enable shared by all LCs in the PLB                                 |

| Input    | Control signal | Set/Reset*     | Asynchronous or synchronous local set/reset shared by all LCs in the PLB. |

FPGA-DS-02043-1.8

| Function | Туре             | Signal Name | Description                                                                                                           |

|----------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| Input    | Control signal   | Clock       | Clock one of the eight Global Buffers, or from the general-purpose interconnects fabric shared by all LCs in the PLB. |

| Input    | Inter-PLB signal | FCIN        | Fast carry in                                                                                                         |

| Output   | Data signals     | 0           | LUT or registered output                                                                                              |

| Output   | Inter-PFU signal | FCOUT       | Fast carry out                                                                                                        |

<sup>\*</sup>Note: If Set/Reset is not used, then the flip-flop is never set/reset, except when cleared immediately after configuration.

### **3.1.2.** Routing

There are many resources provided in the iCE40LM devices to route signals individually with related control signals. The routing resources consist of switching circuitry, buffers, and metal interconnect (routing) segments.

The inter-PLB connections are made with three different types of routing resources: Adjacent (spans two PLBs), x4 (spans five PLBs), and x12 (spans thirteen PLBs). The adjacent, x4 and x12 connections provide fast and efficient connections in the diagonal, horizontal, and vertical directions.

The design tool takes the output of the synthesis tool, and places and routes the design.

### 3.1.3. Clock/Control Distribution Network

Each iCE40LM device has six global inputs, two pins on the top bank, and four pins on the bottom bank.

These global inputs can be used as high fanout nets, clock, reset, or enable signals. The dedicated global pins are identified as Gxx and the global buffers are identified as GBUF[7:0]. These six inputs may be used as general purpose I/O, if they are not used to drive the clock nets.

Table 3.2 lists the connections between a specific global buffer and the inputs on a PLB. All global buffers optionally connect to the PLB CLK input. Any four of the eight global buffers can drive logic inputs to a PLB. Even-numbered global buffers optionally drive the Set/Reset input to a PLB. Similarly, odd-numbered buffers optionally drive the PLB clockenable input. GBUF[7:6, 3:0] can connect directly to G[7:6, 3:0] pins respectively. GBUF4 and GBUF5 can connect to the two on-chip Strobe Generators (GBUF4 connects to LPSG, GBUF5 connects to HSSG).

Table 3.2. Global Buffer (GBUF) Connections to Programmable Logic Blocks

| Global Buffer | LUT Inputs           | Clock | Reset | Clock Enable |

|---------------|----------------------|-------|-------|--------------|

| GBUF0         |                      | Yes   | Yes   | _            |

| GBUF1         |                      | Yes   | 1     | Yes          |

| GBUF2         |                      | Yes   | Yes   | _            |

| GBUF3         | Yes, any 4 of 8 GBUF | Yes   | 1     | Yes          |

| GBUF4         | Inputs               | Yes   | Yes   | _            |

| GBUF5         |                      | Yes   | -     | Yes          |

| GBUF6         |                      | Yes   | Yes   | _            |

| GBUF7         |                      | Yes   | _     | Yes          |

The maximum frequency for the global buffers are listed in Table 4.15.

### 3.1.3.1. Global Hi-Z Control

The global high-impedance control signal, GHIZ, connects to all I/O pins on the iCE40LM device. This GHIZ signal is automatically asserted throughout the configuration process, forcing all user I/O pins into their high-impedance state.

### 3.1.3.2. Global Reset Control

The global reset control signal connects to all PLB and PIO flip-flops on the iCE40LM device. The global reset signal is automatically asserted throughout the configuration process, forcing all flip-flops to their defined wake-up state. For PLB flip-flops, the wake-up state is always reset, regardless of the PLB flip-flop primitive used in the application.

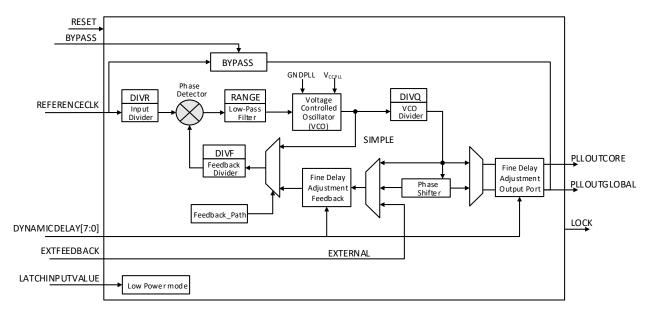

# 3.1.4. sysCLOCK Phase Locked Loops (PLLs) (sysCLOCK PLL is only supported in 36-ball ucBGA package)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The iCE40LM devices have one sysCLOCK PLL (Please note that the 25-pin WLCSP package does not support the PLL). REFERENCECLK is the reference frequency input to the PLL and its source can come from an external I/O pin, the internal strobe generator or from internal routing. EXTFEEDBACK is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The PLLOUT output has an output divider, thus allowing the PLL to generate different frequencies for each output. The output divider can have a value from 1 to 64 (in increments of 2X). The PLLOUT outputs can all be used to drive the iCE40 global clock network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 3.3.

The timing of the device registers can be optimized by programming a phase shift into the PLLOUT output clock which will advance or delay the output clock with reference to the REFERENCECLK clock. This phase shift can either be programmed during configuration or adjusted dynamically. In dynamic mode, the PLL may lose lock after a phase adjustment on the output used as the feedback source and not relock until the tLOCK parameter has been satisfied.

The iCE40LM PLL functions the same as the PLLs in the iCE40 family. For more details on the PLL, refer to iCE40 sysCLOCK PLL Design and Usage Guide.

Figure 3.3. PLL Diagram

Table 3.3 provides signal descriptions of the PLL block.

**Table 3.3. PLL Signal Descriptions**

| Signal Name       | Direction | Description                                                                                                                                                                                 |  |

|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REFERENCECLK      | Input     | Input reference clock                                                                                                                                                                       |  |

| BYPASS            | Input     | The BYPASS control selects which clock signal connects to the PLLOUT output.  0 – PLL generated signal  1 – REFERENCECLK                                                                    |  |

| EXTFEEDBACK       | Input     | External feedback input to PLL. Enabled when the FEEDBACK_PATH attribute is set to EXTERNAL.                                                                                                |  |

| DYNAMICDELAY[7:0] | Input     | Fine delay adjustment control inputs. Enabled when DELAY_ADJUSTMENT_MODE is set to DYNAMIC.                                                                                                 |  |

| LATCHINPUTVALUE   | Input     | When enabled, puts the PLL into low-power mode; PLL output is held static at last input clock value. Set ENABLE ICEGATE_PORTA and PORTB to 1 to enable.                                     |  |

| PLLOUTGLOBAL      | Output    | Output from the Phase-Locked Loop (PLL). Drives a global clock network on the FPGA. The port has optimal connections to global clock buffers GBUF4 and GBUF5.                               |  |

| PLLOUTCORE Output |           | Output clock generated by the PLL, drives regular FPGA routing. The frequency generated on this output is the same as the frequency of the clock signal generated on the PLLOUTLGOBAL port. |  |

| LOCK              | Output    | When High, indicates that the PLL output is phase aligned or locked to the input reference clock.                                                                                           |  |

| RESET             | Input     | Active low reset.                                                                                                                                                                           |  |

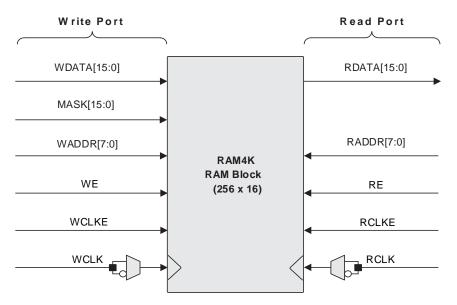

### 3.1.5. sysMEM Embedded Block RAM Memory

Larger iCE40LM device includes multiple high-speed synchronous sysMEM Embedded Block RAMs (EBRs), each 4 kbit in size. This memory can be used for a wide variety of purposes including data buffering, and FIFO.

### 3.1.5.1. sysMEM Memory Block

The sysMEM block can implement single port, pseudo dual port, or FIFO memories with programmable logic resources. Each block can be used in a variety of depths and widths as shown in Table 3.4.

**Table 3.4. sysMEM Block Configurations**

| Block RAM<br>Configuration                                           | Block RAM<br>Configuration<br>and Size | WADDR Port<br>Size (Bits) | WDATA Port<br>Size (Bits) | RADDR Port<br>Size (Bits) | RDATA Port<br>Size (Bits) | MASK Port<br>Size (Bits) |

|----------------------------------------------------------------------|----------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| SB_RAM256x16<br>SB_RAM256x16NR<br>SB_RAM256x16NW<br>SB_RAM256x16NRNW | 256 x 16 (4 K)                         | 8 [7:0]                   | 16 [15:0]                 | 8 [7:0]                   | 16 [15:0]                 | 16 [15:0]                |

| SB_RAM512x8<br>SB_RAM512x8NR<br>SB_RAM512x8NW<br>SB_RAM512x8NRNW     | 512 x 8 (4 K)                          | 9 [8:0]                   | 8 [7:0]                   | 9 [8:0]                   | 8 [7:0]                   | No Mask Port             |

| SB_RAM1024x4 SB_RAM1024x4NR SB_RAM1024x4NW SB_RAM1024x4NRNW          | 1024 x 4 (4 K)                         | 10 [9:0]                  | 4 [3:0]                   | 10 [9:0]                  | 4 [3:0]                   | No Mask Port             |

| SB_RAM2048x2<br>SB_RAM2048x2NR<br>SB_RAM2048x2NW<br>SB_RAM2048x2NRNW | 2048 x 2 (4 K)                         | 11 [10:0]                 | 2 [1:0]                   | 11 [10:0]                 | 2 [1:0]                   | No Mask Port             |

**Note:** For iCE40LM EBR primitives with a negative-edged Read or Write clock, the base primitive name is appended with an N and an R or W depending on the clock that is affected.

13

### 3.1.5.2. RAM Initialization and ROM Operation

If desired, the contents of the RAM can be pre-loaded during device configuration.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

#### 3.1.5.3. Memory Cascading

Larger and deeper blocks of RAM can be created using multiple EBR sysMEM Blocks.

### 3.1.5.4. RAM4K Block

Figure 3.4 shows the 256 x 16 memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array.

Figure 3.4. sysMEM Memory Primitives

Table 3.5 lists the EBR signals.

**Table 3.5. EBR Signal Descriptions**

| Signal Name | Direction | Description                                                           |  |

|-------------|-----------|-----------------------------------------------------------------------|--|

| WDATA[15:0] | Input     | Write Data input.                                                     |  |

| MASK[15:0]  | Input     | Masks write operations for individual data bit-lines.                 |  |

|             |           | 0 – Write bit                                                         |  |

|             |           | 1 – Do not write bit                                                  |  |

| WADDR[7:0]  | Input     | Write Address input. Selects one of 256 possible RAM locations.       |  |

| WE          | Input     | Write Enable input.                                                   |  |

| WCLKE       | Input     | Write Clock Enable input.                                             |  |

| WCLK        | Input     | Write Clock input. Default rising-edge, but with falling-edge option. |  |

| RDATA[15:0] | Output    | Read Data output.                                                     |  |

| RADDR[7:0]  | Input     | Read Address input. Selects one of 256 possible RAM locations.        |  |

| RE          | Input     | Read Enable input.                                                    |  |

| RCLKE       | Input     | Read Clock Enable input.                                              |  |

| RCLK        | Input     | Read Clock input. Default rising-edge, but with falling-edge option.  |  |

The iCE40LM EBR block functions the same as EBR blocks in the iCE40 family. For further information, refer to Memory Usage Guide for iCE40 Devices (FPGA-TN-02002).

### 3.1.6. sysI/O Buffer Banks

iCE40LM devices have up to two I/O banks with independent  $V_{CCIO}$  rails. Configuration bank  $V_{CC\_SPI}$  for the SPI I/Os is connected to  $V_{CCIO2}$  on the 25-pin WLCSP package.

#### 3.1.6.1. Programmable I/O (PIO)

The programmable logic associated with an I/O is called a PIO. The individual PIOs are connected to their respective sysI/O buffers and pads. The PIOs are placed on the top and bottom of the devices.

Figure 3.5. I/O Bank and Programmable I/O Cell

The PIO contains three blocks: an input register block, output register block iCEGate™, and tri-state register block. To save power, the optional iCEGate latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Note that the freeze signal is common to the bank. These blocks can operate in a variety of modes along with the necessary clock and selection logic.

### 3.1.6.2. Input Register Block

The input register blocks for the PIOs on all edges contain registers that can be used to condition high-speed interface signals before they are passed to the device core.

### 3.1.6.3. Output Register Block

The output register block can optionally register signals from the core of the device before they are passed to the sysl/O buffers.

Figure 3.6 shows the input/output register block for the PIOs.

14

15

= Statically defined by configuration program.

Figure 3.6. iCE40 I/O Register Block Diagram

**Table 3.6. PIO Signal List**

| Pin Name                         | I/O Type | Description                   |

|----------------------------------|----------|-------------------------------|

| OUTPUT_CLK                       | Input    | Output register clock         |

| CLOCK_ENABLE                     | Input    | Clock enable                  |

| INPUT_CLK                        | Input    | Input register clock          |

| OUTPUT_ENABLE                    | Input    | Output enable                 |

| D_OUT_0/1                        | Input    | Data from the core            |

| D_IN_0/1 Output Data to the core |          | Data to the core              |

| LATCH_INPUT_VALUE                | Input    | Latches/holds the Input Value |

### 3.1.7. sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow you to implement a wide variety of standards that are found in today's systems with LVCMOS interfaces.

### 3.1.7.1. Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when VCC, VCCIO\_0, VCCIO\_2, and VCC\_SPI (VCC\_SPI is connected to VCCIO\_2 on the 25-pin WLCSP and 36-pin ucBGA packages) reach the level defined in Table 4.4. After the POR signal is deactivated, the FPGA core logic becomes active. You must ensure that all VCCIO banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a device prior to configuration is tri-stated with a weak pull-up to VCCIO. The I/O pins maintain the pre-configuration state until VCC and VCCIO\_2 reach the defined levels. The I/Os take on the software user-configured settings only after VCC\_SPI reaches the level and the device performs a proper download/ configuration. Unused I/Os are automatically blocked and the pull-up termination is disabled.

#### 3.1.7.2. Supported Standards

The iCE40LM sysI/O buffer supports all single-ended input and output standards. The buffer supports the LVCMOS 1.8 V, 2.5 V, and 3.3 V standards. The buffer has individually configurable options for bus maintenance (weak pull-up or none).

Table 3.7 and Table 3.8 show the I/O standards (together with their supply and reference voltages) supported by the iCE40LM devices.

**Table 3.7. Supported Input Standards**

| Input Standard          | V <sub>CCIO</sub> (Typical) |       |       |

|-------------------------|-----------------------------|-------|-------|

| input Standard          | 3.3 V                       | 2.5 V | 1.8 V |

| Single-Ended Interfaces |                             |       |       |

| LVCMOS33                | Yes                         | _     | _     |

| LVCMOS25                | _                           | Yes   | _     |

| LVCMOS18*               | _                           | _     | Yes   |

**Table 3.8. Supported Output Standards**

| Output Standard         | V <sub>CCIO</sub> (Typical) |  |  |  |  |

|-------------------------|-----------------------------|--|--|--|--|

| Single-Ended Interfaces |                             |  |  |  |  |

| LVCMOS33                | 3.3 V                       |  |  |  |  |

| LVCMOS25                | 2.5 V                       |  |  |  |  |

| LVCMOS18*               | 1.8 V                       |  |  |  |  |

### 3.1.8. On-Chip Strobe Generators

The iCE40LM devices feature two different Strobe Generators. One is tailored for low-power operation (Low Power Strobe Generator – LPSG), and generates periodic strobes in the microsecond (µs) ranges. The other is tailored for high-speed operation (High Speed Strobe Generator – HSSG), and generates periodic strobes in the Nanosecond (ns) ranges.

The Strobe Generators (HSSG and LPSG) provide fixed periodic strobes, and these strobes can be used as a clock source. When used as a clock source, the HSSG can provide strobe frequency in the range of 5 MHz - 20 MHz. The LPSG can provide strobe frequency in the range of 4 kHz - 20 kHz.

For further information on how to use the LPSG and HSSG, refer to iCE40LM On-Chip Strobe Generator Usage Guide (FPGA-TN-02212).

© 2018-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 3.1.9. User I<sup>2</sup>C IP

The iCE40LM devices have two  $I^2C$  IP cores. Either of the two cores can be configured either as an  $I^2C$  master or as an  $I^2C$  slave. Both  $I^2C$  cores have preassigned pins, or you can select different pins, when the core is used.

When the IP core is configured as master, it will be able to control other devices on the I<sup>2</sup>C bus through the preassigned pin interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an I<sup>2</sup>C Master. The I<sup>2</sup>C cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Clock stretching

- Up to 400 kHz data transfer speed

- General Call support

For further information on the User I<sup>2</sup>C, refer to iCE40 SPI/I2C Hardened IP Usage Guide (FPGA-TN-02010).

#### 3.1.10. User SPI IP

The iCE40LM devices have two SPI IP cores. Both SPI cores have preassigned pins, or you can select different pins, when the SPI core is used. Both SPI IP core can be configured as a SPI master or as a slave. When the SPI IP core is configured as a master, it controls the other SPI enabled devices connected to the SPI Bus. When SPI IP core is configured as a slave, the device will be able to interface to an external SPI master.

The SPI IP core supports the following functions:

- Configurable Master and Slave modes

- Full-Duplex data transfer

- Mode fault error flag with CPU interrupt capability

- Double-buffered data register

- Serial clock with programmable polarity and phase

- LSB First or MSB First Data Transfer

For further information on the User I<sup>2</sup>C, refer to iCE40 SPI/I2C Hardened IP Usage Guide (FPGA-TN-02010).

### 3.1.11. High Drive I/O Pins

The iCE40LM family devices offer 3 High Drive (HD) outputs in each device in the family. The HD outputs are ideal to drive LED signals on mobile application.

These HD outputs can be driven in different drive modes. The default is standard drive, which source/sink 8 mA current nominally. When HD drive option is selected, these HD outputs can source/sink 24 mA current nominally.

The pins on the HD I/Os are labeled with HD in it.

### 3.1.12. Power On Reset

iCE40LM devices have power-on reset circuitry to monitor  $V_{CC}$ ,  $V_{CCIO\_0}$ ,  $V_{CCIO\_2}$ , and  $V_{CC\_SPI}$  voltage levels during power-up and operation. At power-up, the POR circuitry monitors these voltage levels. It then triggers download from the external Flash memory after reaching the power-up levels specified in Table 4.4. Before and during configuration, the I/Os are held in tri-state. I/Os are released to user functionality once the device has finished configuration.

FPGA-DS-02043-1.8

## 3.2. iCE40LM Configuration

This section describes the programming and configuration of the iCE40LM family.

### 3.2.1. Device Configuration

There are various ways to configure the Configuration RAM (CRAM), using SPI port, including:

- From an SPI Flash (Master SPI mode)

- System microprocessor to drive a Serial Slave SPI port (SSPI mode)

For more details on configuring the iCE40LM, refer to iCE40 Programming and Configuration (FPGA-TN-02001).

### 3.2.2. Power Saving Options

The iCE40LM devices feature iCEGate and PLL low power mode to allow you to meet the static and dynamic power requirements of their applications. Table 3.9 describes the function of these features.

Table 3.9. iCE40LM Power Saving Features Description

| Device Subsystem | Feature Description                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL              | When LATCHINPUTVALUE is enabled, it forces the PLL into low-power mode; PLL output is held static at last input clock value.                                                                                                   |

| iCEGate          | To save power, the optional iCEGate latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Registered inputs are effectively frozen by their associated clock or clockenable control. |

FPGA-DS-02043-1.8 Downloaded from Arrow.com.

## 4. DC and Switching Characteristics

## 4.1. Absolute Maximum Ratings

**Table 4.1. Absolute Maximum Ratings**

| Parameter                                                       | Min  | Max  | Unit |

|-----------------------------------------------------------------|------|------|------|

| Supply Voltage V <sub>CC</sub>                                  | -0.5 | 1.42 | V    |

| Output Supply Voltage V <sub>CCIO</sub> and V <sub>CC_SPI</sub> | -0.5 | 3.60 | V    |

| PLL Supply Voltage V <sub>CCPLL</sub>                           | -0.5 | 1.30 | V    |

| I/O Tri-state Voltage Applied                                   | -0.5 | 3.60 | V    |

| Dedicated Input Voltage Applied                                 | -0.5 | 3.60 | V    |

| Storage Temperature (Ambient)                                   | -65  | 150  | °C   |

| Junction Temperature (T <sub>J</sub> )                          | -65  | 125  | °C   |

#### Notes:

- Stress above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- Compliance with Thermal Management document is required.

- All voltages referenced to GND.

### 4.2. Recommended Operating Conditions

**Table 4.2. Recommended Operating Conditions**

| Symbol                               | Parameter                                                           | Min  | Max  | Unit |

|--------------------------------------|---------------------------------------------------------------------|------|------|------|

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage                                                 | 1.14 | 1.26 | V    |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage V <sub>CCIO_0</sub> , V <sub>CCIO_2</sub> | 1.71 | 3.46 | V    |

| V <sub>CC_PLL</sub> <sup>4</sup>     | PLL Supply Voltage                                                  | 1.14 | 1.26 | V    |

| V <sub>CC_SPI</sub> <sup>5</sup>     | Config SPI port Power Supply Voltage                                | 1.71 | 3.46 | V    |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation                           | -40  | 100  | °C   |

#### Notes:

- Like power supplies must be tied together, V<sub>CCIO\_0</sub> to V<sub>CCIO\_2</sub>, if they are at same supply voltage and if they meet the power up sequence requirement. Please refer to Power Up Sequence section. V<sub>CC</sub> and V<sub>CCPLL</sub> are not recommended to be tied together. Refer to iCE40 Hardware Checklist (FPGA-TN-02006).

- 2. See recommended voltages by I/O standard in subsequent table.

- 3.  $V_{CCIO}$  pins of unused I/O banks should be connected to the  $V_{CC}$  power supply on boards.

- 4. For 25-pin WLCSP, PLL is not supported.

- 5. For 25-pin WLCSP and 36-pin ucBGA packages, V<sub>CC\_SPI</sub> is connected to V<sub>CCIO\_2</sub> on the package. V<sub>CC\_SPI</sub> is used to power the SPI1 ports in both configuration mode and user mode.

## 4.3. Power Supply Ramp Rates

**Table 4.3. Power Supply Ramp Rates**

| Symbol            | Parameter                                      | Min  | Max | Unit |

|-------------------|------------------------------------------------|------|-----|------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies | 0.01 | 10  | V/ms |

#### Notes:

FPGA-DS-02043-1.8

- Assumes monotonic ramp rates.

- Power up sequence must be followed. See the Power-up Sequence section.

## 4.4. Power-On-Reset Voltage Levels

Table 4.4. Power-On-Reset Voltage Levels

| Symbol    | Parameter                                                                             | Min                                       | Max  | Unit |   |

|-----------|---------------------------------------------------------------------------------------|-------------------------------------------|------|------|---|

| VDODLID   | Power-On-Reset ramp up trip point (circuit                                            | V <sub>CC</sub>                           | 0.67 | 0.99 | V |

|           | monitoring $V_{CC}$ , $V_{CCIO\_2}$ , and $V_{CC\_SPI}$ )                             | V <sub>CCIO_2</sub> , V <sub>CC_SPI</sub> | 0.70 | 1.59 | ٧ |

| Vacanti ' | Power-On-Reset ramp down trip point                                                   | V <sub>CC</sub>                           | _    | 0.66 | V |

|           | (circuit monitoring V <sub>CC</sub> , V <sub>CCIO_2</sub> , and V <sub>CC_SPI</sub> ) | V <sub>CCIO_2</sub> , V <sub>CC_SPI</sub> | _    | 1.59 | V |

**Note**: These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

### 4.5. Power-up Sequence

For all iCE40LM devices, it is required to have the  $V_{CC}/V_{CCPLL}$  power supply powered up before all other power supplies. The  $V_{CC}/V_{CCPLL}$  has to be higher than 0.5 V before other supplies are powered from GND.

In addition, for all iCE40LM devices, it is required that  $V_{CCSPI}$  not be the last power supply to ramp up. The  $V_{CCSPI}$  has to be higher than 0.5 V before the last supply is ramped.

In the required power up sequence,  $V_{CC}/V_{CCPLL}$  should be ramped first. Following  $V_{CC}/V_{CCPLL}$ ,  $V_{CCSPI}$  should be ramped next, followed by the remaining supplies. On the 25-pin WLCSP,  $V_{CCPLL}$  is connected to  $V_{CC}$ , and is powered up together with  $V_{CC}$ . On the 25-pin WLCSP and 36-pin caBGA,  $V_{CCIO_2}$  is connected to  $V_{CC_2SPI}$ , and should be powered up right after  $V_{CC}/V_{CCPLL}$  with  $V_{CCSPI}$ . Due to this connection,  $V_{CCIO_2}$  cannot connect to  $V_{CCIO_2}$  even if they are at the same supply voltage. The sequence is defined below:

- For 49-pin caBGA: Vcc, Vccpll, Vcc\_SPI, Vcclo\_0 and Vcclo\_2; Order of Vcclo\_0 and Vcclo\_2 is not important.

- For 36-pin caBGA: V<sub>CC</sub>, V<sub>CCPLL</sub>, V<sub>CC SPI</sub>/V<sub>CCIO 2</sub>, V<sub>CCIO 0</sub>

- For 25-pin WLCSP: V<sub>CC</sub>/V<sub>CCPLL</sub>, V<sub>CC SPI</sub>/V<sub>CCIO 2</sub>, V<sub>CCIO 0</sub>

There is no power down sequence required. However, when partial power supplies are powered down, it is required that the above sequence is followed when these supplies are powered up again.

### 4.6. ESD Performance

Please contact Lattice Semiconductor for additional information.

### 4.7. DC Electrical Characteristics

Over recommended operating conditions.

**Table 4.5. DC Electrical Characteristics**

| Symbol                                               | Parameter                                       | Condition                                                                                                          | Min | Тур | Max  | Unit |

|------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 3, 4</sup> | Input or I/O Leakage                            | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub> + 0.2 V                                                                  | _   | _   | ±10  | μΑ   |

| C <sub>1</sub>                                       | I/O Capacitance <sup>2</sup>                    | V <sub>CCIO</sub> = 3.3 V, 2.5 V, 1.8 V<br>V <sub>CC</sub> = Typ, V <sub>IO</sub> = 0 to V <sub>CCIO</sub> + 0.2 V | _   | 6   | _    | pf   |

| C <sub>2</sub>                                       | Global Input Buffer<br>Capacitance <sup>2</sup> | V <sub>CCIO</sub> = 3.3 V, 2.5 V, 1.8 V<br>V <sub>CC</sub> = Typ, V <sub>IO</sub> = 0 to V <sub>CCIO</sub> + 0.2 V | _   | 6   | _    | pf   |

| V <sub>HYST</sub>                                    | Input Hysteresis                                | V <sub>CCIO</sub> = 1.8 V, 2.5 V, 3.3 V                                                                            | _   | 200 | _    | mV   |

|                                                      |                                                 | $V_{CCIO} = 1.8 \text{ V}, 0 \le V_{IN} \le 0.65 \text{ V}_{CCIO}$                                                 | -3  | _   | -31  | μΑ   |

| I <sub>PU</sub>                                      | Internal PIO Pull-up Current                    | $V_{CCIO} = 2.5 \text{ V}, 0 \le V_{IN} \le 0.65 \text{ V}_{CCIO}$                                                 | -8  | _   | -72  | μΑ   |

|                                                      |                                                 | V <sub>CCIO</sub> = 3.3 V, 0 ≤ V <sub>IN</sub> ≤ 0.65 V <sub>CCIO</sub>                                            | -11 | _   | -128 | μΑ   |

#### Notes:

- Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Internal pull-up resistors are disabled.

- 2.  $T_J 25$  °C, f = 1.0 MHz.

- Refer to V<sub>IL</sub> and V<sub>IH</sub> in Table 4.10.

- Some products are clamped to a diode when V<sub>IN</sub> is larger than V<sub>CCIO</sub>.

### 4.8. Supply Current

Table 4.6. Supply Current<sup>1, 2, 3, 4</sup>

| Symbol                   | Parameter                                                                 | Typ VCC⁴ | Unit |

|--------------------------|---------------------------------------------------------------------------|----------|------|

| ICCSTDBY                 | Core Power Supply Static Current                                          | 100      | μΑ   |

| I <sub>CCPLLSTDBY</sub>  | PLL Power Supply Static Current                                           | 11       | μΑ   |

| ICCIOSTDBY, ICC_SPISTDBY | V <sub>CCIO</sub> , V <sub>CC_SPI</sub> Power Supply Static Current       | 2.5      | μΑ   |

| Іссреак                  | Core Power Supply Startup Peak Current                                    | 11.2     | mA   |

| ICCPLLPEAK               | PLL Power Supply Startup Peak Current                                     | 2.8      | mA   |

| ICCIOPEAK, ICC_SPIPEAK   | V <sub>CCIO</sub> , V <sub>CC_SPI</sub> Power Supply Startup Peak Current | 21.4     | mA   |

#### Notes:

- Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip PLL is off. For more detail with your specific design, use the Power Calculator tool. Power specified with master SPI configuration mode. Other modes may be up to 25% higher.

- 2. Frequency = 0 MHz.

- 3. TJ = 25 °C, power supplies at nominal voltage.

- 4. Does not include pull-up.

- For 25-pin WLCSP, VCCPLL is tied internally on the package, and Vcc\_spi is also connected to Vccio\_2 on the package..

21 FPGA-DS-02043-1.8

Downloaded from Arrow.com.

## 4.9. User I<sup>2</sup>C Specifications

Table 4.7. User I<sup>2</sup>C Specifications

| Parameter                          | Barramatar Dagarintian               | spe | ec (STD Mo | de) | spec (FAST Mode) |     |     | Unit |

|------------------------------------|--------------------------------------|-----|------------|-----|------------------|-----|-----|------|

| Symbol                             | Parameter Description                | Min | Тур        | Max | Min              | Тур | Max |      |

| f <sub>SCL</sub>                   | Maximum SCL clock frequency          | _   | _          | 100 | _                | _   | 400 | kHz  |

| tнı                                | SCL clock HIGH Time                  | 4   | _          | _   | 0.6              | _   | _   | μs   |

| t <sub>LO</sub>                    | SCL clock LOW Time                   | 4.7 | _          | _   | 1.3              | _   | _   | μs   |

| t <sub>SU</sub> , t <sub>DAT</sub> | Setup time (DATA)                    | 250 | _          | _   | 100              | _   | _   | μs   |

| t <sub>HD</sub> , t <sub>DAT</sub> | Hold time (DATA)                     | 0   | _          | _   | 0                | _   | _   | μs   |

| tsu, tsta                          | Setup time (START condition)         | 4.7 | _          | _   | 0.6              | _   | _   | μs   |

| thd, tsta                          | Hold time (START condition)          | 4   | _          | _   | 0.6              | _   | _   | μs   |

| tsu, tsто                          | Setup time (STOP condition)          | 4   | _          | _   | 0.6              | _   | _   | μs   |

| t <sub>BUF</sub>                   | Bus free time between STOP and START | 4.7 |            |     | 1.3              |     | _   | μs   |

| tco, tdat                          | SCL LOW to DATAOUT valid             | _   | _          | 3.4 | _                | _   | 0.9 | μs   |

## 4.10. User SPI Specifications

**Table 4.8. User SPI Specifications**

| Parameter Symbol     | Parameter Description       | Min | Тур | Max  | Unit |

|----------------------|-----------------------------|-----|-----|------|------|

| f <sub>MAX</sub>     | Maximum SCK clock frequency | _   | _   | 45   | MHz  |

| tнı                  | HIGH period of SCK clock    | 9   | _   | _    | ns   |

| t <sub>LO</sub>      | LOW period of SCK clock     | 9   | _   | _    | ns   |

| tsumaster            | Setup time (master mode)    | 2   | _   | _    | ns   |

| tHOLDmaster          | Hold time (master mode)     | 5   | _   | _    | ns   |

| t <sub>SUslave</sub> | Setup time (slave mode)     | 2   | _   | _    | ns   |

| tHOLDslave           | Hold time (slave mode)      | 5   | _   | _    | ns   |

| tscк20uт             | SCK to out (slave mode)     | _   | _   | 13.5 | ns   |

## 4.11. sysI/O Recommended Operating Conditions

Table 4.9. sysI/O Recommended Operating Conditions

| Standard   | V <sub>CCIO</sub> (V) |     |      |  |  |

|------------|-----------------------|-----|------|--|--|

| Standard   | Min                   | Тур | Max  |  |  |

| LVCMOS 3.3 | 3.14                  | 3.3 | 3.46 |  |  |

| LVCMOS 2.5 | 2.37                  | 2.5 | 2.62 |  |  |

| LVCMOS 1.8 | 1.71                  | 1.8 | 1.89 |  |  |

© 2018-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 4.12. sysI/O Single-Ended DC Electrical Characteristics

Table 4.10. sysI/O Single-Ended DC Electrical Characteristics

| Input/Output | V <sub>IL</sub>                                    |                        | V <sub>IH</sub> *                                 |                           | V <sub>OL</sub> Max          | V <sub>OH Min</sub>           | I <sub>OL</sub>         | I <sub>OH</sub> Max     |     |      |  |     |                         |   |    |

|--------------|----------------------------------------------------|------------------------|---------------------------------------------------|---------------------------|------------------------------|-------------------------------|-------------------------|-------------------------|-----|------|--|-----|-------------------------|---|----|

| Standard     | Min (V)                                            | Max (V)                | Min (V)                                           | Max (V)                   | (V)                          | (V)                           | (mA)                    | (mA)                    |     |      |  |     |                         |   |    |

| LVCMOS 3.3   | -0.3                                               | 0.8                    | 2.0                                               | V <sub>CCIO</sub> + 0.2 V | 0.4                          | V <sub>CCIO</sub> - 0.4       | 8                       | -8                      |     |      |  |     |                         |   |    |

| LVCIVIOS 3.3 | -0.3                                               | 0.8                    | 2.0                                               |                           | 0.2                          | V <sub>CCIO</sub> - 0.2       | 0.1                     | -0.1                    |     |      |  |     |                         |   |    |

| LVCMOS 2.F   | -0.3                                               | 0.7 1.7                | 0.7                                               | 1.7                       | .7 V <sub>CCIO</sub> + 0.2 V | 0.4                           | V <sub>CCIO</sub> - 0.4 | 6                       | -6  |      |  |     |                         |   |    |

| LVCMOS 2.5   |                                                    |                        |                                                   |                           |                              | 1.7 V <sub>CCIO</sub> + 0.2 V | 0.2                     | V <sub>CCIO</sub> - 0.2 | 0.1 | -0.1 |  |     |                         |   |    |

| LVCMOS 1.0   | -0.3 0.35 V <sub>CCIO</sub> 0.65 V <sub>CCIO</sub> | 0.2                    |                                                   |                           |                              |                               |                         |                         |     |      |  | 0.4 | V <sub>CCIO</sub> - 0.4 | 4 | -4 |

| LVCMOS 1.8   |                                                    | U.65 V <sub>CCIO</sub> | .65 V <sub>CCIO</sub>   V <sub>CCIO</sub> + 0.2 V | 0.2                       | V <sub>CCIO</sub> – 0.2      | 0.1                           | -0.1                    |                         |     |      |  |     |                         |   |    |

<sup>\*</sup>Note: Some products are clamped to a diode when VIN is larger than VCCIO.

## 4.13. Typical Building Block Performance<sup>1, 2</sup>

### 4.13.1. Pin-to-Pin Performance (LVCMOS25)

Table 4.11. Pin-to-Pin Performance (LVCMOS25)

| Function        | Timing | Unit |

|-----------------|--------|------|

| Basic Functions |        |      |

| 16-bit decoder  | 16.5   | ns   |

| 4:1 MUX         | 18.0   | ns   |

| 16:1 MUX        | 19.5   | ns   |

### 4.13.2. Register-to-Register Performance

Table 4.12. Register-to-Register Performance

| Function                      | Timing | Unit |

|-------------------------------|--------|------|

| Basic Functions               |        |      |

| 16:1 MUX                      | 110    | MHz  |

| 16-bit adder                  | 100    | MHz  |

| 16-bit counter                | 100    | MHz  |

| 64-bit counter                | 40     | MHz  |

| Embedded Memory Functions     |        |      |

| 256 x 16 Pseudo-Dual Port RAM | 150    | MHz  |

#### Notes:

- The above timing numbers are generated using the iCECube2 design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

- Using a V<sub>CC</sub> of 1.14 V at Junction Temp 85 °C.

FPGA-DS-02043-1.8

## 4.14. Derating Logic Timing

Logic timing provided in the following sections of the data sheet and the Lattice design tools are worst case numbers in the operating range. Actual delays may be much faster. Lattice design tools can provide logic timing numbers at a particular temperature and voltage.

## 4.15. Maximum sysI/O Buffer Performance

Table 4.13. Maximum sysI/O Buffer Performance

| I/O Standard | Max Speed | Unit |

|--------------|-----------|------|

| Inputs       |           |      |

| LVCMOS33     | 250       | MHz  |

| LVCMOS25     | 250       | MHz  |

| LVCMOS18     | 250       | MHz  |

| Outputs      |           |      |

| LVCMOS33     | 250       | MHz  |

| LVCMOS25     | 250       | MHz  |

| LVCMOS18     | 155       | MHz  |

Note: Measured with a toggling pattern.

## 4.16. iCE40LM Family Timing Adders

Over recommended commercial operating conditions.

Table 4.14. iCE40LM Family Timing Adders

| Buffer Type      | Description Timing (Typ)               |       |     |  |

|------------------|----------------------------------------|-------|-----|--|

| Input Adjusters  |                                        |       |     |  |

| LVCMOS33         | LVCMOS, V <sub>CCIO</sub> = 3.3 V      | 0.18  | nS  |  |

| LVCMOS25         | LVCMOS, V <sub>CCIO</sub> = 2.5 V      | 0.00  | MHz |  |

| LVCMOS18         | LVCMOS, V <sub>CCIO</sub> = 1.8 V 0.19 |       |     |  |

| Output Adjusters |                                        |       |     |  |

| LVCMOS33         | LVCMOS, V <sub>CCIO</sub> = 3.3 V      | -0.12 | MHz |  |

| LVCMOS25         | LVCMOS, V <sub>CCIO</sub> = 2.5 V 0.00 |       |     |  |

| LVCMOS18         | LVCMOS, V <sub>CCIO</sub> = 1.8 V      | 1.32  | MHz |  |

#### Notes:

- Timing adders are relative to LVCMOS25 and characterized but not tested on every device.

- LVCMOS timing measured with the load specified in Table 4.19.

- Commercial timing numbers are shown.

## 4.17. iCE40LM External Switching Characteristics

Over recommended commercial operating conditions.

Table 4.15. iCE40LM External Switching Characteristics

| Parameter              | Description                                                | Device                                          |      |      | Unit |

|------------------------|------------------------------------------------------------|-------------------------------------------------|------|------|------|

| Clocks                 |                                                            | •                                               |      |      |      |

| Global Clocks          |                                                            |                                                 |      |      |      |

| f <sub>MAX_GBUF</sub>  | Frequency for Global Buffer Clock network                  | All devices                                     | _    | 185  | MHz  |

| t <sub>W_GBUF</sub>    | Clock Pulse Width for Global Buffer                        | Clock Pulse Width for Global Buffer All devices |      |      |      |

| t <sub>SKEW_GBUF</sub> | Global Buffer Clock Skew Within a Device                   | All devices                                     | _    | 650  | ps   |

| Pin-LUT-Pin Propa      | ngation Delay                                              | •                                               |      |      |      |

| t <sub>PD</sub>        | Best case propagation delay through one LUT logic          | All devices                                     | _    | 9.1  | ns   |

| General I/O Pin Pa     | arameters (Using Global Buffer Clock without PLL)*         |                                                 |      |      |      |

| t <sub>SKEW_IO</sub>   | Data bus skew across a bank of I/Os                        | All devices                                     | _    | 450  | ps   |

| t <sub>co</sub>        | Clock to Output - PIO Output Register All devices          |                                                 |      | 11.5 | ns   |

| t <sub>SU</sub>        | Clock to Data Setup - PIO Input Register All devices -0.23 |                                                 |      |      | ns   |

| t <sub>H</sub>         | Clock to Data Holdp - PIO Input Register                   | All devices                                     | 5.55 | _    | ns   |

<sup>\*</sup>Note: 25-pin WLCSP package does not support PLL.

## 4.18. sysCLOCK PLL Timing - Preliminary

Over recommended operating conditions.

Table 4.16. sysCLOCK PLL Timing – Preliminary

| Parameter                           | Description                                       | Condition                   | Min  | Max  | Unit   |

|-------------------------------------|---------------------------------------------------|-----------------------------|------|------|--------|

| f <sub>IN</sub>                     | Input Clock Frequency (REFERENCECLK, EXTFEEDBACK) | _                           | 10   | 133  | MHz    |

| f <sub>OUT</sub>                    | Output Clock Frequency (PLLOUT)                   |                             | 16   | 275  | MHz    |

| f <sub>VCO</sub>                    | PLL VCO Frequency                                 | _                           | 533  | 1066 | MHz    |

| f <sub>PFD</sub>                    | Phase Detector Input Frequency                    | _                           | 10   | 133  | MHz    |

| AC Character                        | istics                                            |                             | •    | •    |        |

| t <sub>DT</sub>                     | Output Clock Duty Cycle                           | _                           | 40   | 60   | %      |

| t <sub>PH</sub>                     | Output Phase Accuracy                             | _                           | _    | ±12  | deg    |

|                                     | Output Clask Bariad litter                        | f <sub>OUT</sub> <= 100 MHz | _    | 450  | ps p-p |

| Output Clock Period Jitte           | Output Clock Period Jitter                        | f <sub>OUT</sub> > 100 MHz  | _    | 0.05 | UIPP   |

| . 156                               | Output Clock Cycle-to-Cycle Jitter                | f <sub>OUT</sub> <= 100 MHz | _    | 750  | ps p-p |

| topjit <sup>1, 5, 6</sup>           | Output Clock Cycle-to-Cycle Jitter                | f <sub>OUT</sub> > 100 MHz  | _    | 0.10 | UIPP   |

|                                     | Output Clock Phase Jitter                         | f <sub>PFD</sub> <= 25 MHz  | _    | 275  | ps p-p |

|                                     | Output Clock Fliase sitter                        | f <sub>PFD</sub> >c` 25 MHz | _    | 0.05 | UIPP   |

| tw                                  | Output Clock Pulse Width                          | At 90% or 10%               | 1.33 | _    | ns     |

| t <sub>LOCK</sub> <sup>2, 3</sup>   | PLL Lock-in Time                                  | _                           | _    | 50   | μs     |

| tunlock                             | PLL Unlock Time                                   | _                           | _    | 50   | ns     |

|                                     | Locate Clark Barried litter                       | f <sub>PFD</sub> ≥ 20 MHz   | _    | 1000 | ps p-p |

| t <sub>IPJIT</sub> 4                | Input Clock Period Jitter                         | f <sub>PFD</sub> < 20 MHz   | _    | 0.02 | UIPP   |

| t <sub>FDTAP</sub>                  | Fine Delay adjustment, per Tap                    | _                           | 98   | 226  | ps     |

| t <sub>STABLE</sub> <sup>3</sup>    | LATCHINPUTVALUE LOW to PLL Stable                 | _                           | _    | 500  | ns     |

| t <sub>STABLE_PW</sub> <sup>3</sup> | LATCHINPUTVALUE Pulse Width                       | _                           | 100  | _    | ns     |

FPGA-DS-02043-1.8 25

| Parameter               | Description              | Condition | Min | Max | Unit       |

|-------------------------|--------------------------|-----------|-----|-----|------------|

| t <sub>RST</sub>        | RESET Pulse Width        | _         | 10  | _   | ns         |

| t <sub>RSTREC</sub>     | RESET Recovery Time      | _         | 10  | _   | μs         |

| t <sub>DYNAMIC_WD</sub> | DYNAMICDELAY Pulse Width | _         | 100 | _   | VCO Cycles |

#### Notes:

- Period jitter sample is taken over 10,000 samples of the primary PLL output with a clean reference clock. Cycle-to-cycle jitter is taken over 1000 cycles. Phase jitter is taken over 2000 cycles. All values per JESD65B.

- 2. Output clock is valid after tLOCK for PLL reset and dynamic delay adjustment.

- 3. At minimum f<sub>PFD</sub>. As the f<sub>PFD</sub> increases the time decreases to approximately 60% the value listed.

- 4. Maximum limit to prevent PLL unlock from occurring. Does not imply the PLL will operate within the output specifications listed in this table.

- 5. The jitter values increase with loading of the PLD fabric and in the presence of SSO noise.

- PLL jitter and lock time measurements are based on an external clean clock source. With different clock source, these values maybe different.

## 4.19. SPI Master Configuration Time

**Table 4.17. SPI Master Configuration Time**

| Symbol              | Parameter                         | Condition                             | Max | Unit |

|---------------------|-----------------------------------|---------------------------------------|-----|------|

|                     |                                   | All devices – Low Frequency (Default) | 95  | ms   |

| t <sub>CONFIG</sub> | POR/CRESET_B to Device I/O Active | All devices – Medium frequency        | 35  | ms   |

|                     |                                   | All devices – High frequency          | 18  | ms   |

Note: Assumes sysMEM Block is initialized to an all zero pattern, if they are used.

## 4.20. sysCONFIG Port Timing Specifications

**Table 4.18. sysCONFIG Port Timing Specifications**

| Symbol                                                                                                                                                                                                         | Parameter                                                                                             | Conditions                    | Min  | Тур | Max | Unit            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------|------|-----|-----|-----------------|

| All Configura                                                                                                                                                                                                  | ation Mode                                                                                            |                               |      |     |     |                 |

| t <sub>CRESET_B</sub>                                                                                                                                                                                          | Minimum CRESET_B LOW pulse width required to restart configuration, from falling edge to rising edge. | _                             | 200  | _   | _   | ns              |