## **FUNCTIONAL DESCRIPTION**

The VSC8115 contains an on-chip phase locked-loop (PLL) consisting of a phase/frequency detector (PFD), a loop filter using one external capacitor, an LC-based voltage-controlled oscillator (VCO), and a programmable frequency divider. The PFD compares the phase relationship between the VCO output and an external 19.44 MHz LVTTL reference clock to make coarse adjustments to the VCO block so that its output is held within ±500 ppm of the reference clock. The PFD also compares the phase relationship between the VCO output and the serial data input to make fine adjustments to the VCO block. The loop filter converts the phase detector output into a smooth DC voltage. This DC voltage is used as the input to the VCO block whose output frequency is a function of the input voltage. The VCO output signal is fed into a programmable frequency divider that generates either a 622.08 Mbps signal if STS12 is HIGH, or a 155.52 Mbps signal if STS12 is LOW, back to the PFD.

### **Lock Detection**

The VSC8115 features a lock detection for the PLL. The lock detect (LOCKDET) output goes HIGH to indicate that the PLL is locked to the serial data inputs and that valid data and clock are present at the high-speed differential outputs. If LOCKDET output is LOW, then either the PLL is forced to lock to the REFCLK input or the VCO has drifted away from the local reference clock by more than 500 ppm.

LOCKDET requires that the reference clock be present to operate properly.

## **Signal Detection**

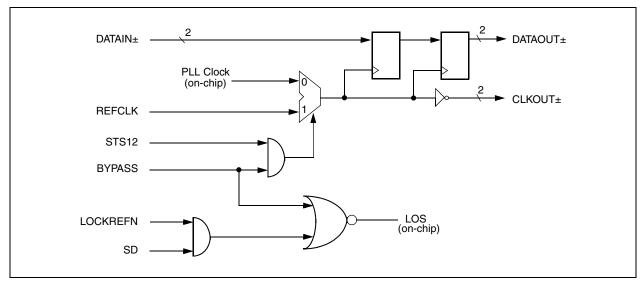

The VSC8115 has a signal detect (SD) input and a lock-to-reference (LOCKREFN) input. The SD pin is a LVPECL input and the LOCKREFN pin is a LVTTL input. These two control pins are used to indicate an LOS condition and are connected inside the part as shown in Figure 1 on page 3. If either one of these two inputs goes LOW and BYPASS is LOW, the VSC8115 will enter a Loss of Signal (LOS) state, and will hold the DATAOUT± output at logic LOW state. During the LOS state, the VSC8115 will also hold the output clock CLKOUT± to within ±500 ppm of the REFCLK. See Table 1 on page 3.

Most optical modules have an SD output. This SD output indicates that there is sufficient optical power and is typically active HIGH. If the SD output on the optical module is LVPECL, it should be connected directly to the SD input on the VSC8115, and the LOCKREFN input be tied HIGH. If the SD output is LVTTL, it should be connected directly to the LOCKREFN input, and the SD input should be tied HIGH.

The SD and LOCKREFN inputs also can be used for other applications when it is required to hold the CLKOUT± output to within ±500 ppm of the reference clock and to force the DATAOUT± output to the logic LOW state.

### Reference Clock

Upon powering up the VSC8115, it is recommended that the reference clock be present at least 40 bit times before the data signal is introduced.

# **PLL Bypass Operation**

The BYPASS pin is intended for use in production test and should be set at logic LOW in normal operation. If both BYPASS and STS12 pins are set at logic HIGH, the VSC8115 will bypass the PLL and present an inverted version of the REFCLK to the clock output CLKOUT±. The REFCLK's rising edge is used to capture data at DATAIN± and transmit data at DATAOUT±. This bypass operation can be used to facilitate the board debugging process.

Figure 1. Control Diagram for Signal Detection and PLL Bypass Operation

Table 1. Signal Detect and PLL Bypass Operation Control

| STS12 | BYPASS | LOCKREFN | SD | DATAOUT     | CLKOUT      |

|-------|--------|----------|----|-------------|-------------|

| 1     | 0      | 1        | 1  | DATAIN      | PLL clock   |

| 1     | 0      | 1        | 0  | LOW         | PLL clock   |

| 1     | 0      | 0        | 1  | LOW         | PLL clock   |

| 1     | 0      | 0        | 0  | LOW         | PLL clock   |

| 1     | 1      | Х        | Х  | DATAIN      | REFCLK      |

| 0     | 0      | 1        | 1  | DATAIN      | PLL clock   |

| 0     | 0      | 1        | 0  | LOW         | PLL clock   |

| 0     | 0      | 0        | 1  | LOW         | PLL clock   |

| 0     | 0      | 0        | 0  | LOW         | PLL clock   |

| 0     | 1      | Х        | Х  | Not allowed | Not allowed |

# **ELECTRICAL SPECIFICATIONS**

### **DC Characteristics**

Guaranteed over recommended operating conditions listed in Table 8 on page 5.

Table 2. LVPECL Single-Ended Inputs and Outputs

| Symbol          | Parameter                                | Minimum                 | Maximum                | Unit | Condition                         |

|-----------------|------------------------------------------|-------------------------|------------------------|------|-----------------------------------|

| V <sub>IH</sub> | Input HIGH voltage                       | V <sub>DD</sub> – 1.125 | V <sub>DD</sub> – 0.5  | V    | Guaranteed input HIGH voltage     |

| V <sub>IL</sub> | Input LOW voltage                        | V <sub>DD</sub> – 2.0   | V <sub>DD</sub> – 1.5  | V    | Guaranteed input LOW voltage      |

| I <sub>IH</sub> | Input HIGH current                       | -0.5                    | 10                     | μΑ   | $V_{IN} = V_{DD} - 0.5 V$         |

| I <sub>IL</sub> | Input LOW current                        | -0.5                    | 10                     | μΑ   | $V_{IN} = V_{DD} - 2.0 \text{ V}$ |

| V <sub>OL</sub> | Output LOW voltage V <sub>DD</sub> - 2.0 |                         | V <sub>DD</sub> – 1.8  | V    | 50Ω to (V <sub>DD</sub> – 2.0 V)  |

| V <sub>OH</sub> | Output HIGH voltage                      | V <sub>DD</sub> – 1.25  | V <sub>DD</sub> – 0.67 | ٧    | 50Ω to (V <sub>DD</sub> – 2.0 V)  |

### **Table 3. LVPECL Differential Inputs**

| Symbol          | Parameter                  | Minimum                | Maximum               | Unit | Condition                       |

|-----------------|----------------------------|------------------------|-----------------------|------|---------------------------------|

| V <sub>IH</sub> | Input HIGH voltage         | V <sub>DD</sub> – 1.75 | $V_{DD} - 0.4$        | V    | Guaranteed input HIGH voltage   |

| V <sub>IL</sub> | Input LOW voltage          | V <sub>DD</sub> – 2.0  | V <sub>DD</sub> – 0.7 | V    | Guaranteed input LOW voltage    |

| $\Delta V_{IN}$ | Differential input voltage | 250                    |                       | mV   |                                 |

| I <sub>IH</sub> | Input HIGH current         | -0.5                   | 10                    | μА   | $\Delta V_{IN} = 0.5 \text{ V}$ |

| I <sub>IL</sub> | Input LOW current          | -0.5                   | 10                    | μΑ   | $\Delta V_{IN} = 0.5 \text{ V}$ |

### **Table 4. LVDS Differential Outputs**

| Symbol            | Parameter                     | Minimum | Typical | Maximum | Unit | Condition |

|-------------------|-------------------------------|---------|---------|---------|------|-----------|

| V <sub>OCM</sub>  | Output common-mode voltage    | 1.0     | 1.35    | 1.7     | V    |           |

| ΔV <sub>OUT</sub> | OUT Differential output swing |         |         | 1700    | mV   |           |

### **Table 5. LVPECL Differential Outputs**

| Symbol           | Parameter                  | Minimum | Typical | Maximum | Unit | Condition                                |

|------------------|----------------------------|---------|---------|---------|------|------------------------------------------|

| V <sub>OCM</sub> | Output Common-Mode Voltage | 0.8     | 1.35    | 1.7     | V    | 50 $\Omega$ to (V <sub>DD</sub> – 2.0 V) |

| $\Delta V_{OUT}$ | Differential Output Swing  | 800     |         | 1700    | mV   | 50 Ω to (V <sub>DD</sub> – 2.0 V)        |

### Table 6. LVTTL Inputs

| Symbol          | Parameter          | Minimum | Maximum  | Unit | Condition                                          |

|-----------------|--------------------|---------|----------|------|----------------------------------------------------|

| V <sub>IH</sub> | Input HIGH voltage | 2.0     | $V_{DD}$ | ٧    |                                                    |

| V <sub>IL</sub> | Input LOW voltage  | 0       | 0.8      | ٧    |                                                    |

| I <sub>IH</sub> | Input HIGH current | -50     | 50       | μΑ   | $V_{IN} = 2.75 \text{ V}, V_{DD} = \text{maximum}$ |

| I <sub>IL</sub> | Input LOW current  | -50     | 50       | μΑ   | V <sub>IN</sub> = 0.5 V, V <sub>DD</sub> = maximum |

### **Table 7. Power Supply Requirements**

| Symbol          | Parameter                                 | Minimum | Typical | Maximum | Unit | Condition            |

|-----------------|-------------------------------------------|---------|---------|---------|------|----------------------|

| I <sub>DD</sub> | Power supply current from V <sub>DD</sub> |         | 57      | 80      | mA   | Outputs unterminated |

| P <sub>D</sub>  | Power dissipation                         |         | 188.1   | 277     | mW   | Outputs unterminated |

# **Operating Conditions**

**Table 8. Recommended Operating Conditions**

| Symbol   | Parameter                                                                                | Minimum         | Typical | Maximum        | Unit           |

|----------|------------------------------------------------------------------------------------------|-----------------|---------|----------------|----------------|

| $V_{DD}$ | Power supply voltage                                                                     | 3.135           | 3.3     | 3.465          | V              |

| Т        | Operating temperature under bias <sup>(1)</sup> VSC8115, VSC8115-T VSC8115-02 VSC8115-03 | 0<br>-40<br>-20 |         | 70<br>85<br>85 | °C<br>°C<br>°C |

<sup>1.</sup> Lower limit of specification is ambient temperature, and upper limit is case temperature.

# **Maximum Ratings**

**Table 9. Absolute Maximum Ratings**

| Symbol           | Parameter                                         | Minimum | Maximum               | Unit |

|------------------|---------------------------------------------------|---------|-----------------------|------|

| $V_{DD}$         | Power supply voltage, referenced to GND           | -0.5    | 4.0                   | V    |

|                  | DC input voltage (LVPECL, LVTTL)                  | -0.5    | V <sub>DD</sub> + 0.5 | V    |

|                  | Output current (LVDS or LVPECL)                   | +50     | -50                   |      |

| T <sub>S</sub>   | Storage temperature                               | -65     | 150                   | °C   |

| V <sub>ESD</sub> | Electrostatic discharge voltage, human body model | -750    | 750                   | V    |

Stresses listed under Absolute Maximum Ratings may be applied to devices one at a time without causing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

#### **ELECTROSTATIC DISCHARGE**

This device can be damaged by ESD. Vitesse recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures may adversely affect reliability of the device.

**VITESSE**

### **AC Characteristics**

Guaranteed over recommended operating conditions listed in Table 8 on page 5.

**Table 10. Performance Specifications**

| Symbol                    | Parameter                                      | Minimum | Typical | Maximum                                        | Unit              | Condition                                                          |

|---------------------------|------------------------------------------------|---------|---------|------------------------------------------------|-------------------|--------------------------------------------------------------------|

| f                         | VCO center frequency                           |         | 622.08  |                                                | MHz               |                                                                    |

| f <sub>TOL</sub>          | CRU's reference clock frequency tolerance      | -250    |         | 250                                            | ppm               |                                                                    |

| fT <sub>REF_CLK</sub>     | _CLK OC-12/STS-12 capture range ±500 ppm       |         | ppm     | With respect to the fixed reference frequency. |                   |                                                                    |

| CLKOUT <sub>DC</sub>      | Clock output duty cycle                        | 45      |         | 55                                             | % of UI           | 20% minimum transition density.                                    |

| t <sub>LOCK</sub>         | OC-12/STS-12 acquistion lock time              |         |         | 16                                             | μs                | Valid REFCLK and device already powered up.                        |

| tLOCKDET_R,<br>tLOCKDET_F | LVDS and LVPECL output rise time and fall time |         |         | 500                                            | ps                | 10% to 90%, with 100 $\Omega$ and 5 pF capacitive equivalent load. |

| J <sub>GEN_CLK</sub>      | CLKOUT± jitter generation                      |         | 0.005   | 0.01                                           | UI <sub>rms</sub> |                                                                    |

| J <sub>TOL</sub>          | OC-12/STS-12 jitter tolerance                  | 0.45    |         |                                                | UI                | Sinusoidal input jitter of DATAIN± from 250 kHz to 5 MHz.          |

### **Jitter Tolerance**

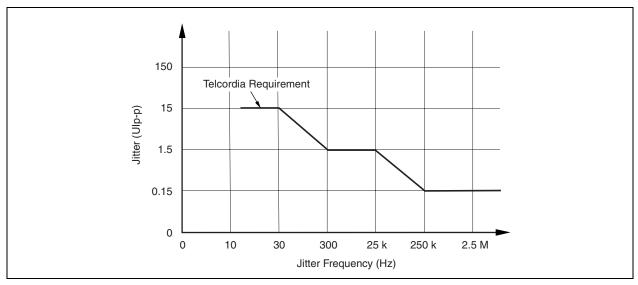

Jitter tolerance is the ability of the CDR to track timing variations in the received data stream. The Telecordia and ITU specifications allow the received optical data to contain jitter; however, the amount that must be tolerated is a function of the frequency of the jitter. At high frequencies, the specifications do not require the VSC8115 to tolerate large amounts of jitter, whereas, at low frequencies, many unit intervals (bit times) of jitter have to be tolerated. The VSC8115 tolerates this jitter with margin over the specification limits. See Figure 2. The VSC8115 obtains and maintains lock based on the data transition information. When there is no transition on the data stream, the recovered clock frequency is held to within ±500 ppm of the reference clock. The VSC8115 maintains lock status with a data stream carrying over 1,000 consecutive identical digits (CID).

Figure 2. Input Jitter Tolerance Specification

### **Jitter Generation**

Maximum jitter generation is 0.01 UI within the SONET/SDH band when rms jitter of less than 14 ps (OC-12) or 56 ps (OC-3) is presented to the serial data inputs.

### **Retimed Data and Clock Outputs**

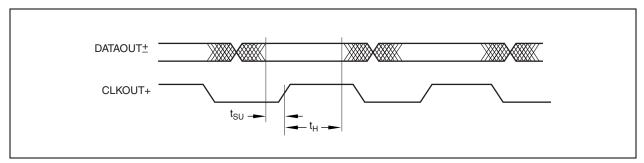

It is recommended that the retimed data output be captured with the rising edge of the clock output as shown in Figure 3. Data valid time is longer for OC-3/STS-3 mode of operation than that of OC-12/STS-12. Data valid time before the output clock's rising edge is the available setup time ( $t_{SU}$ ), while the data valid time after the clock's rising edge is the available hold time ( $t_{H}$ ).

Figure 3. Retimed Data and Clock Outputs Timing Diagram

Table 11. Retimed Data and Clock Outputs Timing

| Symbol          | Parameter            | Minimum | Maximum | Unit | Condition                     |

|-----------------|----------------------|---------|---------|------|-------------------------------|

| t <sub>SU</sub> | Available setup time | 450     |         | ps   | STS-12 operation (622.08 MHz) |

|                 |                      | 2.0     |         | ns   | STS-3 operation (155.52 MHz)  |

| t <sub>H</sub>  | Available hold time  | 650     |         | ps   | STS-12 operation (622.08 MHz) |

|                 |                      | 3.0     |         | ns   | STS-3 operation (155.52 MHz)  |

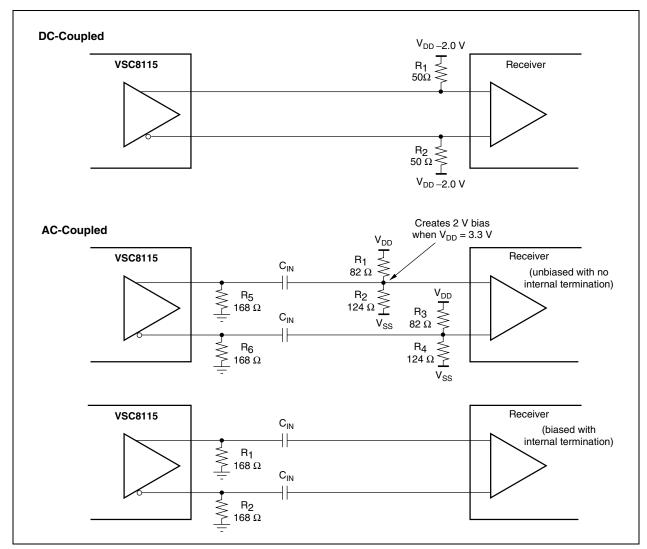

### **High-Speed Outputs**

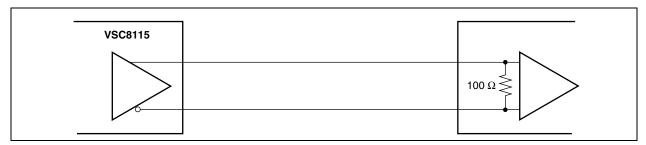

The high-speed output buffers, DATAOUT $\pm$  and CLKOUT $\pm$ , can be terminated as either LVDS or LVPECL outputs. If used as LVDS outputs, the transmission lines should be routed with 100  $\Omega$  differential impedance and terminated at the receive end with a 100 $\Omega$  resistor across the differential pair. If used as LVPECL outputs, the transmission line should be 50  $\Omega$  terminated, with 50  $\Omega$  pull-down resistors near the receiving end. See Figure 4 and Figure 5.

Figure 4. High-Speed Outputs, LVDS Termination

Figure 5. High-Speed Outputs, LVPECL Terminations

# **PACKAGE INFORMATION**

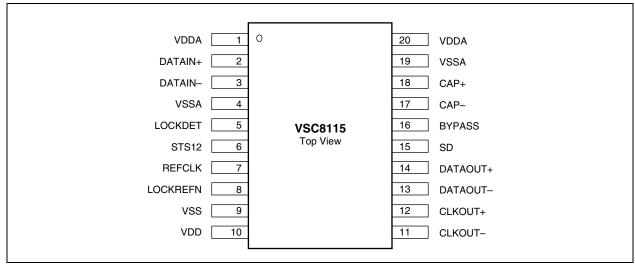

# Pin Diagram

Figure 6. Pin Diagram

## **Pin Identifications**

Table 12. Pin Identifications

| Pin | Signal   | I/O | Туре      | Description                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDDA     |     | Pwr       | 3.3 V power supply for high-speed I/Os and on-chip PLL blocks.                                                                                                                                                                                                                                                                                                 |

| 2   | DATAIN+  | I   | LVDS/PECL | Receive data input, true. The high-speed output clock (CLKOUT±) is recovered from this high-speed differential input data.                                                                                                                                                                                                                                     |

| 3   | DATAIN-  | I   | LVDS/PECL | Receive data input, complement. The high-speed output clock (CLKOUT±) is recovered from this high-speed differential input data.                                                                                                                                                                                                                               |

| 4   | VSSA     |     | Power     | Ground pin for low-speed I/Os and on-chip digital PLL blocks.                                                                                                                                                                                                                                                                                                  |

| 5   | LOCKDET  | 0   | LVPECL    | Active HIGH to indicate that the PLL is locked to serial data input and valid clock and data are present at the serial outputs (DATAOUT± and CLKOUT±). The LOCKDET will go inactive under the following conditions:  • If SD is set LOW  • If LOCKREFN is set LOW  • If the VCO has drifted away from the local reference clock, REFCLK, by more than 500 ppm. |

| 6   | STS12    | I   | LVTTL     | STS-12 or STS-3 mode selection. Set HIGH to select the STS-12 operation. Set LOW to select the STS-3 operation.                                                                                                                                                                                                                                                |

| 7   | REFCLK   | I   | LVTTL     | Local reference clock input for the CRU, 19.44 MHz. REFCLK is used for the PLL phase adjustment during power up. It also serves as a stable clock source in the absence of serial input data.                                                                                                                                                                  |

| 8   | LOCKREFN | I   | LVTTL     | Lock to REFCLK input. When set LOW, this pin holds the CLKOUT± output to within ±500 ppm of the REFCLK input and forces the DATAOUT± output to the LOW state.                                                                                                                                                                                                  |

| 9   | VSS      |     | Power     | Ground pin for low-speed I/Os and on-chip digital CMOS blocks.                                                                                                                                                                                                                                                                                                 |

| 10  | VDD      |     | Power     | 3.3 V power supply for low-speed I/Os and on-chip digital CMOS blocks.                                                                                                                                                                                                                                                                                         |

**VITESSE**

Table 12. Pin Identifications (continued)

| Pin | Signal   | I/O | Туре        | Description                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | CLKOUT-  | 0   | LVDS/LVPECL | High-speed clock output, complement. This clock is recovered from the receive data input (DATAIN±) and supports either LVDS or LVPECL.                                                                                                                                                                                                                     |

| 12  | CLKOUT+  | 0   | LVDS/LVPECL | High-speed clock output, true. This clock is recovered from the receive data input (DATAIN±) and supports either LVDS or LVPECL.                                                                                                                                                                                                                           |

| 13  | DATAOUT- | 0   | LVDS/LVPECL | High-speed data output, complement. This is the retimed version of the receive data input (DATAIN±) and supports either LVDS or LVPECL.                                                                                                                                                                                                                    |

| 14  | DATAOUT+ | 0   | LVDS/LVPECL | High-speed data output, true. This is the retimed version of the receive data input (DATAIN±) and and supports either LVDS or LVPECL.                                                                                                                                                                                                                      |

| 15  | SD       | I   | LVPECL      | Signal detect. SD should be connected to the SD output on the optical module. SD is active HIGH. When SD is set HIGH, it means there is sufficient optical power. When SD is set LOW to indicate an LOS condition, the CLKOUT± output signal will be held to within +500 ppm of the RECLK input. Additionally, the DATAOUT± will be held in the LOW state. |

| 16  | BYPASS   | I   | LVTTL       | Used for production testing. Set to V <sub>SS</sub> for normal operation.                                                                                                                                                                                                                                                                                  |

| 17  | CAP-     | I   | Analog      | External loop filter input, complement. The loop filter capacitor should be connected to these pins. The capacitor value should be 1.0 $\mu$ F ±10%.                                                                                                                                                                                                       |

| 18  | CAP+     | I   | Analog      | External loop filter input, true. The loop filter capacitor should be connected to these pins. The capacitor value should be 1.0 $\mu$ F $\pm 10\%$ .                                                                                                                                                                                                      |

| 19  | VSSA     |     | Power       | Ground pin for low-speed I/Os and on-chip digital PLL blocks.                                                                                                                                                                                                                                                                                              |

| 20  | VDDA     |     | Power       | 3.3 V power supply for high-speed I/Os and on-chip PLL blocks.                                                                                                                                                                                                                                                                                             |

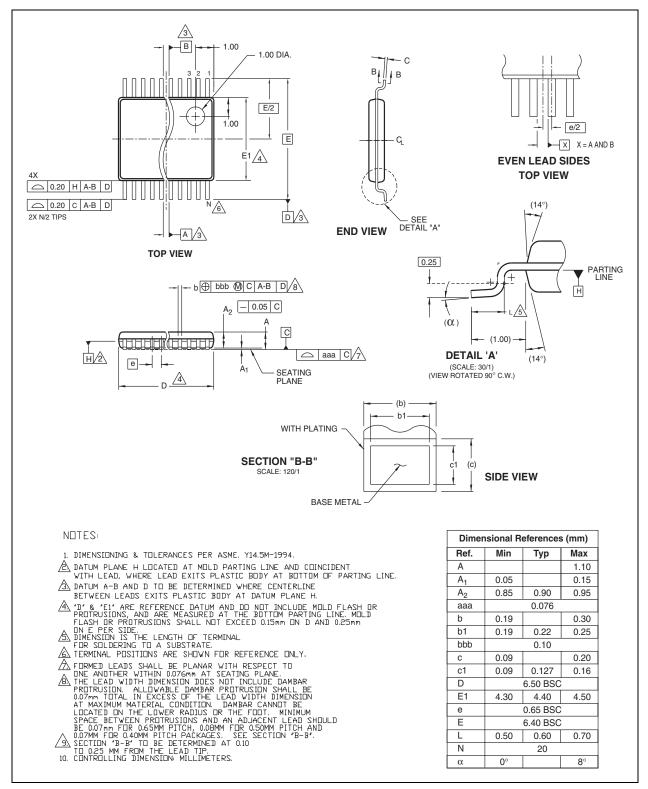

## **Package Drawing**

Figure 7. Package Drawing

■ 11 of 13 ■

## **Moisture Sensitivity Level**

This device is rated moisture sensitivity level 3 or better as specified in the joint IPC and JEDEC standard IPC/JEDEC J-STD-020. For more information, see the IPC and JEDEC standard.

# **ORDERING INFORMATION**

Lead-free products from Vitesse comply with the temperatures and profiles defined in the joint IPC and JEDEC standard IPC/JEDEC J-STD-020. For more information, see the IPC and JEDEC standard.

The following table lists the ordering information for the VSC8115 device.

### VSC8115 STS-12/STS-3 Multirate Clock and Data Recovery Unit

| Part Number     | Description                                                    |  |  |

|-----------------|----------------------------------------------------------------|--|--|

| VSC8115YA       | 20-pin TSSOP, 4.40 mm × 6.50 mm body                           |  |  |

|                 | Operating temperature: 0 °C ambient to 70 °C case              |  |  |

| VSC8115XYA      | Lead-free, 20-pin TSSOP, 4.40 mm × 6.50 mm body                |  |  |

|                 | Operating temperature: 0 °C ambient to 70 °C case              |  |  |

| VSC8115YA-T     | 20-pin TSSOP, 4.40 mm × 6.50 mm body, tape and reel            |  |  |

|                 | Operating temperature: 0 °C ambient to 70 °C case              |  |  |

| VSC8115XYA-T    | Lead-free, 20-pin TSSOP, 4.40 mm × 6.50 mm body, tape and reel |  |  |

|                 | Operating temperature: 0 °C ambient to 70 °C case              |  |  |

| VSC8115YA-02    | 20-pin TSSOP, 4.40 mm × 6.50 mm body                           |  |  |

|                 | Operating temperature under bias: -40 °C ambient to 85 °C case |  |  |

| VSC8115XYA-02   | Lead-free, 20-pin TSSOP, 4.40 mm × 6.50 mm body                |  |  |

|                 | Operating temperature under bias: -40 °C ambient to 85 °C case |  |  |

| VSC8115YA-02-T  | 20-pin TSSOP, 4.40 mm × 6.50 mm body, tape and reel            |  |  |

|                 | Operating temperature under bias: -40 °C ambient to 85 °C case |  |  |

| VSC8115XYA-02-T | Lead-free, 20-pin TSSOP, 4.40 mm × 6.50 mm body, tape and reel |  |  |

|                 | Operating temperature under bias: -40 °C ambient to 85 °C case |  |  |

| VSC8115YA-03    | 20-pin TSSOP, 4.40 mm × 6.50 mm body                           |  |  |

|                 | Operating temperature under bias: -20 °C ambient to 85 °C case |  |  |

| VSC8115XYA-03   | Lead-free, 20-pin TSSOP, 4.40 mm × 6.50 mm body                |  |  |

|                 | Operating temperature under bias: -20 °C ambient to 85 °C case |  |  |

| VSC8115YA-03-T  | 20-pin TSSOP, 4.40 mm × 6.50 mm body, tape and reel            |  |  |

|                 | Operating temperature under bias: -20 °C ambient to 85 °C case |  |  |

| VSC8115XYA-03-T | Lead-free, 20-pin TSSOP, 4.40 mm × 6.50 mm body, tape and reel |  |  |

|                 | Operating temperature under bias: -20 °C ambient to 85 °C case |  |  |

#### **CORPORATE HEADQUARTERS**

Vitesse Semiconductor Corporation 741 Calle Plano Camarillo, CA 93012 Tel: 1-800-VITESSE • FAX:1-(805) 987-5896

Copyright © 1999–2000, 2002–2005 by Vitesse Semiconductor Corporation

### PRINTED IN THE U.S.A

Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Vitesse for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Vitesse products are not intended for use in life support products where failure of a Vitesse product could reasonably be expected to result in death or personal injury. Anyone using a Vitesse product in such an application without express written consent of an officer of Vitesse does so at their own risk, and agrees to fully indemnify Vitesse for any damages that may result from such use or sale.

Vitesse Semiconductor Corporation is a registered trademark. All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

■ 13 of 13 ■

**VITESSE**