# **Vishay Semiconductors**

## CUT THE SPIKES WITH VCUT05D1-SD0

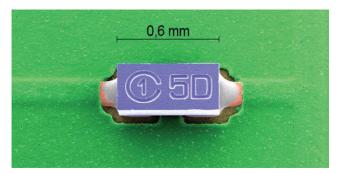

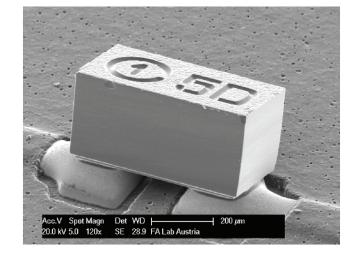

The VCUT05D1-SD0 is a Bidirectional and Symmetrical (BiSy) ESD-protection device which clamps positive and negative overvoltage transients to ground. Connected between the signal or data line and the ground the VCUT05D1-SD0 offers a high isolation (low leakage current, low capacitance) within the specified working range. Due to the short leads and small package size of the tiny CLP0603 package the line inductance is very low, so that fast transients like and ESD-strike can be clamped with minimal over- or undershoots.

| ELECTRICAL CHARACTERISTICS VCUT05D1-SD0<br>(T <sub>amb</sub> = 25 °C, unless otherwise specified) |                                                                                  |                      |      |      |      |       |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------|------|------|------|-------|

| PARAMETER                                                                                         | TEST CONDITIONS/REMARKS                                                          | SYMBOL               | MIN. | TYP. | MAX. | UNIT  |

| Protection paths                                                                                  | Number of lines which can be protected                                           | N <sub>channel</sub> | -    | -    | 1    | lines |

| Reverse stand-off voltage                                                                         | Max. reverse working voltage                                                     | V <sub>RWM</sub>     | -    | -    | 5.5  | V     |

| Reverse voltage                                                                                   | at I <sub>R</sub> = 0.1 μA                                                       | V <sub>R</sub>       | 5.5  | -    | -    | V     |

| Reverse current                                                                                   | at V <sub>RWM</sub> = 5.5 V                                                      | I <sub>R</sub>       | -    | -    | 0.1  | μA    |

| Reverse breakdown voltage                                                                         | at I <sub>R</sub> = 1 mA                                                         | V <sub>BR</sub>      | 6.5  | 8    | 9    | V     |

| Reverse clamping voltage                                                                          | at I <sub>PP</sub> = 1 A                                                         | V <sub>C</sub>       | -    | 8.8  | 10   | V     |

|                                                                                                   | at $I_{PP} = I_{PPM} = 6 A$                                                      | V <sub>C</sub>       | -    | 11   | 13   | V     |

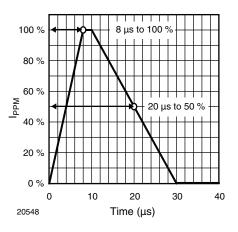

| Capacitance                                                                                       | at $V_R = 0 V$ ; f = 1 MHz                                                       | CD                   | -    | 13   | 14   | pF    |

|                                                                                                   | at V <sub>R</sub> = 2.5 V; f = 1 MHz                                             | CD                   | -    | 11   | -    | pF    |

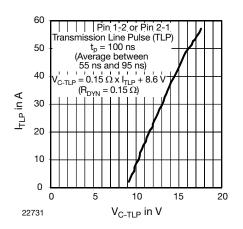

| Clamping voltage                                                                                  | Transmission Line Pulse (TLP); $t_p = 100 \text{ ns}$<br>$I_{TLP} = 8 \text{ A}$ | V <sub>C-TLP</sub>   | -    | 9.8  | -    | V     |

| Clamping voltage                                                                                  | Transmission Line Pulse (TLP); $t_p = 100$ ns $I_{TLP} = 16$ A                   | V <sub>C-TLP</sub>   | -    | 11   | -    | V     |

| Dynamic resistance                                                                                | resistance Transmission Line Pulse (TLP); t <sub>p</sub> = 100 ns                |                      | -    | 0.15 | -    | Ω     |

## TYPICAL CHARACTERISTICS (T<sub>amb</sub> = 25 °C, unless otherwise specified)

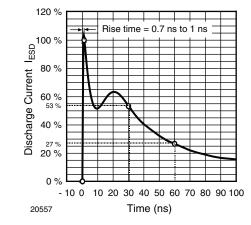

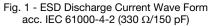

Fig. 2 - 8/20 µs Peak Pulse Current Wave Form acc. IEC 61000-4-5

# **Vishay Semiconductors**

www.vishay.com

Fig. 3 - Typical Capacitance C<sub>D</sub> vs. Reverse Voltage V<sub>R</sub>

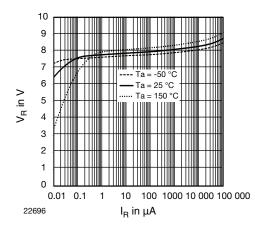

Fig. 4 - Typical Reverse Voltage  $V_R$  vs. Reverse Current  $I_R$

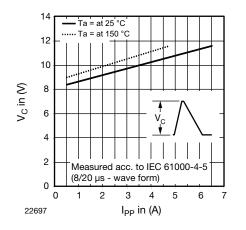

Fig. 5 - Typical Peak Clamping Voltage V<sub>C</sub> vs. Peak Pulse Current  $I_{PP}$

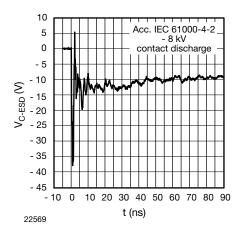

Fig. 6 - Typical Clamping Performance at 8 kV Contact Discharge acc. IEC 61000-4-2

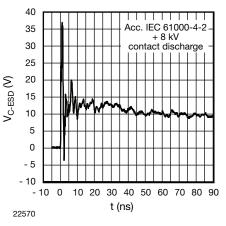

Fig. 7 - Typical Clamping Performance at 8 kV Contact Discharge acc. IEC 61000-4-2

Fig. 8 - Typical Clamping Voltage at 100 ns Transmission Line Pulse (TLP)

3

Document Number: 83443

For technical questions, contact: <u>ESDprotection@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

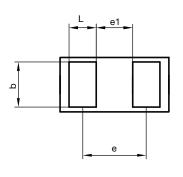

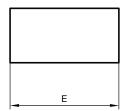

# PACKAGE DIMENSIONS in millimeters (mils): CLP0603-2L

www.vishay.com

VISHAY

|    | Millimeters |      | mils |       |       |       |

|----|-------------|------|------|-------|-------|-------|

|    | min.        | nom. | max. | min.  | nom.  | max.  |

| A  | 0.24        | 0.27 | 0.30 | 9.44  | 10.63 | 11.81 |

| A1 |             |      | 0.02 |       |       | 0.79  |

| b  | 0.22        | 0.25 | 0.28 | 8.66  | 9.84  | 11.02 |

| D  | 0.27        | 0.30 | 0.33 | 10.62 | 11.81 | 12.99 |

| E  | 0.57        | 0.60 | 0.63 | 22.44 | 23.62 | 24.80 |

| е  |             | 0.40 |      |       | 15.75 |       |

| e1 |             | 0.25 |      |       | 9.84  |       |

| L  | 0.12        | 0.15 | 0.18 | 4.72  | 5.91  | 7.09  |

Package = Chip dimensions in mm

D

A1

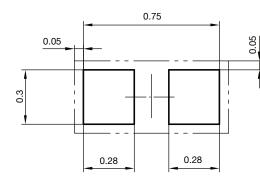

foot print recommendation:

#### 22606

2 terminal leadless package (CLP0603-2L) Document no.: S8-V-3906.04-023 (4) Created - Date: 22. Nov. 2010 Rev.3 - Date: 14. Sept. 2011

Rev. 1.3, 19-Nov-13

4

Document Number: 83443

For technical questions, contact: <u>ESDprotection@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

**Vishay Semiconductors**

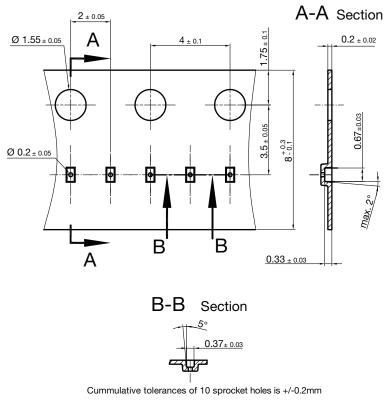

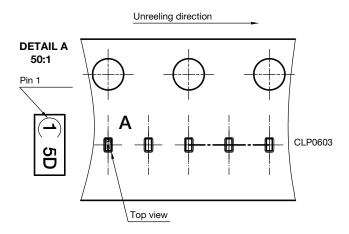

#### CARRIER TAPE in millimeters: CLP0603

22591 Document no. S8-V-3906.04-0025 (4) Created - Date: 22. Nov. 2010

## **ORIENTATION IN CARRIER CLP0603**

22607

Orientation in Carrier Tape (CLP0603) S8-V-3906.04-026 (4) 22.10.2010

5 For technical questions, contact: <u>ESDprotection@vishay.com</u>

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

# VCUT05D1-SD0

# **Vishay Semiconductors**

## **APPLICATION NOTE**

### **1. PCB FOOTPRINT DESIGN**

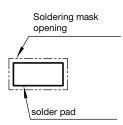

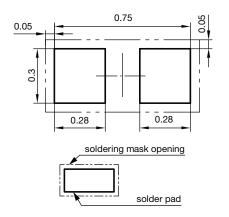

Verified by internal tests, Vishay recommends the soldering pad and solder mask opening design as shown in fig. 1. We recommend using a non-solder mask defined (NSMD) design, as shown below. The reason is that with a NSMD design, the size of the actual solder pad is more accurate (tolerances for copper etchings are smaller compared to a solder mask defined process).

Fig. 1 - Recommended Soldering Pad Design

#### 2. PCB SOLDERING PAD METALLIZATION

There are several common pad metallization/finishes, including OSP (Organic Solderability Protectant), HASL (Hot Air Solder Level), and ENiAu. Because of the CLP0603's extremely small size, Vishay only recommends using the electroless Ni/immersion gold over copper pad plating.

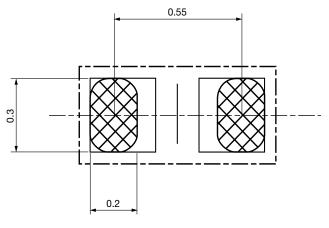

#### **3. SCREEN PRINT PROCESS**

The solder paste is applied to the PCB by using a screen print process. The recommended stencil thickness for the CLP0603 package is 80  $\mu$ m (the absolute maximum is 100  $\mu$ m). The recommended dimensions for the stencil openings are 12 mil (300  $\mu$ m) by 8 mil (200  $\mu$ m) for both pads. The side wall of the stencil openings should be tapered approximately 5 degrees. An electro-polished finish will support a better release of the paste.

Fig. 2 - Maximum Stencil Openings for a Stencil Thickness of 80 µm

Note

A wider stencil opening will result in a better solder paste release from the stencil. So the best quality can be obtained by using the optimum between the stencil quality, thickness, and opening.

If a tilting of the package is observed, the amount of solder paste should be reduced slightly. Please also take into consideration the direct relation between the amount of solder paste and the package shear strength.

#### 4. SOLDER PASTE TYPE

Type 4 solder pastes (or smaller powder sizes) are recommended. In our evaluation we used the Cookson Electronics' Alpha OM-338 CSP (96.5 % Sn/3 % Ag/0.5 % Cu) solder paste.

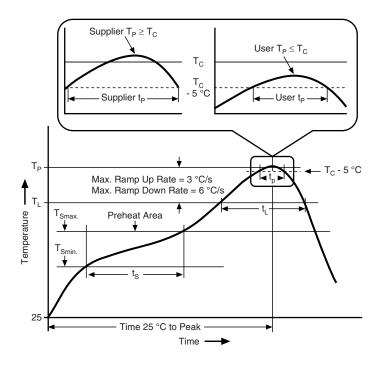

#### 5. REFLOW SOLDERING PROCESS

A standard surface-mount reflow soldering process can be used (reference: JPC/JEDEC J-STD-020D).

However, for an optimum process, recommendations from the solder paste supplier should be considered. Variations in chemistry and viscosity of the fluxer may require small adjustments to the soldering profile.

6 For technical questions, contact: <u>ESDprotection@vishay.com</u>

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

# VCUT05D1-SD0

| TABLE 1 - CLASSIFICATION REFLOW PROFILES                                                                              |                                                   |                                           |  |  |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------|--|--|

| PROFILE FEATURE                                                                                                       | SnPb EUTECTIC ASSEMBLY                            | LEAD (Pb)-FREE ASSEMBLY                   |  |  |

| PREHEAT AND SOAK                                                                                                      |                                                   |                                           |  |  |

| Temperature min. (T <sub>Smin.</sub> )                                                                                | 100 °C                                            | 150 °C                                    |  |  |

| Temperature max. (T <sub>Smax.</sub> )                                                                                | 150 °C                                            | 200 °C                                    |  |  |

| Time (T <sub>Smin.</sub> to T <sub>Smax.</sub> ) (t <sub>S</sub> )                                                    | 60 s to 120 s                                     | 60 s to 120 s                             |  |  |

| Average ramp-up rate (T <sub>Smax.</sub> to T <sub>p</sub> )                                                          | 3 °C/s maximum                                    |                                           |  |  |

| Liquidous temperature (T <sub>L</sub> )                                                                               | uidous temperature (T <sub>L</sub> ) 183 °C 217 ° |                                           |  |  |

| Time to liquidous (t <sub>L</sub> )                                                                                   | 60 s to 150 s                                     | 60 s to 150 s                             |  |  |

| Peak package temperature (T <sub>p</sub> ) <sup>(1)</sup>                                                             | See classification temperature in table 3         | See classification temperature in table 4 |  |  |

| Time (t <sub>p</sub> ) $^{(2)}$ with 5 °C of the specified classification temperature (T <sub>C</sub> ) 20 s $^{(2)}$ |                                                   | 30 s <sup>(2)</sup>                       |  |  |

| Average ramp-down rate (T <sub>p</sub> to T <sub>Smax.</sub> )                                                        | 6 °C/s maximum                                    |                                           |  |  |

| Time 25 °C to peak temperature                                                                                        | 6 min maximum 8 min maximum                       |                                           |  |  |

#### Notes

- <sup>(1)</sup> Tolerance for peak profile temperature (T<sub>p</sub>) is defined as a supplier minimum and user maximum

- $^{(2)}$  Tolerance for time at peak profile temperature (T<sub>p</sub>) is defined as a supplier minimum and user maximum

#### Notes

- 1. All temperatures refer to the center of the package, measured on the package body surface that is facing up during assembly reflow (e.g. live-bug). If parts are reflowed in other than the normal live-bug assembly reflow orientation (i.e. dead-bug). T<sub>p</sub> shall be within ± 2 °C of the live-bug T<sub>p</sub> and still meet the T<sub>C</sub> requirements, otherwise, the profile shall be adjusted to achieve the latter. To accurately measure actual peak package body temperatures refer to JEP140 for the recommended thermocouple use.

- 2. Reflow profiles in this document are for classification/preconditioning and are not meant to specify board assembly profiles. Actual board assembly profiles should be developed based on specific process needs and board designs and should not exceed the parameters in table 1. For example, if T<sub>C</sub> is 260 °C and time t<sub>p</sub> is 30 s, this means the following for the supplier and the user:

- For a supplier: The peak temperature must be at least 260 °C. The time above 255 °C must be at least 30 s.

- For a user: The peak temperature must not exceed 260 °C. The time above 255 °C must not exceed 30 s.

- 3. All components in the test load shall meet the classification profile requirements.

- 4. SMD packages classified to a given moisture sensitivity level by using procedures or criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), IPC-SM-786 (rescinded) do not need to be reclassified to the current revision unless a change in classification level or a higher peak classification temperature is desired.

Rev. 1.3, 19-Nov-13

7

Document Number: 83443

For technical questions, contact: ESDprotection@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

www.vishay.com

# **Vishay Semiconductors**

| TABLE 2 - SnPb EUTECTIC PROCESS - CLASSIFICATION TEMPERATURES (T <sub>c</sub> ) |                                 |                                 |  |  |

|---------------------------------------------------------------------------------|---------------------------------|---------------------------------|--|--|

| PACKAGE THICKNESS                                                               | VOLUME mm <sup>3</sup><br>< 350 | VOLUME mm <sup>3</sup><br>≥ 350 |  |  |

| < 2.5 mm                                                                        | 235 °C                          | 220 °C                          |  |  |

| ≥ 2.5 mm                                                                        | 220 °C                          | 220 °C                          |  |  |

| TABLE 3 - LEAD (Pb)-FREE PROCESS - CLASSIFICATION TEMPERATURES (T <sub>C</sub> ) |                                 |                                       |                                  |  |

|----------------------------------------------------------------------------------|---------------------------------|---------------------------------------|----------------------------------|--|

| PACKAGE THICKNESS                                                                | VOLUME mm <sup>3</sup><br>< 350 | VOLUME mm <sup>3</sup><br>350 to 2000 | VOLUME mm <sup>3</sup><br>> 2000 |  |

| < 1.6 mm                                                                         | 260 °C                          | 260 °C                                | 260 °C                           |  |

| 1.6 mm to 2.5 mm                                                                 | 260 °C                          | 250 °C                                | 245 °C                           |  |

| > 2.5 mm                                                                         | 250 °C                          | 245 °C                                | 245 °C                           |  |

Notes

5. At the direction of the device manufacturer, but not the board assembler/user, the maximum peak package body temperature ( $T_p$ ) can exceed the values specified in tables 2 and 3. The use of a higher  $T_p$  does not change the classification temperature ( $T_c$ ).

6. Package volume excludes external terminals (e.g., balls, bumps, lands, leads) and/or nonintegral heat sinks.

- 7. The maximum component temperature reached during reflow depends on package thickness and volume. The use on convection reflow processes reduces the thermal gradients between packages. However thermal gradients due to differences in thermal mass of SMD packages may still exist.

- 8. Moisture sensitivity levels of components intended for use in a lead (Pb)-free assembly process shall be evaluated using the lead (Pb)-free classification temperatures and profiles defined in table 1 and 3, whether or not lead (Pb)-free.

- 9. SMD packages classified to a given moisture sensitivity level by using procedures or criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), IPC-SM-786 (rescinded) do not need to be reclassified to the current revision unless a change in classification level or a higher peak classification temperature is desired.

## 6. SOLDERING QUALITY INISPECTION

An X-ray inspection system is required to find defects such as shorts between pads, open contacts, and voids within the solder. In addition, a visual inspection by microscope or camera (of appropriate magnification) can be used to inspect the sides of the solder joints for acceptable shape and molten solder.

### 7. SHEAR TEST COMPARISON

The data below shows a comparison of shear strength after a reflow soldering process.

9. INTERCHANGEABILITY OF THE CLP WITH A

Based on our studies, the CLP is 100 % compatible with

PLASTIC PACKAGE OF THE SAME SIZE

plastic packages of the same size.

|                        | VISHAY | COMPETITOR 1 | COMPETITOR 2 | COMPETITOR 3 |

|------------------------|--------|--------------|--------------|--------------|

| Typical shear strength | 500 g  | 350 g        | 600 g        | 440 g        |

## 8. REWORK PROCEDURE

For rework, the CLP0603 package must be removed from the PCB if there is any issue with the solder joints. Standard SMT rework systems are recommended for this. Due to the small size of the package, the rework system should be equipped with a proper magnification aid.

#### Rev. 1.3, 19-Nov-13

8

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

Vishay

# Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.