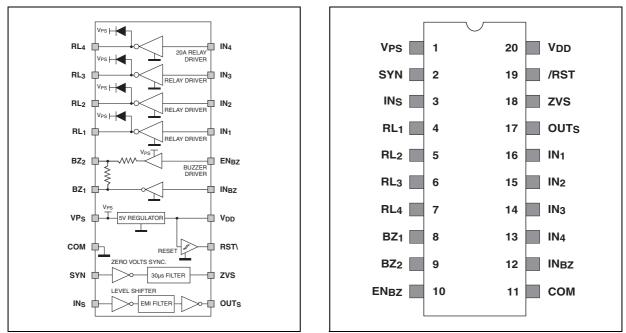

**Figure 3. Pin-out connections**

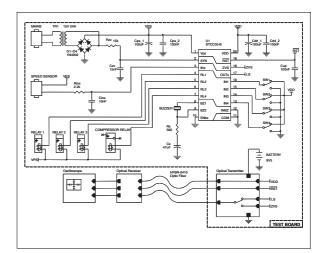

Figure 2. Block diagram

## FUNCTIONAL DESCRIPTION

The STCC05 is a control circuit embedding most of the analog & power circuitry of an air conditioner or refrigirator control module. It interfaces the micro-controller MCU with the AC power and cooling process sections.

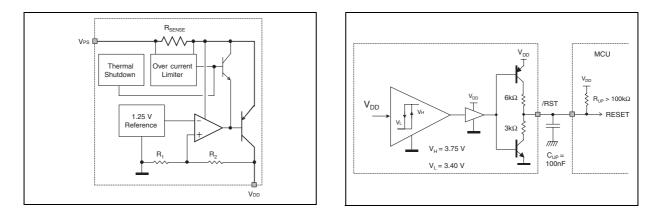

## The voltage supply

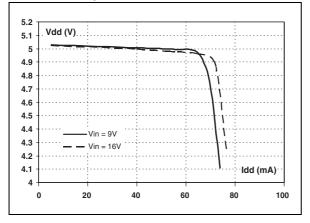

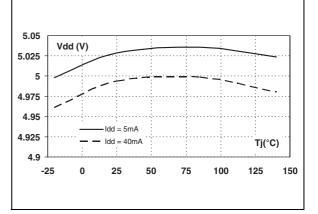

The 5V voltage regulator supplies the micro-controller MCU. Its input voltage ranges from 7V to 18V; and its average DC output current up to 50mA. With an output filtering capacitor of 100µF, its output voltage accuracy is better than +/- 5% in the whole operating range of the ambient temperature  $T_{AMB}$ , the load current I<sub>DD</sub> and the input voltage V<sub>PS</sub>, contributing directly to the ADC accuracy.

The regulator includes also an over current limiter and a thermal shutdown. The over current limiter protects the regulator against output short circuits and inrush currents during the power up. The current limiter is made of a serial shunt resistance as current sensor and a circuit that regulates the input current. Moreover, the thermal shutdown protects the whole circuit against overload operations. It is made of a thermal sensing junction and a hysteresis comparator that is able to switch off the passing element.

<u>ل</u>حک

2/13

## The reset circuit

This circuit ensures a Low Voltage Detection (LVD) of the output of the regulator. Most micro-controllers have an active RESET pin in the low state: so, the /RST pin will be active at low state.

The reset comparator senses the regulator voltage V<sub>DD</sub>. The /RST pin goes high when V<sub>DD</sub> is higher than the high threshold  $V_H = 3.75V$  and after a delay time T<sub>UP</sub>; and is low when the V<sub>DD</sub> decreases below the low threshold  $V_L = 3.4V$  after the delay time T<sub>DW</sub>.

These delays are set by an external capacitor  $C_{UP}$  connected to the /RST pin and depend on the trigger thresholds of /RST: For  $C_{UP}$  = 100nF,  $T_{UP}$ = 400µs with  $V_{TH}$ =  $V_H/2$ ;  $T_{DW}$ = 200µs with  $V_{TH}$ =  $V_L/2$ .

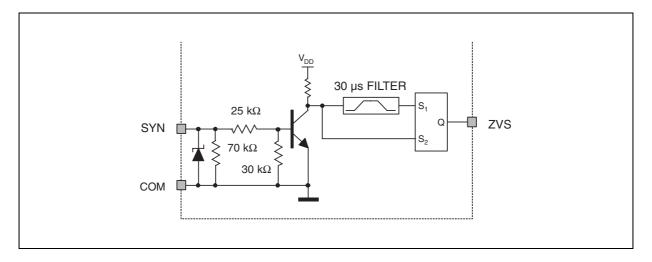

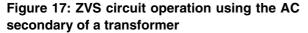

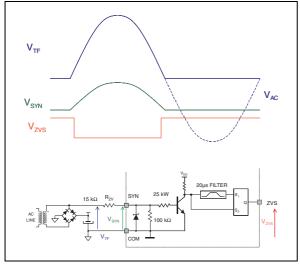

#### The Zero Voltage Synchronization ZVS circuit

The Zero Voltage Synchronization ZVS circuit generates the signal ZVS that synchronizes the whole operation with the AC line cycle (20 ms on 50 Hz or 16.7 ms on 60 Hz). This signal allows the MCU to control the AC loads and achieve the timing functions.

The input pin SYN is an image of the mains voltage. It is connected to either the power supply transformer through a resistor  $R_{ZV}$  or an opto-coupler that is controlled directly by the AC line voltage. The circuit is protected against fast line transient voltages: a robust ESD protection and a 30µs digital filter are implemented to provide a higher immunity to the MCU operation. Its output signal ZVS is inverted respect to the input signal V<sub>SYN</sub>.

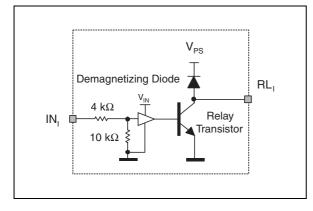

#### The relay coil drivers

These robust circuits allow a DC relay coil to be driven by an MCU output. The relay coil has a minimum resistance of  $580\Omega$  and has a power up to 0.25W for V<sub>PS</sub> = 12 V. These characteristics are representative of 3A relays such as FTR-F3AA-12V or JQ1A-12V series.

The output stage is made of a transistor and a demagnetization diode. The transistor is referred to the ground COM, has a DC current rating of 50mA; and its collector is connected to the output  $RL_I$  (I=1, 2, 3). The diode is connected between the output pin  $RL_I$  and the supply pin  $V_{PS}$ .

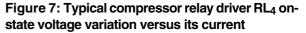

Moreover, a fourth coil driver has an extended 150mA current capability to be able to drive the coil of a relay having a  $130\Omega$  minimum resistance and a 1.1W maximum power. These characteristics are representative of 20A relays such as G4A-E-DC12, OMIF-S-112 or UKH12S series.

Á7/

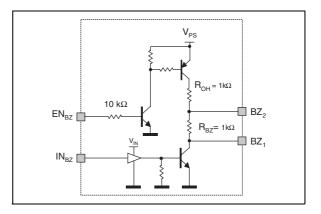

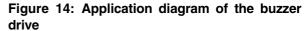

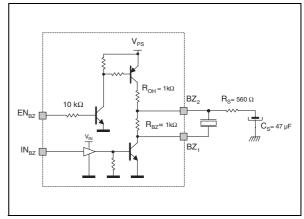

## The buzzer driver with enable control

The MCU can excite a warning buzzer with a 50% PWM signal. The buzzer driver amplifies this signal in current and translates it from the 5V MCU output to the  $V_{PS}$  supply to produce the right sound level from the buzzer.

The output stage is made of a NPN transistor, a PNP transistor and two  $1k\Omega$  resistors.

The NPN transistor, referred to the power ground COM, is controlled by the input  $IN_{BZ}$ ; its collector is connected to the output  $BZ_1$ . The input  $IN_{BZ}$  is driven by a simple push-pull MCU buffer.

The PNP transistor, referred to the V<sub>PS</sub> polarity, is controlled by the input  $EN_{BZ}$ ; and its collector is connected to the output BZ<sub>2</sub> through a 1k $\Omega$  resistor. The input  $EN_{BZ}$  is driven by a simple push-pull MCU buffer.

The pin BZ<sub>2</sub> is the supply terminal of the buzzer; and the circuit has a DC current rating of 9mA and the PWM section runs from 10Hz up to 5kHz.

A 1k $\Omega$  resistor R<sub>BZ</sub> is connected between the BZ<sub>1</sub> and BZ<sub>2</sub> pins to discharge the buzzer periodically. Moreover, the addition of an external capacitor-resistor network on BZ<sub>2</sub> pin will allow the buzzer to turn on and off smoothly when the pin EN<sub>BZ</sub> is toggling.

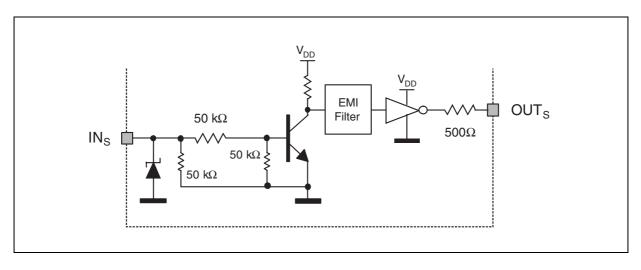

#### The speed sensor level shifter

The  $OUT_S$  signal is generated by an electronic signal such as the indoor fan speed clock issued of a Hall Effect sensor or a door switch signal and is transmitted to the MCU. As the IN<sub>S</sub> input may be disturbed; a spike suppressor and a simple EMI filter are added to increase the input robustness. The output signal OUT<sub>S</sub> is not inverted with respect to the input signal IN<sub>S</sub>.

4/13

| Symbol             | Pin Parameter name & conditions                     |                                                                                                                  | Value                             | Unit |

|--------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|

| V <sub>DD</sub>    | V <sub>DD</sub>                                     | Output supply voltage                                                                                            | - 0.3 to 6                        | V    |

| V <sub>PS</sub>    | V <sub>PS</sub> , IN <sub>S</sub>                   | Power supply voltage, level shifter input                                                                        | - 0.3 to 20                       | V    |

| V <sub>SYN</sub>   | SYN                                                 | ZVS input voltage, $R_{ZV} = 15k\Omega$                                                                          | - 1 to 20                         | V    |

| V <sub>MO</sub>    | $BZ_1, BZ_2,$<br>RL <sub>x</sub> , x = 1 to 4       | Output voltage                                                                                                   | - 0.3 to<br>V <sub>PS</sub> + 0.3 | V    |

| VI                 | IN <sub>1</sub> , IN <sub>2</sub> , IN <sub>3</sub> | Input logic voltage                                                                                              | - 0.3 to<br>V <sub>DD</sub> + 0.3 | V    |

| Vo                 | ZVS, OUT <sub>S</sub> , /RST                        | Output logic voltage                                                                                             | - 0.3 to<br>V <sub>DD</sub> + 0.3 | V    |

|                    | V <sub>PS</sub>                                     | V <sub>PS</sub> Maximum sourced current pulse, tp = 10ms                                                         |                                   | mA   |

|                    | $RL_x$ , x = 1 to 3                                 | Maximum sunk driver current pulse, tp = 10ms                                                                     | 60                                | mA   |

| IM                 |                                                     | Maximum DC sunk current                                                                                          | 50                                | mA   |

| IM                 | RL <sub>4</sub>                                     | Maximum sunk driver current pulse, tp = 10ms                                                                     | 160                               | mA   |

|                    | 11-4                                                | Maximum DC sunk current                                                                                          | 150                               | mA   |

|                    | $RL_{x}, x = 1 \text{ to } 4$                       | Maximum diver diode reverse current                                                                              | 1                                 | mA   |

| I <sub>BZ AV</sub> | BZ <sub>1</sub> , BZ <sub>2</sub>                   | Average output current                                                                                           | ± 2                               | mA   |

| I <sub>BZ PK</sub> | BZ <sub>1</sub> , BZ <sub>2</sub>                   | Peak output current, tp = 50µs                                                                                   | ± 50                              | mA   |

| ΣΙ                 | $RL_x$ , I = 1 to 4                                 | Maximum DC sunk current in all relay drivers $V_{PS} = 16V$ , $T_{AMB} = 70^{\circ}$ C, $I_{DD} = 50$ mA, DIP-20 | 220                               | mA   |

| ΣI <sub>M</sub>    | Γι= χ, Ι = Ι ΙΟ 4                                   | Maximum DC sunk current in all relay drivers $V_{PS} = 16V$ , $T_{AMB} = 85^{\circ}C$ , $I_{DD} = 25mA$ , DIP-20 | 300                               | ШA   |

| P <sub>DIS</sub>   | All                                                 | Maximum dissipation, DIP-20, T <sub>AMB</sub> = 70°C                                                             | 0.90                              | W    |

| T <sub>AMB</sub>   | All                                                 | Operating ambient temperature                                                                                    | - 20 to 85                        | °C   |

| ТJ                 | All                                                 | Operating junction temperature                                                                                   | - 10 to 150                       | °C   |

| ١J                 |                                                     | Storage junction temperature                                                                                     | - 25 to 150                       | °C   |

## Table 2: Absolute Ratings (limiting values)

## Table 3: Electromagnetic Compatibility Ratings

$(T_J = 25^{\circ}C)$ , according to typical application diagram of page 1, unless otherwise specified)

| Symbol           | Node                              | Parameter name & conditions                                          | Value | Unit |

|------------------|-----------------------------------|----------------------------------------------------------------------|-------|------|

| V <sub>ESD</sub> | All pins                          | ESD protection, MIL-STD 883 method 3015, HBM model                   | ± 2   |      |

| V <sub>ESD</sub> | IN <sub>S</sub> , SYN,            |                                                                      |       | kV   |

|                  | V <sub>PS</sub> , V <sub>DD</sub> | ESD protection, IEC 61000-4-2, per intput, in contact <sup>(1)</sup> | ± 2   | ΝV   |

| V <sub>PPB</sub> | All pins                          | Total peak pulse voltage Burst, IEC 61000-4-4, (2)                   | ± 4   |      |

**Note 1:** System oriented test circuit with  $R_{ZV} = 15k\Omega$ ,  $R_{INS} = 2.2k\Omega$  and  $C_{DD} = C_{PS} = 100nF$ **Note 2:** System oriented test circuit; refer to application section

#### Table 4: Thermal Resistance

| Symbol               | Parameter                                                                      |    | Unit |

|----------------------|--------------------------------------------------------------------------------|----|------|

| D                    | DIP-20 thermal resistance junction to ambient                                  | 00 | °C/W |

| R <sub>th(j-a)</sub> | Single PCB with a copper thickness = $35\mu m$ and surface $S_{CU} = 0.5 cm^2$ | 90 | C/vv |

## STCC05-B

| Symbol               | Pin                  | I Characteristics (T <sub>J</sub> = 25°)<br>Name    | Conditions                                                                                                                                                        | Min.                | Тур   | Max.                | Unit |

|----------------------|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|---------------------|------|

| Cymbol               |                      |                                                     | oltage supply                                                                                                                                                     |                     | 1 y P | max.                |      |

|                      |                      |                                                     | $I_{DD} = 5$ to 40mA                                                                                                                                              |                     |       | [ ]                 |      |

| V <sub>DD</sub>      | V <sub>DD</sub>      | Output voltage supply                               |                                                                                                                                                                   | 4.75                | 5     | 5.25                | V    |

| V <sub>PS</sub>      | V <sub>PS</sub>      | Input supply voltage                                |                                                                                                                                                                   | 7                   |       | 18                  | V    |

| I <sub>SQ</sub>      | V <sub>PS</sub>      | Quiescent supply current                            | $V_{DD} = 5V, I_{DD} = 0$ (open)                                                                                                                                  |                     | 1.3   | 2                   | mA   |

| I <sub>IN_SC</sub>   | V <sub>PS</sub>      | Limiting input current                              | V <sub>DD</sub> = 0V<br>Output in short circuit                                                                                                                   | 50                  | 80    | 120                 | mA   |

| T <sub>OFF</sub>     | V <sub>DD</sub>      | Shutdown temperature                                |                                                                                                                                                                   |                     | 170   |                     | °C   |

| $\Delta T$           | V                    | Releasing thermal hysteresis                        |                                                                                                                                                                   |                     | 15    |                     | °C   |

|                      |                      |                                                     | Reset circuit                                                                                                                                                     |                     |       |                     |      |

| V <sub>H</sub>       |                      | Disabling reset threshold                           |                                                                                                                                                                   | 3.4                 | 3.75  | 4                   |      |

| VL                   | V <sub>DD</sub>      | Enabling reset threshold                            |                                                                                                                                                                   | 3.1                 | 3.4   | 3.6                 | V    |

| V <sub>HYS</sub>     |                      | Threshold hysteresis                                |                                                                                                                                                                   |                     | 0.35  |                     |      |

| T <sub>UP</sub>      |                      | Disabling reset delay time                          | $C_{UP} = 100 nF, V_{TH} = V_H/2, R_{UP} = 100 k\Omega$                                                                                                           | 200                 | 400   | 800                 |      |

| $T_DW$               | /RST                 | Enabling reset delay time                           | $\begin{array}{l} C_{UP} = 100 n F,  V_{TH} = V_L/2, \\ R_{UP} = 100 k \Omega \end{array}$                                                                        | 100                 | 200   | 400                 | μs   |

|                      |                      | Zero Voltage                                        | synchronization circuit                                                                                                                                           |                     |       |                     |      |

| TD                   | ZVS                  | Transition filtering time                           | Rising and falling step                                                                                                                                           | 10                  | 30    | 70                  | μs   |

| V <sub>TH</sub>      | SYN                  | Transition threshold                                |                                                                                                                                                                   | 0.6                 | 1.1   | 1.4                 | V    |

| I <sub>SYN</sub> SYN | 0)(1)                |                                                     | V <sub>SYN</sub> = 5V                                                                                                                                             |                     | 0.3   |                     |      |

|                      | SYN                  | Input nominal current                               | V <sub>SYN</sub> = 18V                                                                                                                                            |                     | 0.9   | 1.5                 | mA   |

|                      |                      | Level shifter, zero volta                           | age synchronization, rese                                                                                                                                         | t circuits          |       |                     |      |

| VOH                  | LVOUT                | High level output voltage                           |                                                                                                                                                                   | $0.8  V_{DD}$       |       |                     | V    |

| V <sub>OL</sub>      | /RST<br>ZVS          | Low level output voltage                            |                                                                                                                                                                   |                     |       | 0.2 V <sub>DD</sub> | V    |

|                      |                      | Re                                                  | lay coil drivers                                                                                                                                                  |                     |       |                     |      |

| I <sub>IN4</sub>     | IN <sub>4</sub>      | Input activating current                            | $V_{IN4} = 5V$                                                                                                                                                    |                     | 0.85  | 1.4                 | mA   |

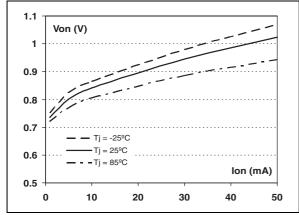

| Von                  | RL <sub>4</sub>      | On state output voltage                             | I <sub>ON</sub> = 150mA, V <sub>IN4</sub> > 3.1V                                                                                                                  |                     | 1     | 1.2                 | V    |

| I <sub>INx</sub>     | IN <sub>1 to 3</sub> | Input activating current                            | $V_{INx} = 5V$                                                                                                                                                    |                     | 0.85  | 1.4                 | mA   |

| Von                  |                      | On state output voltage                             | $I_{ON} = 50 \text{mA}, V_{INx} > 3.1 \text{V}$                                                                                                                   |                     | 1     | 1.2                 | V    |

| V <sub>RL H</sub>    | RL <sub>1 to 4</sub> | Off state output voltage                            | $V_{INx} < 50.8V, R_{L} = 580\Omega$                                                                                                                              | 0.9 V <sub>PS</sub> |       | V <sub>PS</sub>     | V    |

| VINx                 | IN <sub>1 to 4</sub> | Transition threshold                                |                                                                                                                                                                   | 0.8                 | 1.9   | 3.1                 | V    |

|                      |                      | Buzzer driv                                         | er with enable control                                                                                                                                            | II                  |       |                     |      |

| V <sub>INBZ</sub>    | INI                  | Input muting voltage                                |                                                                                                                                                                   | 0.8                 | 1.5   | 3.1                 | V    |

| F <sub>BUZ</sub>     | IN <sub>BZ</sub>     | Buzzer PWM frequency                                | Duty cycle = 50%                                                                                                                                                  | 0.01                |       | 5                   | kHz  |

| R <sub>OH</sub>      | BZ <sub>2</sub>      | On state output resistance                          | $V_{INBZ} = 0V, V_{ENBZ} > 3.1V,$<br>$I_{BZ2} = 5mA$                                                                                                              |                     | 1     |                     | kΩ   |

| V <sub>ON</sub>      | BZ <sub>1</sub>      | On state output voltage                             | $\label{eq:ION} \begin{array}{l} I_{ON} = 25 \text{mA}, \ V_{\text{INBZ}} > 3.1 \text{V}, \\ V_{\text{ENBZ}} = 0 \text{V}, \ t_{p} = 50 \mu \text{s} \end{array}$ |                     | 1     | 1.4                 | V    |

| V <sub>ENBZ</sub>    | EN <sub>BZ</sub>     | Enable threshold voltage                            |                                                                                                                                                                   | 0.8                 | 2     | 3.1                 | V    |

| R <sub>BZ</sub>      |                      | BZ <sub>1</sub> - BZ <sub>2</sub> Buzzer resistance |                                                                                                                                                                   |                     | 1     |                     | kΩ   |

|                      |                      | Speed s                                             | ensor level shifter                                                                                                                                               |                     |       |                     |      |

| V <sub>INS H</sub>   |                      | High level detection                                |                                                                                                                                                                   | 7                   |       | 18                  | V    |

| VINS L               | INS                  | Low level detection                                 |                                                                                                                                                                   |                     |       | 0.8                 | V    |

| I <sub>INS</sub>     | 1                    | Internal input current                              | V <sub>INS</sub> = 12V                                                                                                                                            |                     | 500   | 800                 | μA   |

|                      |                      | 1                                                   |                                                                                                                                                                   |                     |       |                     |      |

**Table 5: Electrical Characteristics** ( $T_1 = 25^{\circ}C$ ,  $V_{CC} = 12V$  unless otherwise specified)

### **DC CHARACTERISTICS**

Figure 4: Typical regulator voltage  $V_{DD}$  variation versus its output current  $I_{DD}$  at  $T_J = 25^{\circ}C$

## Figure 6: Typical relay driver $R_{L (1 \text{ to } 3)}$ onstate voltage variation versus its current

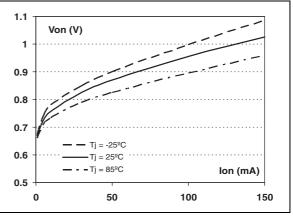

#### AIR CONDITIONER APPLICATION CONSIDERATIONS

## ■ IMMUNITY IMPROVEMENT OF STCC05 AND THE MICROCONTROLLER

Some basic rules can be applied to improve the STCC05 immunity in its application:

- The power ground of V<sub>PS</sub> should be split from the signal ground of V<sub>DD</sub>,

- The STCC05 is placed as close as possible of the MCU,

- The supply capacitors would increase the system immunity by being placed closed to the blocks they feed, (3) or putting decoupling capacitors (f.i.  $C_{DD} = C_{PS} = 100$ nF)

- Large supply wire on the PCB should be avoided to reduce sensitivity to radiated interferences.

- A decoupling capacitor can be put on the pin  $IN_S$  of the speed sensor interface and the MCU reset pin (4) (f.i.  $C_{INS} = 10nF$ ;  $C_{UP} = 100nF$ ).

Depending of the PCB layout quality, others capacitors may be put on sensitive pins such as the output regulator pin  $V_{DD}$  and the zero crossing synchronization input pin SYN.

(1)

(2)

Downloaded from Arrow.com.

## STCC05-B

#### Figure 8: Example of PCB layout improvement for higher immunity

## ■ STCC05 ELECTROMAGNETIC COMPATIBILITY

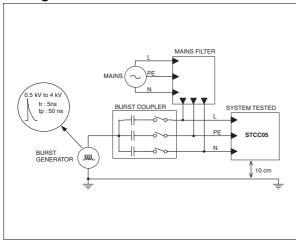

Standards such as IEC61000-4-x evaluate the electromagnetic compatibility of appliance systems. To test the immunity level of the STCC05 to the IEC61000-4-4 (Electrical Fast Transient Bursts), a board representative of usual application control unit should be considered by applying the immunity design rules defined in the previous paragraph.

IEC61000-4-4 test does not allow any measurement equipment to be connected to the tested system, as it would corrupt the test results. That is why this board should include a remote monitoring circuit based on optic fibers. Thus, without any electrical link with an oscilloscope, it is possible to monitor the  $V_{DD}$  voltage as well as the /RST or the ZVS outputs of the STCC05, during the IEC61000-4-4 test. This optical link detects parasitic commutations of outputs as short as 60ns.

With this board, and the burst generator coupled to the mains as specified in the IEC61000-4-4 standard (see the following principle diagram), the STCC05 has been tested successfully at 4kV.

## Figure 9: IEC61000-4-4 Electrical Fast Transient Burst general STCC05 test circuit

#### Figure 10: Test circuit schematic

<u>ل</u>حک

## ■ STCC05 POWER PERFORMANCE VERSUS ITS THERMAL CAPABILITY

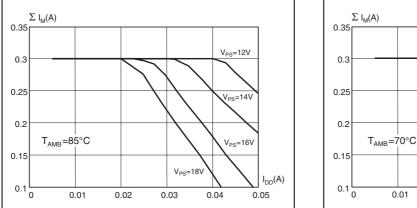

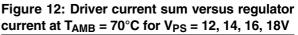

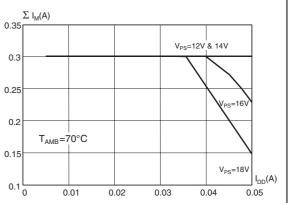

Figure 11: Driver current sum versus regulator current at  $T_{AMB} = 85^{\circ}$ C for  $V_{PS} = 12, 14, 16, 18V$

The main heat sources of the circuit during operation are the voltage regulator and the relay coil drivers. Depending of the power supply voltage  $V_{PS}$ , the ambient temperature  $T_{AMB}$ , and the thermal of resistance of the package  $R_{th(j-a)}$ , the sum of all the coil driver currents  $\Sigma I_M$  is linked to the output regulator current  $I_{DD}$ . In order to avoid spurious thermal shutdown of the system, it is advised to respect this relationship as shown on figures 7 and 8.

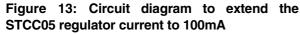

## EXTENSION OF THE REGULATOR CURRENT CAPABILITY

The output current capability of the STCC05 voltage regulator can be increased in a cost effective manner by adding an external ballast transistor and two biasing resistors. With such a circuit, the output voltage regulation remains at 5V 5%, and the current limitation is still active.

Such a topology generates also power losses in the external power transistor especially when the supply voltage  $V_{PS}$  is high or the regulator is in current limiting mode. Therefore it is advised to use a package with a suitable thermal resistance ( $R_{th j-a}$ ).

An example is proposed in the following figure doubling the regulator current capability of the solution to 100mA while producing a current limitation typically at 110mA.

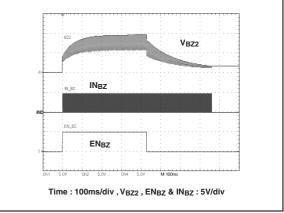

#### FLOATING BUZZER OPERATION

The sound produced by the buzzer is controlled by the frequency of the square signal applied to the  $\ensuremath{\mathsf{IN}_{\mathsf{BZ}}}$  input pin.

The external  $R_S C_S$  network connected to the  $BZ_2$  output pin produces a soft sound by smoothing the buzzer supplying envelope at power up and power down. Contrary to basic drivers, which directly apply

| 57 |

|----|

|    |

the voltage to the buzzer, this circuit feeds the buzzer with the exponential voltage induced by the charge and the discharge of the  $R_S C_S$  network.

The  $R_{OH}$  and  $R_S$  resistors contribute to reduce high harmonic sound distortions. Indeed, they limit the peak current through the buzzer, feed the buzzer with the  $C_S$  capacitor voltage, and limit the current through the low side NPN transistor of the driver.

Therefore to set rising/falling durations of the sound shape, it is advised to adjust only the value of the C<sub>S</sub> capacitor.

The integrated  $R_{BZ}$  resistor is selected to discharge the buzzer when the low side transistor is off, especially at the maximum operating frequency. The buzzer is completely discharged within five times the time constant of the resistor-buzzer with  $\tau = R_{BZ} \times C_{BUZZER}$ .

Therefore,  $R_{BZ} < 1 / (10 \text{ x } F_{MAX} \text{ x } C_{BUZZER})$ . Since the buzzer capacitance  $C_{BUZZER}$  is about 20nF at the maximum operating frequency of driver is 5kHz, this  $R_{BZ}$  resistance is set at 1k $\Omega$ .

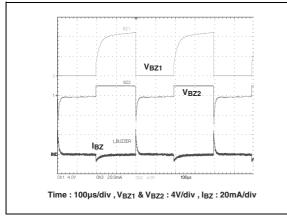

# Figure 15: Buzzer terminal voltages $V_{BZ1}$ & $V_{BZ2}$ and buzzer current $I_{BZ}$

## ZERO CROSSING DETECTION CIRCUITS

The detection of the zero crossing of the AC line voltage can be achieved at least on two ways with the STCC05, depending of the power supply unit.

When the power supply uses a magnetic 50/60Hz transformer, the input pin SYN is connected to a transformer output through a resistor  $R_{ZV}$ , the electrical path being closed by the low side bridge diodes.

10/13

The delay between the real Zero Crossing event and the falling edge of ZVS depends on the internal filtering time, the resistance R<sub>ZV</sub>, the rectifier drop voltage V<sub>F</sub>, the V<sub>PS</sub> supply load and the temperature. The STCC05 contribution to this delay can be evaluated by measuring the delay between its input voltage V<sub>TF</sub> and its output voltage V<sub>ZVS</sub>. When using V<sub>F</sub> = 0.8V, R<sub>ZV</sub> = 15k $\Omega$ , V<sub>PS</sub> = 15V, I<sub>CC</sub> = 20mA, it is about 50 µs on rising voltage V<sub>TF</sub> and 115 µs on falling voltage V<sub>TF</sub>.

When the power supply uses a switch mode power supply, the input pin SYN is synchronized by an opto-coupler, which is connected to the mains terminals through high resistances. The isolator output is on all the time except during the zero crossing where no more current feeds the input and the output transistor switches off.

Finally, the opto-coupler could be connected directly in high side mode between the SYN and the  $V_{DD}$  pins: the ZVS signal is then made of high level pulses synchronized with the zero crossing. However, the coupler could be connected in low side mode with an external 10k pull-up resistor to  $V_{DD}$ : the ZVS is now inverted with low level pulses.

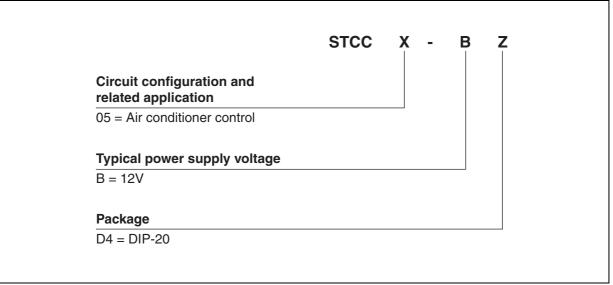

## Figure 19: Ordering Information Scheme

|          |      | DIMENSIONS  |       |      |        |       |       |

|----------|------|-------------|-------|------|--------|-------|-------|

|          | REF. | Millimetres |       |      | Inches |       |       |

|          |      | Min.        | Тур.  | Max. | Min.   | Тур.  | Max.  |

|          | a1   | 0.508       |       |      | 0.020  |       |       |

|          | В    | 1.39        |       | 1.65 | 0.055  |       | 0.065 |

| ↓<br>→ • | b    |             | 0.45  |      |        | 0.018 |       |

| F        | b1   |             | 0.25  |      |        | 0.010 |       |

|          | D    |             |       | 25.4 |        |       | 1.000 |

| €        | E    |             | 8.5   |      |        | 0.335 |       |

|          | е    |             | 2.54  |      |        | 0.100 |       |

|          | e3   |             | 22.86 |      |        | 0.900 |       |

|          | F    |             |       | 7.1  |        |       | 0.279 |

|          | I    |             |       | 3.93 |        |       | 0.155 |

|          | L    |             | 3.3   |      |        | 0.130 |       |

|          | Z    |             |       | 1.34 |        |       | 0.053 |

# Figure 20: DIP-20 Package Mechanical Data

## **Table 6: Ordering Information**

| Part Number | Marking  | Package | Weight | Base qty | Delivery<br>mode |

|-------------|----------|---------|--------|----------|------------------|

| STCC05-BD4  | STCC05-B | DIP-20  | 1.4 g  | 20       | Tube             |

# Table 7: Revision History

| Date        | Revision | Description of Changes |

|-------------|----------|------------------------|

| 05-Oct-2004 | 1        | First issue            |

57

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

> The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

> > © 2004 STMicroelectronics - All rights reserved

STMicroelectronics group of companies Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com