## Features (Continued)

- Embedded ROM coded firmware avoids code download and allows immediate operation at startup

- Supports firmware patch code downloads for in-field upgradeability

- Two independent AGC controls for tuner's IF and RF stages

- RSSI measurement via embedded 8-bit ADC

- ACI filtering for 7 MHz channels enables use of a fixed 8 MHz SAW filter

- Time and frequency equalizer (31 taps for digital cable)

- Carrier recovery: ±0.6 MHz. Timing recovery: ±200 ppm (DVB-T/H) / ±1000 ppm (DVB-C)

- Advanced performance for SFN networks

- State-of-the-art impulsive noise protection algorithm

- CPE compensation to counteract tuner phase noise

- Ultra-fast, on-chip and automatic, UHF/VHF band scanning (QuickScan)

- BER, PER, and SNR, lock indicators

- Master TS output modes, parallel or serial (with tri-state

#### function)

- Slave TS parallel output: external device polls data from on-chip FIFO (GPIF interface). Provides seamless interface to external controller / PHY for USB2.0, PCI-E, etc...

- On-chip PID filtering to reduce TS output bit rate (allows operation with USB1.1 microprocessor)

- Up to six GPIOs

- Two 5 V-tolerant I<sup>2</sup>C control buses (host-side, tuner-side) with on-chip I<sup>2</sup>C repeater (logic switch).

- Clock reference from 4, 16, 20, 24, or 27 MHz tuner output reference clock or external crystal (on-chip crystal oscillator)

- Minimal BOM using standard components

- 3.3 and 1.2 V core power supplies and variable I/O supply from 1.8 to 3.3 V

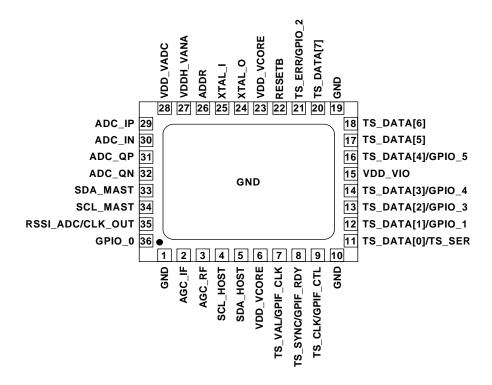

- Ultra-compact and thin QFN-36, 5x6 mm, Pb-free/RoHScompliant package

# **Description** (Continued)

Next to DVB-T's 2K and 8K FFT modes, the Si2165 includes a 4K FFT mode, compliant to DVB-H (ETSI EN 300 744 Annex F). Also both a "native" and "in-depth" interleaver are included. With these features, the Si2165 can receive DVB-H programs in fixed receiver applications (which do not require decoding of DVB-H's additional MPE FEC layer of error control coding).

With embedded smart echoes management and impulse noise reduction algorithms, demodulation performance is best-in-class while still achieving low-power operation. The Si2165 includes an IF sub-sampling mode to further reduce power consumption. For cable standards, the device implements a 31-tap equalizer to handle long echoes.

The Si2165 contains an on-chip crystal oscillator and only requires the connection of a standard crystal or a reference clock. Crystal frequencies of 16, 20, 24, and 27 MHz are supported. Alternatively, a clock signal at any of these frequencies, and additionally 4 MHz (as available, for example, from the tuner front end), can be connected to the device's clock input, eliminating the need for a dedicated crystal.

An embedded 32-bit DSP controls device operation. Sophisticated on-chip algorithms ensure optimum reception even under difficult terrestrial conditions, such as echoes outside the guard interval, pre-echoes, or strong impulsive noise. The associated DSP firmware is embedded into ROM for ease-of-use (no code download required at startup). Nevertheless, patch code can be downloaded via the I<sup>2</sup>C interface at boot-up, for example, to adjust the demodulator for unexpected conditions that may be encountered in the field.

The Si2165 supports ultra-fast channel scanning for both cable and terrestrial DTV channels, thanks to a proprietary QuickScan feature, which is provided as a downloadable patch file (for selected supported tuners).

The use of QuickScan reduces channel discovery time at device setup and runs autonomously on the Si2165 (small software burden on the MPEG/host processor).

The user can select between serial and parallel master MPEG transport stream (TS) output modes. TS clock can be set with a constant period for CA modules.

Furthermore, a TS slave parallel mode is available in which the device signals the availability of TS data in its internal output FIFO to a host, which then reads out this data. The user can program an on-chip 32-PID hardware filter to reduce the output bit rate to only pass TS packets belonging to one or multiple programs/services. For most cases, this can reduce the data rate to below 12 Mbps, allowing the use of an USB1.x interface to carry the selected TS data from a PC peripheral to the host PC. The Si2165 provides a glueless interface to Silicon Labs MCUs with embedded USB interfaces.

A total of six general-purpose inputs/outputs are available (logic levels); Three of these GPIOs also provide  $\Delta/\Sigma$  and interrupt output capabilities. Additionally, for a tuner that does not require RF and/or IF AGC control signals, the corresponding pins can be reconfigured as two general-purpose outputs (GPOs).

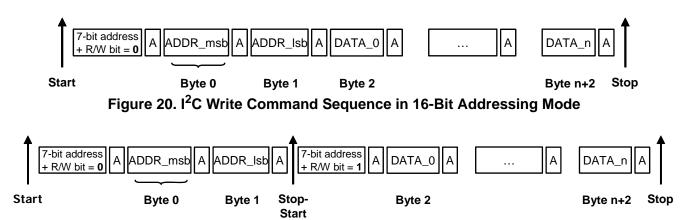

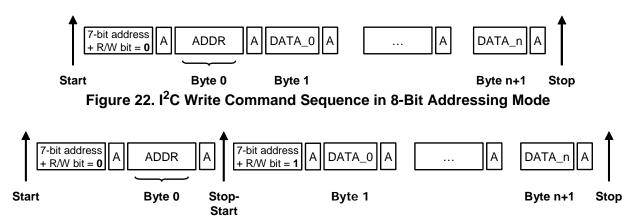

An I<sup>2</sup>C host bus interface is used to configure and monitor all internal parameters/registers. I<sup>2</sup>C addressing mode can be configured in either 16- or 8-bit format. An internal pass-through switch acts as an I<sup>2</sup>C repeater and can be configured to pass I<sup>2</sup>C commands to a secondary (tuner-side) I<sup>2</sup>C bus, when required. This feature provides a "quiet" I<sup>2</sup>C bus to the RF front end.

The Si2165 guarantees a low-cost system implementation due to its minimal bill of materials and PCB footprint. A maximum of 13 to 20 components (R, C, and crystal, depending on the application selected) and 15x20 mm on a 2-layer PCB are required.

# TABLE OF CONTENTS

| <u>Section</u>                                                        | <u>Page</u> |

|-----------------------------------------------------------------------|-------------|

| Glossary                                                              | 5           |

| 1. Electrical Specifications                                          |             |

| 2. Functional Description                                             |             |

| 2.1. Front End                                                        |             |

| 2.2. Demodulator                                                      |             |

| 2.3. Equalizer                                                        |             |

| 2.4. FEC Module                                                       |             |

| 2.5. PID Filter                                                       |             |

| 2.6. TS Output Interface                                              |             |

| 2.7. DSP                                                              |             |

| 2.8. Synchro Block                                                    |             |

| 2.9. Control Block                                                    |             |

| 3. Operational Description                                            |             |

| 3.1. Revision                                                         |             |

| 3.2. Definitions                                                      | _           |

| 3.3. Clocks                                                           |             |

| 3.4. Tuner Interface                                                  |             |

| 3.5. Digital Front End                                                |             |

| 3.6. Demodulator                                                      |             |

| 3.7. Forward Error Correction                                         |             |

| 3.8. System Control                                                   |             |

| 4. MPEG Transport Stream Bus                                          |             |

| 4.1. General TS Output Programmability (Available in All Bus Modes)   |             |

| 4.3. TS Slave Parallel Mode (Microprocessor Interface Mode)           |             |

| 4.4. TS PID Filtering                                                 |             |

| 4.5. TS Timing Diagrams                                               |             |

| 5. I <sup>2</sup> C Control Bus                                       | 36          |

| 5.1. I <sup>2</sup> C Device Address Selection                        |             |

| 5.2. I <sup>2</sup> C Bus Architecture and Operation Modes            |             |

| 5.3. I <sup>2</sup> C Register Addressing Modes (8 or 16-bit)         |             |

| 5.4. I <sup>2</sup> C Switch Operation                                |             |

| 5.5. I <sup>2</sup> C Pull-up Resistors and Bus Voltage Compatibility | 38          |

| 6. General Purpose I/O (GPIO)                                         |             |

| 6.1. Full-function GPIOs: GPIO_0, GPIO_1, GPIO_2                      | 30          |

| 6.2. Logic-Level GPIOs: GPIO_3, GPIO_4, and GPIO_5                    |             |

| 6.3. Selection of the Multiplexed GPIO Ports                          |             |

| 6.4. Activation of GPIO Ports                                         |             |

| 6.5. Additional General-Purpose Output (GPO)                          |             |

| 6.6. Interrupts                                                       |             |

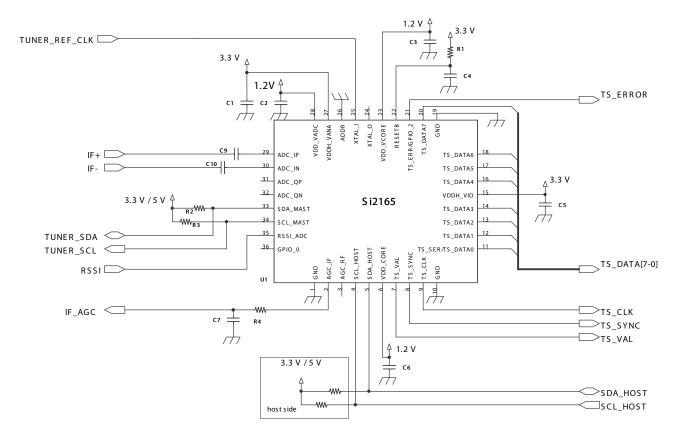

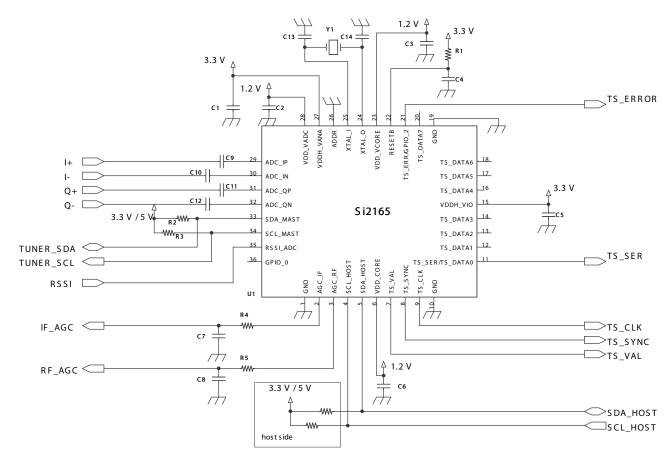

| 7. Typical Application Schematics                                     |             |

| 7.1. Typical Application with IF or Low-IF Tuner | 42  |

|--------------------------------------------------|-----|

| 7.2. Typical Application with ZIF Silicon Tuner  | 43  |

| 7.3. Typical Bill Of Materials                   | 44  |

| 8. Additional Reference Information for Design   |     |

| 9. Programming Guide                             |     |

| 9.1. API Example                                 |     |

| 10. Register Map Summary                         |     |

| 11. Register Descriptions                        |     |

| 12. Pin Descriptions                             |     |

| 13. Ordering Guide                               | 170 |

| 14. Package Marking                              |     |

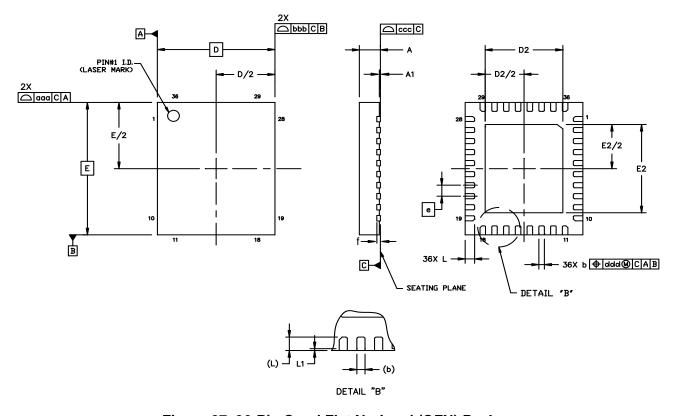

| 15. Package Outline                              |     |

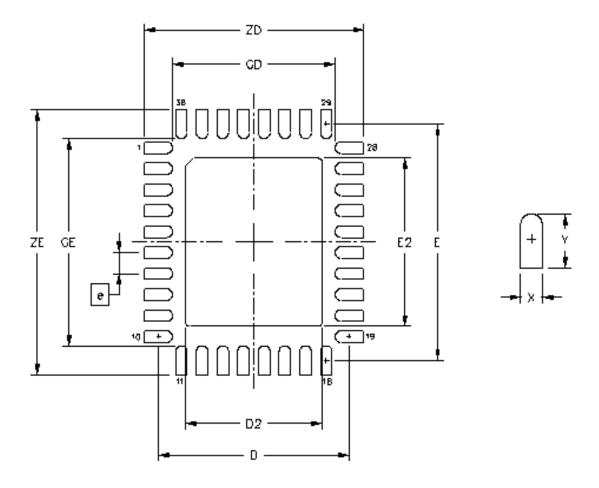

| 16. PCB Land Pattern                             |     |

| Document Change List                             |     |

| Contact Information                              | 176 |

# **G**LOSSARY

| Acronym              | Description                                      |

|----------------------|--------------------------------------------------|

| ACI                  | Adjacent Channel Interference                    |

| ADC                  | Analog to Digital Converter                      |

| AGC                  | Automatic Gain Control                           |

| BER                  | Bit Error Ratio                                  |

| ВОМ                  | Bill of Materials                                |

| CCI                  | Co-Channel Interference                          |

| COFDM                | Coded Orthogonal Frequency Division Multiplexing |

| СР                   | Continuous Pilot                                 |

| CPE                  | Common Phase Error                               |

| CR                   | Code Rate                                        |

| DEI                  | De-interleaver De-interleaver                    |

| DFE                  | Decision Feedback Equalizer                      |

| DVB                  | Digital Video Broadcasting                       |

| DSP                  | Digital Signal Processor                         |

| ETSI                 | European Telecommunications Standards Institute  |

| FEC                  | Forward Error Correction                         |

| FFE                  | Feed Forward Equalizer                           |

| FFT                  | Fast Fourier Transform                           |

| FIFO                 | First In, First Out                              |

| GI                   | Guard Interval                                   |

| GPIF                 | General Purpose Interface                        |

| GPIO                 | General Purpose Input/Output                     |

| HP                   | High Priority (stream)                           |

| I <sup>2</sup> C bus | 2-wire communication bus between devices         |

| LP                   | Low Priority (stream)                            |

| PCI                  | Peripheral Component Interconnect                |

| PER                  | Packet Error Rate                                |

| PID                  | Packet Identifier                                |

| POR                  | Power On and Reset                               |

| QAM                  | Quadrature Amplitude Modulation                  |

| QFN                  | Quad Flat Pack with No Leads                     |

| QPSK                 | Quad Phase Shift Keying Modulation               |

| RS                   | Reed-Solomon Decoder                             |

| RSSI                 | Received Signal Strength Indicator               |

| SNR                  | Signal to Noise Ratio                            |

| SP                   | Scattered Pilot                                  |

| SR                   | Symbol Rate (in Mbaud)                           |

| SRC                  | Sample Rate Converter                            |

| TEI                  | Transport Error Indicator                        |

| TOP                  | Take Over Point (for AGC loops)                  |

| TPS | Transmission Parameter Signaling |

|-----|----------------------------------|

| TS  | Transport Stream                 |

| USB | Universal Serial Bus             |

# 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                | Symbol                | Min  | Тур                | Max  | Unit |

|--------------------------|-----------------------|------|--------------------|------|------|

| Digital Supply Voltage   | V <sub>DD_VCORE</sub> | 1.14 | 1.20               | 1.26 | V    |

| Analog Supply Voltage    | V <sub>DDH_VANA</sub> | 3.00 | 3.30               | 3.60 | V    |

| ADC Supply Voltage       | V <sub>DD_VADC</sub>  | 1.14 | 1.20               | 1.26 | V    |

| Interface Supply Voltage | $V_{DD\_VIO}$         | 1.62 | 1.80 / 2.50 / 3.30 | 3.60 | V    |

| Ambient Temperature      | T <sub>A</sub>        | 0    | 25                 | 85   | °C   |

# Table 2. Absolute Maximum Ratings<sup>1</sup>

| Parameter                  | Symbol                       | Value                              | Unit |

|----------------------------|------------------------------|------------------------------------|------|

| Digital Supply Voltage     | VDD_VCORE                    | -0.3 to 1.5                        | V    |

| Analog Supply Voltage      | VDD_VANA                     | -0.3 to 3.9                        | V    |

| ADC Supply Voltage         | VDD_VADC                     | -0.3 to 1.5                        | V    |

| Interface Supply Voltage   | VDD_VIO                      | -0.3 to 3.9                        | V    |

| Input Current <sup>2</sup> | lin                          | 10                                 | mA   |

| Input Voltage <sup>2</sup> | Vin                          | -0.3 to min (VDD_VIO + 0.3, 3.9)   | V    |

| IF or I/Q inputs           | V <sub>ADC_IN/IP/QN/QP</sub> | -0.3 to min (VDD_VADC + 0.3, 1.5)  | V    |

| RSSI input                 | V <sub>RSSI_ADC</sub>        | -0.3 to min (VDDH_VANA + 0.3, 3.9) | V    |

| Operating Temperature      | Тор                          | -20 to +100                        | °C   |

| Storage Temperature        | Tstg                         | -55 to +150                        | °C   |

### Notes:

2. For input pins RESETB, ADDR, GPIO\_0, GPIO\_1, GPIO\_2, GPIO\_3, GPIO\_4 and GPIO\_5.

<sup>1.</sup> Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure beyond recommended operating conditions for extended periods may affect device reliability.

Table 3. System

| Parameter                               | Min               | Тур           | Max  | Unit     |

|-----------------------------------------|-------------------|---------------|------|----------|

| General                                 |                   |               |      | ·        |

| Power-up Time                           | _                 | _             | 10   | ms       |

| I <sup>2</sup> C Speed (Host side)      | < 1               | _             | 400  | kHz      |

| Input Clock Reference                   | _                 | 4/16/20/24/27 | _    | MHz      |

| Supported Crystal Frequency             | _                 | 16/20/24/27   | _    | MHz      |

| Input ADC Sampling Clock                | <u> </u>          |               |      | •        |

| ZIF Mode                                | 18.5              | 48            | 60   | MHz      |

| IF Sub-sampling Mode                    | 18.5              | 27            | 32.5 | MHz      |

| IF Over-sampling Mode                   | 37                | 48            | 60   | MHz      |

| System Clock                            | _                 | _             | 85   | MHz      |

| TS Output Rates                         | <u> </u>          |               |      | •        |

| Serial Mode DVB-T                       | _                 | _             | 42   | MHz      |

| Serial Mode DVB-C                       | _                 | _             | 65   | MHz      |

| Current Supplies and Power Consumption  | n                 |               |      | <b>'</b> |

| DVB-T, 8 MHz, IF Mode, adc_clk = 56 MHz | Parallel TS Outpu | t             |      |          |

| VDD_VCORE (@ 1.2 V)                     | _                 | 55            | _    | mA       |

| VDD_VADC (@ 1.2 V)                      | _                 | 15            | _    | mA       |

| VDDH_VANA (@ 3.3 V)                     | _                 | 9             | _    | mA       |

| VDD_VIO (@ 3.3 V)                       | _                 | 8             | _    | mA       |

| Total Power                             | _                 | 140           | _    | mW       |

| DVB-C, 6.9 Mbauds, 256 QAM, adc_clk = 5 | 66 MHz            |               |      | •        |

| VDD_VCORE (@ 1.2 V)                     | _                 | 39            | _    | mA       |

| VDD_VADC (@ 1.2 V)                      | _                 | 15            | _    | mA       |

| VDDH_VANA (@ 3.3 V)                     | _                 | 9             | _    | mA       |

| VDD_VIO (@ 3.3 V)                       | _                 | 8             | _    | mA       |

| Total Power                             |                   | 120           |      | mW       |

| Stand-by Mode                           |                   |               |      |          |

| VDDH_VANA (@ 3.3 V)                     | _                 | 4             | _    | mA       |

| Total Power                             | _                 | 13            | _    | mW       |

Table 4. Analog Front End—I/Q A/D Converters

| Parameter                        | Symbol              | Min | Тур                     | Max | Unit |

|----------------------------------|---------------------|-----|-------------------------|-----|------|

| DC Accuracy                      |                     |     |                         |     |      |

| Resolution                       | N                   | _   | 12                      | _   | bits |

| Analog Signal Input              |                     |     |                         |     |      |

| Number of A/D Converters         | N <sub>IQ-ADC</sub> | _   | 2 (differential inputs) | _   |      |

| ADC Impedance                    | Z <sub>in,ADC</sub> | _   | 12                      | _   | kΩ   |

| Input Differential Voltage Range | V <sub>FSR</sub>    | _   | 1                       |     | Vpp  |

Table 5. Analog Front End—RSSI A/D Converter

| Parameter                | Min | Тур | Max | Unit |

|--------------------------|-----|-----|-----|------|

| Resolution               | _   | 8   | _   | bit  |

| Number of A/D Converters | _   | 1   | _   |      |

| Input Voltage Range      | _   | 0–2 | _   | V    |

| Analog Input Bandwidth   | _   | 500 | _   | Hz   |

| Input Impedance          | _   | > 1 | _   | ΜΩ   |

# 2. Functional Description

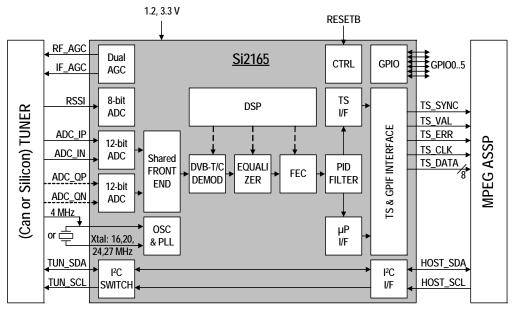

The Si2165 consists of the following functional blocks: front end, demodulator, equalizer, FEC module, PID filter, TS output interface, DSP, synchro block, and control block. These functions are described in the following sections.

Figure 1. Functional Block Diagram

### 2.1. Front End

The front end interfaces the analog inputs to the digital demodulation section of the receiver. Thanks to the presence of two ADCs with differential inputs, the front end can support zero-IF or low-IF "complex" inputs next to standard-IF or low-IF "real" inputs. In case of a "real" input, a source selector switch allows the selection of either ADC; so, two RF tuners can be connected. After A/D conversion, the front end performs I and Q mismatch correction, if required. The front end further contains a separate 8-bit ADC for RSSI (Receive Strength Signal Indicator) measurement. RF and IF AGC control signals are provided to the tuner. An on-chip PLL generates ADC sampling and digital clocks from an external crystal (on-chip oscillator) or reference clock input. The front end output to the demodulator module is the digitized ADC data, down-mixed to a complex baseband signal and rate-converted from the programmable ADC sample rate to a rate equal to exactly 4 times the symbol rate.

### 2.2. Demodulator

For DVB-T/H, the demodulator performs successively adjacent channel filtering, impulse noise filtering, FFT processing, and echo shift compensation.

FFT window positioning is provided by the synchronization module. The demodulator provides the equalizer module with the demodulated and distorted carriers, consisting of scattered pilots, continuous pilots, TPS carriers, and carriers with QAM symbols.

For DVB-C, the demodulator performs adjacent channel filtering through a high-rejection half-Nyquist filter. An automatic digital gain control is also performed at the Nyquist filter output to compensate for power reduction within the filter such that its output signal power level remains optimized. A timing error detector provides an error signal to a second-order loop filter, which delivers a timing correction signal to control the sampling rate conversion in the front end block. The bandwidth and damping factor of the loop are programmable in order to achieve both high acquisition range and good performance during the tracking phase. A highly-programmable frequency sweep function is available to cope with large frequency offsets. The frequency correction signal is sent back to the downconverter of the front end block, which applies the proper frequency shift on the input spectrum. The overall synchronization process of the QAM demodulator is controlled by a configurable state machine, which uses status information from the different blocks to sequence the synchronization algorithms. This makes synchronization completely autonomous and, therefore, simplifies the host processor software.

# 2.3. Equalizer

For DVB-T/H, the equalizer estimates the channel transfer function and corrects the received signal, providing channel-corrected signal samples and confidence information to the downstream blocks. COFDM systems are designed to reduce the equalizer to its most simple expression: a single-tap filter. In order to correct each subcarrier, the equalizer has to estimate the frequency response of the channel. This task is facilitated by the insertion, at transmission, of known pilots at specific frequencies. These pilots are modulated and boosted to ensure better reception. First, the equalizer has to demodulate them. Then, it can estimate the channel response. This information is used to straighten the distorted carriers. Concurrently, the channel estimation is used to compute Channel State Information (CSI), which will be used by the demapper to weigh the soft bits information. The Si2165 also uses specific CSI algorithms to deal with high levels of Co-Channel Interference (CCI).

For DVB-C, the equalizer block implements an adaptive decision-feedback equalizer, a carrier recovery loop, and a demapper suitable for the DVB-C standard. A signal-to-noise estimator allows both the equalizer and carrier recovery loop parameters to be automatically controlled during the acquisition and tracking phases.

The DFE equalizer contains two parts:

- Feed-forward part with programmable length, which receives symbols at the symbol rate from the demodulator

- Feedback part, which receives decided symbols from the demapper

Equalizer coefficients are continuously adapted to the measured channel response.

Carrier recovery, which implements a phase detector and a programmable second-order loop filter, receives decision errors from the demapper. To optimize performance, dedicated hardware controls the operation of both equalizer and carrier recovery during the acquisition and tracking phases.

### 2.4. FEC Module

The FEC module consists of an **inner FEC** (for DVB-T/H) and **outer FEC** (for DVB-T/H and DVB-C). Operating on the output of the equalizer, it provides an error-corrected transport stream to the TS output interface.

The forward error correction module is compliant to broadcast cable standard EN 300 429 (DVB-C) and terrestrial standard EN 300 744 (DVB-T), also supporting Annex F (DVB-H).

This module can be configured by setting the standard and the relevant broadcast parameters: constellation, FFT mode, guard interval, code rate, hierarchy level, and stream demodulated (HP or LP). All other control registers dedicated to FEC synchronization contain default values already adapted to the mode received.

The FEC starts to synchronize once the demodulator is locked. At the end of processing, a lock indicator indicates that the FEC is locked and that the transport stream contains valid data.

For DVB-T/H, the FEC receives constellation point (I/Q) data from the DVB-T/H equalizer as well as related Channel State Information (CSI). For DVB-C, the FEC receives 4–8 bit encoded symbol data, depending on the constellation (16 to 256 QAM).

For DVB-T/H, an **inner FEC** includes a symbol (frequency) de-interleaver, de-mapper, bit de-interleaver, and Viterbi decoder. The symbol de-interleaver could be configured as native or in-depth, where the native mode is the original mode of the DVB-T specification, and the in-depth mode is the specific mode from Annex F. When the indepth mode is selected in 2K or 4K FFT mode, the symbol de-interleaver always acts on blocks of 6048 data symbols. Rate smoothing is implemented to cancel the jitter effects of the COFDM symbol structure and of FFT window synchronization. The demapper computes soft decision bits from the frequency de-interleaved complex symbol and CSI data. Bit de-interleaving is then processed to achieve randomization at the bit stream level. The Viterbi decoder includes automatic de-puncturing of the incoming stream and systematically synchronizes to the start of the COFDM symbol.

For DVB-T/H modes, the **outer FEC** consists of a packet synchronizer, Forney De-Interleaver, Reed-Solomon Decoder, and Energy-Dispersal Descrambler. For DVB-C mode, the complete FEC section is identical to the **outer FEC** section of DVB-T/H.

Packet synchronization provides DVB packets of 204 bytes. The Si2165 offers fully-automated packet synchronization for both terrestrial and cable standards. The Forney de-interleaver spreads remaining burst errors to allow their correction by the Reed-Solomon decoder. The Reed-Solomon decoder, with a correction capacity of eight erroneous bytes per TS packet, corrects the residual errors after de-interleaving and declares the output packet un-correctable if its correction capacity is exceeded. Finally, the energy-dispersal descrambler synchronized by the inverted SYNC byte, 0xB8, retrieves the original TS.

### 2.5. PID Filter

The PID filter allows for optional filtering of the MPEG-TS packets. The user can specify up to 32 PID values, which are either blocked or passed. In the latter case, all other PID's are blocked except the chosen PID.

# 2.6. TS Output Interface

The TS output interface formats the TS into a parallel or serial MPEG-TS interface and provides various output formatting options. Two output bus modes exist: a regular master-mode synchronous interface (parallel or serial) providing clock and data, and an asynchronous parallel interface that allows an external device (typically a microcontroller) to read a burst of 512 MPEG TS data bytes out of the Si2165's internal output FIFO.

### 2.7. DSP

An embedded DSP supervises the entire synchronization task. Embedded ROM code is present in the Si2165. Onboard RAM provides memory space for a firmware patch download or for implementation of extra features, such as the QuickScan (blindscan) routine.

# 2.8. Synchro Block

The synchro block mainly consists of hardware coprocessors that aid the DSP in the synchronization task.

### 2.9. Control Block

The control block is mainly a clock and reset management block that generates all internal clocks and associated resets required by the Si2165. It also includes dedicated test logic for manufacturing test purposes.

# 3. Operational Description

# 3.1. Revision

The part revision is given by the die version, which can be read from the revcode (0023h) register.

See "3.8.2.2. Device Initialization Sequence" on page 25 for an overview of system boot information.

### 3.2. Definitions

The following definitions apply throughout the text of this data sheet.

- DVB rate:

- For DVB-T/H, DVB\_rate denotes the reference frequency, i.e. 8/7 x BW (for instance, ~9.14 MSPS for an 8 MHz bandwidth).

- For DVB-C, DVB rate denotes the symbol rate, i.e., 1 to 7.2 MBaud for an 8 MHz bandwidth.

- The FE clk frequency is the frequency of the front end clock.

- If adc\_clock is > 4 x DVB\_rate, FE\_clk frequency = adc\_clk frequency.

- Otherwise, FE\_clk frequency = 2 x adc\_clk frequency.

### 3.3. Clocks

### 3.3.1. Clock Reference Input: Crystal or External Clock Source

The reference clock of Si2165 is either a crystal connected between the XTAL\_I and XTAL\_O pins (the device has an on-chip crystal oscillator), or a sinusoidal or rectangular clock provided by an external source on pin XTAL\_IN. When Si2165 is used with a crystal, supported crystal frequencies are 16, 20, 24, and 27 MHz.

When Si2165 is used with an external clock source, supported clock frequencies are 4, 16, 20, 24, and 27 MHz.

Register **chip\_mode (0000h)** has to be set to indicate whether the clock comes from the crystal or an external clock.

**Note:** When **chip\_mode (0000h)** is set to "off", no clock is provided to the chip, which corresponds to the Si2165 standby mode and represents the device default state after hardware reset.

The reference clock accuracy should be better than ±200 ppm for DVB-T/H while it is relaxed to ±1000 ppm maximum for DVB-C.

For DVB-T/H, the **timing\_sync\_range (0318h)** register adjusts the demodulator timing recovery range according to the selected crystal accuracy. A crystal with worse frequency accuracy will require a higher timing recovery range setting. However, the higher the range value, the longer the demodulator locking time will be. The value is the required local oscillator precision in ppm. For example, it should be set to 50 for a ±50 ppm crystal.

### 3.3.2. Clock Reference Output

The input clock reference can be routed outside Si2165 via the RSSI pin to drive an external chip (e.g. in a dual front end application). Register **rssi\_pad\_ctrl (0646h)** allows toggling between the two functionalities for this pin.

### 3.3.3. Clock Domains

Si2165 has three internal clock domains that are relevant to the user.

- **adc clk**: ADC sampling clock. Used by ADC, dc offset correction, and I/Q mismatch correction.

- **FE\_clk**: Front End clock. Used for IF frequency shift, anti-alias filtering, and timing correction.

- **sys clk**: System clock. Used by the demodulator up to transport stream output.

adc\_sampling\_mode (00E0h) has to be set according to adc\_clk frequency and DVB\_rate; then FE\_clk will be affected according to the following table:

| adc_clk Divided by DVB_rate | Oversampling<br>Mode | adc_sampling_mode (00E0h)                          | FE_clk<br>Frequency | Max. adc_clk<br>Frequency |

|-----------------------------|----------------------|----------------------------------------------------|---------------------|---------------------------|

| > 4                         | Ovr4                 | If_ovr4 or zif_ovr4 (depending on tuner interface) | = adc_clk           | 65 MHz                    |

| ≤ 4                         | Ovr2                 | If_ovr2 or zif_ovr2 (depending on tuner interface) | = adc_clk * 2       | 32.5 MHz                  |

Requirements for sys\_clk are 8 x DVB\_rate < Sys\_clk < 85 MHz. Usually, sys\_clk is set around 80 MHz for DVB-T/H and around 60 MHz for DVB-C.

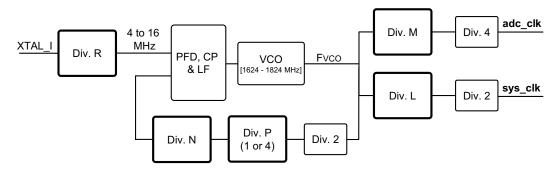

### 3.3.4. Clock Generation/PLL Dividers

Both adc\_clk and sys\_clk are generated from an on-chip PLL, which contains five dividers. Figure 2 shows a diagram of the embedded PLL block.

Figure 2. PLL Divider Details

For normal device operation, register pll enable (00A2h) needs to be enabled.

Divider R pll\_divr (00A3h) shall be chosen such that:

the ratio XTAL\_I/R falls between 4 and 16 MHz.

Pre-scaler P pll divp (00A2h) is selecting between a division by 1 or a division by 4.

Divider N pll\_divn (00A2h) shall be calculated such that:

$Fvco = XTAL_I/R \times 2 \times N \times P$  falls in the 1624 to 1824 MHz VCO frequency range.

Divider M pll\_divm (00A1h) and divider L pll\_divl (00A0h) are set to ensure proper adc\_clk and sys\_clk frequencies.

adc clk is programmed according to the following formula:

$$adc\_clk = F_{VCO} / (4 \times pll\_divm)$$

sys\_clk is programmed according to the following formula:

$$sys\_clk = F_{VCO} / (2 \times pll\_divl)$$

There is no valid default PLL divider setting preloaded.

### 3.4. Tuner Interface

### 3.4.1. I/Q ADCs

The Si2165 analog input stage contains two 12-bit pipeline A/D converters. All voltage references and biases are included on-chip. The Si2165 basic interface scheme is ac-coupled inputs. Optimized ADC settings have to be written after software reset through registers adc\_ri0 (0129h) to adc\_ri6 (012Fh) and adc\_ri8 (0123h). See "3.8.2.2. Device Initialization Sequence" on page 25.

### 3.4.2. Input Configurations

Si2165 supports connection to tuners with standard IF (~36 MHz), low-IF (typically 3-4 MHz) or Zero-IF (ZIF) analog baseband I/Q outputs. The latter mode is possible thanks to the presence of two ADCs. Register adc\_sampling\_mode (00E0h) selects the ADC sampling mode (IF or ZIF).

In IF sampling mode, a single ADC is used. The ADC in function can be selected with register **iq\_adc\_swap (0122h)**. By default, ADC\_I is used. This register can also be used to switch between two different IF sources connected to the device.

In ZIF sampling mode, both ADCs are used. If a spectrum inversion happens in the tuner or if I and Q traces are inverted on the PCB, the proper tuner connection can be restored via register **iq\_adc\_swap (0122h)**.

Both oversampling and sub-sampling modes are supported. In this context, sub-sampling refers to the use of an ADC clock frequency lower than the IF frequency. The advantage of sub-sampling is lower power consumption, but it may cause performance degradation especially with respect to adjacent channel immunity. The advantage of oversampling is better performance as it requires lower tuner selectivity.

For all modes, the sampling frequency has to be chosen such that ADC aliasing is minimized. This obviously depends on the selectivity of the tuner and has to be assessed for the worst-case adjacent channel scenario (typical 54 MHz sampling frequency is used in case of a 36 MHz IF scheme).

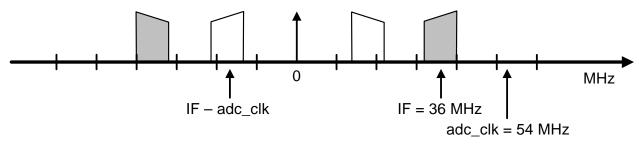

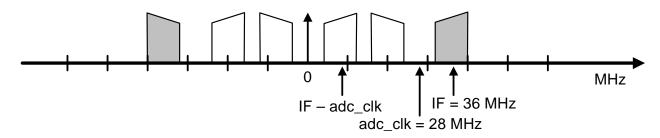

## 3.4.2.1. Standard IF

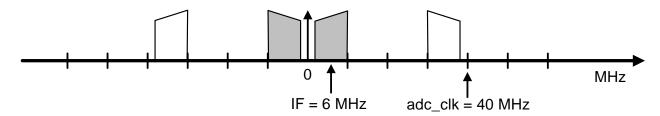

Figures 3 and 4 show examples of the ADC output spectrum for standard IF applications. Two cases can be distinguished, depending on whether the sampling clock is higher (oversampling) or lower (sub-sampling) than the input IF center frequency.

Over-sampling: ADC Clock > IF Center-Frequency

Figure 3. ADC Output Spectrum in Standard-IF Mode (Oversampling)

Sub-sampling: ADC Clock < IF Center-Frequency

Figure 4. ADC Output Spectrum in Standard-IF Mode (Sub-sampling)

As shown in Figures 3 and 4, the A/D conversion creates replications of the IF input signal. Digital\_IF indicates the frequency of the desired signal, which is located at frequency IF – adc\_clk. This signal has to be downconverted to baseband. A frequency shift equal to "– digital\_IF" must be applied to the input signal. This is done through register if freq shift (00E8h).

if freq shift =

$$-$$

digital IF (in Hz) x  $2^{29}$  / FE clk (in Hz)

If a spectrum inversion happens in the tuner, the spectrum located at – digital\_IF has to be selected instead of digital\_IF to recover the right spectrum.

### 3.4.2.2. Low-IF

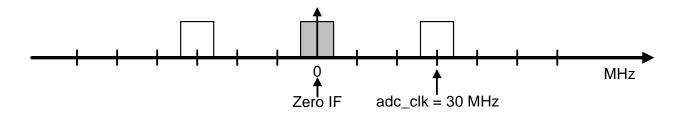

Low-IF denotes the case where the IF signal frequency is less than half of the ADC clock frequency (Nyquist). Figure 5 shows an example of the ADC output spectrum for low IF applications.

Figure 5. ADC Output Spectrum in Low-IF Mode

Since the sampling frequency is higher than twice the IF signal frequency, no downconversion occurs during sampling. Thus, digital\_IF equals the low-IF frequency. This signal has to be downconverted to baseband. A frequency shift equal to "– digital\_IF" must be applied to the input signal. This is done through register **if\_freq\_shift** (00E8h).

if freq shift =

$$-$$

digital IF (in Hz) x  $2^{29}$  / FE clk (in Hz)

If a spectrum inversion happens in the tuner, the spectrum located at "- digital\_IF" has to be selected instead of digital IF to recover the right spectrum.

### 3.4.2.3. Zero IF (I/Q)

Figure 6 shows an example of the ADC output spectrum for ZIF applications.

Figure 6. ADC Output Spectrum in Zero-IF

In ZIF mode, there is no need to downconvert the signal to baseband (digital\_IF = 0); so, the value of the **if\_freq\_shift (00E8h)** register should be programmed to zero. If a spectrum inversion happens in the tuner or if I and Q traces are inverted on the PCB, the proper tuner connection can be restored via register **iq\_adc\_swap (0122h)**.

The following table summarizes the various tuner interface modes.

| Tuner Interface | adc_sampling_mode (00E0h)                   | Digital_IF   | Solution for Spectral<br>Inversion |

|-----------------|---------------------------------------------|--------------|------------------------------------|

| IF over-samp    | IF_ovrx (x = 2 or 4 upon oversampling mode) | IF – adc_clk | Shift over Digital_IF * (-1)       |

| IF sub-samp     | IF_ovrx                                     | IF – adc_clk | Shift over Digital_IF * (-1)       |

| Low-IF          | IF_ovrx                                     | IF           | Shift over Digital_IF * (-1)       |

| ZIF             | ZIF_ovrx                                    | 0            | Invert I/Q with iq_adc_swap(0122h) |

In DVB-C, demodulation is achieved with or without spectral inversion if register **ps\_ambig\_mode (0450h)** is in auto mode (default). In this case, the spectral inversion status can be read from register **ps\_ambig\_out (0444h)**. When in manual mode, the user should program, in register **ps\_ambig\_reg (0450h)**, whether or not to activate the spectral inversion.

### 3.4.3. **RSSI ADC**

If the **rssi\_pad\_ctrl (0646h)** register has been set to do so, the Si2165 can monitor the RSSI (Received Signal Strength Indicator) signal from tuners that provide such output. The device contains an 8-bit ADC that digitizes the RSSI signal applied to the RSSI\_ADC pin. The signal is assumed to be dc-coupled. Because of the low sampling rate of the RSSI ADC, the input signal bandwidth should not be more than 500 Hz.

The RSSI ADC is turned on via register en\_rssi (0641h). The start\_rssi (0641h) register allows activating or stopping RSSI measurement monitoring. When the RSSI function is active, register rssi (0642h) contains the most recent digitized value of the RSSI input signal.

The refresh rate of RSSI measurement can be modified by the **rssi\_update\_time (0641h)** register value according to the following formula:

RefreshRate (in Hz) = sys\_clk (in Hz) / 2<sup>rssi\_update\_time+5</sup>

**Note:** There is no gain / offset control capability on this input.

### 3.4.4. Analog AGC

Si2165 provides RF\_AGC and IF\_AGC output signals, which drive the corresponding tuner inputs, to ensure that proper signal level(s) at the ADC input(s) are maintained.

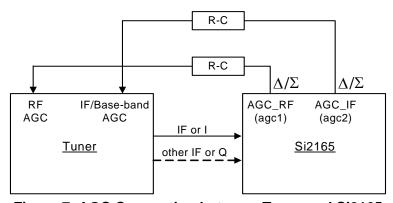

Both AGC outputs are  $\Delta/\Sigma$  outputs and need to be R-C filtered prior to use by the tuner (see Figure 7).

Figure 7. AGC Connection between Tuner and Si2165

Section "7.1. Typical Application with IF or Low-IF Tuner" on page 42 describes the recommended R-C circuit. Minimum and maximum voltage swings can be set with registers agc1\_min (015Eh) and agc1\_max (015Fh), and agc2\_min (016Eh) and agc2\_max (016Fh).

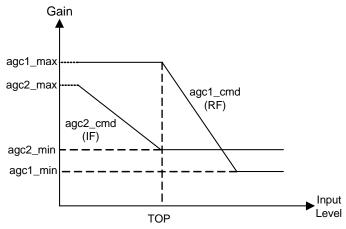

AGC operation is performed to optimize the noise and linearity performance of the tuner. The highest gain is applied to the RF stage as long as the level is below the Takeover Point (TOP) to maximize noise performance. When the input level is higher than the TOP, the RF gain is reduced to ensure that linearity is maintained. This behavior is shown in Figure 8.

Figure 8. AGC Scheme

As shown in Figure 8, the TOP is set with register agc2\_min (016Eh). If the value of agc2\_min is increased, the TOP is reduced. The AGC operation within Si2165 keeps the RF gain (agc1) to its maximum and adapts the IF/BB gain to ensure a proper level at the ADC input. If IF/BB gain (agc2) reaches the value set into the agc2\_min (016Eh) register, the RF gain is reduced to reach the correct ADC level.

If the gain-versus-voltage characteristics of the amplifiers have a negative slope, the polarity of AGC controls have to be inverted via registers **agc1\_pola** (0160h) and **agc2\_pola** (0170h). The default setting is a positive slope.

It should be noted that the maximum AGC levels cannot exceed the selected V<sub>DD VIO</sub> supply voltage.

Users can read the two agc1 and agc2 values from registers agc1\_cmd (0168h) and agc2\_cmd (0178h).

For each AGC output, the AGC outputs can be set independently to push-pull or open drain modes using registers agc1\_buftyp (0160h) and agc2\_buftyp (0170h). Furthermore, registers agc\_if\_tri (018Bh) and agc\_rf\_tri (018Dh) enable or tri-state the corresponding AGC outputs. Finally, the two registers, agc\_rf\_slr (0192h) and agc\_if\_slr (0190h), allow modifying the slew rate with four settings on each AGC output pins. Register agc\_lock (0188h) indicates when analog AGC has converged.

AGC1 and AGC2 loop bandwidths are programmable to set appropriate settling time and ensure stability for tuners with different gain versus voltage characteristics.

### 3.5. Digital Front End

The digital front end receives the ADC data and performs dc offset correction, I/Q mismatch correction, anti-alias filtering, and sample rate conversion.

### 3.5.1. DC Offset Correction

A dc removal function has been implemented to remove potential dc offset on I and Q input signals. Register dc\_bypass (0131h) enables or disables this feature.

When enabled, the current dc offset correction values can be read from registers dc\_offset\_i (0132h) and dc\_offset\_q (0133h), and the correction loop can be frozen to the current correction values via register dc\_freeze (0131h). Register dc\_coeff (0131h) enables setting of the loop bandwidth.

If iq\_adc\_swap (0122h) is set to "swapped", dc\_offset\_i (0132h) indicates the ADC Q offset and vice-versa.

### 3.5.2. I/Q Mismatch Correction

In ZIF applications, impairments in the tuner can lead to phase and amplitude mismatches on I/Q complex input signals; so, correction functions have been implemented to compensate for these.

Amplitude mismatch correction is applied to the Q branch and is enabled via register iq\_freeze (0134h). The gain currently applied to the Q branch can be read from register q\_gain (013Ch). If iq\_adc\_swap (0122h) is set to "swapped", q\_gain (013Ch) indicates the gain applied to the I branch. Register iq\_kagc (0135h) enables setting of the loop bandwidth.

Phase mismatch correction is enabled via register phase\_freeze (0140h). The current phase correction can be read from register phi cor (0144h). Register phase kloop (0141h) enables setting of the loop bandwidth.

### 3.5.3. Anti-Alias Filtering

Low-pass filtering has to be performed on the signal to remove unwanted images in order to avoid aliasing during the sample rate conversion that follows.

A digital AGC function allows compensating for the removed power. Register aaf crestf dbx8 (01A0h) sets the reference level for the filter's average output power level. The corresponding gain applied to the signal (after AGC convergence) can be read from register aaf agc cmd (01B0h).

### 3.5.4. Bandwidth Setting For DVB-T/H

The user should select the DVB-T/H broadcast channel bandwidth (5, 6, 7, or 8 MHz) into the bandwidth (0308h) register.

Note: Where value = received bandwidth / 10 kHz i.e. 700 for 7 MHz (default value being 800 i.e. 8 MHz)

### 3.5.5. Sample Rate Conversion

The ratio between FE\_clk and DVB\_rate has to be programmed such that the sample rate converter can perform the timing recovery function. This is done through register **oversamp (00E4h)** with the following calculation:

oversamp =

$$FE_clk$$

(in Hz) / DVB\_rate (in Hz) x  $2^{23}$

### 3.5.6. ACI Filtering

Low-pass filtering has to be performed on the signal to remove adjacent channels and allow proper demodulation. In DVB-C, this filter is a square root raised cosine filter (Nyquist filter).

A digital AGC function allows the chip to compensate for removed power. Register aci\_crestf\_dbx8 (01C8h) sets the reference level for the filter's average output power level. The corresponding gain applied to the signal (after AGC convergence) can be read from register aci\_agc\_cmd (01D8h).

### 3.6. Demodulator

Register standard (00ECh) configures the demodulator for either DVB-T/H or DVB-C demodulation. After poweron reset DVB-T/H is the default standard.

### 3.6.1. DVB-T/H

### 3.6.1.1. Normal Operation via TPS (Transmission Pilot Signaling)

In DVB-T/H, parameters needed for device synchronization are broadcast in the TPS carriers. Register tps lock (0394h) signals whether the Si2165 has detected this information in the TPS carriers.

The TPS word length (33 bits for DVB-H, 31 bits for DVB-T, 23 bits for DVB-T without Cell-ID) can be read from register tps length (0418h).

Choice of high-priority (HP) or low-priority (LP) streams is achieved through programming the req stream (02E4h) register.

When the TPS are found, the demodulator is automatically configured with the parameters detected in the TPS stream. When automatic synchronization is active, detected modulation parameters can be read from the following registers:

| Registers                  | Definition              | Read-only Values                |

|----------------------------|-------------------------|---------------------------------|

| auto_fft_mode (03F0h)      | FFT mode                | 2K, 4K, 8K                      |

| auto_guard_int (03F4h)     | Guard Interval type     | 1/32, 1/16, 1/8, 1/4            |

| auto_constellation (03F8h) | Constellation type      | QPSK, 16 QAM, 64 QAM            |

| auto_rate_HP (0400h)       | Code Rate for HP stream | 1/2, 2/3, 3/4, 5/6, 7/8         |

| auto_rate_LP (0404h)       | Code Rate for LP stream | 1/2, 2/3, 3/4, 5/6, 7/8         |

| auto_hierarchy (0408h)     | Hierarchical level      | None, Alpha 1, Alpha 2, Alpha 4 |

Automatic synchronization can be disabled using register automatic\_synchro (02E8h). When turned off, individual DVB-T/H parameters need to be programmed using registers req\_fft\_mode (02ECh), req\_guard\_int (02F0h), req\_constellation (02F4h), req\_rate\_HP (02F8h), req\_rate\_LP (0300h), and req\_hierarchy (0304h).

#### 3.6.1.2. Cell ID

Cell-ID is the identifier of the broadcasting DVB-T/H transmitter. The **cell\_id (040Ch)** register provides the TPS decoded cell-ID value.

### 3.6.1.3. DVB-H Specifics

Next to standard 2K and 8K FFT modes for DVB-T, Si2165 also includes a 4K FFT mode for DVB-H reception. DVB-H transmission can also use a different kind of inner symbol deinterleaver. If the device detects within the TPS that the DVB-H specific in-depth deinterleaver is used, the DSP unit will automatically activate this function within the FEC block. The detected deinterleaver mode can be read from register **dvbh\_interleaver (041Ch)**.

If register automatic\_synchro (02E8h) is not set in automatic mode, the user should manually set the deinterleaver mode using register symb deint mode (04C0h).

Extended TPS information is available in DVB-H mode and signals whether MPE-FEC coding and time slicing are used on either the low- or high-priority stream(s).

| Registers                                                                        | Registers Indications                                    |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------|--|

| Ip_mpe_fec (0415h) MPE-F.E.C. is used on minimum one elementary LP stream        |                                                          |  |

| hp_mpe_fec (0417h) MPE-F.E.C. is used on minimum one elementary HP stream        |                                                          |  |

| Ip_time_slicing (0414h) Time slicing is used on minimum one elementary LP stream |                                                          |  |

| hp_time_slicing (0416h)                                                          | Time slicing is used on minimum one elementary HP stream |  |

### 3.6.1.4. Common Phase Error (CPE) Compensation

To correct for a phase noise component common across the COFDM carriers, the Si2165 implements some CPE compensation. Register **cpe\_req (0310h)** enables this feature, which is recommended to be left activated.

### 3.6.1.5. Impulsive Noise Protection

Special algorithms have been implemented to counteract most of the impulsive noise impairments on the DVB-T/H spectrum. Register **impulsive\_noise\_remover (031Ch)** enables this feature, which is recommended to be left activated.

### 3.6.1.6. Demod Status

Si2165 indicates if the DVB-T/H demodulator is locked in register **demod\_lock\_t** (0390h). Register **freq\_lock\_t** (0398h) indicates whether carrier recovery is achieved. Register **timing\_lock\_t** (039Ch) indicates whether timing recovery is achieved. Register **fft\_lock\_t** (03A0h) indicates whether fft window synchronization is achieved.

For DVB-T/H demodulation, after any change to the RF setting(s) on the tuner, it is recommended to apply a "start\_synchro" command via register **start\_synchro** (02E0h).

### 3.6.1.7. Timing Recovery

Timing offset can be computed from the timing\_corr\_t (03B0h) register according to the following formula:

TimingOffset (in ppm) =

$$4 \times 10^6 \times$$

With the default values of the loop parameters, the timing acquisition range of this loop is typically ±50 ppm. The acquisition range can be modified up to ±200 ppm thanks to register **timing\_sync\_range (0318h)**. Note, however, that the acquisition time may increase with the timing recovery range enlargement.

### 3.6.1.8. Carrier Recovery

The carrier recovery range can be adjusted with register **freq\_sync\_range (030Ch)**. The default value is set for 50 kHz offset.

Frequency offset can be computed from the freq\_corr\_t (03B4h) register according to the following formula:

## 3.6.1.9. DVB-T/H Equalizer

Time and frequency equalizers have been optimized for fixed/portable terrestrial channel recovery. The onboard firmware continually optimizes the behavior of both equalizers to the measured channel response. The current measured channel length can be computed from register **channel\_length (03A4h)**.

An estimation of the signal-to-noise ratio can be computed from registers **sigma2\_est (02A4h)** and **ref\_signal\_power (02C0)**. Actual value of C/N in dB is given by the following formula:

$$C/N$$

(in dB) = 10 x (log10 (sigma2\_est / 2) / (ref\_signal\_power x 64))

### 3.6.1.10. Reacquisition (Auto Re-lock) for DVB-T/H

Si2165 will relock automatically after an interruption to the RF input signal as e.g. the result of an antenna disconnect or RF signal interruption.

### 3.6.1.11. Scanning Procedure for DVB-T/H

Fast scanning (host processor assisted)

During channel scanning, Si2165 can inform via register **check\_signal (03A8h)** whether or not a COFDM DVB-T/H signal is present on a given RF channel. This improves channel scan time significantly as it provides a faster readout than waiting for the complete DVB-T/H lock process for those channels where no (or analog) modulation is present.

QuickScan (on-chip, ultra-fast automatic channel scan)

The complete channel scan procedure is detailed in a forthcoming application note.

### 3.6.2. DVB-C

### 3.6.2.1. Constellation

The constellation format (from 16 QAM to 256 QAM, including rectangular constellations 32 & 128) shall be user-defined into the register, **reg\_constellation (02F4h)**.

## 3.6.2.2. Symbol Rate

Programming of the symbol rate is achieved via the **oversamp (00E4h)** register as defined in "3.5.5. Sample Rate Conversion".

### 3.6.2.3. Timing Recovery Loop

The timing recovery block implements a timing error detector and a second-order loop filter, for which loop bandwidth and damping factor are programmable for both acquisition and tracking modes.

The damping factor formula is:

$$Df = 13 \times 2^{(KP - (KI/2) - 11)}$$

Downloaded from Arrow.com.

The normalized bandwidth formula is:

BI.Ts =

$$13 \times 2^{((KI/2) - 11)} \times (Df + 0.25 / Df)$$

KP is user-defined by two registers, tim\_kp\_acq (0201h) and tim\_kp\_loc (0203h), while KI is similarly set by two registers, tim\_ki\_acq (0200h) and tim\_ki\_loc (0202h). Depending on whether the device operates in acquisition or locked mode either "\_acq" or "\_lock" registers are selected. Register demod\_lock\_c (023Eh) is used internally to automatically switch from acquisition parameters to lock parameters.

Timing offset can be computed from the timing corr c (0208h) register according to the following formula:

TimingOffset (in ppm) =

$$-10^6$$

x timing\_corr\_c / (timing\_corr\_c +  $2^{20}$ )

With the default values of the loop parameters, the timing acquisition range of this loop is typically ±3000 ppm.

In addition to the above mentioned loop, a coarse timing recovery function is also provided which allows enlarging the timing acquisition range up to ±25% of the symbol rate. This feature is used for blind scanning of the band and its use is described in a forthcoming application note.

### 3.6.2.4. Carrier Recovery Loop

The carrier recovery block implements a phase detector and a programmable second-order loop filter and allows recovery of the carrier phase at the output of the equalizer. The loop parameters (loop bandwidth & damping factor) are programmable for acquisition and tracking modes:

The damping factor formula is:

$$Df = 2^{(KP - (KI/2) - 11)} \times SQRT(\pi \times 360)$$

The normalized loop bandwidth formula is:

BI. Ts =

$$2^{((KI/2) - 10)} x (Df + 0.25 / Df) x SQRT(\pi x 90)$$

KP is user-defined by two registers, **kp\_acq (0238h)** and **kp\_lock (023Ah)**, while KI is similarly set by two registers, **ki\_acq (0239h)** and **ki\_lock (023Bh)**. Depending on whether the device operates in acquisition or locked mode, either "\_acq" or "\_lock" registers are selected. Register **demod\_lock\_c (023Eh)** is used internally to automatically switch from acquisition parameters to lock parameters.

A readout for carrier frequency offset is available and given by the **phase\_cor\_c (0240h)** register according to the following formula:

In addition to this loop, a programmable frequency sweep can be performed to enlarge the maximum frequency offset that the device is able to recover (up to 11% of the required symbol rate). The initial value of the carrier frequency sweep is set via register **sweep\_init (0230h)** according to the following formula:

The range of the carrier frequency sweep is set via register **sweep\_range (0231h)** according to the following formula:

SweepRange (in Hz) = DVB rate (in Hz) x sweep range

$$/ 256$$

The speed of the carrier frequency sweep is set via register **sweep\_step (0232h)**. For each symbol, the frequency is incremented by:

SweepStep (in Hz) = DVB rate (in Hz) x sweep step

$$/ 2^{24}$$

When the carrier recovery loop has converged, the sweep carrier frequency offset correction is given by register freq corr c (0234h):

The total carrier frequency offset is the sum of FrequencyOffset + SweepFrequencyOffset.

### 3.6.2.5. Demod Status

Si2165 indicates if the DVB-C demodulator is locked in register demod\_lock\_c (023Eh).

### 3.6.2.6. Reacquisition (Auto Re-lock) for DVB-C

In DVB-C mode, if lock is lost for a time longer than a programmable timeout value, the device performs an automatic soft reset. The reset time after unlock is programmable via the **lock\_timeout (00C4h)** register. The auto relock function is enabled via the **auto\_reset (00CBh)** register.

### 3.6.2.7. Equalizer for DVB-C

The time equalizer operates on 32 QAM symbols (31 taps) and consists of a feed-forward part (FFE) and a feed-back part (DFE).

The length of the FFE part is programmable via register **ffe\_length (0260h)**, and the DFE part uses the remaining taps. The central tap position of the FFE is set with register **central\_tap (0261h)** and must be less than the FFE length.

Equalizer coefficient adaptation is performed by two different algorithms depending on whether the carrier has been recovered:

- As long as the carrier recovery is not locked, a Constant Modulus Algorithm is used, and FFE coefficients are adapted using the adaptation step programmed in register **gain\_cma (0264h)**.

- Once the carrier has been recovered a Decision Directed Algorithm is used, and both FFE and DFE coefficients

are adapted using the adaptation steps programmed in registers gain\_ddffe (0264h) and gain\_dddfe (0265h).

It is strongly recommended to set the **auto\_algo (0278h)** register to "dfe\_init" value, in order to automatically recover lock status in case of any de-synchronization.

An estimation of the signal-to-noise ratio at the output of the equalizer is provided in register **c\_n** (026Ch), and the actual value of C/N in dB is given by the following formula:

$$C/N$$

(in dB) = 10 x log10 ( $2^{24}/c_n$ )

### 3.6.2.8. Scanning Procedure for DVB-C

The complete digital cable channel scan procedure is detailed in a forthcoming application note.

### 3.7. Forward Error Correction

### 3.7.1. DVB-T/H

For DVB-T/H, the FEC section consists of inner and outer FEC. Refer to Functional Description for additional detail. Si2165 does not include decoding of the additional MPE-FEC layer for mobile DVB-H reception. However for DVB-H reception with fixed receivers, decoding of the MPE FEC layer is not required. The FEC for DVB-T/H is automatically configured.

### 3.7.2. DVB-C

For DVB-C, the FEC section does not require any user-specific configuration (unless changing default settings of packet synchronization).

### 3.7.3. Lock Status and Performance Indicators

### 3.7.3.1. Device Status

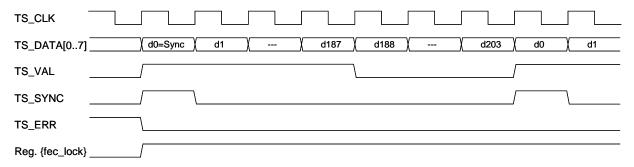

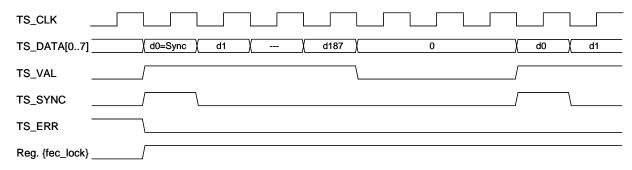

The Si2165 provides readouts for both packet and FEC lock. In DVB-C mode, packet synchronization is performed via a correlation search on the SYNC (0x47 / 0xB8) byte of the TS packet.

In DVB-C mode, packet synchronization searches for the regular occurrence of 0x47/0xB8 SYNC bytes within the stream. The number of consecutive occurrences to generate a lock status can be set in register **ps\_sync\_thr** (044Dh). Once locked, register **ps\_superv\_thr** (044Eh) sets the number of consecutive missed occurrences to generate an unlock status. If required when locked, register **ps\_stay\_locked** (0448h) allows the lock state to be maintained.

| Lock Indicators             | Registers        |

|-----------------------------|------------------|

| Packet Synchronization lock | ps_lock (0440h)  |

| F.E.C. lock                 | fec_lock (04E0h) |

In DVB-T/H mode, packet synchronization is automatically achieved since the frame contains an integral number of TS packets.

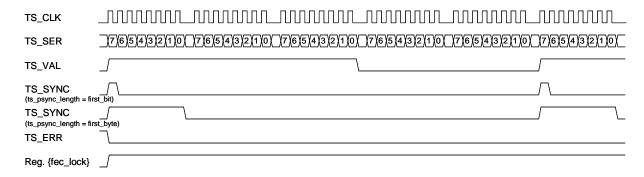

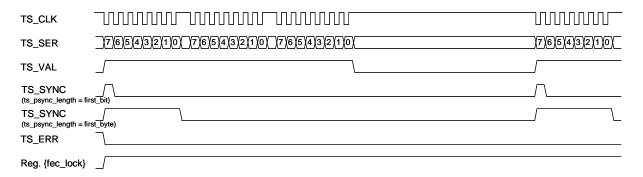

Register ts\_before\_lock (04E4h) can be programmed to optionally hold the TS output bus quiet, forcing it to 0, when there is no FEC lock. In that case, the signalization signals (TS\_SYNC, TS\_VAL) are also forced to 0, but then TS\_CLK remains active.

### 3.7.3.2. Performance Indicators

#### ■ CBER

The Viterbi decoder provides Channel Bit Error Rate (CBER) monitoring information. The computation method consists of re-encoding the output of the Viterbi decoder and comparing the re-encoded bits to the delayed hard decisions at the input of the Viterbi decoder.

The error rate monitoring mechanism is as follows:

- cber\_bit (0428h) register value provides the number of bits to take into account for one computation period.

- cber\_err (0430h) register value provides the number of erroneous bits found over the computation period.

- The final CBER ratio computation is then defined by the following formula:

$$CBER = \frac{CBER\_ERR}{CBER\ BIT}$$

- Register cber\_rst (0424h) is used to reset the error counters and start a new computation period.

- Status register cber\_avail (0434h) indicates that the computation period is over after a CBER reset (or after device reset).

### ■ BER

The Reed-Solomon decoder allows monitoring of input Bit Error Rate (BER).

The error rate monitoring mechanism is as follows:

- ber\_pkt (0470h) register value provides the number of RS packets to take into account for one computation period.

- ber\_bit (0478h) register value provides the number of erroneous bits found over the computation period.

- The final BER computation is then defined by the following formula:

$$BER = \frac{BER\_BIT}{BER\_PKT \times 204 \times 8}$$

- Register ber\_rst (046Ch) is used to reset the error counter and start a new computation period.

- Status register ber\_avail (047Ch) indicates that the computation period is over after a BER reset (or a device reset).

#### ■ PER

The Reed-Solomon decoder allows monitoring of output Packet Error Rate (PER).

The error rate monitoring mechanism is as follows:

- per\_pkt (0484h) register value provides the number of RS packets to take into account for one computation period.

- per (048Ch) register value provides the number of erroneous packets found over the computation period

- The final PER computation is then defined by the following formula:

$$PER = \frac{PER}{PER\_PKT}$$

- Register per\_rst (0480h) is used to reset the error counter and start a new computation period.

- Status register per avail (0490h) indicates that the computation period is over after a PER reset (or a device reset).

- UNCOR Counter

In addition, the Reed Solomon decoder also offers a way to monitor the occurrence of uncorrectable packets over a flexible period of time.

Register **uncor\_cnt** (0468h) provides the number of uncorrectable RS packets after a reset up to its saturation value of 255, until the next reset via register **uncor rst** (0464h).

## 3.8. System Control

### 3.8.1. Power Supply Ramp-Up / Ramp-Down Sequence

Si2165 requires only two industry-standard power supplies: 1.2 and 3.3 V.  $V_{DD\_VIO}$  is usually set to 3.3 V, but 1.8 or 2.5 V can be substituted as well. There is no specific power-up/power-down sequencing with regards to  $V_{DD\_VCORE}$ ,  $V_{DD\_VIO}$ ,  $V_{DDH\_VANA}$ , and  $V_{DD\_VADC}$  supplies. However, it is recommended that RESETB be held low while the supplies are powered up in order to prevent potential bus conflicts on the I/O pins of the Si2165. Once the supplies have stabilized to their nominal voltages, RESETB can be brought high. Also, if  $V_{DD\_VCORE}$  is turned off to enter a low power state, the RESETB pin must be brought and held low while  $V_{DD\_VCORE}$  is off to put the Si2165 into a state with the lowest possible power consumption.

### 3.8.2. Initialization Procedure

#### 3.8.2.1. Hard Reset

Pin RESETB, active low, resets all the logic and sets all internal registers to their respective default values. Any pre-loaded DSP firmware patch would need to be reloaded.

After power-on reset, all output signals i.e. TS\_DATA[0..7], AGC\_IF, AGC\_RF and GPIO\_0 are left in high-impedance (tri-state) mode.

The following registers provide individual output-enable control of output signals on pins TS\_DATA[0..7], TS\_SYNC, TS\_ERR, TS\_VAL, TS\_CLK, AGC\_IF, AGC\_RF and GPIO\_0: ts\_data0\_tri (04EFh) to ts\_data7\_tri (04EFh), ts\_sync\_tri (04F0h), ts\_err\_tri (04F0h), ts\_val\_tri (04F0h), ts\_clk\_tri (04F0h), agc\_if\_tri (018Bh), agc\_rf\_tri (018Dh), and gpio0\_tri (05C1h).

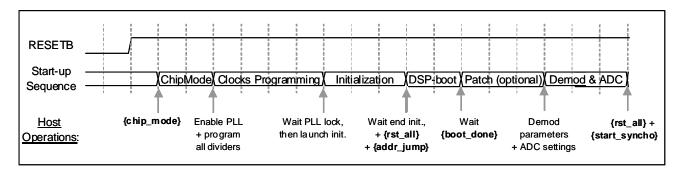

### 3.8.2.2. Device Initialization Sequence

Si2165 device requires an initialization procedure that includes internal calibration. This must be done after each power-on reset and will take less than 10 ms to be completed.

### **Step 1: System Configuration**

Consists of programming the **chip\_mode (0000h)** register. This register releases the Si2165 from standby mode and specifies the clock source type on which the chip will rely.

### Step 2: PLL Setup

Internal clocks frequencies have to be set properly according to the frequency of the reference clock/crystal. This is done by enabling the PLL via pll\_enable (00A2h), then accessing the pll\_divl (00A0h), pll\_divm (00A1h), pll\_divn (00A2h), pll\_divp (00A2h), and pll\_divr (00A3h) registers.

### Step 3: Initialization Procedure

In order to launch the initialization mode, user should activate register chip init (0050h) then start init (0096h).

The user should then either monitor register **init\_done (0054h)** until the status shows "completed" or wait for a fixed timeout (5 ms typical, depending on the sys\_clk frequency).

Then, the user should return to normal device functional mode by again appropriately programming the **chip\_init** (0050h) register and issue one software reset via register **rst\_all** (00C0h).

### Step 4: Start DSP

For DVB-T/H operation, the DSP should now be started by programming register **addr\_jump (0348h)**. This 32-bit register determines the memory address to jump to, when the firmware is available in memory (default value is F4000000h).

In case a DSP firmware patch is necessary, it should be downloaded via I<sup>2</sup>C transactions after the DSP boot (refer to "3.8.3.1. DSP Boot" for the indication of DSP boot completion).

For DVB-C demodulation, usually, no firmware patch is necessary, and, in this case, the DSP can be parked by setting register **addr\_jump (0348h)** to 0. The DSP block can also be turned off, thus saving some power consumption, by modifying register **dsp\_clock (0104h)**. If a downloaded firmware patch is recommended for DVB-C demodulation, then the on-chip DSP shall always remain active.

### Step 5: Demodulation Parameters and ADC Settings

Finally, the desired standard and appropriate related IF parameters must be set using registers:

standard (00ECh), adc\_sampling\_mode (00E0h), if\_freq\_shift (00E8h), and oversamp (00E4h), which are common to both DVB standards.

The recommended and optimized ADC settings are as follows:

- 1. Set adc ri1 (012Ah): 0x46

- 2. Set adc ri3 (012Ch): 0x00

- 3. Set adc ri5 (012Eh): 0x0A

- 4. Set adc ri6 (012Fh): 0xFF

- 5. Set adc\_ri8 (0123h): 0x70

Then, bandwidth (0308h) is specific to DVB-T/H, or req\_constellation (02F4h) is specific to DVB-C.

End the procedure by applying a soft reset procedure as described in "3.8.2.3. Soft Reset Procedure".

The startup sequence is summarized in Figure 9.

Figure 9. Initialization Sequence

### 3.8.2.3. Soft Reset Procedure

Register **rst\_all (00C0h)** is used to perform a soft reset that re-initializes all the Si2165 logic, except the internal registers. Any preloaded DSP firmware patch is not affected by a soft reset. A soft reset is mandatory before attempting to achieve the first demodulator lock.

Then, a new synchronization has to be launched via the **start synchro (02E0h)** register.

**Note:** Intensively applying soft reset commands on the Si2165 device will not freeze its proper operation (after the next synchronization start).

### 3.8.3. DSP Operations

### 3.8.3.1. DSP Boot

Register boot done (0341h) indicates whether the DSP boot process has been successful or is still in-progress.

### 3.8.3.2. DSP Watchdog

In the unlikely event that the DSP locks and automatically reboots as the result of an action from the internal watchdog, the **wdog\_error** (0341h) register provides an indicator that such a reboot has occurred.

The user can reset this error using the rst\_wdog\_error (0341h) register.

### 3.8.3.3. Patch Identification

In case a firmware patch has been downloaded into RAM, the patch code version can be identified by reading register **patch\_version (0344h)**.

DSP patch compilation generates a CRC key that can be compared, after downloading, to the CRC key computed inside Si2165. Readout of the 16-bit key is found in register **crc (037Ah)**.

Register rst crc (0379h) allows resetting the CRC key within the device.

### 3.8.4. Standby Mode

### 3.8.4.1. Software Power-down

Register **chip\_mode (0000h)** allows configuration of the Si2165 in such a way that all logic inside the device becomes inactive with the exception of the I<sup>2</sup>C block (but not affecting the programmed register values or any preloaded DSP firmware patch).

The proper sequence to set Si2165 in power down mode is as follows:

- 1. Stop the clock of the DSP through register dsp\_clock (0104h).

- 2. Set Si2165 in stand-by mode via register chip\_mode (0000h).

The proper sequence to recover from above power-down mode is as follows:

- 1. Set Si2165 in operating mode via register chip\_mode (0000h).

- 2. Start the clock of the DSP through register dsp\_clock (0104h).

## 3.8.4.2. Shutting Off V<sub>DD VCORE</sub> Alone

If the application needs to power down only the  $V_{DD\_VCORE}$  (1.2 V) supply while still keeping the  $V_{DD\_VIO}$  (typically 1.8, 2.5, or 3.3 V) active, the *RESETB pin must stay low at all times while*  $V_{DD\_VCORE}$  *is turned-off.*

# 4. MPEG Transport Stream Bus

Si2165 supports three output modes. However, only one output bus mode can be active at any given time:

- TS master parallel: Si2165 outputs TS\_CLK and TS\_DATA over an 8-bit parallel data bus

- TS master serial: Si2165 outputs TS\_CLK and TS\_DATA over a 1-bit serial data bus

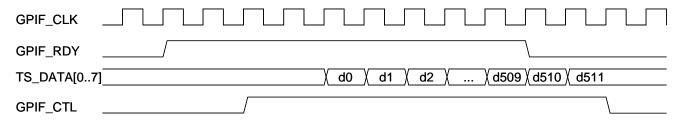

- TS slave parallel GPIF (general purpose interface): Si2165 indicates when data is buffered in its internal FIFO. An external device polls data by providing a clock/strobe signal. Si2165 provides data over an 8-bit parallel data bus.

The MPEG Transport Stream (TS) output interface carries the decoded terrestrial/cable data to external devices for further MPEG decoding. The MPEG-TS output interface consists of the following pins for each mode:

| Pin | Pin Name            | TS Serial Mode                       | TS Parallel Mode                     | GPIF: TS Slave Parallel<br>Mode |

|-----|---------------------|--------------------------------------|--------------------------------------|---------------------------------|

| 7   | TS_VAL / GPIF_CLK   | TS valid data signal                 | TS valid data signal                 | GPIF clock                      |

| 8   | TS_SYNC / GPIF_RDY  | TS synchro / frame start signal      | TS synchro / frame start signal      | GPIF ready signal               |

| 9   | TS_CLK / GPIF_CTL   | TS clock                             | TS clock                             | GPIF control signal             |

| 11  | TS_DATA[0] / TS_SER | TS serial data stream                | TS parallel output bit #0            | TS parallel output bit #0       |

| 12  | TS_DATA[1] / GPIO_1 | Unused (can be GPIO #1)              | TS parallel output bit #1            | TS parallel output bit #1       |

| 13  | TS_DATA[2] / GPIO_3 | Unused (can be GPIO #3)              | TS parallel output bit #2            | TS parallel output bit #2       |

| 14  | TS_DATA[3] / GPIO_4 | Unused (can be GPIO #4)              | TS parallel output bit #3            | TS parallel output bit #3       |

| 16  | TS_DATA[4] / GPIO_5 | Unused (can be GPIO #5)              | TS parallel output bit #4            | TS parallel output bit #4       |

| 17  | TS_DATA[5]          | Unused                               | TS parallel output bit #5            | TS parallel output bit #5       |

| 18  | TS_DATA[6]          | Unused                               | TS parallel output bit #6            | TS parallel output bit #6       |

| 20  | TS_DATA[7]          | Unused                               | TS parallel output bit #7            | TS parallel output bit #7       |

| 21  | TS_ERR / GPIO_2     | TS packet error indicator or GPIO #2 | TS packet error indicator or GPIO #2 | Unused signal or GPIO #2        |

Table 6. Three Main TS Modes and Pin Assignment

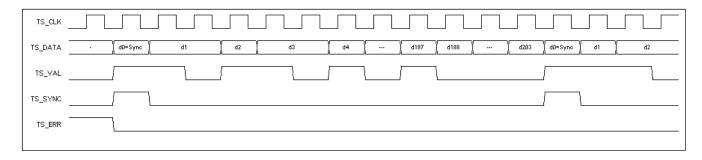

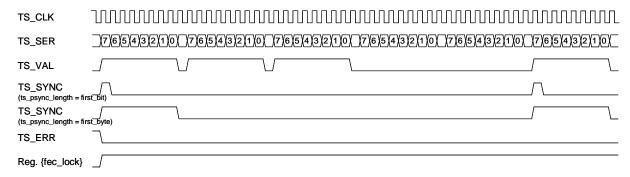

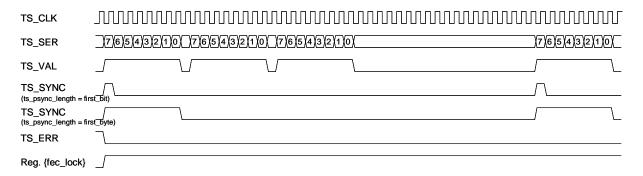

In parallel mode, TS\_DATA[0..7] carries the TS stream. In serial mode, TS\_SER / TS\_DATA[0] carries the TS stream.

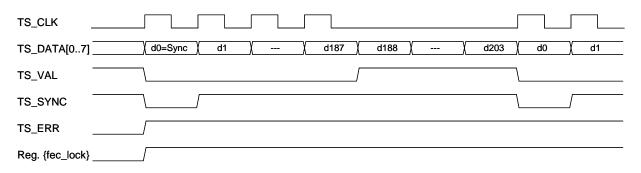

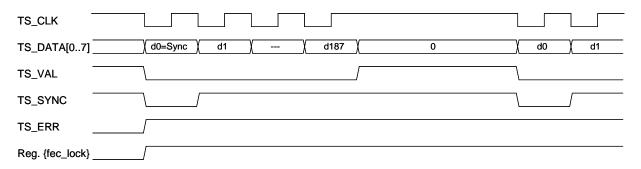

In master mode: TS\_CLK, TS\_SYNC, TS\_VAL, and TS\_ERR signals are available.

- TS CLK is the MPEG TS clock output.

- TS\_SYNC output is active during the first byte of each TS packet. TS\_SYNC is only active when TS synchronization exists.

- TS\_VAL output is used to indicate when valid data is present. TS\_VAL is active during the MPEG-TS payload packet data (188 bytes per TS packet) and inactive during Reed-Solomon parity packet data (16 bytes per TS packet) or when there is no TS synchronization. Note also that there will be clock periods during which TS\_VAL will signal that no valid data is present, due to the fact that TS\_CLK does not equal the actual TS bit or byte clock.

- TS\_ERR output indicates that an uncorrectable error has been detected in the RS decoding stage and that the current TS data packet contains uncorrectable errors. The TS\_ERR output is active during the entire erroneous TS packet.

# 4.1. General TS Output Programmability (Available in All Bus Modes)

The programmability described in this section is available for all modes (master parallel, master serial, slave parallel).

Register **ts\_data\_sync\_overwr (04E4h)** provides the option to overwrite the sync byte. When enabled, all sync bytes received are replaced by 0x47 value. When "disabled", they are left unchanged.

Reed-Solomon parity bytes may be optionally forced to zero via register ts\_data\_parity (04E4h).

Register ts before lock (04E4h) provides the option to force TS data to zero as long as no FEC lock is obtained.

Register **ts\_data\_dir (04E4h)** allows changing the MSB-to-LSB bit order on the TS\_DATA bus in parallel mode. This ensures an easy routing of the Si2165 output irrespective of pin order on the host device. In serial mode, this register allows a selection between MSB-first and LSB-first serial output.

Register ts\_tei (04E4h) enables signaling of the Transport Error Indicator (TEI) bit, the MSB of the second byte of each TS packet. When signaling is "enabled", the TEI bit is set to "1" when an unrecoverable packet error has occurred. When "disabled", the TEI bit is always left unchanged.

After device power-on reset, all TS data and control signals are in tri-state mode as default.

The MPEG-TS data output pins are individually released from tri-state by using registers **ts\_data0\_tri (04EFh)** to **ts\_data7\_tri (04EFh)**.

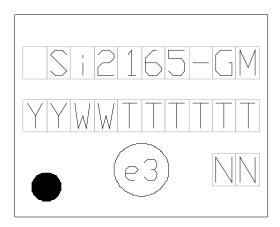

Similarly, registers ts\_clk\_tri (04F0h), ts\_sync\_tri (04F0h), ts\_err\_tri (04F0h), and ts\_val\_tri (04F0h) provide release from tri-state for control signals TS\_CLK, TS\_SYNC, TS\_ERR, and TS\_VAL.