## **Pin Description**

| Pin# | Pin Name  | Pin Type | Pin Description                                                                                                     |

|------|-----------|----------|---------------------------------------------------------------------------------------------------------------------|

| 1    | IREF      | Output   | Connect to 475-Ohm resistor to set HCSL output drive current                                                        |

| 2    | 100M_Q4-  | Output   | 100MHz HCSL output                                                                                                  |

| 3    | 100M_Q4+  | Output   | 100MHz HCSL output                                                                                                  |

| 4    | 100M_Q3-  | Output   | 100MHz HCSL output                                                                                                  |

| 5    | 100M_Q3+  | Output   | 100MHz HCSL output                                                                                                  |

| 6    | SCLK      | Input    | SMBus compatible input clock. Supports fast mode 400 kHz input clock                                                |

| 7    | SDATA     | I/O      | SMBus compatible data line                                                                                          |

| 8    | GND_25M   | Power    | Ground for 25MHz output                                                                                             |

| 9    | 25M_OUT1  | Output   | 25MHz LVCMOS output. When disabled, output is trisated and has a normal 110kOhm pull-down                           |

| 10   | 25M_OUT2  | Output   | 25MHz LVCMOS output. When disabled, output is trisated and has a normal 110kOhm pull-down                           |

| 11   | VDD_25M   | Power    | 3.3V supply for 25MHz output                                                                                        |

| 12   | GND_XTAL  | Power    | Ground for XTAL                                                                                                     |

| 13   | PDRESET   | Input    | Power on reset, when low all PLLs are powered down and output trisated. SMBus registers are reset to default values |

| 14   | X1        | Input    | Crystal input. Integrated 6pf capacitance                                                                           |

| 15   | X2        | Output   | Crystal output. Integrated 6pf capacitance                                                                          |

| 16   | VDD_XTAL  | Power    | 3.3V supply for XTAL                                                                                                |

| 17   | 100M_Q2-  | Output   | 100MHz HCSL output                                                                                                  |

| 18   | 100M_Q2+  | Output   | 100MHz HCSL output                                                                                                  |

| 19   | GNDO_100M | Output   | Ground for 100MHz output buffer                                                                                     |

| 20   | VDDO_100M | Power    | 3.3V supply for 100MHz output buffer                                                                                |

| 21   | VDDO_100M | Power    | 3.3V supply for 100MHz output buffer                                                                                |

| 22   | GNDA      | Power    | Ground for 100MHz related PLL                                                                                       |

| 23   | VDDA      | Power    | 3.3V supply for 100MHz related PLL                                                                                  |

| 24   | 100M_Q1-  | Output   | 100MHz HCSL output                                                                                                  |

| 25   | 100M_Q1+  | Output   | 100MHz HCSL output                                                                                                  |

| 26   | 100M_Q0+  | Output   | 100MHz HCSL output                                                                                                  |

| 27   | 100M_Q0-  | Output   | 100MHz HCSL output                                                                                                  |

| 28   | GNDO_100M | Power    | Ground for 100MHz output buffer                                                                                     |

# Serial Data Interface (SMBus)

PI6C49015 is a slave only SMBus device that supports indexed block read and indexed block write protocol using a single 7-bit address and read/write bit as shown below.

#### **Address Assignment**

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0/1 |

#### **How to Write**

| 1 bit        | 8 bits | 1   | 8 bits             | 1   | 8 bits            | 1   | 8 bits         | 1   |     | 8 bits             | 1   | 1 bit       |

|--------------|--------|-----|--------------------|-----|-------------------|-----|----------------|-----|-----|--------------------|-----|-------------|

| Start<br>bit | d2H    | Ack | Register<br>offset | Ack | Byte<br>Count = N | Ack | Data Byte<br>0 | Ack | ••• | Data Byte<br>N - 1 | Ack | Stop<br>bit |

#### Note:

#### How to Read (M: abbreviation for Master or Controller; S: abbreviation for slave/clock)

| 1 bit              | 8<br>bits           | 1 bit              | 8<br>bits                                                           | 1 bit              | 1 bit              | 8<br>bits           | 1 bit              | 8<br>bits                                                                | 1 bit              | 8<br>bits                                         | 1 bit              | <br>8<br>bits                                | 1 bit                           | 1 bit             |

|--------------------|---------------------|--------------------|---------------------------------------------------------------------|--------------------|--------------------|---------------------|--------------------|--------------------------------------------------------------------------|--------------------|---------------------------------------------------|--------------------|----------------------------------------------|---------------------------------|-------------------|

| M:<br>Start<br>bit | M:<br>Send<br>"D2h" | S:<br>sends<br>Ack | M:<br>send<br>start-<br>ing<br>data-<br>byte<br>loca-<br>tion:<br>N | S:<br>sends<br>Ack | M:<br>Start<br>bit | M:<br>Send<br>"D3h" | S:<br>sends<br>Ack | S:<br>sends<br># of<br>data<br>bytes<br>that<br>will<br>be<br>sent:<br>X | M:<br>sends<br>Ack | S:<br>sends<br>start-<br>ing<br>data<br>byte<br>N | M:<br>sends<br>Ack | <br>S:<br>sends<br>data<br>byte<br>N+X-<br>1 | M: Not<br>Ac-<br>knowl-<br>edge | M:<br>Stop<br>bit |

## **Byte 0: Spread Spectrum Control Register**

| Bit    | Description                                                                                             | Туре | Power Up<br>Condition | Output(s)<br>Affected                 | Notes                                    |

|--------|---------------------------------------------------------------------------------------------------------|------|-----------------------|---------------------------------------|------------------------------------------|

| 7      | Spread Spectrum Selection for 100 MHz HCSL PCI-Express clocks                                           | RW   | 0                     | All 100MHz HCSL<br>PCI Express output | 0=spread off<br>1 = -0.5% down<br>spread |

| 6      | Enables hardware or software control of OE bits (see Byte 0–Bit 6 and Bit 5 Functionality table)        | RW   | 0                     | PD_RESET pin, bit 5                   | 0 = hardware cntl<br>1 = software ctrl   |

| 5      | Software PD_RESET bit. Enables or disables all outputs (see Byte 0–Bit 6 and Bit 5 Functionality table) | RW   | 1                     | All outputs                           | 0 = disabled<br>1 = enabled              |

| 4 to 1 | Reserved                                                                                                | RW   | Undefined             | Not Applicable                        |                                          |

| 0      | OE for 25M_Out2                                                                                         | RW   | 1                     | 25M_Out2                              | 0 = disabled<br>1 = enabled              |

<sup>1.</sup> Register offset for indicating the starting register for indexed block write and indexed block read. Byte Count in write mode cannot be 0.

# Byte 0 - Bit 6 and Bit 5 Functionality

| Bit 6 | Bit 5 | Description                                                                           |

|-------|-------|---------------------------------------------------------------------------------------|

| 0     | X     | PD_RESET HW pin/signal = enabled                                                      |

| 1     | 0     | Disables all outputs and tri-states the outputs, PD_RESET HW pin/signal = DO NOT CARE |

| 1     | 1     | Enable all outputs, PD_RESET HW pin/signal = DON'T CARE                               |

# **Byte 1: Control Register**

| Bit    | Description                | Туре | Power Up Condition | Output(s) Affected | Notes                       |

|--------|----------------------------|------|--------------------|--------------------|-----------------------------|

| 7      | Reserved                   | RW   | Undefined          | Not Applicable     |                             |

| 6      | OE for 25M_Out1            | RW   | 1                  | 25M_Out1           | 0 = disabled<br>1 = enabled |

| 5      | Reserved                   | RW   | Undefined          | Not Applicable     |                             |

| 4      | OE for 100M_Q4 HCSL output | RW   | 1                  | 100M_Q4            | 0=disable<br>1 = enabled    |

| 3      | Reserved                   | RW   | Undefined          | Not Applicable     |                             |

| 2      | OE for 100M_Q3 HCSL output | RW   | 1                  | 100M_Q3            | 0=disable<br>1 = enabled    |

| 1 to 0 | Reserved                   | RW   | Undefined          | Not Applicable     |                             |

# **Byte 2: Control Register**

| Bit    | Description | Туре | Power Up Condition | Output(s) Affected | Notes |

|--------|-------------|------|--------------------|--------------------|-------|

| 7 to 5 | Reserved    | RW   | Undefined          | Not Applicable     |       |

| 4 to 0 | Reserved    | R    | Undefined          | Not Applicable     |       |

# **Byte 3: Control Register**

| Bit    | Description                                      | Туре | Power Up<br>Condition | Output(s) Affected | Notes        |

|--------|--------------------------------------------------|------|-----------------------|--------------------|--------------|

| 7      | OE for 100M_Q2 HCSL Output                       | RW   | 1                     | 100M_Q2            | 0 = disabled |

|        | 02 101 10011_ <b>\( 2</b> 11002 0 <b>u.</b> p u. | 2000 |                       | 10011_42           | 1 = enabled  |

| 6 to 3 | Reserved                                         | RW   | Undefined             | Not Applicable     |              |

| 2      | OE for 100M_Q1 HCSL Output                       | RW   | 1                     | 100M_Q1            | 0 = disabled |

| 2      | OE for 100M_Q1 HCSL Output                       | KVV  |                       | 100M_Q1            | 1 = enabled  |

| 1      | OF for 100M ON HOST Ordans                       | DIA  | 1                     | 100M 00            | 0 = disabled |

| 1      | OE for 100M_Q0 HCSL Output                       | RW   |                       | 100M_Q0            | 1 = enabled  |

| 0      | Reserved                                         | R    | Undefined             | Not Applicable     |              |

# Byte 4 & 5: Control Register

| Bit    | Description | Туре | Power Up Condition | Output(s) Affected | Notes |

|--------|-------------|------|--------------------|--------------------|-------|

| 7 to 0 | Reserved    | R    | Undefined          | Not Applicable     |       |

# **Byte 6: Control Register**

| Bit | Description       | Туре | Power Up Condition | Output(s) Affected | Notes |

|-----|-------------------|------|--------------------|--------------------|-------|

| 7   | Revision ID bit 3 | R    | 1                  | Not Applicable     |       |

| 6   | Revision ID bit 2 | R    | 0                  | Not Applicable     |       |

| 5   | Revision ID bit 1 | R    | 0                  | Not Applicable     |       |

| 4   | Revision ID bit 0 | R    | 0                  | Not Applicable     |       |

| 3   | Vendor ID bit 3   | R    | 0                  | Not Applicable     |       |

| 2   | Vendor ID bit 2   | R    | 0                  | Not Applicable     |       |

| 1   | Vendor ID bit 1   | R    | 1                  | Not Applicable     |       |

| 0   | Vendor ID bit 0   | R    | 1                  | Not Applicable     |       |

## Absolute Maximum Ratings¹ (Over operating free-air temperature range)

| Parameters                             | Min. | Max. | Units |

|----------------------------------------|------|------|-------|

| Storage Temperature                    | -65  | 150  | °C    |

| Ambient Temperature with Power Applied | -40  | 85   |       |

| 3.3V Analog Supply Voltage             | -0.5 | 4.6  | V     |

| ESD Protection (HBM)                   |      | 2000 | T v   |

#### Note:

## **Recommended Operating Conditions**

| Symbol                             | Parameters                                             | Test Condition         | Min. | Тур. | Max. | Units |

|------------------------------------|--------------------------------------------------------|------------------------|------|------|------|-------|

| $V_{_{ m DD}}$                     | Power supply                                           |                        | 3.0  | -    | 3.6  | V     |

| $I_{DD}$                           | Total Power Supply Current                             | All outputs unloaded   | -    | 1    | 65   | mA    |

| I <sub>DD</sub> _Output Tri-stated | Total power supply current with tri-<br>stated outputs | OE = "0", no load      | -    | -    | 42   | mA    |

| I <sub>DD Power-Down</sub>         | Total power supply current in power down mode          | PD_RESET= "0", no load | -    | -    | 3.8  | mA    |

| T <sub>A</sub>                     | Operating temperature                                  |                        | -40  | -    | +85  | °C    |

## **LVCMOS DC Electrical Characteristics**

Over Operating Conditions

| Symbol          | Parameter                        | Conditions                        | Min                    | Тур | Max                  | Units          |

|-----------------|----------------------------------|-----------------------------------|------------------------|-----|----------------------|----------------|

| $V_{_{ m IH}}$  | Input High Voltage               |                                   | 2                      | -   | V <sub>DD</sub> +0.3 |                |

| $V_{_{ m IL}}$  | Input Low Voltage                |                                   | -0.3                   | -   | 0.8                  | ] <sub>V</sub> |

| $V_{OH}$        | Output High Voltage              | $I_{OH} = -8mA$                   | $V_{\mathrm{DD}}$ -0.4 | -   | -                    | V              |

| $V_{OL}$        | Output Low Voltage               | $I_{OL} = 8mA$                    | -                      | -   | 0.4                  |                |

| $I_{_{ m IH}}$  | Input High Current               | $V_{\rm IN} = V_{\rm DD} - 0.1 V$ | -                      | -   | 45                   | 4              |

| $I_{_{ m IL}}$  | Input Low Current                | $V_{IN} = 0V$                     | -45                    | -   | -                    | μΑ             |

| R <sub>PU</sub> | Internal Pull-Up Resistance      | PDRESET                           | -                      | 216 | -                    | kOhm           |

| R <sub>DN</sub> | Internal Pull-Down<br>Resistance | 25M_OUT1, 25M_OUT2                | -                      | 110 | -                    | KOIIM          |

<sup>1.</sup> Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

### **HCSL DC Electrical Characteristics**

Over Operating Conditions

| Symbol                | Parameter                                           | Conditions                                                           | Min | Тур | Max | Units |

|-----------------------|-----------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|-------|

| $V_{OH}$              | Output High Voltage                                 |                                                                      | 660 | -   | 950 |       |

| V <sub>OL</sub>       | Output Low Voltage                                  |                                                                      | -   | -   | 150 | 1     |

| V <sub>CROSS</sub>    | Absolute Crossing<br>Point Voltages                 |                                                                      | 250 | -   | 550 | mV    |

| $\Delta V_{ m CROSS}$ | Total variation of V <sub>CROSS</sub> overall edges |                                                                      | -   | -   | 140 |       |

| $I_{OH}$              | Input High Current                                  | With 475-Ohm resistor connected between I <sub>REF</sub> pin and GND | -   | 12  | -   | mA    |

### **LVCMOS AC Electrical Characteristics**

Over Operating Conditions

| Symbol    | Parameter             | Conditions                            | Min | Тур | Max | Units |

|-----------|-----------------------|---------------------------------------|-----|-----|-----|-------|

| Fin       | Input Frequency       |                                       | -   | 25  | -   | MII   |

| Fout      | Output Frequency      | $C_{LOAD} = 15pF$                     | -   | 25  | -   | MHz   |

| $T_r/T_f$ | Output Rise/Fall time | $20\%$ of $V_{DD}$ to 80% of $V_{DD}$ | -   | -   | 1.2 | ns    |

| Toc       | Output Duty Cycle     |                                       | 45  | -   | 55  | %     |

| Tj        | Period Jitter         | 25 MHz clock output                   | -   | -   | 30  | ps    |

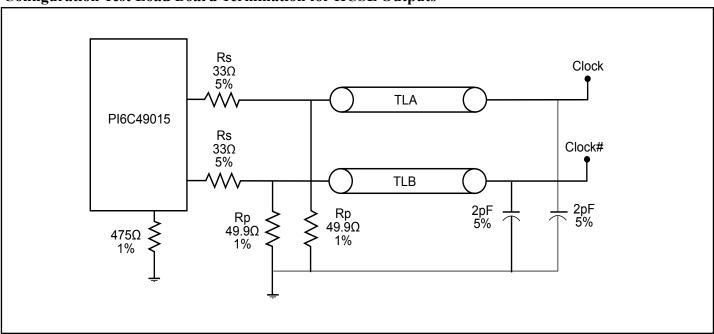

# HCSLAC Switching Characteristics<sup>1,2,3</sup>

Over Operating Conditions

| Symbol                          | Parameter                                    | Conditions                                | Min | Тур | Max | Units |

|---------------------------------|----------------------------------------------|-------------------------------------------|-----|-----|-----|-------|

| Four                            | Output Frequency                             | HCSL termination                          | -   | -   | 100 | MHz   |

| Tr/Tf                           | Output Rise/Fall time                        | Between 0.175V and 0.525V                 | 175 | -   | 700 | ps    |

| $\Delta T_r \! / \! \Delta T_f$ | Rise and Fall Time<br>Variation <sup>2</sup> |                                           | -   | -   | 125 | ps    |

| T <sub>DC</sub>                 | Output Duty Cycle <sup>3</sup>               |                                           | 47  | -   | 53  | %     |

| Tcj                             | Cycle-to-Cycle Jitter <sup>3</sup>           | Differential waveform                     | -   | -   | 70  | ps    |

| Трј                             | Peak-to-Peak Phase<br>Jitter                 | Using PCIe jitter measure-<br>ment method |     |     | 86  | ps    |

| J <sub>RMS2.0</sub>             | PCIe 2.0 RMS Phase<br>Jitter                 | PCIe 2.0 Test Method @ 100MHz Output      |     |     | 3.1 | ps    |

#### Notes:

- 1. Test configuration is Rs=33 $\Omega$ , Rp=49.9 $\Omega$ , and 2pF

- 2. Measurement taken from a single-ended waveform.

- 3. Measurement taken from a differential waveform.

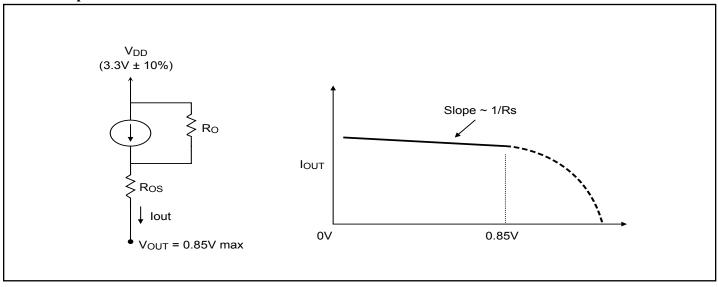

## **HCSL Output Buffer Characteristics**

## **HCSL Output Buffer Characteristics**

| Symbol           | Minimum     | Maximum     |

|------------------|-------------|-------------|

| $R_{\rm O}$      | 3000Ω       | N/A         |

| Ros              | unspecified | unspecified |

| V <sub>OUT</sub> | N/A         | 950mV       |

## **Configuration Test Load Board Termination for HCSL Outputs**

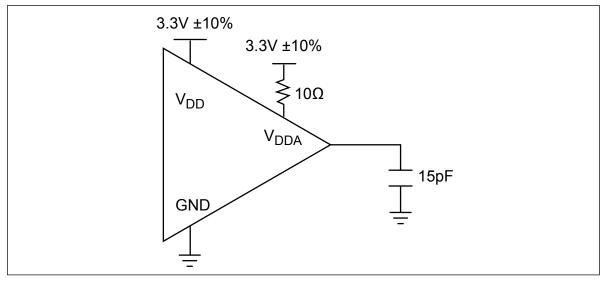

#### **LVCMOS Test Circuit**

## **Application Notes**

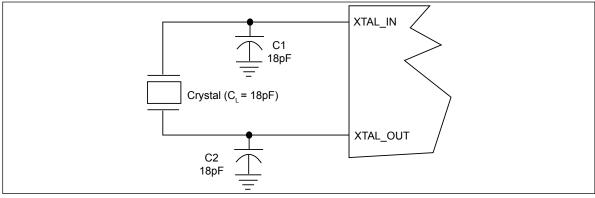

## **Crystal circuit connection**

The following diagram shows PI6C49015 crystal circuit connection with a parallel crystal. For the CL=18pF crystal, it is suggested to use C1= 18pF, C2= 18pF. C1 and C2 can be adjusted to fine tune to the target ppm of crystal oscillator according to different board layouts.

# **Crystal Oscillator Circuit**

# **Recommended Crystal Specification**

#### Pericom recommends:

- a) GC2500003 XTAL 49S/SMD(4.0 mm), 25M, CL=18pF, +/-30ppm, http://www.pericom.com/pdf/datasheets/se/GC\_GF.pdf

- b) FY2500081, SMD 5x3.2(4P), 25M, CL=18pF, +/-30ppm, http://www.pericom.com/pdf/datasheets/se/FY F9.pdf

- c) FL2500047, SMD 3.2x2.5(4P), 25M, CL=18pF, +/-20ppm, http://www.pericom.com/pdf/datasheets/se/FL.pdf

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

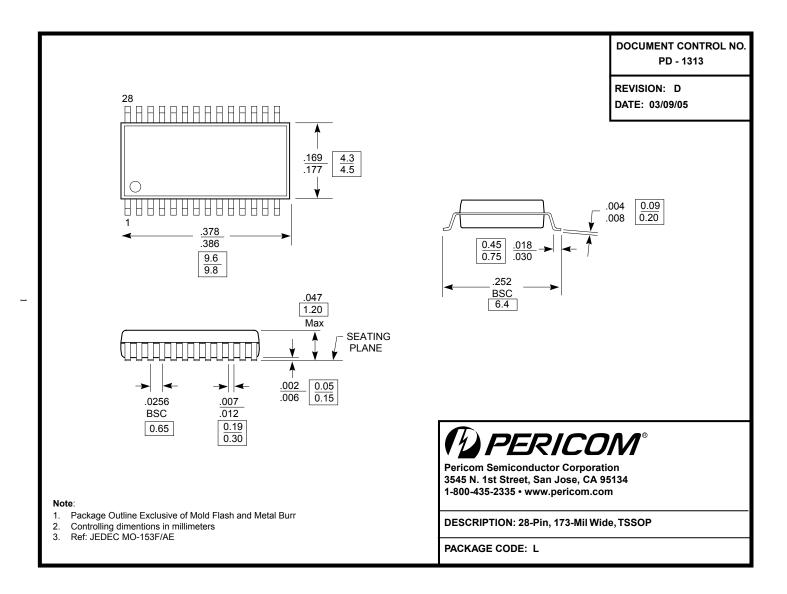

## Ordering Information(1-3)

| Ordering Code | Package Code | Package Description                  |

|---------------|--------------|--------------------------------------|

| PI6C49015LIE  | L            | 28 pin, Pb-free & Green, TSSOP (L28) |

#### Notes

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com