#### **ABSOLUTE MAXIMUM RATINGS**

| Positive Supply Voltage                               | +7V          |

|-------------------------------------------------------|--------------|

| Negative Supply Voltage                               |              |

| V+ to V                                               |              |

| Differential Input Voltage                            | +15V         |

| Input Voltage (Referred to V-)                        | 0.3V to +14V |

| Latch Pin Voltage                                     |              |

| Continuous Output Current                             | ±20mA        |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |              |

| 8-Pin Plastic DIP (derate 9.09mW/°C above             |              |

| 8-Pin SO (derate 5.88mW/°C above   | +/0°C)4/1mW            |

|------------------------------------|------------------------|

| 8-Pin µMAX (derate 4.5mW/°C abov   | /e +70°C)362mW         |

| 16-Pin Plastic DIP (derate 10.53mW | //°C above +70°C)842mW |

| 16-Pin Narrow SO (derate 8.70mW/   | °C above +70°C).696mW  |

| Operating Temperature Ranges:      |                        |

| MAX91_C                            | 0°C to +70°C           |

| MAX91_E                            | 40°C to +85°C          |

| Storage Temperature Range          | 65°C to +150°C         |

| and Temperature (coldering, 10c)   | ±300°C                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

V+ = +5V, V- = -5V, VQ = 1.4V, VLE = 0V, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                          | SYMBOL            | CONDITIONS                                 |                         | MIN  | TYP  | MAX  | UNITS |  |

|----------------------------------------------------|-------------------|--------------------------------------------|-------------------------|------|------|------|-------|--|

| Input Offset Voltage (Note 2)                      | Vos               | $R_S \le 100\Omega$                        | T <sub>A</sub> = +25°C  |      | 0.1  | 2    | m\/   |  |

| Input Offset Voltage (Note 2)                      |                   |                                            | TA = TMIN TO TMAX       |      |      | 3    | mV    |  |

| Offset Drift                                       | TCV <sub>OS</sub> |                                            |                         |      | 2    |      | μV/°C |  |

| Input Offset Current (Note 2)                      | los               | T <sub>A</sub> = +25°C                     |                         |      | 0.3  | 0.5  |       |  |

| Input Onset Current (Note 2)                       | los               | TA = TMIN TO T                             | MAX                     |      |      | 1    | μΑ    |  |

| Innut Dies Courset                                 | ΙB                | $T_A = +25^{\circ}C$                       |                         |      | 2    | 5    | μА    |  |

| Input Bias Current                                 |                   | C, E temperature ranges                    |                         |      |      | 8    |       |  |

| Input Voltage Range                                | VcM               | C, E temperature ranges                    |                         | -5.2 |      | +3.5 | V     |  |

| Input voltage hange                                | V CIVI            | Single +5V                                 | C, E temperature ranges | -0.2 |      | +3.5 | V     |  |

| Common-Mode Rejection Ratio                        | CMRR              | -5.0V ≤ V <sub>CM</sub> ≤ -                | +3.5V                   | 80   | 110  |      | dB    |  |

| Power-Supply Rejection Ratio                       | PSRR              | Positive supply; $4.5V \le V + \le 5.5V$   |                         | 60   | 85   |      | dB    |  |

| Tower-Supply Nejection Natio                       | 1 31111           | Negative supply; -2V ≥ V- ≥ -7V            |                         | 80   | 100  |      |       |  |

| Small-Signal Voltage Gain                          | Ay                | $1V \le V_Q \le 2V$ , $T_A = +25^{\circ}C$ |                         | 1500 | 3500 |      | V/V   |  |

|                                                    | V <sub>OH</sub>   | V+ ≥ 4.5V                                  | $I_{OUT} = 1mA$         | 2.7  | 3.4  |      | V     |  |

| Output Voltage                                     |                   |                                            | $I_{OUT} = 10mA$        | 2.4  | 3.0  |      |       |  |

| Output voltage                                     | V <sub>OL</sub>   | I <sub>SINK</sub> = 4mA                    |                         |      | 0.3  | 0.5  | ·     |  |

|                                                    |                   | $T_A = +25$ °C, $I_{SINK} = 10$ mA         |                         |      | 0.4  |      |       |  |

| Positive Supply Current Per<br>Comparator (Note 3) | l+                | C, E temperature ranges                    |                         |      | 6    | 10   | mA    |  |

| Negative Supply Current Per<br>Comparator (Note 3) | I-                |                                            |                         |      | 1    | 2    | mA    |  |

| Latch-Pin High Input Voltage                       | VIH               |                                            |                         | 2.0  |      |      | V     |  |

| Latch-Pin Low Input Voltage                        | VIL               |                                            |                         |      |      | 0.8  | V     |  |

| Latch-Pin Current                                  | lıL               | V <sub>LE</sub> = 0V                       |                         |      | -1   | -20  | μΑ    |  |

2 \_\_\_\_\_\_*NIXIV*I

#### **ELECTRICAL CHARACTERISTICS (continued)**

V+=+5V, V-=-5V,  $V_Q=1.4V$ ,  $V_{LE}=0V$ ,  $T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25$ °C.) (Note 1)

| PARAMETER                                        | SYMBOL                              | CONDITIONS                                                                  |                        | MIN    | TYP | MAX | UNITS |    |

|--------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------|------------------------|--------|-----|-----|-------|----|

|                                                  |                                     | $\Delta V_{IN} = 100 \text{mV},$                                            | $T_A = +25^{\circ}C$   |        |     | 10  | 14    |    |

| Propagation Delay (Note 4)                       | t <sub>PD+</sub> , t <sub>PD-</sub> | $V_{OD} = 5mV$                                                              | TA = TMIN TO TMAX      |        |     |     | 16    | ns |

|                                                  |                                     | $\Delta V_{IN} = 100 \text{mV},$<br>$V_{OD} = 20 \text{mV}$                 | T <sub>A</sub> = +25°C |        |     | 9   | 12    |    |

|                                                  |                                     |                                                                             | TA = TMIN TO TMAX      |        |     |     | 15    |    |

| Differential Propagation Delay                   | 4+                                  | $\Delta V_{IN} = 100 \text{mV},$                                            | T <sub>A</sub> = +25°C | MAX913 |     | 2   | 4     | 20 |

| (Note 4)                                         | Δt <sub>PD</sub>                    | $V_{OD} = 5mV$                                                              | 1A = +25 C             | MAX912 |     | 3   | 5     | ns |

| Channel-to-Channel Propagation<br>Delay (Note 4) |                                     | $\Delta V_{IN} = 100 \text{mV},$<br>$V_{OD} = 5 \text{mV}$<br>(MAX912 only) | $T_A = +25^{\circ}C$   |        |     | 500 |       | ps |

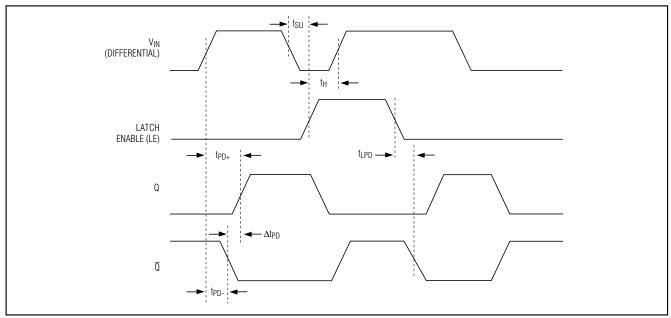

| Latch Setup Time (Note 5)                        | tsu                                 |                                                                             |                        |        | 2   | 0   |       | ns |

| Latch Hold Time (Note 5)                         | tH                                  |                                                                             | ·                      |        | 5   | 2   |       | ns |

| Latch Propagation Delay (Note 6)                 | t <sub>LPD</sub>                    |                                                                             |                        |        |     | 7   |       | ns |

- Note 1: All specifications are 100% tested at  $T_A = +25$ °C, unless otherwise noted. Specification limits over temperature ( $T_A = T_{MIN}$  to  $T_{MAX}$ ) are guaranteed by design.

- Note 2: Input Offset Voltage (V<sub>OS</sub>) is defined as the average of the two input offset voltages, measured by forcing first one output, then the other to 1.4V. Input Offset Current (I<sub>OS</sub>) is defined the same way.

- **Note 3:** Supply currents are measured with V<sub>Q</sub> driven to both V<sub>OH</sub> and V<sub>OL</sub> (not 1.4V).

- Note 4: Propagation Delay (tpD) and Differential Propagation Delay (ΔtpD) cannot be measured in automatic handling equipment with low input overdrive values. Characterization and correlation tests have shown that tpD and ΔtpD limits can be guaranteed by design. Electrical Characteristic DC tests are performed to guarantee that all internal bias conditions are correct. For low overdrive conditions, Vos is added to overdrive. Differential Propagation Delay is defined as ΔtpD = tpD+ tpD-.

- Note 5: Input latch setup time (t<sub>SU</sub>) is the interval in which the input signal must be stable prior to asserting the latch signal. The hold time (t<sub>H</sub>) is the interval after the latch is asserted in which the input signal must be stable. These parameters are guaranteed by design.

- Note 6: Latch Propagation Delay (t<sub>LPD</sub>) is the delay time for the output to respond when the latch-enable pin is deasserted (see *Timing Diagram*).

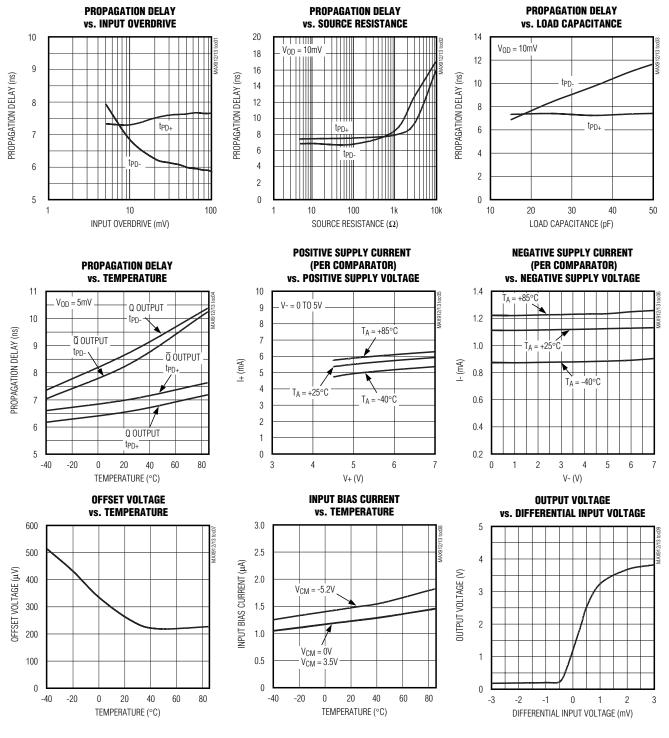

#### **Typical Operating Characteristics**

(V+ = +5V, V- = -5V,  $V_{LE}$  = 0V,  $C_{L}$  = 15pF,  $T_{A}$  = +25°C, unless otherwise noted.)

4 \_\_\_\_\_\_ **/\/\X\/**

### **Typical Operating Characteristics (continued)**

(V+ = +5V, V- = -5V,  $V_{LE}$  = 0V,  $C_{L}$  = 15pF,  $T_{A}$  = +25°C, unless otherwise noted.)

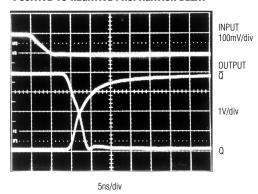

#### POSITIVE-TO-NEGATIVE PROPAGATION DELAY

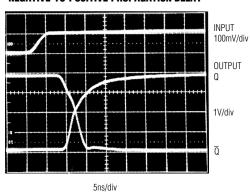

#### **NEGATIVE-TO-POSITIVE PROPAGATION DELAY**

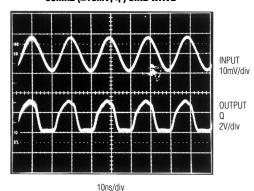

MAX912/MAX913 RESPONSE TO 50MHZ  $(\pm 10 mV_{P-P})$  SINE WAVE

. ., .

#### MAX912/MAX913 RESPONSE TO SLOW-MOVING TRIANGLE WAVE INDUSTRY-STANDARD MAX912/MAX913 RESPONSE **686 RESPONSE** INPUT INPUT 20mV/div 20mV/div OUTPUT OUTPUT 1V/div 1V/div 1V/div 1V/div 20µs/div 20µs/div

MIXIM

### **MAX912 Pin Description**

| PIN   | NAME | FUNCTION                                                                                                                                                     |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | QA   | Comparator A TTL Output                                                                                                                                      |

| 2     | QA   | Comparator A Complementary TTL Output                                                                                                                        |

| 3, 14 | GND  | Logic Ground. Connect <b>both</b> GND pins to ground.                                                                                                        |

| 4     | LEA  | Comparator A Latch Enable. QA and $\overline{\mathbb{Q}}$ A are latched when LEA is TTL high or floating. Comparator A latch is transparent when LEA is low. |

| 5, 12 | N.C. | No Connection. Not internally connected.                                                                                                                     |

| 6     | V-   | Negative Power Supply5V for dual supplies (bypass to GND with a 0.1µF capacitor) or GND for a single supply.                                                 |

| 7     | INA- | Comparator A Inverting Input                                                                                                                                 |

| 8     | INA+ | Comparator A Noninverting Input                                                                                                                              |

| 9     | INB+ | Comparator B Noninverting Input                                                                                                                              |

| 10    | INB- | Comparator B Inverting Input                                                                                                                                 |

| 11    | V+   | Positive Power Supply, +5V. Bypass to GND with a 0.1µF capacitor.                                                                                            |

| 13    | LEB  | Comparator B Latch Enable. QB and $\overline{\rm QB}$ are latched when LEB is TTL high or floating. Comparator B latch is transparent when LEB is low.       |

| 15    | ŪB   | Comparator B Complementary TTL Output                                                                                                                        |

| 16    | QB   | Comparator B TTL Output                                                                                                                                      |

### **MAX913 Pin Description**

| PIN | NAME | FUNCTION                                                                                                                            |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V+   | Positive Power Supply. Bypass to GND with a 0.1µF capacitor.                                                                        |

| 2   | IN+  | Noninverting Input                                                                                                                  |

| 3   | IN-  | Inverting Input                                                                                                                     |

| 4   | V-   | Negative Power Supply5V for dual supplies (bypass to GND with a 0.1µF capacitor) or GND for a single supply.                        |

| 5   | LE   | Latch Enable. Q and $\overline{Q}$ are latched when LE is TTL high or floating. The comparator latch is transparent when LE is low. |

| 6   | GND  | Logic Ground                                                                                                                        |

| 7   | Q    | TTL Output                                                                                                                          |

| 8   | Q    | Complementary TTL Output                                                                                                            |

#### **Detailed Description**

The MAX912 (dual) and MAX913 (single) high-speed comparators have a unique design that prevents oscillation when the comparator is in its linear region. No minimum input slew rate is required.

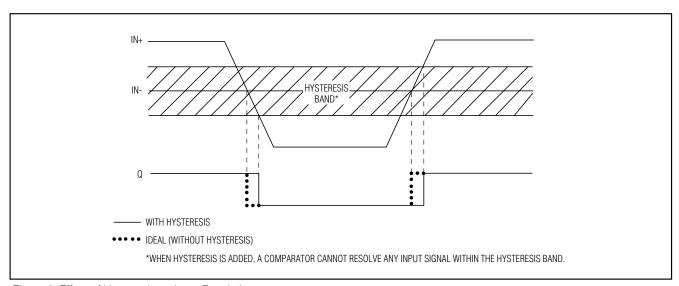

Many high-speed comparators oscillate in the linear region, as shown in the *Typical Operating Characteristics'* industry-standard 686 response graph. One way to overcome this oscillation is to sample the output after it has passed through the unstable region. Another practical solution is to add hysteresis. Either solution results in a loss of resolution and bandwidth.

Because the MAX912/MAX913 do not need hysteresis, they offer high resolution to all signals—including low-frequency signals.

The MAX912/MAX913 provide a TTL-compatible latch function that holds the comparator output state (Figure 1). As long as Latch Enable (LE) is high or floating, the input signal has no effect on the output state. With LE low, the outputs are controlled by the input differential voltage and the latch is transparent.

#### **Input Amplifier**

A comparator can be thought of as having two sections; an input amplifier and a logic interface. The MAX912/MAX913's input amplifier is fully differential with input offset voltage trimmed to below 2.0mV at

+25°C. Input common-mode range extends from 200mV **below** the negative supply rail to 1.5V below the positive power supply. The total common-mode range is 8.7V when operating from ±5VDC supplies.

The MAX912/MAX913's amplifier has no built-in hysteresis. For highest accuracy, do not add hysteresis. Figure 2 shows how hysteresis degrades resolution.

#### Resolution

A comparator's ability to resolve small signal differences—its resolution—is affected by various factors. As with most amplifiers, the most significant factors are the input offset voltage (Vos) and the common-mode and power-supply rejection ratios (CMRR, PSRR). If source impedance is high, input offset current can be significant. If source impedance is unbalanced, the input bias current can introduce another error.

For high-speed comparators, an additional factor in resolution is the comparator's stability in its linear region. Many high-speed comparators are useless in their linear region because they oscillate. This makes the differential input voltage region around 0V unusable, as does a high Vos. Hysteresis does not cure the problem, but acts to keep the input away from its linear range (Figure 2).

The MAX912/MAX913 do not oscillate in the linear region, which greatly enhances the comparator's resolution.

Figure 1. Timing Diagram

NIXIN

### Applications Information

#### **Power Supplies and Bypassing**

The MAX912/MAX913 are tested with  $\pm 5V$  power supplies that provide an input common-mode range (V<sub>CM</sub>) of 8.7V (-5.2V to +3.5V). Operation from a single +5V supply provides a common-mode input range of 3.7V (-0.2V to +3.5). Connect V- to GND for single-supply operation. The MAX912/MAX913 will operate from a minimum single-supply voltage of +4.5V.

The V+ supply provides power to both the analog input stage and digital output circuits, whereas the V- supply only powers the analog section. Bypass V+ and V- to ground with  $0.1\mu\text{F}$  to  $1.0\mu\text{F}$  ceramic capacitors in parallel with  $10\mu\text{F}$  or greater tantalum capacitors. Connect the ceramic capacitors very close to the MAX912/MAX913's supply pins, keeping leads short to minimize lead inductance. For particularly noisy applications, use ferrite beads on the power-supply lines.

#### **Board Layout**

As with all high-speed components, careful attention to layout is essential for best performance.

- 1) Use a printed circuit board with an unbroken ground plane.

- Pay close attention to the bandwidth of bypass components and keep leads short.

- 3) Avoid sockets; solder the comparator and other components directly to the board to minimize unwanted parasitic inductance and capacitance.

#### **Input Slew Rate**

The MAX912/MAX913 design eliminates the input slew-rate requirement imposed on many standard comparators. As long as LE is high after the maximum propagation delay and the input is greater than the comparator's total DC error, the output will be valid without oscillations.

#### Maximum Clock (LE) and Signal Rate

The maximum clock and signal rate is 70MHz, based on the comparator's rise and fall time with a 5mV overdrive at +25°C (Figure 1). With a 20mV overdrive, the maximum propagation delay is 12ns and the clock signal rate is 85MHz.

Figure 2. Effect of Hysteresis on Input Resolution

Chip Information

MAX912 TRANSISTOR COUNT: 285 MAX913 TRANSISTOR COUNT: 154

PROCESS: Bipolar

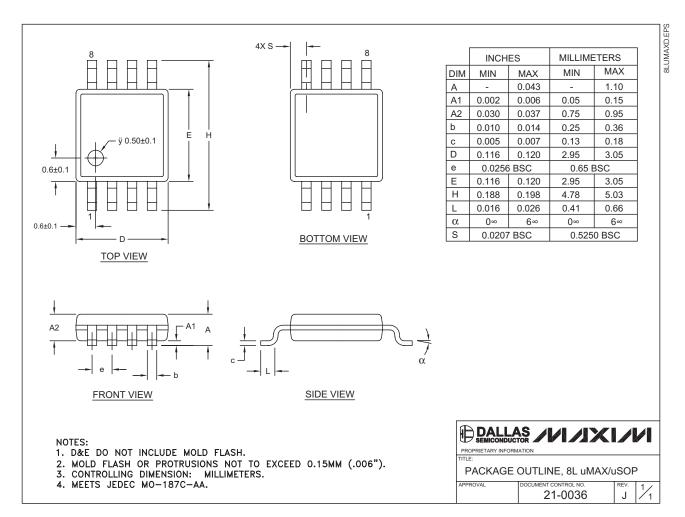

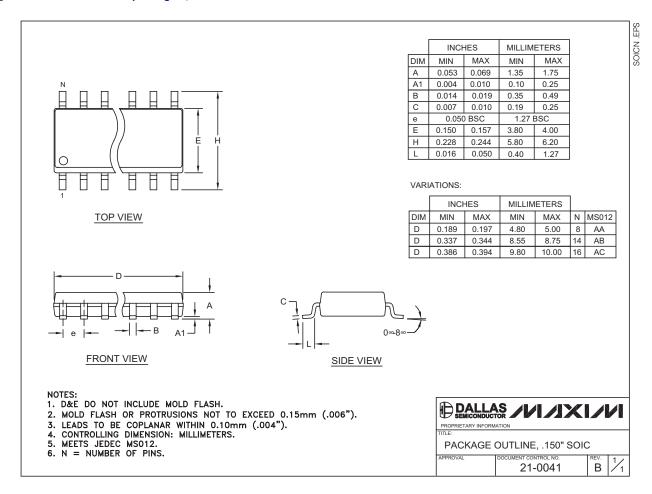

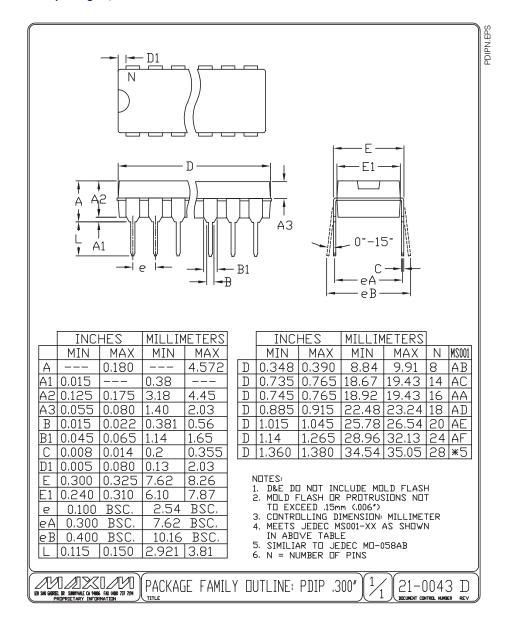

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_