#### **ABSOLUTE MAXIMUM RATINGS**

| DC, SYS, BAT, CISET, DLIM1, DLIM2, E<br>CEN, EN4, CHG, RST1, FB1, FB2, FB3 |                                   |

|----------------------------------------------------------------------------|-----------------------------------|

| PV2 to GND                                                                 |                                   |

| PV13 to SYS                                                                | 0.3V to +0.3V                     |

| PG1, PG2, PG3, PG4 to GND                                                  | 0.3V to +0.3V                     |

| COMP4, FB4 to GND                                                          | 0.3V to (V <sub>SYS</sub> + 0.3V) |

| LX4 to PG4                                                                 | 0.3V to +33V                      |

| OVP4 to GND                                                                | 0.3V to +33V                      |

| LX1, LX2, LX3 Continuous Current (Note                                     | : 1)1.5A                          |

| LX4 Current                                                                | 750mA <sub>RMS</sub>              |

| Output Short-Circuit Duration                                              | Continuous                        |

|                                                                            |                                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$    | 3)             |

|--------------------------------------------------------|----------------|

| 28-Pin Thin QFN Single-Layer Board (der                | ate 20.8mW/°C  |

| above +70°C)                                           | 1666.7mW       |

| 28-Pin Thin QFN Multilayer Board (derate               | 28.6mW/°C      |

| above +70°C)                                           | 2285.7mW       |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | ) (Note 2)     |

| 28-Lead Thin QFN                                       |                |

| Operating Temperature Range                            | 40°C to +85°C  |

| Junction Temperature                                   | 40°C to +125°C |

| Storage Temperature                                    | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                      | +300°C         |

|                                                        |                |

- **Note 1:** LX1, LX2, LX3 have clamp diodes to their respective PG\_ and PV\_. Applications that forward bias these diodes must take care not to exceed the package power dissipation limits.

- **Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="http://www.maxim-ic.com/thermal-tutorial">http://www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(DC, LX\_ unconnected;  $V_{EP} = V_{GND} = 0V$ ,  $V_{BAT} = 4V$ , DLIM[1:2] = 00, EN123 = EN4 = low,  $V_{FB1} = V_{FB2} = V_{FB3} = 1.1V$ ,  $V_{FB4} = 0.6V$ , PV13 = PV2 = SYS,  $T_A = -40^{\circ}$ C to +85°C, capacitors as shown in Figure 1,  $R_{CISFT} = 3k\Omega$ , unless otherwise noted.) (Note 3)

| PARAMETER                      | SYMBOL                                                               | CONDITIONS                                                                                                |           | MIN            | TYP   | MAX   | UNITS |    |

|--------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------|----------------|-------|-------|-------|----|

| DC POWER INPUT                 |                                                                      |                                                                                                           |           |                |       |       |       |    |

| DC Voltage Range               | V <sub>DC</sub>                                                      |                                                                                                           |           |                | 4.1   |       | 5.5   | V  |

| SYS Regulation Voltage         | Vsys reg                                                             | $V_{DC} = 5.75V$                                                                                          | MAX88     | 19A/MAX8819C   | 4.3   | 4.35  | 4.4   | V  |

| 313 Negulation Voltage         | VSYS_REG                                                             | VDC = 3.73V                                                                                               | MAX88     | 19B            | 5.1   | 5.3   | 5.5   | V  |

| DC Undervoltage Threshold      | V <sub>UVLO_DC</sub>                                                 | V <sub>DC</sub> rising, 500mV                                                                             | typical h | ysteresis      | 3.95  | 4.00  | 4.05  | V  |

| DC Overvoltage Threshold       | Vovlo_dc                                                             | V <sub>DC</sub> rising, 300mV                                                                             | typical h | ysteresis      | 5.811 | 5.9   | 6.000 | V  |

|                                |                                                                      | $V_{DC} = 5.75V, V_{SYS}$                                                                                 |           | DLIM[1:2] = 10 | 90    | 95    | 100   |    |

| DC Current Limit (Note 4)      | IDCLIM                                                               | for MAX8819B or V<br>4V for MAX8819A/                                                                     | 'SYS =    | DLIM[1:2] = 01 | 450   | 475   | 500   | mA |

| (Note 4)                       |                                                                      | MAX8819C                                                                                                  |           | DLIM[1:2] = 00 | 900   | 1000  | 1100  |    |

|                                |                                                                      | DLIM[1:2] = 11 (suspend)                                                                                  |           |                | 0.02  | 0.035 |       |    |

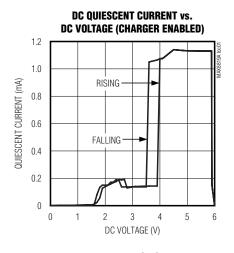

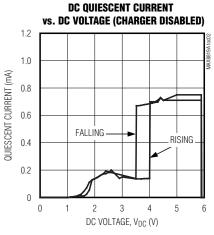

| DC Quiescent Current           | DLIM[1:2] ≠ 11, ISYS<br>EN123 = low, EN4 =<br>V <sub>DC</sub> = 5.5V |                                                                                                           | -         |                |       | 1.33  |       | mA |

|                                |                                                                      | DLIM[1:2] $\neq$ 11, I <sub>SYS</sub> = 0mA, EN123 = low,<br>EN4 = low, CEN = low, V <sub>DC</sub> = 5.5V |           |                | 0.95  |       |       |    |

| DC-to-SYS Dropout Resistance   | R <sub>DS</sub>                                                      | V <sub>DC</sub> = 4V, I <sub>SYS</sub> = 4                                                                | 00mA, D   | DLIM[1:2] = 01 |       | 0.330 | 0.700 | Ω  |

| DC-to-SYS Soft-Start Time      | tss-D-s                                                              |                                                                                                           |           |                |       | 1.5   |       | ms |

| DC Thermal-Limit Temperature   |                                                                      | Die temperature where current limit is reduced                                                            |           |                | 100   |       | °C    |    |

| DC Thermal-Limit Gain          |                                                                      | Amount of input current reduction above thermal-limit temperature                                         |           |                | 5     |       | %/°C  |    |

| SYSTEM                         |                                                                      |                                                                                                           |           |                |       |       |       |    |

| System Operating Voltage Range | V <sub>SYS</sub>                                                     |                                                                                                           |           |                | 2.6   |       | 5.5   | V  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, LX\_ unconnected;  $V_{EP} = V_{GND} = 0V$ ,  $V_{BAT} = 4V$ , DLIM[1:2] = 00, EN123 = EN4 = low,  $V_{FB1} = V_{FB2} = V_{FB3} = 1.1V$ ,  $V_{FB4} = 0.6V$ , PV13 = PV2 = SYS,  $T_A = -40^{\circ}C$  to +85°C, capacitors as shown in Figure 1,  $R_{CISET} = 3k\Omega$ , unless otherwise noted.) (Note 3)

| PARAMETER                                | SYMBOL                    | CONDITIONS                                                                                                                | MIN   | TYP   | MAX   | UNITS |  |

|------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| System Undervoltage Lockout<br>Threshold | V <sub>UVLO_SYS</sub>     | V <sub>SYS</sub> falling, 100mV hysteresis                                                                                | 2.45  | 2.5   | 2.55  | V     |  |

| BAT-to-SYS Reverse Regulation<br>Voltage | V <sub>B</sub> SREG       | DC and BAT are delivering current to SYS;<br>I <sub>BAT</sub> = 95mA; V <sub>DC</sub> = 4.3V,<br>MAX8819A/MAX8819C (only) | 50    | 66    | 90    | mV    |  |

|                                          |                           | V <sub>DC</sub> = 0V, EN123 = low, EN4 = low,<br>V <sub>BAT</sub> = 4V                                                    |       | 10    | 20    |       |  |

|                                          | Isys +                    | $V_{DC} = 5V$ , DLIM[1:2] $\neq$ 11, EN123 = low,<br>EN4 = low, $V_{BAT} = 4V$                                            |       | 0     | 10    |       |  |

| Quiescent Current                        | ISYS +<br>IPV13 +<br>IPV2 | V <sub>DC</sub> = 0V, EN123 = high, EN4 = low,<br>V <sub>BAT</sub> = 4V (step-down converters are not in<br>dropout)      |       | 128   | 290   | μΑ    |  |

|                                          |                           | V <sub>DC</sub> = 0V, EN123 = high, EN4 = high,<br>V <sub>BAT</sub> = 4V (step-down converters are not in<br>dropout)     |       | 362   | 730   |       |  |

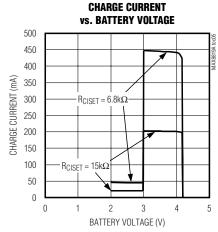

| BATTERY CHARGER (VDC = 5.0)              | <b>/</b> )                |                                                                                                                           | •     |       |       | •     |  |

| BAT-to-SYS On-Resistance                 | R <sub>BS</sub>           | V <sub>DC</sub> = 0V, V <sub>BAT</sub> = 4.2V, I <sub>SYS</sub> = 0.9A                                                    |       | 0.073 | 0.165 | Ω     |  |

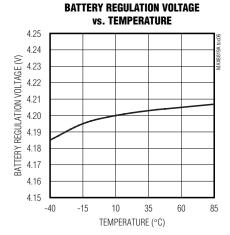

| BAT Regulation Voltage                   | \/                        | T <sub>A</sub> = +25°C                                                                                                    | 4.174 | 4.200 | 4.221 | V     |  |

| (Figure 2)                               | VBATREG                   | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                       | 4.158 | 4.200 | 4.242 | v     |  |

| BAT Recharge Threshold                   |                           | (Note 4)                                                                                                                  | -135  | -100  | -65   | mV    |  |

| BAT Prequalification Threshold           | V <sub>BATPRQ</sub>       | V <sub>BAT</sub> rising, 180mV hysteresis, Figure 2                                                                       | 2.9   | 3.0   | 3.1   | V     |  |

| R <sub>CISET</sub> Resistance Range      |                           | Guaranteed by BAT fast-charge current limit                                                                               | 3     |       | 15    | kΩ    |  |

| CISET Voltage                            | VCISET                    | RCISET = $7.5k\Omega$ , $I_{BAT} = 267mA$                                                                                 | 0.9   | 1.0   | 1.1   | V     |  |

|                                          |                           | $DLIM[1:2] = 10$ , $R_{CISET} = 3k\Omega$                                                                                 | 87    | 92    | 100   |       |  |

|                                          |                           | $DLIM[1:2] = 01$ , $R_{CISET} = 3k\Omega$                                                                                 | 450   | 472   | 500   |       |  |

| BAT Fast-Charge Current Limit            | ICHGMAX                   | DLIM[1:2] = 00, R <sub>CISET</sub> = $15k\Omega$                                                                          | 170   | 200   | 230   | mA    |  |

|                                          |                           | $DLIM[1:2] = 00$ , $R_{CISET} = 7.5k\Omega$                                                                               | 375   | 400   | 425   |       |  |

|                                          |                           | DLIM[1:2] = 00, R <sub>CISET</sub> = $3.74k\Omega$                                                                        | 740   | 802   | 860   |       |  |

| BAT Prequalification Current             | IPREQUAL                  | $V_{BAT} = 2.5V$ , $R_{CISET} = 3.74$ k $\Omega$                                                                          | 60    | 82    | 105   | mA    |  |

| Top-Off Threshold (Note 5)               | ITOPOFF                   | $T_A = +25$ °C, $R_{CISET} = 3.74$ k $\Omega$                                                                             | 60    | 82    | 105   | mA    |  |

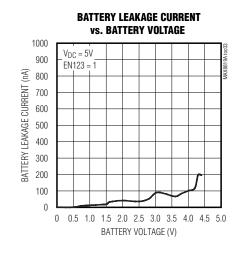

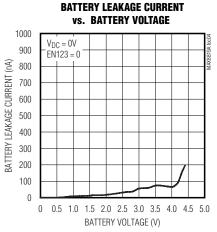

| BAT Leakage Current                      |                           | V <sub>DC</sub> = 0V, EN123 = low, EN4 = low,<br>CEN = low, V <sub>BAT</sub> = 4V                                         |       | 10    | 20    | ^     |  |

| DAT LEAKAGE CUITETIL                     |                           | V <sub>DC</sub> = 5V, DLIM[1:2] = 11, EN123 = low,<br>EN4 = low, V <sub>BAT</sub> = 4V                                    |       | 0     |       | μΑ    |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, LX\_ unconnected;  $V_{EP} = V_{GND} = 0V$ ,  $V_{BAT} = 4V$ , DLIM[1:2] = 00, EN123 = EN4 = low,  $V_{FB1} = V_{FB2} = V_{FB3} = 1.1V$ ,  $V_{FB4} = 0.6V$ , PV13 = PV2 = SYS,  $T_A = -40^{\circ}$ C to +85°C, capacitors as shown in Figure 1,  $R_{CISET} = 3k\Omega$ , unless otherwise noted.) (Note 3)

| PARAMETER                           | SYMBOL              | Co                                     | ONDITIONS                                                                     | MIN   | TYP       | MAX       | UNITS |  |

|-------------------------------------|---------------------|----------------------------------------|-------------------------------------------------------------------------------|-------|-----------|-----------|-------|--|

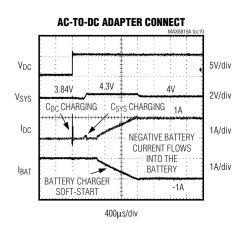

|                                     |                     | Slew rate                              |                                                                               | 333   |           | mA/ms     |       |  |

| 0 6 0 1 7                           |                     | Time from 0 to 50                      |                                                                               | 1.5   |           |           |       |  |

| Charger Soft-Start Time             | tss_chg             | Time from 0 to 10                      | 0mA                                                                           |       | 0.3       |           | ms    |  |

|                                     |                     | Time from 100mA                        | to 500mA                                                                      |       | 1.2       |           | 1     |  |

| Timer Accuracy                      |                     |                                        |                                                                               |       |           | +15       | %     |  |

| Timer Suspend Threshold             |                     |                                        | nen the fast-charge timer<br>/ translates to 20% of the<br>arge current limit | 250   | 300       | 350       | mV    |  |

| Timer Extend Threshold              |                     | •                                      | nen the fast-charge timer<br>cranslates to 50% of the<br>arge current limit   | 700   | 750       | 800       | mV    |  |

| Prequalification Time               | tprequal            |                                        |                                                                               |       | 33        |           | min   |  |

| Fast-Charge Time                    | tFSTCHG             |                                        |                                                                               |       | 660       |           | min   |  |

| Top-Off Time                        | tTOPOFF             |                                        |                                                                               |       | 33        |           | min   |  |

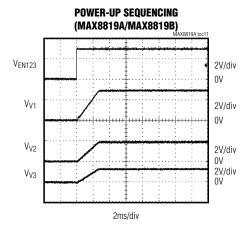

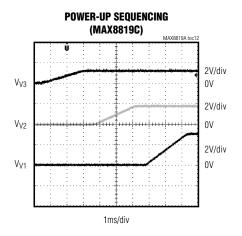

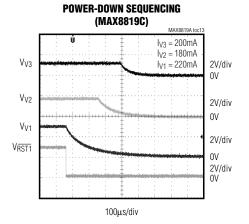

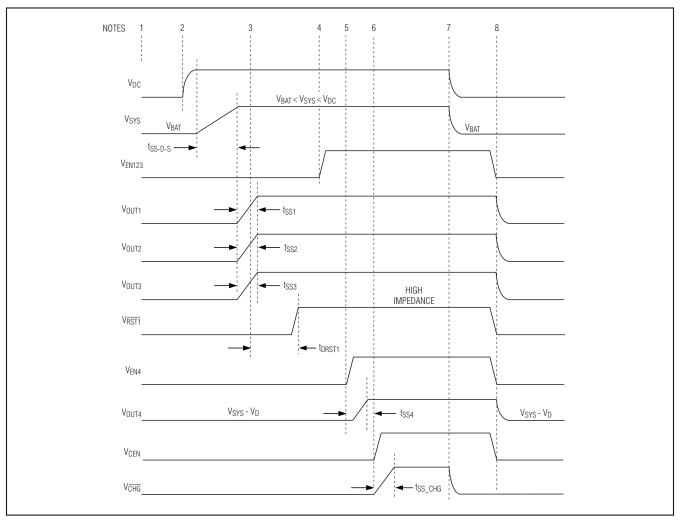

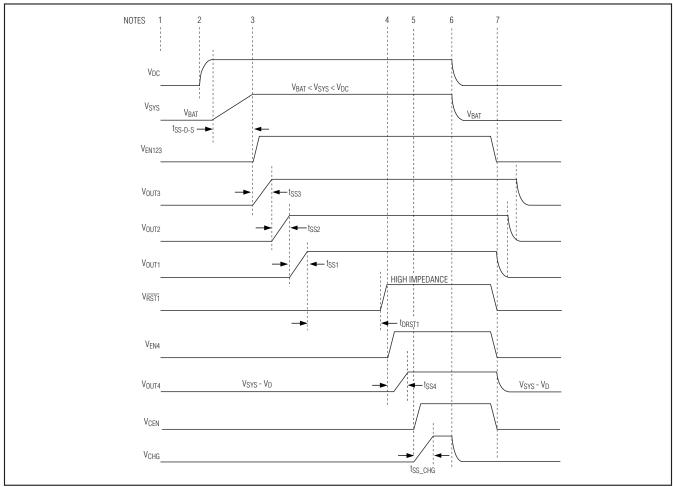

| POWER SEQUENCING (Figures 6         | and 7)              |                                        |                                                                               |       |           |           |       |  |

| REG1, REG2, REG3 Soft-Start<br>Time | tss1, tss2,<br>tss3 |                                        |                                                                               |       | 2.6       |           | ms    |  |

| REG4 Soft-Start Time                | tss4                | $C_{COMP4} = 0.022\mu$                 | uF to GND                                                                     |       | 5         |           | ms    |  |

| REGULATOR THERMAL SHUTDOWN          |                     |                                        |                                                                               |       |           |           |       |  |

| Thermal Shutdown Temperature        |                     | T <sub>J</sub> rising                  |                                                                               |       | +165      |           | °C    |  |

| Thermal Shutdown Hysteresis         |                     |                                        |                                                                               |       | 15        |           | °C    |  |

| REG1-SYNCHRONOUS STEP-DO            | OWN CONVE           | RTER                                   |                                                                               |       |           |           |       |  |

| Input Voltage                       |                     | PV13 supplied fro                      | om SYS                                                                        |       | $V_{SYS}$ |           | V     |  |

| Maximum Output Current              |                     | L = $4.7\mu$ H,<br>RLSR = $0.13\Omega$ | MAX8819A/MAX8819B                                                             | 400   |           |           | mA    |  |

| '                                   |                     | (Note 6)                               | MAX8819C                                                                      | 550   |           |           |       |  |

| Short-Circuit Current               |                     | L = 4.7µH, RLSR =                      | = 0.13Ω                                                                       |       | 600       |           | mA    |  |

| Short-Circuit Detection Threshold   |                     |                                        |                                                                               |       | 230       |           | mV    |  |

| Short-Circuit Foldback Frequency    |                     |                                        |                                                                               |       | fosc/3    |           | Hz    |  |

| FB1 Voltage                         |                     | (Note 7)                               |                                                                               | 0.997 | 1.01      | 1.028     | V     |  |

| Output Voltage Range                |                     |                                        |                                                                               | 1     |           | $V_{SYS}$ | V     |  |

| FB1 Leakage Current                 |                     | V <sub>FB1</sub> = 1.01V               | $T_A = +25$ °C<br>$T_A = +85$ °C                                              | -50   | -5<br>-10 | +50       | nA    |  |

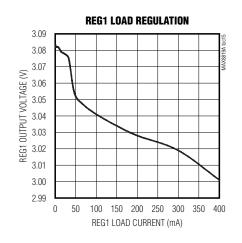

| Load Regulation                     |                     | I <sub>OUT1</sub> = 100mA to 300mA     |                                                                               |       | 1         |           | %     |  |

| Line Regulation                     |                     | (Note 9)                               |                                                                               |       | 1         |           | %/D   |  |

| p-Channel On-Resistance             |                     | $V_{PV13} = 4.0V, I_{LX1} = 180mA$     |                                                                               |       | 190       |           | mΩ    |  |

| n-Channel On-Resistance             |                     | $V_{PV13} = 4.0V, I_{LX}$              |                                                                               |       | 250       |           | mΩ    |  |

| p-Channel Current-Limit             |                     | MAX8819A/MAX8                          |                                                                               | 0.565 | 0.600     | 0.640     |       |  |

| Threshold                           |                     | MAX8819C                               |                                                                               | 0.615 | 0.650     | 0.750     | A     |  |

· \_\_\_\_\_ /V|X|/V|

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, LX\_ unconnected;  $V_{EP} = V_{GND} = 0V$ ,  $V_{BAT} = 4V$ , DLIM[1:2] = 00, EN123 = EN4 = low,  $V_{FB1} = V_{FB2} = V_{FB3} = 1.1V$ ,  $V_{FB4} = 0.6V$ , PV13 = PV2 = SYS,  $T_{A} = -40^{\circ}$ C to +85°C, capacitors as shown in Figure 1,  $R_{CISET} = 3k\Omega$ , unless otherwise noted.) (Note 3)

| PARAMETER                                 | SYMBOL    | С                                              | ONDITIONS               | MIN   | TYP              | MAX              | UNITS |

|-------------------------------------------|-----------|------------------------------------------------|-------------------------|-------|------------------|------------------|-------|

| Skip-Mode Transition Current              |           | (Note 8)                                       |                         |       | 80               |                  | mA    |

| n-Channel Zero-Crossing<br>Threshold      |           |                                                |                         |       | 10               |                  | mA    |

| Maximum Duty Cycle                        |           |                                                |                         | 100   |                  |                  | %     |

| Minimum Duty Cycle                        |           |                                                |                         |       | 12.5             |                  | %     |

| PWM Frequency                             | fosc      |                                                |                         | 1.8   | 2.0              | 2.2              | MHz   |

| Internal Discharge Resistance in Shutdown |           | EN123 = low, res                               | istance from LX1 to PG1 |       | 1.0              |                  | kΩ    |

| REG2-SYNCHRONOUS STEP-DO                  | OWN CONVE | RTER                                           |                         |       |                  |                  |       |

| Input Voltage                             |           | PV2 supplied from                              | n SYS                   |       | V <sub>SYS</sub> |                  | V     |

| Maximum Output Current                    |           | $L = 4.7 \mu H,$ $R_{LSR} = 0.13 \Omega$       | MAX8819A/MAX8819B       | 300   |                  |                  | mA    |

| Maximum Output Ourrent                    |           | (Note 6)                                       | MAX8819C                | 500   |                  |                  | INA   |

| Short-Circuit Current                     |           | $L = 4.7\mu H, R_{LSR}$                        | = 0.13Ω                 |       | 600              |                  | mA    |

| Short-Circuit Detection Threshold         |           |                                                |                         |       | 230              |                  | mV    |

| Short-Circuit Foldback Frequency          |           |                                                |                         |       | fosc/3           |                  | Hz    |

| FB2 Voltage                               |           | (Note 7)                                       |                         | 0.997 | 1.012            | 1.028            | V     |

| Output Voltage Range                      |           |                                                |                         | 1     |                  | V <sub>SYS</sub> | V     |

| EDO La alvaga Current                     |           | V <sub>FB2</sub> = 1.01V                       | T <sub>A</sub> = +25°C  | -50   | -5               | +50              | nA    |

| FB2 Leakage Current                       |           | VFB2 = 1.01V                                   | $T_A = +85^{\circ}C$    |       | -50              |                  | IIA   |

| Load Regulation                           |           | $I_{OUT2} = 100$ mA to                         | o 300mA                 |       | 1                |                  | %     |

| Line Regulation                           |           | (Note 9)                                       |                         |       | 1                |                  | %/D   |

| p-Channel On-Resistance                   |           | $V_{PV2} = 4.0V, I_{LX2}$                      | e = 180mA               |       | 290              |                  | mΩ    |

| n-Channel On-Resistance                   |           | $V_{PV2} = 4.0V, I_{LX2}$                      | e = 180mA               |       | 200              |                  | mΩ    |

| p-Channel Current-Limit                   |           | MAX8819A/MAX8                                  | MAX8819A/MAX8819B       |       | 0.550            | 0.595            | A     |

| Threshold                                 |           | MAX8819C                                       |                         | 0.565 | 0.600            | 0.700            | ^     |

| Skip-Mode Transition Current              |           | (Note 8)                                       |                         |       | 80               |                  | mA    |

| n-Channel Zero-Crossing<br>Threshold      |           |                                                |                         |       | 10               |                  | mA    |

| Maximum Duty Cycle                        |           |                                                |                         | 100   |                  |                  | %     |

| Minimum Duty Cycle                        |           |                                                |                         |       | 12.5             |                  | %     |

| PWM Frequency                             | fosc      |                                                |                         | 1.8   | 2.0              | 2.2              | MHz   |

| Internal Discharge Resistance in Shutdown |           | EN123 = low, resistance from LX2 to PG2        |                         |       | 1.0              |                  | kΩ    |

| REG2 Disable                              | Δlsys     | V <sub>PV2</sub> = 0V, REG2 disabled (Note 10) |                         | 1     | -25              |                  | μΑ    |

| REG3-SYNCHRONOUS STEP-DO                  |           |                                                | , ,                     |       |                  |                  |       |

| Input Voltage                             |           | PV13 supplied from                             | om SYS                  |       | Vsys             |                  | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, LX\_ unconnected;  $V_{EP} = V_{GND} = 0V$ ,  $V_{BAT} = 4V$ , DLIM[1:2] = 00, EN123 = EN4 = low,  $V_{FB1} = V_{FB2} = V_{FB3} = 1.1V$ ,  $V_{FB4} = 0.6V$ , PV13 = PV2 = SYS,  $T_A = -40^{\circ}$ C to +85°C, capacitors as shown in Figure 1,  $R_{CISET} = 3k\Omega$ , unless otherwise noted.) (Note 3)

| PARAMETER                                 | SYMBOL            | C                                          | ONDITIONS               | MIN    | TYP    | MAX              | UNITS |

|-------------------------------------------|-------------------|--------------------------------------------|-------------------------|--------|--------|------------------|-------|

|                                           |                   | $L = 4.7 \mu H$ ,                          | MAX8819A/MAX8819B       | 300    |        |                  |       |

| Maximum Output Current                    |                   | $R_{LSR} = 0.13\Omega$ (Note 6)            | MAX8819C                | 500    |        |                  | mA    |

| Short-Circuit Current                     |                   | $L = 4.7 \mu H, R_{LSR}$                   | = 0.13Ω                 |        | 600    |                  | mA    |

| Short-Circuit Detection Threshold         |                   |                                            |                         |        | 230    |                  | mV    |

| Short-Circuit Foldback Frequency          |                   |                                            |                         |        | fosc/3 |                  | Hz    |

| FB3 Voltage                               |                   | (Note 7)                                   |                         | 0.997  | 1.01   | 1.028            | V     |

| Output Voltage Range                      |                   |                                            |                         | 1      |        | V <sub>SYS</sub> | V     |

| FD0.1                                     |                   | .,                                         | T <sub>A</sub> = +25°C  | -50    | -5     | +50              |       |

| FB3 Leakage Current                       |                   | $V_{FB3} = 1.01V$                          | T <sub>A</sub> = +85°C  |        | -50    |                  | nA    |

| Load Regulation                           |                   | $I_{OUT3} = 100$ mA to                     | o 300mA                 |        | 1.3    |                  | %     |

| Line Regulation                           |                   | (Note 9)                                   |                         |        | 1      |                  | %/D   |

| p-Channel Current-Limit                   |                   | MAX8819A/MAX8                              | 3819B                   | 0.512  | 0.550  | 0.595            | ^     |

| Threshold                                 |                   | MAX8819C                                   |                         | 0.565  | 0.600  | 0.700            | Α     |

| Skip-Mode Transition Current              |                   | (Note 8)                                   |                         |        | 80     |                  | mA    |

| n-Channel Zero-Crossing<br>Threshold      |                   |                                            |                         |        | 10     |                  | mA    |

| p-Channel On-Resistance                   |                   | V <sub>PV13</sub> = 4.0V, I <sub>L</sub> X | 3 = 180mA               |        | 290    |                  | mΩ    |

| n-Channel On-Resistance                   |                   | $V_{PV13} = 4.0V, I_{LX}$                  |                         |        | 120    |                  | mΩ    |

| Maximum Duty Cycle                        |                   |                                            |                         | 100    |        |                  | %     |

| Minimum Duty Cycle                        |                   |                                            |                         |        | 12.5   |                  | %     |

| PWM Frequency                             | fosc              |                                            |                         | 1.8    | 2.0    | 2.2              | MHz   |

| Internal Discharge Resistance in Shutdown |                   | EN123 = low, res                           | istance from LX3 to PG3 |        | 1.0    |                  | kΩ    |

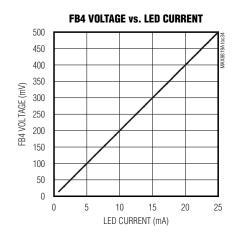

| REG4-STEP-UP CONVERTER                    |                   |                                            |                         | •      |        |                  |       |

| Input Voltage                             |                   | Power supplied fr                          | rom SYS (see Figure 1)  | 2.4    |        | 5.5              | V     |

| Output Voltage Range                      | V <sub>OUT4</sub> |                                            |                         | Vsys   |        | 24               | V     |

| FB4 Regulation Voltage                    | V <sub>FB4</sub>  | No dimming                                 |                         | 475    | 500    | 525              | mV    |

| FB4 Leakage                               |                   | REG4 disabled (E                           | EN4 = low)              | -0.050 | +0.005 | +0.050           | μΑ    |

| Switching Frequency                       |                   |                                            |                         | 0.9    | 1      | 1.1              | MHz   |

| Minimum Duty Cycle                        |                   |                                            |                         |        | 5      |                  | %     |

| Maximum Duty Cycle                        |                   |                                            |                         | 90     | 94     |                  | %     |

| OVP4 Overvoltage Detection                | Vovp              |                                            |                         | 24     | 25     | 26               | V     |

| OVP4 Input Current                        |                   | OVP4 = SYS, EN4                            | 4 = high                |        | 4      |                  | μΑ    |

| OVP4 Leakage Current                      |                   | REG4 disabled (EOVP4 = SYS                 | EN4 = low),             | -1     | +0.001 | +1               | μΑ    |

| n-Channel On-Resistance                   |                   | $V_{SYS} = 4.0V$ , $I_{LX4}$               | . = 200mA               |        | 395    |                  | mΩ    |

| n-Channel Off-Leakage Current             |                   | V <sub>L</sub> X <sub>4</sub> = 28V        |                         | -1     | +0.001 | +1               | μΑ    |

| n-Channel Current Limit                   |                   |                                            |                         | 555    | 695    | 950              | mA    |

8 \_\_\_\_\_\_\_//N

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, LX\_ unconnected;  $V_{EP} = V_{GND} = 0V$ ,  $V_{BAT} = 4V$ , DLIM[1:2] = 00, EN123 = EN4 = low,  $V_{FB1} = V_{FB2} = V_{FB3} = 1.1V$ ,  $V_{FB4} = 0.6V$ , PV13 = PV2 = SYS,  $T_A = -40^{\circ}$ C to +85°C, capacitors as shown in Figure 1,  $R_{CISET} = 3k\Omega$ , unless otherwise noted.) (Note 3)

| PARAMETER                            | SYMBOL      | CONDITIONS                                                         | MIN   | TYP    | MAX   | UNITS |

|--------------------------------------|-------------|--------------------------------------------------------------------|-------|--------|-------|-------|

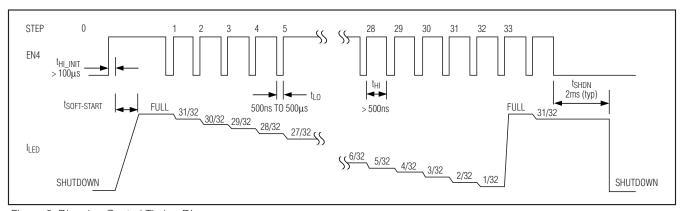

| LED DIMMING CONTROL (EN4)            |             |                                                                    | •     |        |       |       |

| EN4 Low Shutdown Delay               | tshdn       |                                                                    |       | 2      | 3.2   | ms    |

| EN4 High Enable Delay (Figure 8)     | thi_init    |                                                                    | 100   |        |       | μs    |

| EN4 Low Time                         | tLO         |                                                                    | 0.5   |        | 500   | μs    |

| EN4 High Time                        | tHI         |                                                                    | 0.5   |        |       | μs    |

| RESET (RST1)                         |             |                                                                    |       |        |       |       |

| Reset Trip Threshold                 | VTHRST      | Voltage from FB1 to GND, V <sub>FB1</sub> falling, 50mV hysteresis | 0.765 | 0.858  | 0.945 | V     |

| Reset Deassert Delay Time            | tdrst       |                                                                    | 180   | 200    | 220   | ms    |

| Reset Glitch Filter                  | tGLRST      |                                                                    |       | 50     |       | μs    |

| LOGIC (DLIM1, DLIM2, EN123, EN       | I4, CHG, RS | <del>11</del> )                                                    |       |        |       |       |

| Logic Input-Voltage Low              |             | $V_{DC} = 4.1V \text{ to } 5.5V, V_{SYS} = 2.6V \text{ to } 5.5V$  |       |        | 0.4   | V     |

| Logic Input-Voltage High             |             | $V_{DC} = 4.1V \text{ to } 5.5V, V_{SYS} = 2.6V \text{ to } 5.5V$  | 1.2   |        |       | V     |

| Logic Input Pulldown Resistance      |             | V <sub>LOGIC</sub> = 0.4V to 5.5V, CEN, EN123, EN4                 | 400   | 760    | 1200  | kΩ    |

| Logic Leakage Current                |             | V <sub>LOGIC</sub> = 0 to 5.5V, DLIM1, DLIM2                       | -1.0  | +0.001 | +1.0  | μΑ    |

| Logic Output Voltage Low             |             | ISINK = 1mA                                                        |       | 7      | 15    | mV    |

| Logic Output-High Leakage<br>Current |             | V <sub>LOGIC</sub> = 5.5V                                          | -1.0  | +0.001 | +1.0  | μA    |

- **Note 3:** Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

- Note 4: The charger transitions from done to fast-charge mode at this BAT recharge threshold.

- Note 5: The charger transitions from fast-charge to top-off mode at this top-off threshold (Figure 2).

- Note 6: The maximum output current is guaranteed by correlation to the p-channel current-limit threshold, p-channel on-resistance, n-channel on-resistance, oscillator frequency, input voltage range, and output voltage range. The parameter is stated for a 4.7μH inductor with 0.13Ω series resistance. See the *Step-Down Converter Maximum Output Current* section for more information.

- Note 7: The step-down output voltages are 1% high with no load due to the load-line architecture.

- **Note 8:** The skip-mode current threshold is the transition point between fixed-frequency PWM operation and skip-mode operation. The specification is given in terms of output load current for inductor values shown in the typical application circuit (Figure 1).

- Note 9: Line regulation for the step-down converters is measured as ΔV<sub>OUT</sub>/ΔD, where D is the duty cycle (approximately V<sub>OUT</sub>/V<sub>IN</sub>).

- Note 10: REG2 is disabled by connecting PV2 to ground, decreasing the quiescent current.

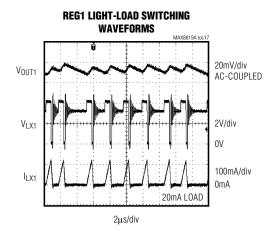

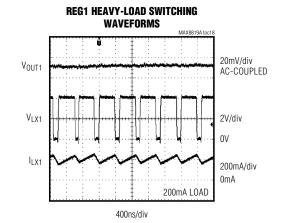

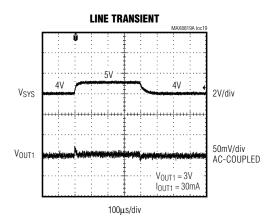

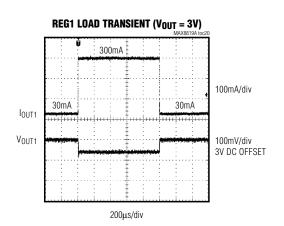

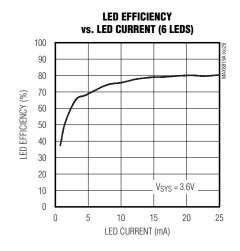

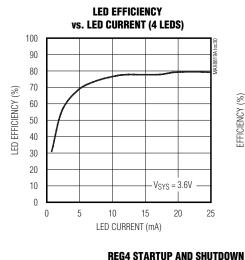

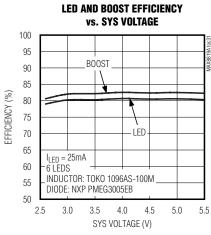

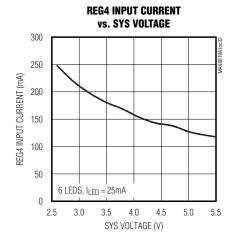

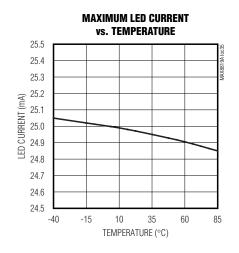

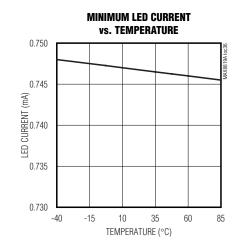

Typical Operating Characteristics

(Circuit of Figure 1, TA = +25°C, unless otherwise noted.)

8 \_\_\_\_\_\_*NIXI/*

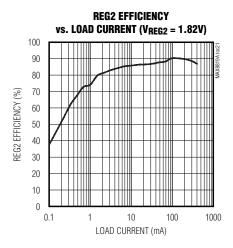

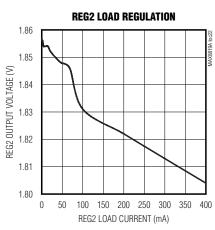

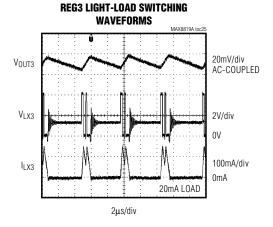

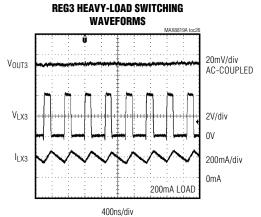

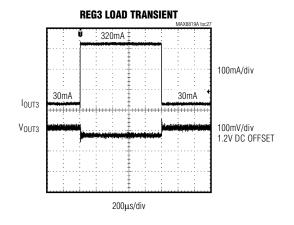

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

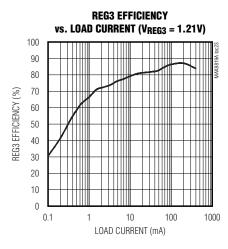

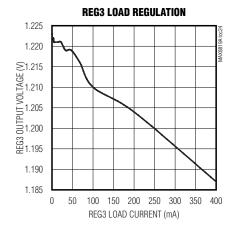

#### \_Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

10 \_\_\_\_\_\_/W/1XI/W

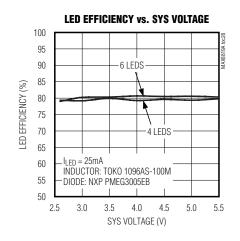

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

# V<sub>EN4</sub> 2V/div V<sub>OVP4</sub> 10V/div OV I<sub>LED</sub> 10mA/div OmA

2ms/div

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

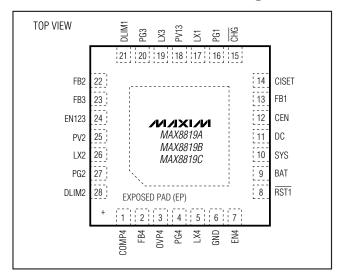

#### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | COMP4 | External Compensation Capacitor for REG4                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | FB4   | REG4 Feedback Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3   | OVP4  | Overvoltage Protection Node for REG4                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4   | PG4   | REG4 Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | LX4   | Inductor Switching Node for REG4                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6   | GND   | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7   | EN4   | REG4 Enable Input and Dimming Control Digital Input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8   | RST1  | Active-Low, Open-Drain Reset Output. $\overline{RST1}$ pulls low to indicate that FB1 is below its regulation threshold. $\overline{RST1}$ goes high 200ms after FB1 reaches its regulation threshold. $\overline{RST1}$ is high-impedance when EN123 is low, and DC is unconnected.                                                                                                                                                                                                                         |

| 9   | BAT   | Positive Battery Terminal Connection. Connect BAT to the positive terminal of a single-cell Li+/Li-Poly battery. Bypass BAT to GND with a 4.7µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                           |

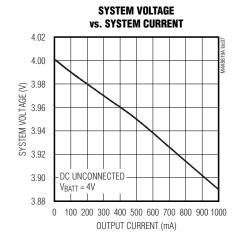

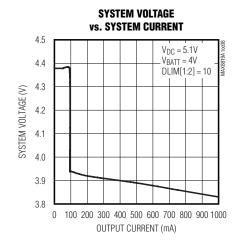

| 10  | SYS   | System Supply Output. Bypass SYS to GND with a 10 $\mu$ F ceramic capacitor. When a valid voltage is present at DC and DLIM[1:2] $\neq$ 11, VSYS is limited to 4.35V (MAX8819A/MAX8819C) or 5.3V (MAX8819B). When the system load (ISYS) exceeds the input current limit, VSYS drops 75mV (VBSREG) below VBAT, allowing both the external power source and the battery to service SYS. SYS is connected to BAT through an internal 70m $\Omega$ system load switch when a valid source is not present at DC. |

| 11  | DC    | DC Power Input. DC is capable of delivering 1A to SYS. DC supports both AC adapters and USB inputs. As shown in Table 1, the DC current limit is controlled by DLIM1 and DLIM2.                                                                                                                                                                                                                                                                                                                              |

| 12  | CEN   | Battery Charger Enable Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13  | FB1   | Feedback Input for REG1. Connect FB1 to the center of a resistor voltage-divider from the REG1 output capacitors to GND to set the output voltage from 1V to V <sub>SYS</sub> .                                                                                                                                                                                                                                                                                                                              |

#### **Pin Description (continued)**

| CISET | Charge Rate Select Input. Connect a resistor from CISET to GND (R <sub>CISET</sub> ) to set the fast-charge current limit, prequalification-charge current limit, and top-off threshold.                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG   | Active-Low, Open-Drain Charge Status Output. CHG pulls low to indicate that the battery is charging. See Figure 3 for more information.                                                                                                            |

| PG1   | REG1 Power Ground                                                                                                                                                                                                                                  |

| LX1   | Inductor Switching Node for REG1. When enabled, LX1 switches between PV13 and PG1 to regulate the FB1 voltage to 1.0V. When disabled, LX1 is pulled to PG1 by $1k\Omega$ in shutdown.                                                              |

| PV13  | Power Input for the REG1 and REG3 Converters. Connect PV13 to SYS. Bypass PV13 to PG1 with a 4.7µF ceramic capacitor.                                                                                                                              |

| LX3   | Inductor Switching Node for REG3. When enabled, LX3 switches between PV13 and PG3 to regulate the FB3 voltage to 1.0V. When disabled, LX3 is pulled to PG3 by a $1k\Omega$ internal resistor.                                                      |

| PG3   | REG3 Power Ground                                                                                                                                                                                                                                  |

| DLIM1 | Input Current-Limit Selection Digital Input 1. Drive high or low according to Table 1 to set the DC input current limit.                                                                                                                           |

| FB2   | Feedback Input for REG2. Connect FB2 to the center of a resistor voltage-divider from the REG2 output capacitors to GND to set the output voltage from 1V to V <sub>SYS</sub> . FB2 must be connected to GND if REG2 is disabled by grounding PV2. |

| FB3   | Feedback Input for REG3. Connect FB3 to the center of a resistor voltage-divider from the REG3 output capacitors to GND to set the output voltage from 1V to V <sub>SYS</sub> .                                                                    |

| EN123 | REG1, REG2, and REG3 Enable Input. Drive EN123 high to enable REG1, REG2, and REG3. Drive EN123 low to disable REG1, REG2, and REG3. The enable/disable sequencing is shown in Figures 6 and 7.                                                    |

| PV2   | Power Input for REG2. Connect PV2 to SYS for normal operation. Bypass PV2 to PG2 with a 2.2µF ceramic capacitor. For systems that do not require REG2, connect PV2, FB2, and PG2 to GND (LX2 may be unconnected or connected to GND).              |

| LX2   | Inductor Switching Node for REG2. When enabled, LX2 switches between PV2 and PG2 to regulate the FB2 voltage to 1.0V. When disabled, LX2 is pulled to PG2 by a $1k\Omega$ internal resistor.                                                       |

| PG2   | REG2 Power Ground                                                                                                                                                                                                                                  |

| DLIM2 | Input Current-Limit Selection Digital Input 2. Drive high or low according to Table 1 to set the DC input current limit.                                                                                                                           |

|       |                                                                                                                                                                                                                                                    |

|       | CHG PG1 LX1 PV13 LX3 PG3 DLIM1 FB2 FB3 EN123 PV2 LX2 PG2                                                                                                                                                                                           |

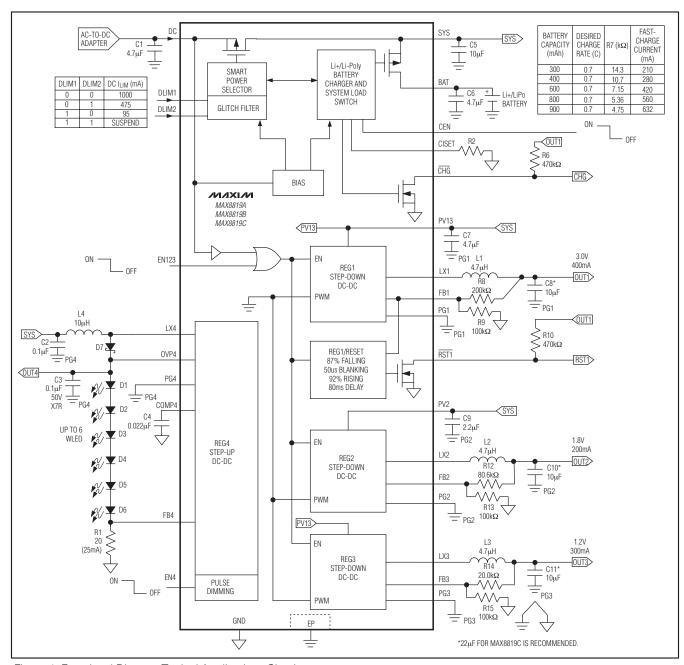

Figure 1. Functional Diagram/Typical Applications Circuit

#### **Detailed Description**

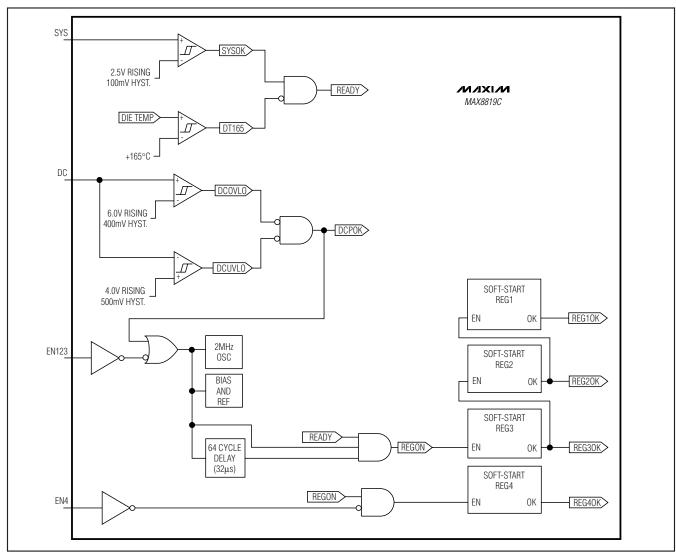

The MAX8819\_ is a complete power solution that includes a battery charger, step-down converters, and WLED power. As shown in Figure 1, the IC integrates a DC power input, Li+/Li-Poly battery charger, three step-down converters, and one step-up converter for powering

white LEDs. All three step-down converters feature adjustable output voltages set with external resistors.

The MAX8819\_ has one external power input that connects to either an AC-to-DC adapter or USB port. Logic inputs DLIM1 and DLIM2 select the desired input current limit.

In addition to charging the battery, the IC supplies power to the system through the SYS output. The charging current is provided from SYS so that the set input current limit controls the total SYS current, this is the sum of the system load current and the battery-charging current.

In some instances, there may not be enough DC input current to supply peak system loads. The Smart Power Selector circuitry offers flexible power distribution from an AC-to-DC adapter or USB source to the battery and system load. The battery is charged with any available power not used by the system load. If a system load peak exceeds the input current limit, supplemental current is taken from the battery. Thermal limiting prevents overheating by reducing power drawn from the input source. In the past, it might have been necessary to reduce system functionality to limit current drain when a USB source is connected. However, with the MAX8819\_, this is no longer the case. When the DC or USB source hits its limit, the battery supplies supplemental current to maintain the load.

The IC features overvoltage protection. Part of this protection is a 4.35V (MAX8819A/MAX8819C) or 5.3V (MAX8819B) voltage limiter at SYS. If DC exceeds the overvoltage threshold of 5.88V (VOVLO\_DC), the input limiter disconnects SYS from DC, but battery-powered operation of all regulators is still allowed.

#### **Input Limiter**

The Smart Power Selector seamlessly distributes power between the current-limited external input (DC), the battery (BAT), and the system load (SYS). The basic functions performed are:

With both an external power supply (DC) and battery (BAT) connected:

- When the system load requirements are less than the input current limit, the battery is charged with residual power from the input.

- When the system load requirements exceed the input current limit, the battery supplies supplemental current to the load through the internal system load switch.

- When the battery is connected and there is no external power input, the system (SYS) is powered from the battery.

- When an external power input is connected and there is no battery, the system (SYS) is powered from the external power input.

A thermal-limiting circuit reduces the battery charge rate and external power source current to prevent the MAX8819\_ from overheating.

#### System Load Switch

An internal 70m $\Omega$  MOSFET connects SYS to BAT when no voltage source is available at DC. When an external source is detected at DC, this switch opens and SYS is powered from the valid input source through the Smart Power Selector.

When the system load requirements exceed the input current limit, the battery supplies supplemental current to the load through the internal system load switch. If the system load continuously exceeds the input current limit, the battery does not charge, even though external power is connected. This is not expected to occur in most cases because high loads usually occur only in short peaks. During these peaks, battery energy is used, but at all other times the battery charges.

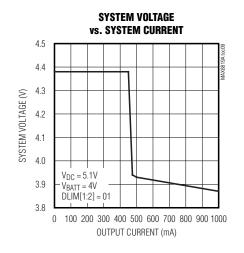

#### DC Power Input (DC, DLIM1, DLIM2)

DC is a current-limited power input that supplies the system (SYS) up to 1A. The DC to SYS switch is a linear regulator designed to operate in dropout. This linear regulator prevents the SYS voltage from exceeding 5.3V for the MAX8819B or 4.35V for the MAX8819A/ MAX8819C. As shown in Table 1, DC supports four different current limits that are set with the DLIM1 and DLIM2 digital inputs. These current limits are ideally suited for use with AC-to-DC wall adapters and USB power. The operating voltage range for DC is 4.1V to 5.5V, but it can tolerate up to 6V without damage. When the DC input voltage is below the undervoltage threshold (4V), it is considered invalid. When the DC voltage is below the battery voltage it is considered invalid. The DC power input is disconnected when the DC voltage is invalid. Bypass DC to ground with at least a 4.7µF capacitor.

Four current settings are provided based upon the settings of DLIM1 and DLIM2, see Table 1. DLIM1 and DLIM2 are deglitched. This deglitching prevents the problem of major carry transitions momentarily entering the suspend state.

**Table 1. DC Current-Limit Settings**

| DLIM1 | DLIM2 | DC I <sub>LIM</sub> (mA) |

|-------|-------|--------------------------|

| 0     | 0     | 1000                     |

| 0     | 1     | 475                      |

| 1     | 0     | 95                       |

| 1     | 1     | Suspend                  |

16 \_\_\_\_\_\_\_ /VIXI/M

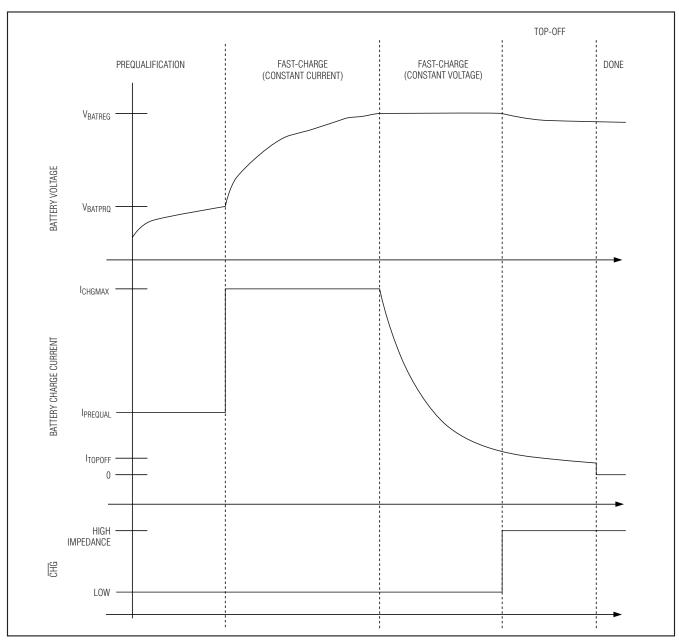

Figure 2. Li+/Li-Poly Charge Profile

#### **Battery Charger**

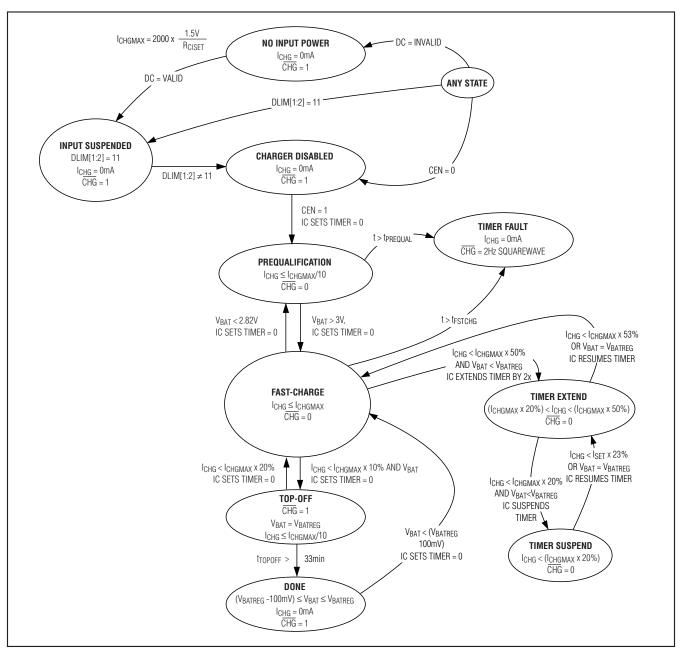

Figure 2 shows the typical Li+/Li-Poly charge profile for the MAX8819\_, and Figure 3 shows the battery charger state diagram.

With a valid DC input that is not suspended, the battery charger initiates a charge cycle once CEN is driven high. It first detects the battery voltage. If the battery voltage is less than the prequalification threshold (3.0V), the charger enters prequalification mode and charges the battery at 10% of the maximum fast-charge current while deeply discharged. Once the battery voltage rises to 3.0V, the charger transitions to fast-charge mode and applies the maximum charge current. As charging continues, the battery voltage rises until it approaches the battery regulation voltage (4.2V typ)

Figure 3. Li+/Li-Poly Charger State Diagram

where charge current starts tapering down. When charge current decreases to 10% of the maximum fast-charge current, the charger enters a 33min top-off state and then charging stops. If the battery voltage subsequently drops 100mV below the battery regulation voltage, charging restarts and the timers reset.

The battery charge rate is set by several factors:

- Battery voltage

- DC input current limit

- The charge-setting resistor, RCISET

- The system load (Isys)

- The die temperature

- The battery charger is enabled by the processor driving the CEN input high. A valid input must be available at DC. The battery charger is disabled without a valid input at DC or by driving CEN low.

- The system current has priority over the battery charger; the battery charger automatically reduces its charge current to maintain the input current limit while still providing the system current (ISYS).

- The input current limit is tapered down from full current to zero current when the die temperature transitions from +100°C to +120°C. Since ISYS has priority over the battery charge current, the battery charge current tapers down before ISYS. The overall result is self-regulation of die temperature (see the *Thermal Limiting and Overload Protection* section for more information).

- The battery charger stops charging in done mode as shown in Figures 2 and 3.

#### Charge Status Output (CHG)

CHG is an open-drain, active-low output that indicates charger status. As shown in Figures 2 and 3, CHG is low when the charger is in its prequalification or fast-charge states. When a timer count is exceeded in either state, CHG indicates the fault by blinking at a 2Hz rate and remains in that state until the charger is reset by CEN going low, removal of DC or setting DLIM[1:2] = 11.

When the MAX8819\_ is used with a microprocessor ( $\mu$ P), connect a pullup resistor between CHG and the system logic voltage to indicate charge status to the  $\mu$ P. Alternatively, CHG sinks up to 20mA for an LED charge indicator.

If the charge status output feature is not required, connect  $\overline{\text{CHG}}$  to ground or leave unconnected.

#### Charge Timer

As shown in Figure 3, a fault timer prevents the battery from charging indefinitely. In prequalification mode, the charge time is internally fixed to 33min.

#### tprequal = 33min

In fast-charge mode, the charge timer is internally fixed to 660min.

#### tfstchg = 660min

When the charger exits fast-charge mode, a fixed 33min top-off mode is entered:

#### tTOPOFF = 33min

While in the constant-current fast-charge mode (Figure 2), if the MAX8819\_ reduces the battery charge current due to its internal die temperature or large system loads, it slows down the charge timer. This feature eliminates

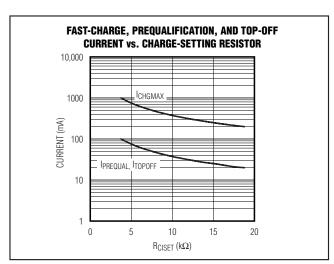

Figure 4. Calculated Charge Currents vs. R<sub>CISET</sub>

### Table 2. Calculated Charge Currents vs. RCISET

| R <sub>CISET</sub> (kΩ) | ICHGMAX<br>(mA) | IPREQUAL<br>(mA) | ITOPOFF<br>(mA) |

|-------------------------|-----------------|------------------|-----------------|

| 3.01                    | 1000            | 100              | 100             |

| 4.02                    | 746             | 75               | 75              |

| 4.99                    | 601             | 60               | 60              |

| 6.04                    | 497             | 50               | 50              |

| 6.98                    | 430             | 43               | 43              |

| 8.06                    | 372             | 37               | 37              |

| 9.09                    | 330             | 33               | 33              |

| 10                      | 300             | 30               | 30              |

| 11                      | 273             | 27               | 27              |

| 12.1                    | 248             | 25               | 25              |

| 13                      | 231             | 23               | 23              |

| 14                      | 214             | 21               | 21              |

| 15                      | 200             | 20               | 20              |

nuisance charge timer faults. When the battery charge current is between 100% and 50% of its programmed fast-charge level, the fast-charge timer runs at full speed. When the battery charge current is between 50% and 20% programmed fast-charge level, the fast-charge timer is slowed by 2x. Similarly, when the battery charge current is below 20% of the programmed fast-charge level, the fast-charge timer is paused. The fast-charge timer is not slowed or paused when the charger is in the constant voltage portion of its fast-charge mode (Figure 2) where the charge current reduces normally.

#### Charge Current (CISET)

As shown in Table 2 and Figure 4, a resistor from CISET to ground (RCISET) sets the maximum fast-charge current (ICHGMAX), the charge current in prequalification mode (IPREQUAL), and the top-off threshold (ITOPOFF). The MAX8819\_ supports values of ICHGMAX from 200mA to 1000mA. Select the RCISET as follows:

$$R_{CISET} = 2000 \times \frac{1.5V}{I_{CHGMAX}}$$

Determine I<sub>CHGMAX</sub> by considering the characteristics of the battery. It is not necessary to limit the charge current based on the capabilities of the expected AC-to-DC adapter or USB/DC input current limit, the system load, or thermal limitations of the PCB. The IC automatically lowers the charging current as necessary to accommodate for these factors.

For the selected value of RCISET, calculate ICHGMAX, IPREQUAL, and ITOPOFF as follows:

$$I_{CHGMAX} = 2000 \times \frac{1.5V}{R_{CISET}}$$

$I_{PREQUAL} = I_{TOPOFF} = 10\% \times I_{CHGMAX}$

### Step-Down Converters (REG1, REG2, REG3)

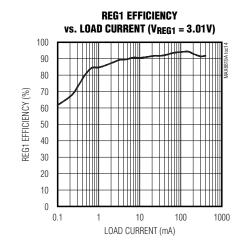

REG1, REG2, and REG3 are high-efficiency, 2MHz current-mode step-down converters with adjustable outputs. REG1 is designed to deliver 400mA for the MAX8819A/MAX8819B and 550mA for the MAX8819C. REG2 and REG3 are designed to deliver 300mA for the MAX8819A/MAX8819B and 500mA for the MAX8819C.

The PV13 step-down regulator power input must be connected to SYS. PV2 must also be connected to SYS for normal operation of REG2, but REG2 can be disabled by connecting PV2, FB2, and PG2 to GND. When REG2 is disabled, LX2 can be unconencted or connected to GND. The step-down regulators operate with VSYS from 2.6V to 5.5V. Undervoltage lockout ensures that the step-down regulators do not operate with SYS below 2.55V (max).

See the Step-Down Converter Enable/Disable (EN123) and Sequencing section for how to enable and disable the step-down converters. When enabled, the MAX8819\_ gradually ramps each output up during a 2.6ms soft-start time. When enabled, the MAX8819C sequentially ramps up each output. Soft-start eliminates input current surges when regulators are enabled.

See the *Step-Down Control Scheme* section for information about the step-down converters control scheme.

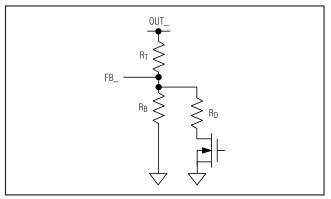

The IC uses external resistor-dividers to set the step-down output voltages between 1V and Vsys. Use at least 10µA of bias current in these dividers to ensure no change in the stability of the closed-loop system. To set the output voltage, select a value for the resistor connected between FB\_ and GND (RFBL). The recommended value is  $100k\Omega$ . Next, calculate the value of the resistor connected from FB\_ to the output (RFBH):

$$R_{FBH} = R_{FBL} \times \left( \frac{V_{OUT}}{1.0V} - 1 \right)$$

REG1, REG2, and REG3 are optimized for high, medium, and low output voltages, respectively. The highest overall efficiency occurs with V1 set to the highest output voltage and V3 set to the lowest output voltage.

#### Step-Down Control Scheme

At light load, the step-down converter switches only as needed to supply the load. This improves light-load efficiency. At higher load currents (~80mA), the step-down converter transitions to fixed 2MHz switching.

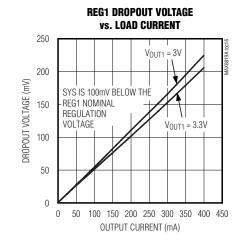

#### Step-Down Dropout and Minimum Duty Cycle

All of the step-down regulators are capable of operating in 100% duty-cycle dropout, however, REG1 has been optimized for this mode of operation. During 100% duty-cycle operation, the high-side p-channel MOSFET turns on constantly, connecting the input to the output through the inductor. The dropout voltage  $(V_{DO})$  is calculated as follows:

$$V_{DO} = I_{LOAD}(R_P + R_{LSR})$$

where:

Rp = p-channel power switch RDS(ON)

RLSR = external inductor ESR

The minimum duty cycle for all step-down regulators is 12.5% (typ), allowing a regulation voltage as low as 1V over the full SYS operating range. REG3 is optimized for low duty-cycle operation.

#### Step-Down Input Capacitor

The input capacitor in a step-down converter reduces current peaks drawn from the power source and reduces switching noise in the controller. The impedance of the input capacitor at the switching frequency must be less than that of the source impedance of the supply so that high-frequency switching currents do not pass through the input source.

The step-down regulator power inputs are critical discontinuous current paths that require careful bypassing. In the PCB layout, place the step-down converter input bypass capacitors as close as possible to each pair of switching converter power input pins (PV\_ to PG\_) to minimize parasitic inductance. If making connections to these capacitors through vias, be sure to use multiple vias to ensure that the layout does not insert excess inductance or resistance between the bypass capacitor and the power pins.

The input capacitor must meet the input ripple current requirement imposed by the step-down converter. Ceramic capacitors are preferred due to their low ESR and resilience to power-up surge currents. Choose the input capacitor so that its temperature rise due to input ripple-current does not exceed approximately  $+10^{\circ}$ C. For a step-down DC-DC converter, the maximum input ripple current is half of the output current. This maximum input ripple current occurs when the step-down converter operates at 50% duty factor (VIN = 2 x VOUT).

Bypass PV13 to PG1 and PG3 with a  $4.7\mu F$  ceramic capacitor. If REG2 is required, bypass PV2 to PG2 with a  $2.2\mu F$  capacitor. Use capacitors that maintain their capacitance over temperature and DC bias. Ceramic capacitors with an X7R or X5R temperature characteristic generally perform well. The capacitor voltage rating should be 6.3V or greater.

#### Step-Down Output Capacitors

The output capacitance keeps output ripple small and ensures control-loop stability. The output capacitor must have low impedance at the switching frequency. Ceramic, polymer, and tantalum capacitors are suitable with ceramic exhibiting the lowest ESR and lowest high-frequency impedance. The MAX8819A/MAX8819B require at least 10µF of output capacitance. The MAX8819C requires ar least 22µF of output capacitance.

As the case sizes of ceramic surface-mount capacitors decreases, their capacitance vs. DC bias voltage characteristic becomes poor. Due to this characteristic, it is possible for 0805 capacitors to perform well while 0603 capacitors of the same value may not. The MAX8819A/ MAX8819B require a nominal output capacitance of  $10\mu F$ , however, after their DC bias voltage derating, the output capacitance must be at least  $7.5\mu F$ .

#### Step-Down Inductor

Choose the step-down converter inductance to be  $4.7\mu H$ . The minimum recommended saturation current requirement is 700mA. In PWM mode, the peak inductor currents are equal to the load current plus one half of the inductor ripple current. See Table 3 for suggested inductors.

**Table 3. Suggested Inductors**

| MANUFACTURER | SERIES     | INDUCTANCE<br>(µH) | ESR (m $\Omega$ ) | CURRENT RATING (mA) | DIMENSIONS<br>(mm)                               |

|--------------|------------|--------------------|-------------------|---------------------|--------------------------------------------------|

| Sumida       | CDRH2D11HP | 4.7                | 190               | 750                 | $3.0 \times 3.0 \times 1.2 = (10.8 \text{mm})^3$ |

| Sumida       | CDH2D09    | 4.7                | 218               | 700                 | $3.0 \times 3.0 \times 1.0 = (9.0 \text{mm})^3$  |

| Taiva Vudan  | NR3012     | 4.7                | 130               | 770                 | $3.0 \times 3.0 \times 1.2 = (10.8 \text{mm})^3$ |

| Taiyo Yuden  | NR3010     | 4.7                | 190               | 750                 | $3.0 \times 3.0 \times 1.0 = (9.0 \text{mm})^3$  |

| TDK          | VLF3012    | 4.7                | 160               | 740                 | $2.8 \times 2.6 \times 1.2 = (8.7 \text{mm})^3$  |

| TDK          | VLF3010    | 4.7                | 240               | 700                 | $2.8 \times 2.6 \times 1.0 = (7.3 \text{mm})^3$  |

| TOKO         | DE2812C    | 4.7                | 130               | 880                 | $3.0 \times 2.8 \times 1.2 = (10.8 \text{mm})^3$ |

| FDK          | MIPF2520   | 4.7                | 110               | 1100                | $2.5 \times 2.0 \times 1.0 = (5 \text{mm})^3$    |

| FDK          | MIPF2016   | 4.7                | 160               | 900                 | $2.0 \times 1.6 \times 1.0 = (3.2 \text{mm})^3$  |

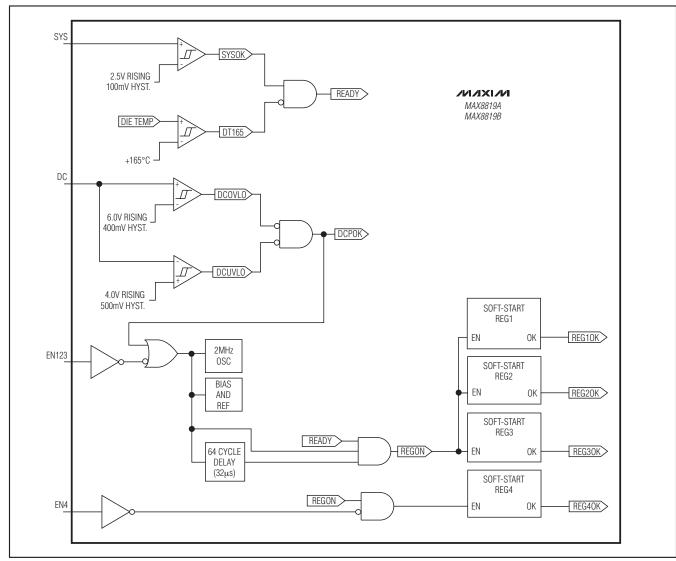

Figure 5a. MAX8819A/MAX8819B Enable/Disable Logic

The peak-to-peak inductor ripple current during PWM operation is calculated as follows:

$$I_{P-P} = \frac{V_{OUT}(V_{SYS} - V_{OUT})}{V_{SYS} \times f_S \times L}$$

where fs is the 2MHz switching frequency.

The peak inductor current during PWM operation is calculated as follows:

$$I_{L\_PEAK} = I_{LOAD} + \frac{I_{P\_P}}{2}$$

#### Step-Down Converter Maximum Output Current

The maximum regulated output current from a step-down converter is ultimately determined by the p-channel peak current limit (IPK). The calculation follows:

$$IOUT_MAX = IPK - (IP-P/2)$$

For example, if VSYS = 5.3V, VOUT = 3V, fS = 2MHz, L = 4.7  $\mu$ H, and IPK = 0.6A:

$I_{P-P} = 3V \times (5.3V - 3V)/(5.3V \times 2MHz \times 4.7\mu H) = 0.138A$ then  $I_{OUT} \text{ MAX} = 0.6A - (0.138A/2) = 0.531A$ .

22 \_\_\_\_\_\_\_/N/1X//N

Figure 5b. MAX8819C Enable Logic

As the load current is increased beyond this point, the output voltage sags and the converter goes out of regulation because the inductor current cannot increase above the p-channel peak current limit.

#### Step-Down Converter Short-Circuit Protection

The step-down converter implements short-circuit protection by monitoring the feedback voltage, VFB\_. After soft-start, if VFB\_ drops below 0.23V, the converter reduces its switching frequency to fs/3. The inductor current still reaches the p-channel peak current limit, however, at one-third the frequency. Therefore, the output and input currents are reduced to approximately one-third of the maximum value in response to an output short circuit to

ground. When the short is removed, the inductor current raises the voltage on the output capacitor and the step-down converter resumes normal operation.

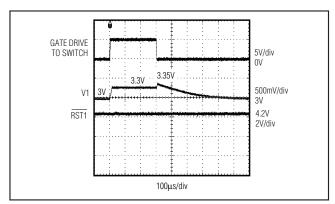

#### REG1 Reset (RST1)

RST1 is an active-low, open-drain output that pulls low to indicate that FB1 is below its regulation threshold. RST1 goes high 200ms after FB1 reaches its regulation threshold. RST1 is high-impedance when EN123 is high. See Figures 6 and 7.

A 50µs blanking delay is provided when FB1 is falling, so that RST1 does not glitch if the REG1 output voltage is dynamically adjusted by altering the resistors in its feedback network.

MIXIM

Figure 6. MAX8819A/MAX8819B Enable/Disable Waveforms Example

#### Step-Down Converter Active Discharge in Shutdown

Each MAX8819\_ step-down converter (REG1, REG2, REG3) has an internal  $1k\Omega$  resistor that discharges the output capacitor when the converter is off. The discharge resistors ensure that the load circuitry powers down completely. The internal discharge resistors are connected when a converter is disabled and when the device is in UVLO with an input voltage greater than 1.0V. With an input voltage less than 1.0V the internal discharge resistors are not activated.

#### Step-Down Converter Enable/ Disable (EN123) and Sequencing

Figure 5a shows the MAX8819A/MAX8819B enable and disable logic. Figure 5b shows the MAX8819C

enable/disable logic. Figure 6 shows an example of enable and disable waveforms for the MAX8819A/MAX8819B.

#### Figure 6 notes:

- 1) The device is off with no external power applied to DC. The system voltage (VSYS) is equal to the battery voltage (VBAT).

- 2) An external supply is applied to DC that causes the step-down converter to power up after the DC-to-SYS soft-start time (tss-D-s). When the DC input is valid and DLIM[1:2] ≠ 11, Vsys increases.