#### **ABSOLUTE MAXIMUM RATINGS**

| PGND to SGND                                        | 0.3V to +0.3V                                    |

|-----------------------------------------------------|--------------------------------------------------|

| PV <sub>DD</sub> to SV <sub>DD</sub>                | -0.3V to +0.3V                                   |

| PVss to SVss                                        | 0.3V to +0.3V                                    |

| PV <sub>DD</sub> and SV <sub>DD</sub> to PGND or Se | GND0.3V to +4V                                   |

| PVss and SVss to PGND or SG                         | GND4V to +0.3V                                   |

| IN_ to SGND                                         | 0.3V to +0.3V                                    |

| SHDN_ to SGND                                       | (SGND - 0.3V) to (SV <sub>DD</sub> + 0.3V)       |

| OUT_ to SGND                                        | ( $SV_{SS}$ - 0.3V) to ( $SV_{DD}$ + 0.3V)       |

| C1P to PGND                                         | (PGND - 0.3V) to (PV <sub>DD</sub> + 0.3V)       |

| C1N to PGND                                         | (PV <sub>SS</sub> - $0.3V$ ) to (PGND + $0.3V$ ) |

| Output Short Circuit to GND or                      | V <sub>DD</sub> Continuous                       |

|                                                     |                                                  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|-------------------------------------------------------|

| 14-Pin TSSOP (derate 9.1mW/°C above +70°C)727mW       |

| 16-Bump UCSP (derate 15.2mW/°C above +70°C)1212mW     |

| Junction Temperature+150°C                            |

| Operating Temperature Range40°C to +85°C              |

| Storage Temperature Range65°C to +150°C               |

| Bump Temperature (soldering) (Note 1)                 |

| Infrared (15s)+220°C                                  |

| Vapor Phase (60s)+215°C                               |

| _ead Temperature (soldering, 10s)+300°C               |

Note 1: This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(PV_{DD} = SV_{DD} = 3V, PGND = SGND = 0, \overline{SHDNL} = \overline{SHDNR} = SV_{DD}, C1 = C2 = 2.2\mu F, R_{IN} = R_F = 10k\Omega, R_L = \infty, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.) \text{ (Note 2)}$

| PARAMETER                    | SYMBOL            | CONDITIONS                         |                             | MIN                       | TYP | MAX                       | UNITS |

|------------------------------|-------------------|------------------------------------|-----------------------------|---------------------------|-----|---------------------------|-------|

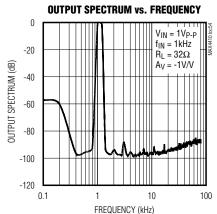

| Supply Voltage Range         | $V_{DD}$          | Guaranteed by PSRR test            |                             | 1.8                       |     | 3.6                       | V     |

| 0: 10 10                     |                   | One channel enabled                |                             |                           | 4   |                           | mA    |

| Quiescent Supply Current     | IDD               | Two channels enabled               |                             |                           | 7   | 11.5                      |       |

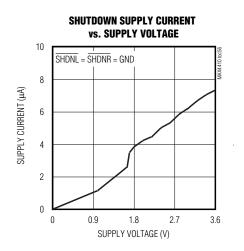

| Shutdown Supply Current      | ISHDN             | SHDNL = SHDNR = 0                  | AND                         |                           | 6   | 10                        | μΑ    |

| OLIDA. Through alde          |                   | V <sub>I</sub> H                   |                             | 0.7 x<br>SV <sub>DD</sub> |     |                           | V     |

| SHDN_ Thresholds             |                   |                                    |                             |                           |     | 0.3 x<br>SV <sub>DD</sub> |       |

| SHDN_ Input Leakage Current  |                   |                                    |                             | -1                        |     | +1                        | μΑ    |

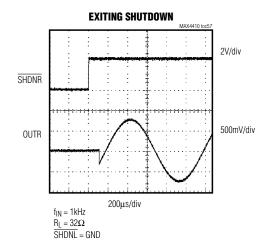

| SHDN_ to Full Operation      | tson              |                                    |                             |                           | 175 |                           | μs    |

| CHARGE PUMP                  |                   |                                    |                             |                           |     |                           |       |

| Oscillator Frequency         | fosc              |                                    |                             | 272                       | 320 | 368                       | kHz   |

| AMPLIFIERS                   |                   |                                    |                             |                           |     |                           |       |

| Input Offset Voltage         | Vos               | Input AC-coupled, $R_L = 32\Omega$ |                             |                           | 0.5 | 2.4                       | mV    |

| Input Bias Current           | I <sub>BIAS</sub> |                                    |                             | -100                      |     | +100                      | nA    |

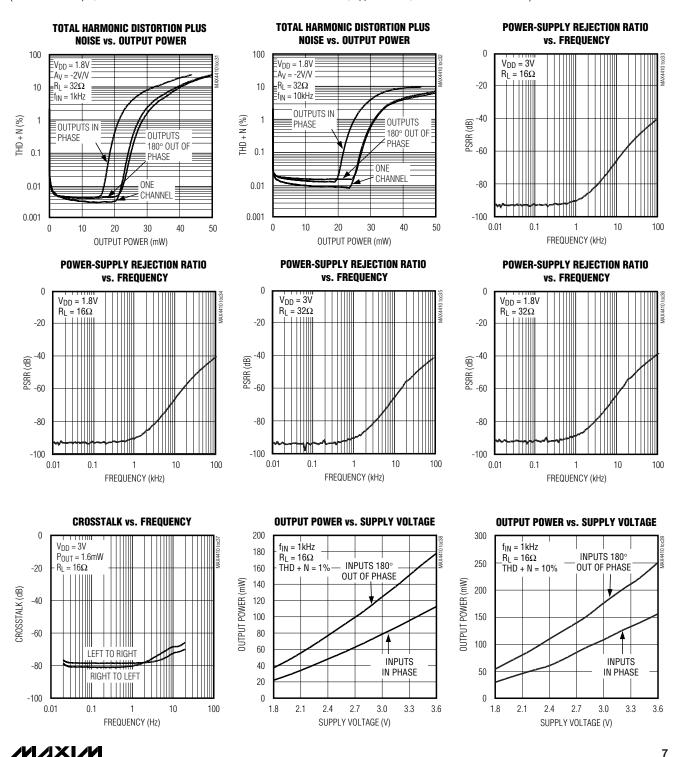

| Power-Supply Rejection Ratio | n Ratio PSRR      | $1.8V \le V_{DD} \le 3.6V$         | DC                          | 75                        | 90  |                           | dB    |

|                              |                   | 200mV <sub>P-P</sub> ripple        | f <sub>RIPPLE</sub> = 1kHz  |                           | 90  |                           |       |

|                              |                   |                                    | f <sub>RIPPLE</sub> = 20kHz |                           | 55  |                           |       |

| Cutant Banan                 | Pout              | THD + N = 1%                       | $R_L = 32\Omega$            |                           | 65  |                           | mW    |

| Output Power                 |                   | $R_{L} = 16\Omega$                 |                             | 40                        | 80  |                           | 11100 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(PV_{DD} = SV_{DD} = 3V, PGND = SGND = 0, \overline{SHDNL} = \overline{SHDNR} = SV_{DD}, C1 = C2 = 2.2\mu F, R_{IN} = R_F = 10k\Omega, R_L = \infty, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                               | SYMBOL  | CONDITIONS                                               |                                         | MIN TYP | MAX | UNITS |

|-----------------------------------------|---------|----------------------------------------------------------|-----------------------------------------|---------|-----|-------|

| Total Harmonic Distortion Plus<br>Noise | THD + N | f <sub>IN</sub> = 1kHz                                   | $R_L = 32\Omega$ ,<br>$P_{OUT} = 25$ mW | 0.00    | 3   | %     |

|                                         |         |                                                          | $R_L = 16\Omega,$<br>$P_{OUT} = 50$ mW  | 0.00    | 3   |       |

| Signal-to-Noise Ratio                   | SNR     | $R_L = 32\Omega$ , $P_{OUT} = 20$ mW, $f_{IN} = 1$ kHz   |                                         | 95      |     | dB    |

| Slew Rate                               | SR      |                                                          |                                         | 0.8     |     | V/µs  |

| Maximum Capacitive Load                 | CL      | No sustained oscillations                                |                                         | 300     |     | рF    |

| Crosstalk                               |         | $R_L = 16\Omega$ , $P_{OUT} = 1.6$ mW, $f_{IN} = 10$ kHz |                                         | 70      |     | dB    |

| Thermal Shutdown Threshold              |         |                                                          |                                         | 140     |     | °C    |

| Thermal Shutdown Hysteresis             |         |                                                          |                                         | 15      |     | °C    |

| ESD Protection                          |         | Human body model (OL                                     | JTR, OUTL)                              | ±8      |     | kV    |

Note 2: All specifications are 100% tested at  $T_A = +25$ °C; temperature limits are guaranteed by design.

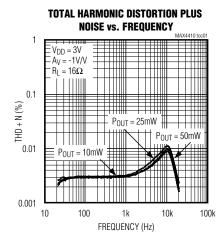

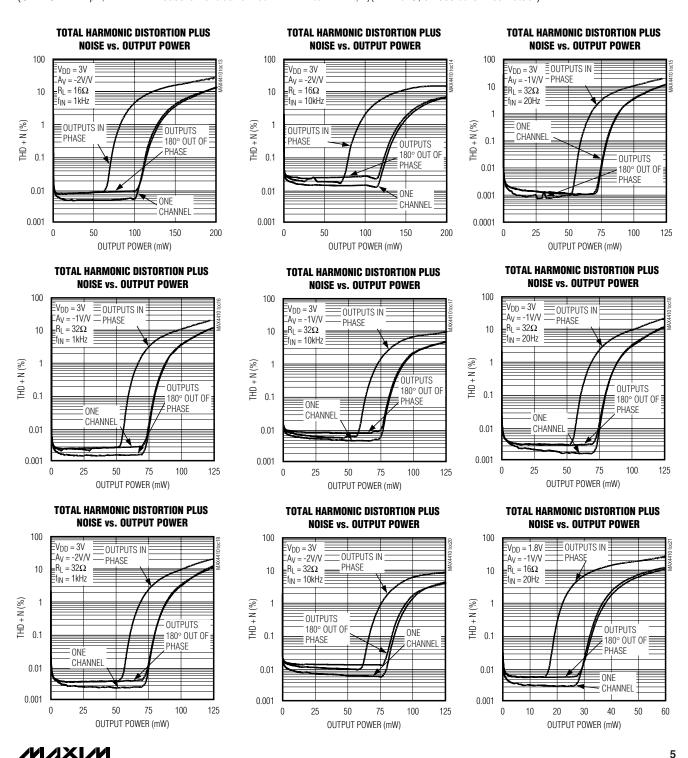

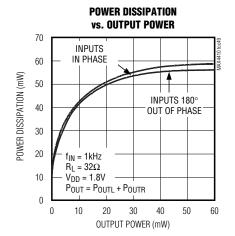

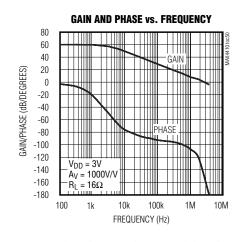

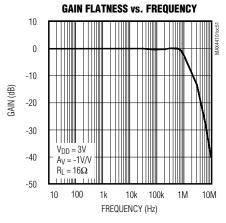

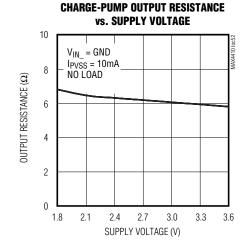

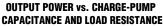

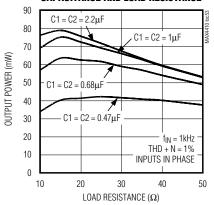

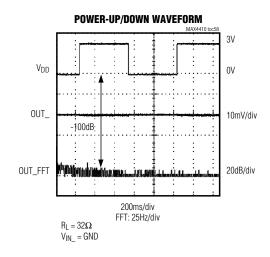

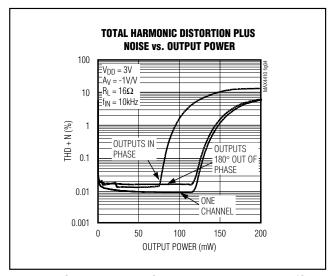

### Typical Operating Characteristics

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, TA = +25°C, unless otherwise noted.)

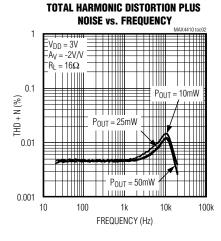

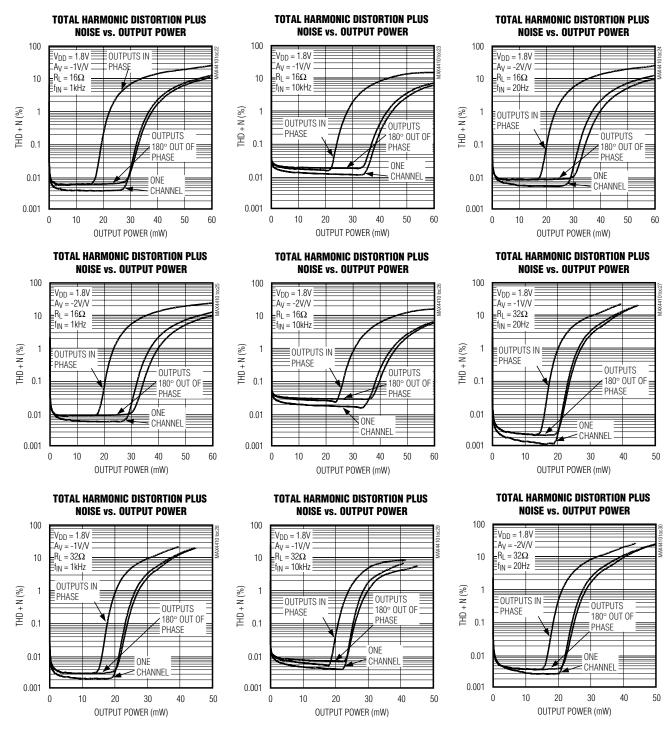

### Typical Operating Characteristics (continued)

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

Downloaded from Arrow.com.

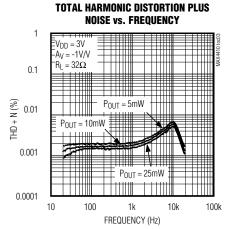

### Typical Operating Characteristics (continued)

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

Downloaded from Arrow.com.

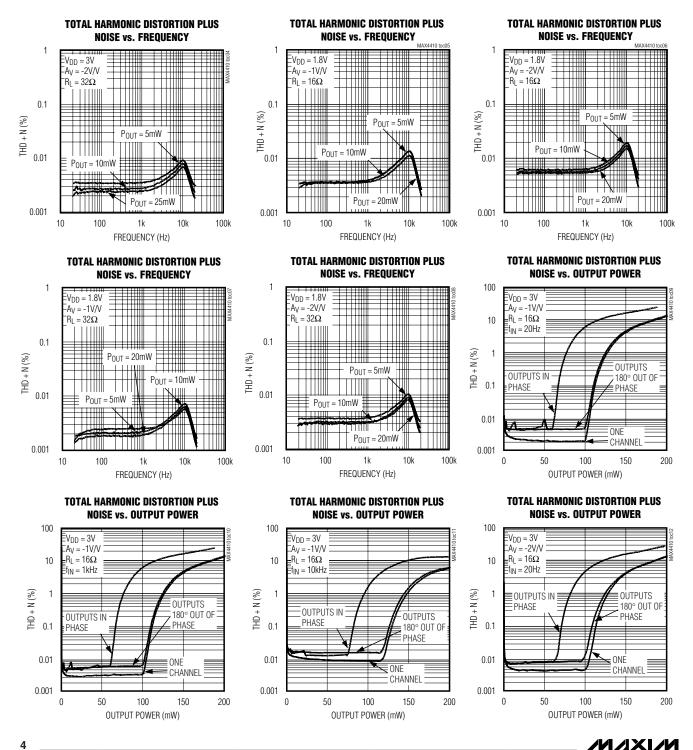

### Typical Operating Characteristics (continued)

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

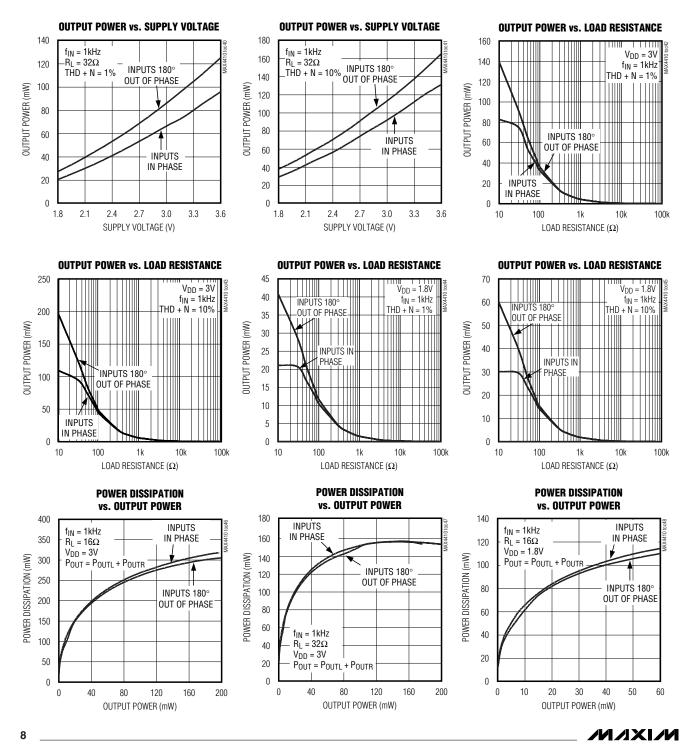

### Typical Operating Characteristics (continued)

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(C1 = C2 = 2.2µF, THD + N measurement bandwidth = 22Hz to 22kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(C1 = C2 =  $2.2\mu$ F, THD + N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25$ °C, unless otherwise noted.)

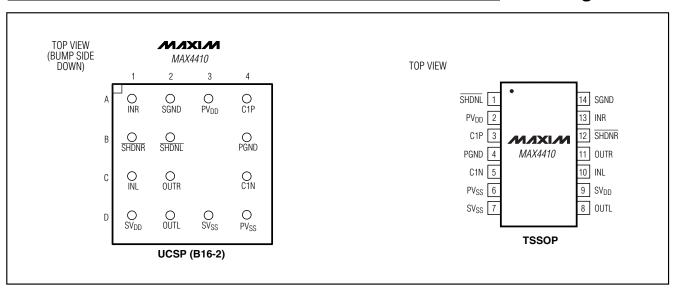

### Pin Description

| PIN   | ВИМР |                  |                                                                                           |  |  |

|-------|------|------------------|-------------------------------------------------------------------------------------------|--|--|

| TSSOP | UCSP | NAME             | FUNCTION                                                                                  |  |  |

| 1     | B2   | SHDNL            | Active-Low, Left-Channel Shutdown. Connect to V <sub>DD</sub> for normal operation.       |  |  |

| 2     | А3   | PV <sub>DD</sub> | Charge-Pump Power Supply. Powers charge-pump inverter, charge-pump logic, and oscillator. |  |  |

| 3     | A4   | C1P              | Flying Capacitor Positive Terminal                                                        |  |  |

| 4     | B4   | PGND             | Power Ground. Connect to SGND.                                                            |  |  |

| 5     | C4   | C1N              | Flying Capacitor Negative Terminal                                                        |  |  |

| 6     | D4   | PVss             | Charge-Pump Output                                                                        |  |  |

| 7     | D3   | SV <sub>SS</sub> | Amplifier Negative Power Supply. Connect to PVSS.                                         |  |  |

| 8     | D2   | OUTL             | Left-Channel Output                                                                       |  |  |

| 9     | D1   | SV <sub>DD</sub> | Amplifier Positive Power Supply. Connect to PVDD.                                         |  |  |

| 10    | C1   | INL              | Left-Channel Audio Input                                                                  |  |  |

| 11    | C2   | OUTR             | Right-Channel Output                                                                      |  |  |

| 12    | B1   | SHDNR            | Active-Low, Right-Channel Shutdown. Connect to V <sub>DD</sub> for normal operation.      |  |  |

| 13    | A1   | INR              | Right-Channel Audio Input                                                                 |  |  |

| 14    | A2   | SGND             | Signal Ground. Connect to PGND.                                                           |  |  |

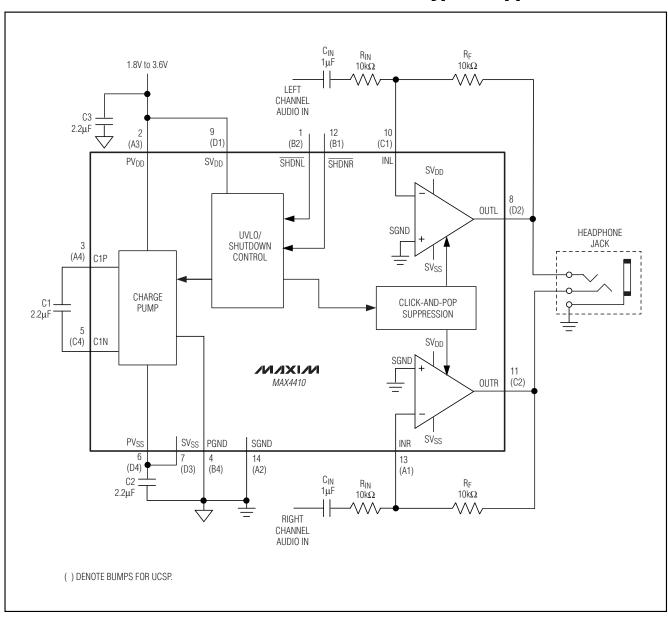

### Detailed Description

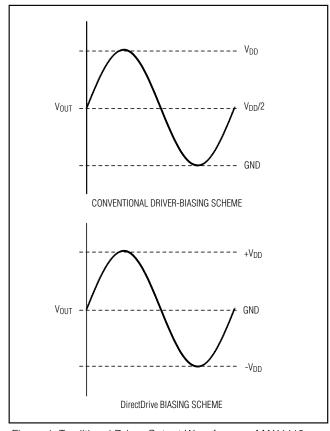

The MAX4410 stereo headphone driver features Maxim's DirectDrive architecture, eliminating the large outputcoupling capacitors required by traditional single-supply headphone drivers. The device consists of two 80mW Class AB headphone drivers, undervoltage lockout (UVLO)/shutdown control, charge-pump, and comprehensive click-and-pop suppression circuitry (see Typical Application Circuit). The charge pump inverts the positive supply (PVDD), creating a negative supply (PVSS). The headphone drivers operate from these bipolar supplies with their outputs biased about GND (Figure 1). The drivers have almost twice the supply range compared to other 3V single-supply drivers, increasing the available output power. The benefit of this GND bias is that the driver outputs do not have a DC component typically V<sub>DD</sub>/2. Thus, the large DC-blocking capacitors are unnecessary, improving frequency response while conserving board space and system cost.

Each channel has independent left/right, active-low shutdown controls, making it possible to optimize power savings in mixed-mode, mono/stereo operation. The device features an undervoltage lockout that prevents operation from an insufficient power supply and click-and-pop suppression that eliminates audible transients on startup and shutdown. Additionally, the MAX4410 features thermal overload and short-circuit protection and can withstand ±8kV ESD strikes on the output pins.

#### **DirectDrive**

Traditional single-supply headphone drivers have their outputs biased about a nominal DC voltage (typically half the supply) for maximum dynamic range. Large coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone driver.

Maxim's DirectDrive architecture uses a charge pump to create an internal negative supply voltage. This allows the outputs of the MAX4410 to be biased about GND, almost doubling dynamic range while operating from a single supply. With no DC component, there is no need for the large DC-blocking capacitors. Instead of two large (220µF, typ) tantalum capacitors, the MAX4410 charge pump requires two small ceramic capacitors, conserving board space, reducing cost, and improving the frequency response of the headphone driver. See the Output Power vs. Charge-Pump Capacitance and Load Resistance graph in the *Typical Operating Characteristics* for details of the possible

Figure 1. Traditional Driver Output Waveform vs. MAX4410 Output Waveform

capacitor sizes. There is a low DC voltage on the driver outputs due to amplifier offset. However, the offset of the MAX4410 is typically 0.5mV, which, when combined with a  $32\Omega$  load, results in less than 16µA of DC current flow to the headphones.

Previous attempts to eliminate the output-coupling capacitors involved biasing the headphone return (sleeve) to the DC-bias voltage of the headphone amplifiers. This method raises some issues:

- 1) When combining a microphone and headphone on a single connector, the microphone bias scheme typically requires a 0V reference.

- 2) The sleeve is typically grounded to the chassis. Using this biasing approach, the sleeve must be isolated from system ground, complicating product design.

- During an ESD strike, the driver's ESD structures are the only path to system ground. Thus, the driver must be able to withstand the full ESD strike.

4) When using the headphone jack as a line out to other equipment, the bias voltage on the sleeve may conflict with the ground potential from other equipment, resulting in possible damage to the drivers.

#### Low-Frequency Response

In addition to the cost and size disadvantages of the DCblocking capacitors required by conventional headphone amplifiers, these capacitors limit the amplifier's low-frequency response and can distort the audio signal.

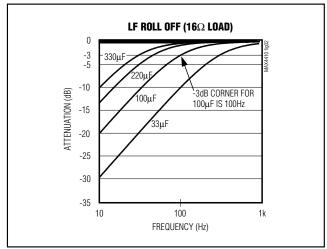

The impedance of the headphone load and the DCblocking capacitor form a highpass filter with the -3dB point set by:

$$f_{-3dB} = \frac{1}{2\pi R_I C_{OUT}}$$

where R<sub>L</sub> is the headphone impedance and C<sub>OUT</sub> is the DC-blocking capacitor value. The highpass filter is required by conventional single-ended, single power-supply headphone drivers to block the midrail DC bias component of the audio signal from the headphones. The drawback to the filter is that it can attenuate low-frequency signals. Larger values of C<sub>OUT</sub> reduce this effect but result in physically larger, more expensive capacitors. Figure 2 shows the relationship between the size of C<sub>OUT</sub> and the resulting low-frequency attenuation. Note that the -3dB point for a 16 $\Omega$  headphone with a 100 $\mu$ F blocking capacitor is 100Hz, well within the normal audio band, resulting in low-frequency attenuation of the reproduced signal.

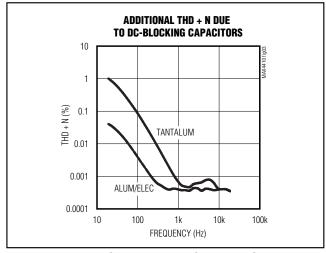

2) The voltage coefficient of the DC-blocking capacitor contributes distortion to the reproduced audio signal as the capacitance value varies as a function of the voltage change across the capacitor. At low frequencies, the reactance of the capacitor dominates at frequencies below the -3dB point and the voltage coefficient appears as frequency-dependent distortion. Figure 3 shows the THD + N introduced by two different capacitor dielectric types. Note that below 100Hz, THD + N increases rapidly.

The combination of low-frequency attenuation and frequency-dependent distortion compromises audio reproduction in portable audio equipment that emphasizes low-frequency effects such as multimedia laptops, as well as MP3, CD, and DVD players. By eliminating the DC-blocking capacitors through DirectDrive technology, these capacitor-related deficiencies are eliminated.

#### Charge Pump

The MAX4410 features a low-noise charge pump. The 320kHz switching frequency is well beyond the audio range, and thus does not interfere with the audio signals. The switch drivers feature a controlled switching speed that minimizes noise generated by turn-on and turn-off transients. By limiting the switching speed of the switches, the di/dt noise caused by the parasitic bond wire and trace inductance is minimized. Although not typically required, additional high-frequency noise attenuation can be achieved by increasing the size of C2 (see *Typical Application Circuit*).

Figure 2. Low-Frequency Attenuation for Common DC-Blocking Capacitor Values

Figure 3. Distortion Contributed by DC-Blocking Capacitors

#### Shutdown

The MAX4410 features two shutdown controls allowing either channel to be shut down or muted independently. SHDNL controls the left channel while SHDNR controls the right channel. Driving either SHDN\_ low disables the respective channel, sets the driver output impedance to about  $1k\Omega$ , and reduces the supply current to less than  $10\mu A$ . When both SHDN\_ inputs are driven low, the charge pump is also disabled, further reducing supply current draw to  $6\mu A$ . The charge pump is enabled once either SHDN\_ input is driven high.

#### Click-and-Pop Suppression

In traditional single-supply audio drivers, the output-coupling capacitor is a major contributor of audible clicks and pops. Upon startup, the driver charges the coupling capacitor to its bias voltage, typically half the supply. Likewise, on shutdown the capacitor is discharged to GND. This results in a DC shift across the capacitor, which in turn, appears as an audible transient at the speaker. Since the MAX4410 does not require output-coupling capacitors, this does not arise.

Additionally, the MAX4410 features extensive click-andpop suppression that eliminates any audible transient sources internal to the device. The Power-Up/Down Waveform in the *Typical Operating Characteristics* shows that there are minimal spectral components in the audible range at the output upon startup or shutdown.

In most applications, the output of the preamplifier driving the MAX4410 has a DC bias of typically half the supply. At startup, the input-coupling capacitor is charged to the preamplifier's DC-bias voltage through the RF of the MAX4410, resulting in a DC shift across the capacitor and an audible click/pop. Delaying the rise of the MAX4410's  $\overline{\rm SHDN}_{-}$  signals 4 to 5 time constants (200ms to 300ms) based on RIN and CIN relative to the start of the preamplifier eliminates this click/pop caused by the input filter.

### Applications Information Power Dissipation

Under normal operating conditions, linear power amplifiers can dissipate a significant amount of power. The maximum power dissipation for each package is given in the *Absolute Maximum Ratings* section under Continuous Power Dissipation or can be calculated by the following equation:

$$P_{DISSPKG(MAX)} = \frac{T_{J(MAX)} - T_{A}}{\theta_{JA}}$$

where  $T_{J(MAX)}$  is +150°C,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the reciprocal of the derating factor in

°C/W as specified in the *Absolute Maximum Ratings* section. For example,  $\theta_{JA}$  of the TSSOP package is +109.9°C/W.

The MAX4410 has two sources of power dissipation, the charge pump and the two drivers. If the power dissipation for a given application exceeds the maximum allowed for a given package, either reduce V<sub>DD</sub>, increase load impedance, decrease the ambient temperature, or add heat sinking to the device. Large output, supply, and ground traces improve the maximum power dissipation in the package.

Thermal overload protection limits total power dissipation in the MAX4410. When the junction temperature exceeds +140°C, the thermal protection circuitry disables the amplifier output stage. The amplifiers are enabled once the junction temperature cools by 15°C. This results in a pulsing output under continuous thermal overload conditions.

#### **Output Power**

The device has been specified for the worst-case scenario— when both inputs are in phase. Under this condition, the drivers simultaneously draw current from the charge pump, leading to a slight loss in headroom of Vss. In typical stereo audio applications, the left and right signals have differences in both magnitude and phase, subsequently leading to an increase in the maximum attainable output power. Figure 4 shows the two extreme cases for in and out of phase. In reality, the available power lies between these extremes.

Figure 4. Output Power vs. Supply Voltage with Inputs In/Out of Phase

14 \_\_\_\_\_\_ M/XI/N

#### Powering Other Circuits from a Negative Supply

An additional benefit of the MAX4410 is the internally generated, negative supply voltage (-VDD). This voltage is used by the MAX4410 to provide the ground-referenced output level. It can, however, also be used to power other devices within a design. Current draw from this negative supply (PVss) should be limited to 5mA, exceeding this will affect the operation of the headphone driver. The negative supply voltage appears on the PVss pin. A typical application is a negative supply to adjust the contrast of LCD modules.

When considering the use of PV<sub>SS</sub> in this manner, note that the charge-pump voltage at PV<sub>SS</sub> is roughly proportional to -V<sub>DD</sub> and is not a regulated voltage. The charge-pump output impedance plot appears in the *Typical Operating Characteristics*.

### **Component Selection Gain-Setting Resistors**

External feedback components set the gain of the MAX4410. Resistors R<sub>F</sub> and R<sub>IN</sub> (see *Typical Application Circuit*) set the gain of each amplifier as follows:

$$A_V = -\left(\frac{R_F}{R_{IN}}\right)$$

To minimize V<sub>OS</sub>, set R<sub>F</sub> equal to  $10k\Omega$ . Values other than  $10k\Omega$  increase V<sub>OS</sub> due to the input bias current, which in turn increases the amount of DC current flow to the speaker.

#### Compensation Capacitor

The stability of the MAX4410 is affected by the value of the feedback resistor (R<sub>F</sub>). The combination of R<sub>F</sub> and the input and parasitic trace capacitance introduces an additional pole. Adding a capacitor in parallel with R<sub>F</sub> compensates for this pole. Under typical conditions with proper layout, the device is stable without the additional capacitor.

#### Input Filtering

The input capacitor ( $C_{IN}$ ), in conjunction with  $R_{IN}$ , forms a highpass filter that removes the DC bias from an incoming signal (see *Typical Application Circuit*). The AC-coupling capacitor allows the amplifier to bias the signal to

an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose  $R_{\text{IN}}$  according to the *Gain-Setting Resistors* section. Choose the  $C_{\text{IN}}$  such that  $f_{\text{-}3d\text{B}}$  is well below the lowest frequency of interest. Setting  $f_{\text{-}3d\text{B}}$  too high affects the low-frequency response of the amplifier. Use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, may result in increased distortion at low frequencies.

Other considerations when designing the input filter include the constraints of the overall system and the actual frequency band of interest. Although high-fidelity audio calls for a flat-gain response between 20Hz and 20kHz, portable voice-reproduction devices such as cellular phones and two-way radios need only concentrate on the frequency range of the spoken human voice (typically 300Hz to 3.5kHz). In addition, speakers used in portable devices typically have a poor response below 150Hz. Taking these two factors into consideration, the input filter may not need to be designed for a 20Hz to 20kHz response, saving both board space and cost due to the use of smaller capacitors.

#### Charge-Pump Capacitor Selection

Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low-ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric. Table 1 lists suggested manufacturers.

#### Flying Capacitor (C1)

The value of the flying capacitor (C1) affects the load regulation and output resistance of the charge pump. A C1 value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Increasing the value of C1 improves load regulation and reduces the charge-pump output resistance to an extent. See the Output Power vs. Charge-Pump Capacitance and Load Resistance graph in the *Typical Operating Characteristics*. Above 2.2µF, the on-resistance of the switches and the ESR of C1 and C2 dominate.

**Table 1. Suggested Capacitor Manufacturers**

| SUPPLIER    | PHONE        | FAX          | WEBSITE               |

|-------------|--------------|--------------|-----------------------|

| Taiyo Yuden | 800-348-2496 | 847-925-0899 | www.t-yuden.com       |

| TDK         | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

Note: Please indicate you are using the MAX4410 when contacting these component suppliers.

#### Output Capacitor (C2)

The output capacitor value and ESR directly affect the ripple at PVss. Increasing the value of C2 reduces output ripple. Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels. See the Output Power vs. Charge-Pump Capacitance and Load Resistance graph in the *Typical Operating Characteristics*.

#### Power-Supply Bypass Capacitor

The power-supply bypass capacitor (C3) lowers the output impedance of the power supply, and reduces the impact of the MAX4410's charge-pump switching transients. Bypass PV<sub>DD</sub> with C3, the same value as C1, and place it physically close to the PV<sub>DD</sub> and PGND pins (refer to the MAX4410 EV kit for a suggested layout).

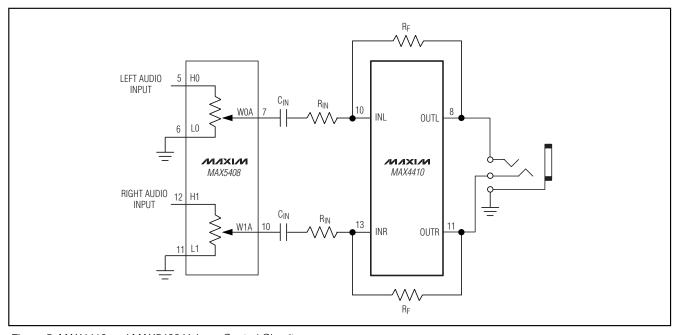

#### **Adding Volume Control**

The addition of a digital potentiometer provides simple volume control. Figure 5 shows the MAX4410 with the MAX5408 dual log taper digital potentiometer used as an input attenuator. Connect the high terminal of the MAX5408 to the audio input, the low terminal to ground and the wiper to  $C_{\rm IN}$ . Setting the wiper to the top position passes the audio signal unattenuated. Setting the wiper to the lowest position fully attenuates the input.

#### **Layout and Grounding**

Proper layout and grounding are essential for optimum performance. Connect PGND and SGND together at a single point on the PC board. Connect all components associated with the charge pump (C2 and C3) to the PGND plane. Connect PVDD and SVDD together at the device. Connect PVSS and SVSS together at the device. Bypassing of both supplies is accomplished by charge-pump capacitors C2 and C3 (see *Typical Application Circuit*). Place capacitors C2 and C3 as close to the device as possible. Route PGND and all traces that carry switching transients away from SGND and the traces and components in the audio signal path. Refer to the layout example in the MAX4410 EV kit datasheet.

When using the MAX4410 in a UCSP package, make sure the traces to OUTR (bump C2) are wide enough to handle the maximum expected current flow. Multiple traces may be necessary.

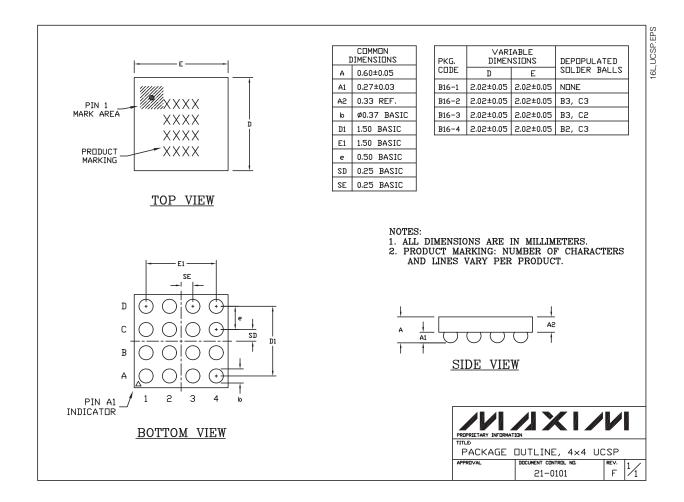

#### **UCSP Considerations**

For general UCSP information and PC layout considerations, refer to the Maxim Application Note: *Wafer-Level Ultra Chip-Scale Package*.

Figure 5. MAX4410 and MAX5408 Volume Control Circuit

### **Typical Application Circuit**

### **Pin Configurations**

**Chip Information**

TRANSISTOR COUNT: 4295

PROCESS: BiCMOS

18 \_\_\_\_\_\_ **/// ///**

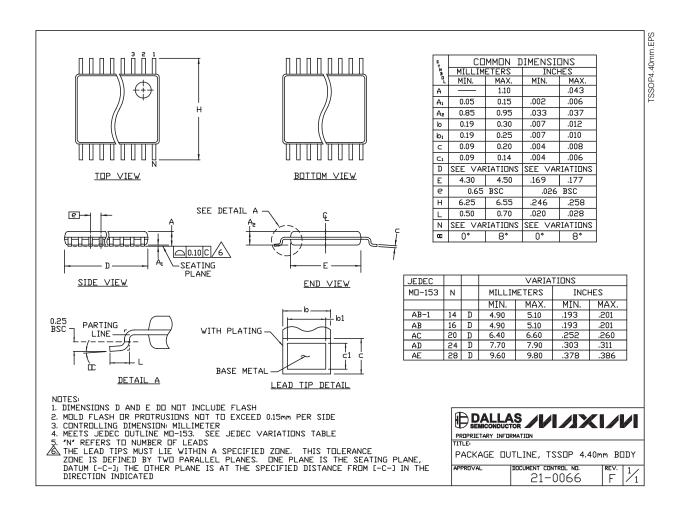

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

20 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600