# LC898300XA

## Recommended Operating Conditions at Ta = -30 to $85^{\circ}$ C, V<sub>SS</sub> = 0V

| Parameter            | Question          | Conditions       |     | L Locit |                 |      |

|----------------------|-------------------|------------------|-----|---------|-----------------|------|

|                      | Symbol            | TIDOI CONditions | min | typ     | max             | Unit |

| Supply voltage range | V <sub>DD</sub>   |                  | 2.7 | 3.0     | 3.3             | V    |

| Input voltage range  | V <sub>IN</sub> 1 |                  | 0   | -       | V <sub>DD</sub> | V    |

\*1: Input voltage without diode connection to V<sub>DD</sub>. (SDA, SCL)

### **Electrical Characteristics**

| Devenueter                                  | Querra ha a l                                                                                      | Oracliticas              | Applied air            |                    | Linit |                    |      |

|---------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|------------------------|--------------------|-------|--------------------|------|

| Parameter                                   | Symbol                                                                                             | Conditions               | Applied pin            | min                | typ   | max                | Unit |

| DC characteristics at $V_{SS} = 0V$ ,       | <b>DC characteristics</b> at V <sub>SS</sub> = 0V, V <sub>DD</sub> = 2.7 to 3.3V, Ta = -30 to 85°C |                          |                        |                    |       |                    |      |

| High level input voltage                    | V <sub>IH</sub> 1                                                                                  | CMOS                     | TEST                   | 0.7V <sub>DD</sub> | -     | -                  | V    |

| Low level input voltage                     | V <sub>IL</sub> 1                                                                                  |                          |                        | -                  | -     | 0.2V <sub>DD</sub> | V    |

| High level input voltage                    | V <sub>IH</sub> 2                                                                                  | CMOS                     | EN                     | 1.5                | -     | -                  | V    |

| Low level input voltage                     | V <sub>IL</sub> 2                                                                                  |                          |                        | -                  | -     | 0.36               | V    |

| High level input voltage                    | V <sub>IH</sub> 3                                                                                  | CMOS Schmitt             | RSTB, SDA              | 1.5                | -     | -                  | V    |

| Low level input voltage                     | V <sub>IL</sub> 3                                                                                  |                          | , SCL                  | -                  | -     | 0.36               | V    |

| Low level output voltage                    | V <sub>OL</sub>                                                                                    | I <sub>OL</sub> = 4mA    | SDA                    | -                  | -     | 0.4                | V    |

| Input leakage current                       | Ι <sub>ΙL</sub>                                                                                    | $V_{I} = V_{DD}, V_{SS}$ | RSTB, EN<br>, SDA, SCL | -10                | -     | +10                | μΑ   |

| Analog characteristics at V <sub>SS</sub> = | 0V, V <sub>DD</sub> = 3V, Ta =                                                                     | 25°C                     |                        |                    |       |                    |      |

| H-bridge ON resistance Pch                  | R <sub>ONP</sub>                                                                                   | I <sub>F</sub> = 100mA   |                        | -                  | 2.5   | -                  | Ω    |

| H-bridge ON resistance Nch                  | R <sub>ONN</sub>                                                                                   | I <sub>S</sub> = 100mA   |                        | -                  | 1.5   | -                  | Ω    |

| Adjustable resonance frequency range        | Fmo                                                                                                | vs typ value             |                        | -10                | -     | +10                | %    |

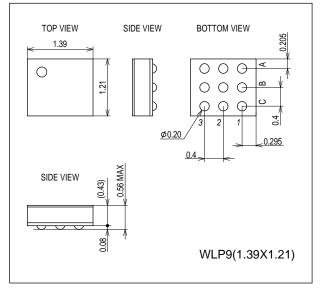

# Package Dimensions

unit : mm (typ)

3429

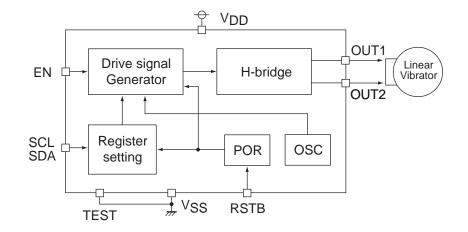

# **Block Diagram**

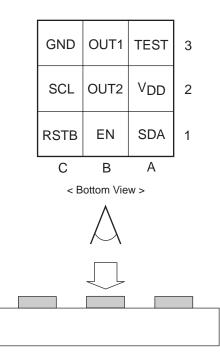

# **Pin Assignment**

Pin list

I/O (I: input, O: output, B: bi-direction, P: power supply, NC: not connected)

| No | Name            | I/O | No | Name | I/O | No | Name | I/O |

|----|-----------------|-----|----|------|-----|----|------|-----|

| 1A | SDA             | В   | 1B | EN   | I   | 1C | RSTB | I   |

| 2A | V <sub>DD</sub> | Р   | 2B | OUT2 | 0   | 2C | SCL  | I   |

| ЗA | TEST            | I   | 3B | OUT1 | 0   | 3C | GND  | Р   |

Pin layout

#### Pin description

I/O (I: input, O: output, B: bi-direction, P: power supply, NC: not connected)

| Signal name     | I/O | Function                       | Remarks                                  |

|-----------------|-----|--------------------------------|------------------------------------------|

| OUT1            | 0   | Motor drive pin                | H-bridge output                          |

| OUT2            | 0   | Motor drive pin                | H-bridge output                          |

| RSTB            | I   | Reset and standby control      | L: enable, H: disable                    |

| EN              | I   | Motor drive ON/OFF             | L: disable, H: enable                    |

| SCL             | I   | I <sup>2</sup> C I/F clock pin |                                          |

| SDA             | В   | I <sup>2</sup> C I/F data pin  | Open drain                               |

| TEST            | I   | TEST pin                       | L: disable, H: enable (normally Low fix) |

| V <sub>DD</sub> | Р   | Power supply pin               |                                          |

| VSS             | Р   | GND pin                        |                                          |

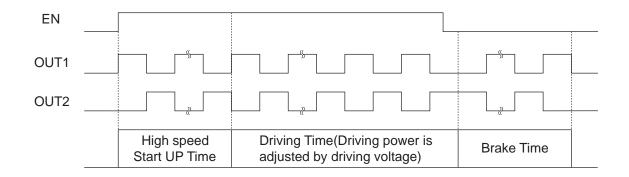

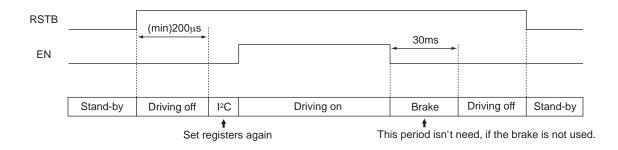

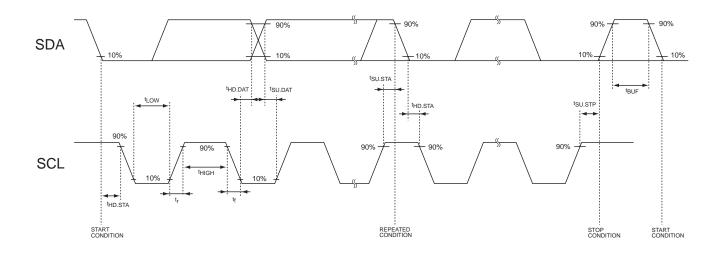

## **Timing chart**

Motor drive timing

The Motor is driven by EN pin, and the driving time is controlled by keeping EN pin "H". The High speed start UP time, driving power and Brake time can be modified by  $I^2C$  setting. The initial driving frequency must be set by  $I^2C I/F$  at the center of resonance frequency of the linear vibrators, when the initial driving frequency is inadequate. The minimum width of EN signal must be larger than the cycle of initial driving frequency setting.

#### Stand-by Control

The Stand-by mode is controlled by RSTB pin. (RSTB="L"  $\rightarrow$  Stand-by mode is ON.)

When the stand-by mode is "ON", the register value is set to initial value. So, the register must be set again after the stand-by mode is "OFF". And, the "EN" signal and I2C command must wait over 200us after "RSTB" pin is set to "H".

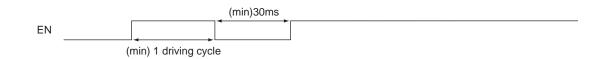

### EN Control

The width of EN=High should be set at least 1 driving cycle.

ex) 0x02 RESOFRQ=0x0A (175Hz)  $\rightarrow$  (min) 5.71ms The width of EN=Low should be kept over 30ms, if the pre-driving period is over 30ms. On the other hand, If the pre-driving period is less than 30ms, the minimum width of EN=Low is same as the pre-driving width.

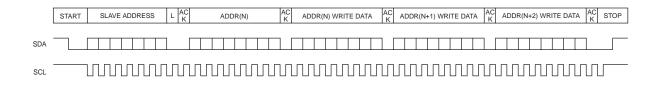

# I<sup>2</sup>C Serial Interface

Writing format (Sequential Writing is possible)

After the start condition, slave address (7bit) and "L"(Write mode) are received, the flag "ACK=L" is replied. Next, after the 8bit address is received, the flag "ACK=L" is replied. Next, after the 8bit write data is received, the flag "ACK=L" is replied. Next, when the stop condition is received, the write data can be written in the specified address. Moreover, it is possible to write data in the incremental address by the continuous input of the 8bit data confirming the flag "ACK=L" after the every 8bit write data input.

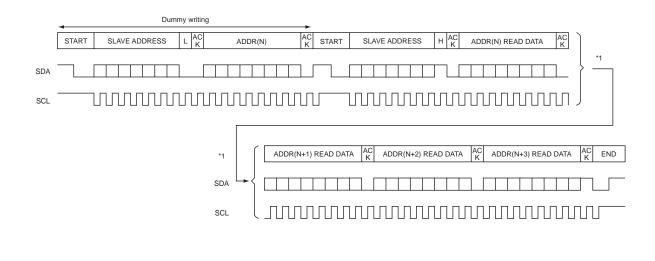

### Reading format (Sequential Reading is possible)

After the dummy writing, the start condition, slave address (7bit) and "H"(Read mode) are received, the flag "ACK=L" is replied. Next, the 8bit read data is output. After them, when the stop condition is not received, and the read condition is continued, the read data of incremental address is output one by one. The read condition is end when the end condition is received after the flag "ACK=H".

Slave Address

The Slave Address is as follows.

| Slave Address | 1001001 |

|---------------|---------|

|---------------|---------|

# LC898300XA

| Parameter                        | Symbol              | Pin        | Min | Тур | Max | Unit | comment |

|----------------------------------|---------------------|------------|-----|-----|-----|------|---------|

| SCL clock frequency              | f <sub>SCL</sub>    | SCL        | -   | -   | 400 | kHz  |         |

| START condition Hold time        | t <sub>HD;STA</sub> | SCL<br>SDA | 0.6 | -   | -   | us   |         |

| SCL clock Low width              | t <sub>LOW</sub>    | SCL        | 1.3 | -   | -   | us   |         |

| SCL clock High width             | t <sub>HIGH</sub>   | SCL        | 0.6 | -   | -   | us   |         |

| RE-START condition<br>Setup time | t <sub>su;sta</sub> | SCL<br>SDA | 0.6 | -   | -   | us   |         |

| SDA Hold time                    | t <sub>HD;DAT</sub> | SCL<br>SDA | 0   | -   | 0.9 | us   |         |

| SDA Setup time                   | t <sub>SU;DAT</sub> | SCL<br>SDA | 0.2 | -   | -   | us   | *1      |

| SDA, SCL Rise time               | tr                  | SCL<br>SDA |     | -   | 0.3 | us   | *1      |

| SDA, SCL Fall time               | tf                  | SCL<br>SDA |     | -   | 0.3 | us   | *1      |

| STOP condition Setup time        | t <sub>SU;STP</sub> | SCL<br>SDA | 0.6 | -   | -   | us   |         |

| STOP to START<br>BUS open time   | t <sub>BUF</sub>    | SCL<br>SDA | 1.3 | -   | -   | us   |         |

\*1) Design Assurance (Shipment test none)

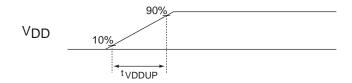

## AC Characteristic (Power On Reset) at $V_{SS} = 0V$ , $V_{DD} = 2.7$ to 3.3V, Ta = -30 to $85^{\circ}C$

|                              | -                  | ~~~ |     |     |      |         |

|------------------------------|--------------------|-----|-----|-----|------|---------|

| Parameter                    | Symbol             | Min | Тур | Max | Unit | comment |

| V <sub>DD</sub> Rise Up Time | t <sub>VDDUP</sub> | -   | -   | 100 | ms   | -       |

## LC898300XA

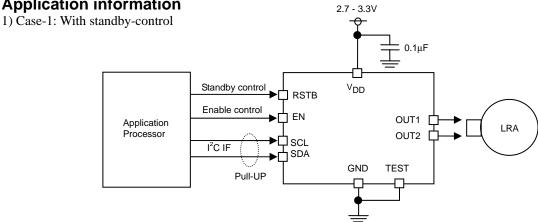

### **Application information**

Note) When SDA&SCL signal voltages are different from VDD, even if the RSTB pin is set to Low, the IO leak current flows. ex) In case of VDD=3.0V & SDA=SCL=1.8V, the current consumption is about 100µA(typ).

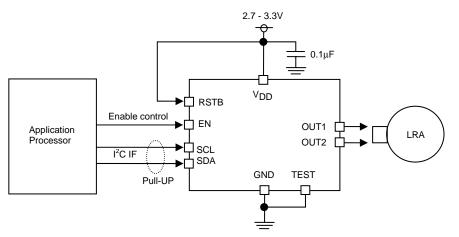

#### 2) Case-2: Without standby-control

Note) In case of  $V_{DD}=3.0V$ , the current consumption is about 1.5mA(typ).

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.