### **Contents**

| Acı | ronym | ns in This Document                                            | 5  |  |  |

|-----|-------|----------------------------------------------------------------|----|--|--|

| 1.  | Feat  | tures                                                          | 6  |  |  |

| 2.  |       | oduction                                                       |    |  |  |

| 3.  | Ove   | rview                                                          | 8  |  |  |

| 4.  | Arch  | hitecture                                                      |    |  |  |

| 4   | 4.1.  | Generic Logic Block                                            |    |  |  |

| 4   | 4.2.  | AND Array                                                      |    |  |  |

| 4   | 4.3.  | Enhanced Logic Allocator                                       | 10 |  |  |

| 4   | 4.4.  | Product Term Allocator                                         |    |  |  |

| 4   | 4.5.  | Cluster Allocator                                              |    |  |  |

| 4   | 4.6.  | Wide Steering Logic                                            |    |  |  |

| 4   | 4.7.  | Macrocell                                                      | 12 |  |  |

| 4   | 4.8.  | ·                                                              |    |  |  |

| 4   | 4.9.  | Clock Enable Multiplexer                                       | 13 |  |  |

| 4   | 4.10. | Initialization Control                                         | 13 |  |  |

| 4   | 4.11. | GLB Clock Generator                                            | 13 |  |  |

| 4   | 4.12. | Output Routing Pool (ORP)                                      | 14 |  |  |

| 4   | 4.13. | Output Routing Multiplexers                                    | 14 |  |  |

| 4   | 4.14. | ORP Bypass and Fast Output Multiplexers                        | 15 |  |  |

| 4   | 4.15. | Output Enable Routing Multiplexers                             | 15 |  |  |

| 5.  | 1/0   | Cell                                                           | 16 |  |  |

| 6.  | Glob  | bal OE Generation                                              | 17 |  |  |

| 7.  | Zerc  | o Power/Low Power and Power Management                         | 18 |  |  |

| 8.  | IEEE  | E 1149.1-Compliant Boundary Scan Testability                   | 19 |  |  |

| 9.  | 1/0   | Quick Configuration                                            | 20 |  |  |

| 10. | . IE  | EEE 1532-Compliant In-System Programming                       | 21 |  |  |

| 11. | . U   | Iser Electronic Signature                                      | 22 |  |  |

| 12. | . Se  | ecurity Bit                                                    | 23 |  |  |

| 13. | . Н   | lot Socketing                                                  | 24 |  |  |

| 14. | . D   | Pensity Migration                                              | 25 |  |  |

| 15. | . A   | EC-Q100 Tested and Qualified                                   | 26 |  |  |

| 16. | . A   | bsolute Maximum Ratings <sup>1, 2, 3</sup>                     | 27 |  |  |

| 17. | . R   | ecommended Operating Conditions                                | 28 |  |  |

| 18. | . Ei  | rase Reprogram Specifications                                  | 29 |  |  |

| 19. | . Н   | lot Socketing Characteristics <sup>1, 2, 3</sup>               | 30 |  |  |

| 20. | . /   | O Recommended Operating Conditions                             | 31 |  |  |

| 21. | . D   | C Electrical Characteristics                                   | 32 |  |  |

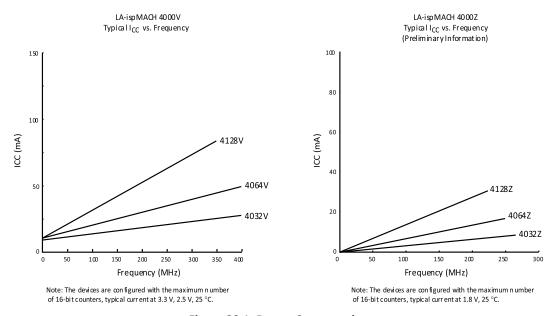

| 22. | . Sı  | upply Current, LA-ispMACH 4000V                                | 33 |  |  |

| 23. | . Sı  | upply Current, LA-ispMACH 4000Z                                | 34 |  |  |

| 24. | . /   | O DC Electrical Characteristics                                | 35 |  |  |

| 25. | . L/  | A-ispMACH 4000V/Z External Switching Characteristics           | 36 |  |  |

| 26. |       | iming Model                                                    |    |  |  |

| 27. | . L/  | A-ispMACH 4000V/Z Internal Timing Parameters                   | 38 |  |  |

| 28. | . L/  | A-ispMACH 4000V/Z Timing Adders                                | 40 |  |  |

| 29. |       | oundary Scan Waveforms and Timing Specifications               |    |  |  |

| 30. |       | ower Consumption                                               |    |  |  |

| 31. | •     |                                                                |    |  |  |

| 32. |       |                                                                |    |  |  |

| 33. |       | ignal Descriptions                                             |    |  |  |

| 34. |       | A-ispMACH 4000V ORP Reference Table                            |    |  |  |

| 35. |       | A-ispMACH 4000Z ORP Reference Table                            |    |  |  |

| 36. |       | A-ispMACH 4000V/Z Power Supply and NC Connections <sup>1</sup> |    |  |  |

|     |       |                                                                |    |  |  |

| 37.     | LA-ispMACH 4032V and 4064V Logic Signal Connections: 44-Pin TQFP      | 49 |

|---------|-----------------------------------------------------------------------|----|

| 38.     | LA-ispMACH 4032V/Z and 4064V/Z Logic Signal Connections: 48-Pin TQFP  | 51 |

| 39.     | LA-ispMACH 4064V/Z and 4128V/Z Logic Signal Connections: 100-Pin TQFP | 53 |

| 40.     | LA-ispMACH 4128V Signal Connections: 128-Pin TQFP                     | 56 |

| 41.     | LA-ispMACH 4128V Signal Connections: 144-Pin TQFP                     | 59 |

| 42.     | Ordering Information                                                  |    |

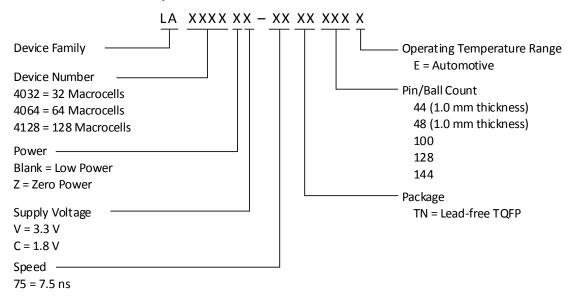

| 42.3    | 1. Part Number Description                                            |    |

| 42.2    | 2. Ordering Part Numbers                                              | 63 |

|         | notive Disclaimer                                                     |    |

| Supple  | emental Information                                                   | 65 |

| For     | Further Information                                                   | 65 |

| Revisio | on History                                                            | 66 |

# Figures

| Figure 3.1. Functional Block Diagram                                              | 8  |

|-----------------------------------------------------------------------------------|----|

| Figure 4.1. Generic Logic Block                                                   | 9  |

| Figure 4.2. AND Array                                                             | 10 |

| Figure 4.3. Macrocell Slice                                                       | 10 |

| Figure 4.4. Macrocell                                                             |    |

| Figure 4.5. GLB Clock Generator                                                   | 13 |

| Figure 4.6. ORP Slice                                                             |    |

| Figure 5.1. I/O Cell                                                              |    |

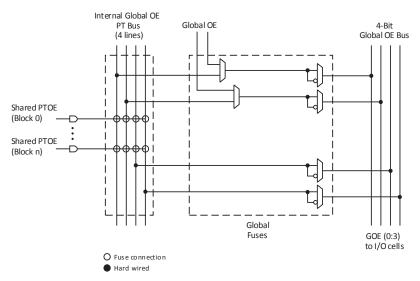

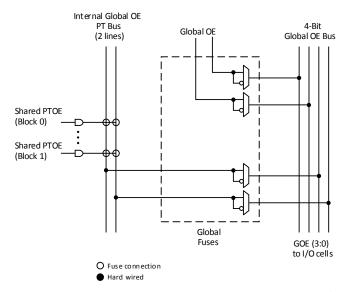

| Figure 6.1. Global OE Generation for All Devices Except LA-ispMACH 4032V/Z        |    |

| Figure 6.2. Global OE Generation for LA-ispMACH 4032V/Z                           |    |

| Figure 24.1. I/O DC Electrical Characteristics                                    |    |

| Figure 26.1. LA-ispMACH 4000V/Z Automotive Timing Model                           |    |

| Figure 30.1. Power Consumption                                                    |    |

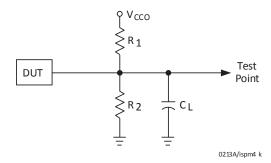

| Figure 32.1. Output Test Load, LVTTL and LVCMOS Standards                         | 44 |

| Tables                                                                            |    |

| Table 2.1. LA-ispMACH 4000V Automotive Family Selection Guide                     | 7  |

| Table 2.2. LA-ispMACH 4000Z Automotive Family Selection Guide                     |    |

| Table 4.1. Individual PT Steering                                                 | 11 |

| Table 4.2. Available Clusters for Each Macrocell                                  | 11 |

| Table 4.3. Product Term Expansion Capability                                      | 12 |

| Table 4.4. ORP Combinations for I/O Blocks with 8 I/Os                            |    |

| Table 4.5. ORP Combinations for I/O Blocks with 16 I/Os                           | 15 |

| Table 4.6. ORP Combinations for I/O Blocks with 12 I/Os                           | 15 |

| Table 16.1. Absolute Maximum Ratings                                              | 27 |

| Table 17.1. Recommended Operating Conditions                                      |    |

| Table 18.1. Erase Reprogram Specifications                                        |    |

| Table 19.1. Hot Socketing Specifications                                          |    |

| Table 20.1. sysI/O Recommended Operating Conditions                               |    |

| Table 21.1. DC Electrical Characteristics                                         |    |

| Table 22.1. Supply Current, LA-ispMACH 4000V                                      |    |

| Table 23.1. Supply Current, LA-ispMACH 4000Z                                      |    |

| Table 24.1. I/O DC Electrical Characteristics                                     |    |

| Table 25.1. LA-ispMACH 4000V/Z External Switching Characteristics                 |    |

| Table 27.1. LA-ispMACH 4000V/Z Internal Timing Parameters                         |    |

| Table 28.1. LA-ispMACH 4000V/Z Timing Adders*                                     |    |

| Table 29.1. Boundary Scan Waveforms and Timing Specifications                     |    |

| Table 31.1. Power Estimation Coefficients                                         |    |

| Table 32.1. Test Fixture Required Components                                      |    |

| Table 33.1. Signal Descriptions                                                   |    |

| Table 34.1. LA-ispMACH 4000V ORP Reference Table                                  |    |

| Table 35.1. LA-ispMACH 4000V ORP Reference Table                                  |    |

| Table 36.1. LA-ispMACH 4000V ORP Reference Table                                  |    |

| Table 37.1. LA-ispMACH 4032V and 4064V Logic Signal Connections: 44-Pin TQFP      |    |

| Table 38.1. LA-ispMACH 4032V/Z and 4064V/Z Logic Signal Connections: 48-Pin TQFP  |    |

| Table 39.1. LA-ispMACH 4064V/Z and 4128V/Z Logic Signal Connections: 100-Pin TQFP |    |

| Table 40.1. LA-ispMACH 4128V Signal Connections: 100-Pin TQFP                     |    |

| Table 41.1. LA-ispMACH 4128V Signal Connections: 144-Pin TQFP                     |    |

| Table 74.1. Utuettiik iiituttiatiut                                               |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                    |

|---------|-------------------------------|

| AEC     | Automotive Electronic Council |

| GLB     | Generic Logic Blocks          |

| GRP     | Global Routing Pool           |

| IOB     | I/O Blocks                    |

| ISP     | In-System Programming         |

| ORP     | Output Routing Pool           |

| TQFP    | Thin Quad Flat Pack           |

| UES     | User Electronic Signature     |

#### 1. Features

- High Performance

- f<sub>MAX</sub> = 168 MHz maximum operating frequency

- t<sub>PD</sub> = 7.5 ns propagation delay

- Up to four global clock pins with programmable clock polarity control

- Up to 80 PTs per output

- Ease of Design

- Enhanced macrocells with individual clock, reset, preset and clock enable controls

- Up to four global OE controls

- Individual local OE control per I/O pin

- Excellent First-Time-Fit<sup>™</sup> and refit

- Fast path, SpeedLocking<sup>™</sup> Path, and wide-PT path

- Wide input gating (36 input logic blocks) for fast counters, state machines and address decoders

- Zero Power (LA-ispMACH 4000Z)

- Typical static current 10 μA (4032Z)

- 1.8 V core low dynamic power

- LA-ispMACH 4000Z operational down to 1.6 V

- AEC-Q100 Tested and Qualified

- Automotive: -40 to 125 °C ambient (T<sub>A</sub>)

- Easy System Integration

- Superior solution for power sensitive consumer applications

- Operation with 3.3 V, 2.5 V or 1.8 V LVCMOS I/O

- Operation with 3.3 V (4000V) or 1.8 V (4000Z) supplies

- 5 V tolerant I/O for LVCMOS 3.3, LVTTL, and PCI interfaces

- Hot-socketing

- Open-drain capability

- Input pull-up, pull-down or bus-keeper

- Programmable output slew rate

- 3.3 V PCI compatible

- IEEE 1149.1 boundary scan testable

- 3.3 V/2.5 V/1.8 V In-System Programmable (ISP™) using IEEE 1532 compliant interface

- I/O pins with fast setup path

- Lead-free (RoHS) package

### 2. Introduction

The high performance LA-ispMACH 4000V/Z automotive family from Lattice offers a SuperFAST CPLD solution that is tested and qualified to the AEC-Q100 standard. The family is a blend of Lattice's two most popular architectures: the ispLSI® 2000 and ispMACH 4A. Retaining the best of both families, the LA-ispMACH 4000V/Z architecture focuses on significant innovations to combine the highest performance with low power in a flexible CPLD family.

The LA-ispMACH 4000V/Z automotive family combines high speed and low power with the flexibility needed for ease of design. With its robust Global Routing Pool and Output Routing Pool, this family delivers excellent First-Time-Fit, timing predictability, routing, pinout retention and density migration.

Table 2.1. LA-ispMACH 4000V Automotive Family Selection Guide

|                        | LA-ispMACH 4032V                               | LA-ispMACH 4064V                                                         | LA-ispMACH 4128V                                                           |

|------------------------|------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Macrocells             | 32                                             | 64                                                                       | 128                                                                        |

| I/O + Dedicated Inputs | 30+2/32+4                                      | 30+2/32+4/64+10                                                          | 64+10/92+4/96+4                                                            |

| t <sub>PD</sub> (ns)   | 7.5                                            | 7.5                                                                      | 7.5                                                                        |

| t <sub>S</sub> (ns)    | 4.5                                            | 4.5                                                                      | 4.5                                                                        |

| t <sub>CO</sub> (ns)   | 4.5                                            | 4.5                                                                      | 4.5                                                                        |

| f <sub>MAX</sub> (MHz) | 168                                            | 168                                                                      | 168                                                                        |

| Supply Voltage (V)     | 3.3 V                                          | 3.3 V                                                                    | 3.3 V                                                                      |

| Pins/Package           | 44-pin Lead-Free TQFP<br>48-pin Lead-Free TQFP | 44-pin Lead-Free TQFP<br>48-pin Lead-Free TQFP<br>100-pin Lead-Free TQFP | 100-pin Lead-Free TQFP<br>128-pin Lead-Free TQFP<br>144-pin Lead-Free TQFP |

Table 2.2. LA-ispMACH 4000Z Automotive Family Selection Guide

| •                      | •                     |                        |                        |

|------------------------|-----------------------|------------------------|------------------------|

|                        | LA-ispMACH 4032Z      | LA-ispMACH 4064Z       | LA-ispMACH 4128Z       |

| Macrocells             | 32                    | 64                     | 128                    |

| I/O + Dedicated Inputs | 32+4                  | 32+4/64+10             | 64+10                  |

| t <sub>PD</sub> (ns)   | 7.5                   | 7.5                    | 7.5                    |

| t <sub>S</sub> (ns)    | 4.5                   | 4.5                    | 4.5                    |

| t <sub>CO</sub> (ns)   | 4.5                   | 4.5                    | 4.5                    |

| f <sub>MAX</sub> (MHz) | 168                   | 168                    | 168                    |

| Supply Voltage (V)     | 1.8 V                 | 1.8 V                  | 1.8 V                  |

| Pins/Package           | 48-pin Lead-Free TQFP | 48-pin Lead-Free TQFP  |                        |

|                        |                       | 100-pin Lead-Free TQFP | 100-pin Lead-Free TQFP |

The LA-ispMACH 4000V/Z automotive family offers densities ranging from 32 to 128 macrocells. There are multiple density-I/O combinations in Thin Quad Flat Pack (TQFP) packages ranging from 44 to 144 pins. Table 2.1 and Table 2.2 show the macrocell, package and I/O options, along with other key parameters.

The LA-ispMACH 4000V/Z automotive family has enhanced system integration capabilities. It supports 3.3 V (4000V and 1.8 V (4000Z) supply voltages and 3.3 V, 2.5 V and 1.8 V interface voltages. Additionally, inputs can be safely driven up to 5.5 V when an I/O bank is configured for 3.3 V operation, making this family 5 V tolerant. The LA-ispMACH 4000V/Z also offers enhanced I/O features such as slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. The LA-ispMACH 4000V/Z automotive family is in-system programmable through the IEEE Standard 1532 interface. IEEE Standard 1149.1 boundary scan testing capability also allows product testing on automated test equipment. The 1532 interface signals TCK, TMS, TDI and TDO are referenced to VCC (logic core).

### 3. Overview

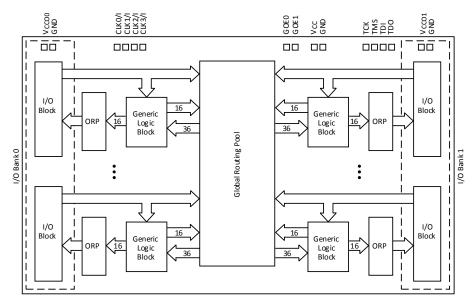

The LA-ispMACH 4000V/Z automotive devices consist of multiple 36-input, 16-macrocell Generic Logic Blocks (GLBs) interconnected by a Global Routing Pool (GRP). Output Routing Pools (ORPs) connect the GLBs to the I/O Blocks (IOBs), which contain multiple I/O cells. This architecture is shown in Figure 3.1.

Figure 3.1. Functional Block Diagram

The I/Os in the LA-ispMACH 4000V/Z automotive devices are split into two banks. Each bank has a separate I/O power supply. Inputs can support a variety of standards independent of the chip or bank power supply. Outputs support the standards compatible with the power supply provided to the bank. Support for a variety of standards helps designers implement designs in mixed voltage environments. In addition, 5 V tolerant inputs are specified within an I/O bank that is connected to Vcco of 3.0 V to 3.6 V for LVCMOS 3.3, LVTTL and PCI interfaces.

### **Architecture**

There are a total of two GLBs in the LA-ispMACH 4032V/Z, increasing to 8 GLBs in the LA-ispMACH 4128V/Z. Each GLB has 36 inputs. All GLB inputs come from the GRP and all outputs from the GLB are brought back into the GRP to be connected to the inputs of any other GLB on the device. Even if feedback signals return to the same GLB, they still must go through the GRP. This mechanism ensures that GLBs communicate with each other with consistent and predictable delays. The outputs from the GLB are also sent to the ORP. The ORP then sends them to the associated I/O cells in the I/O block.

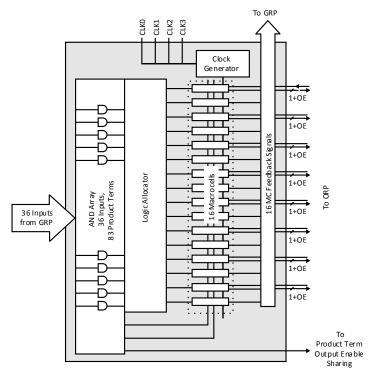

### 4.1. Generic Logic Block

The LA-ispMACH 4000V/Z Automotive GLB consists of a programmable AND array, logic allocator, 16 macrocells and a GLB clock generator. Macrocells are decoupled from the product terms through the logic allocator and the I/O pins are decoupled from macrocells through the ORP. Figure 4.1 illustrates the GLB.

Figure 4.1. Generic Logic Block

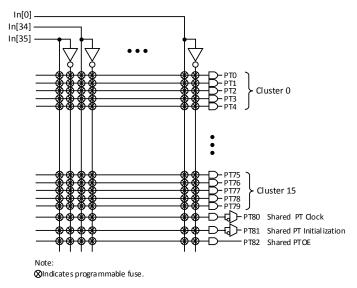

### 4.2. AND Array

The programmable AND Array consists of 36 inputs and 83 output product terms. The 36 inputs from the GRP are used to form 72 lines in the AND Array (true and complement of the inputs). Each line in the array can be connected to any of the 83 output product terms via a wired-AND. Each of the 80 logic product terms feed the logic allocator with the remaining three control product terms feeding the Shared PT Clock, Shared PT Initialization and Shared PT OE. The Shared PT Clock and Shared PT Initialization signals can optionally be inverted before being fed to the macrocells.

Every set of five product terms from the 80 logic product terms forms a product term cluster starting with PTO. There is one product term cluster for every macrocell in the GLB. Figure 4.2 is a graphical representation of the AND Array.

Downloaded from Arrow.com.

Figure 4.2. AND Array

### 4.3. Enhanced Logic Allocator

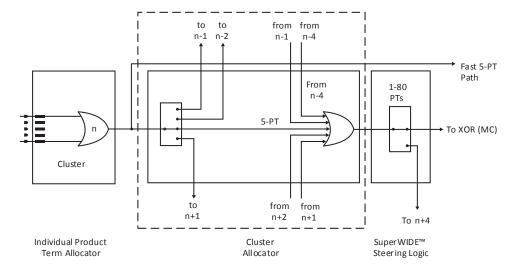

Within the logic allocator, product terms are allocated to macrocells in product term clusters. Each product term cluster is associated with a macrocell. The cluster size for the LA-ispMACH 4000V/Z automotive family is 4+1 (total 5) product terms. The software automatically considers the availability and distribution of product term clusters as it fits the functions within a GLB. The logic allocator is designed to provide three speed paths: 5-PT fast bypass path, 20-PT Speed Locking path and an up to 80-PT path. The availability of these three paths lets designers trade timing variability for increased performance.

The enhanced Logic Allocator of the LA-ispMACH 4000V/Z automotive family consists of the following blocks:

- Product Term Allocator

- Cluster Allocator

- Wide Steering Logic

Figure 4.3 shows a macrocell slice of the Logic Allocator. There are 16 such slices in the GLB.

Figure 4.3. Macrocell Slice

#### 4.4. Product Term Allocator

The product term allocator assigns product terms from a cluster to either logic or control applications as required by the design being implemented. Product terms that are used as logic are steered into a 5-input OR gate associated with the cluster. Product terms that used for control are steered either to the macrocell or I/O cell associated with the cluster. Table 4.1 shows the available functions for each of the five product terms in the cluster. The OR gate output connects to the associated I/O cell, providing a fast path for narrow combinatorial functions, and to the logic allocator.

**Table 4.1. Individual PT Steering**

| Product Term                              | Logic                                                                   | Control                     |

|-------------------------------------------|-------------------------------------------------------------------------|-----------------------------|

| PT <i>n</i> Logic PT Single PT for XOR/OR |                                                                         | Single PT for XOR/OR        |

| PTn+1                                     | Logic PT                                                                | Individual Clock (PT Clock) |

| PTn+2                                     | PTn+2 Logic PT Individual Initialization or Individual Clock Enable (PT |                             |

| PTn+3                                     | PTn+3 Logic PT Individual Initialization (PT Initialization)            |                             |

| PTn+4 Logic PT Individual OE (PTOE)       |                                                                         | Individual OE (PTOE)        |

#### 4.5. Cluster Allocator

The cluster allocator allows clusters to be steered to neighboring macrocells, thus allowing the creation of functions with more product terms. Table 4.2 shows which clusters can be steered to which macrocells. Used in this manner, the cluster allocator can be used to form functions of up to 20 product terms. Additionally, the cluster allocator accepts inputs from the wide steering logic. Using these inputs, functions up to 80 product terms can be created.

Table 4.2. Available Clusters for Each Macrocell

| Macrocell |            | Available  | e Clusters |     |

|-----------|------------|------------|------------|-----|

| M0        | _          | CO         | C1         | C2  |

| M1        | CO         | C1         | C2         | C3  |

| M2        | C1         | C2         | C3         | C4  |

| M3        | C2         | C3         | C4         | C5  |

| M4        | C3         | C4         | <b>C</b> 5 | C6  |

| M5        | C4         | C5         | C6         | C7  |

| M6        | C5         | C6         | C7         | C8  |

| M7        | C6         | <b>C</b> 7 | C8         | C9  |

| M8        | C7         | C8         | <b>C</b> 9 | C10 |

| M9        | C8         | C9         | C10        | C11 |

| M10       | <b>C</b> 9 | C10        | C11        | C12 |

| M11       | C10        | C11        | C12        | C13 |

| M12       | C11        | C12        | C13        | C14 |

| M13       | C12        | C13        | C14        | C15 |

| M14       | C13        | C14        | C15        | _   |

| M15       | C14        | C15        | _          | _   |

#### 4.6. Wide Steering Logic

The wide steering logic allows the output of the cluster allocator n to be connected to the input of the cluster allocator n+4. Thus, cluster chains can be formed with up to 80 product terms, supporting wide product term functions and allowing performance to be increased through a single GLB implementation. Table 4.3 shows the product term chains.

**Table 4.3. Product Term Expansion Capability**

| Expansion Chains | Macrocells Associated with Expansion Chain (with Wrap Around)      | Max PT/Macrocell |

|------------------|--------------------------------------------------------------------|------------------|

| Chain-0          | $M0 \rightarrow M4 \rightarrow M8 \rightarrow M12 \rightarrow M0$  | 75               |

| Chain-1          | $M1 \rightarrow M5 \rightarrow M9 \rightarrow M13 \rightarrow M1$  | 80               |

| Chain-2          | $M2 \rightarrow M6 \rightarrow M10 \rightarrow M14 \rightarrow M2$ | 75               |

| Chain-3          | $M3 \rightarrow M7 \rightarrow M11 \rightarrow M15 \rightarrow M3$ | 70               |

Every time the super cluster allocator is used, there is an incremental delay of  $t_{EXP}$ . When the super cluster allocator is used, all destinations other than the one being steered to, are given the value of ground (i.e., if the super cluster is steered to M (n+4), then M (n) is ground).

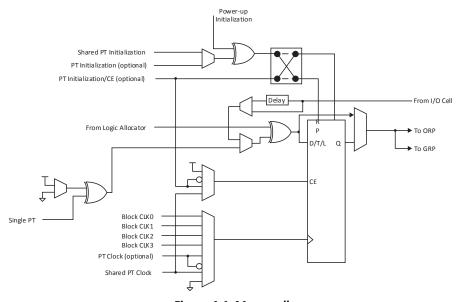

#### 4.7. Macrocell

The 16 macrocells in the GLB are driven by the 16 outputs from the logic allocator. Each macrocell contains a programmable XOR gate, a programmable register/latch, along with routing for the logic and control functions. Figure 4.4 shows a graphical representation of the macrocell. The macrocells feed the ORP and GRP. A direct input from the I/O cell allows designers to use the macrocell to construct high-speed input registers. A programmable delay in this path allows designers to choose between the fastest possible set-up time and zero hold time.

Figure 4.4. Macrocell

### 4.8. Enhanced Clock Multiplexer

The clock input to the flip-flop can select any of the four block clocks along with the shared PT clock, and true and complement forms of the optional individual term clock. An 8:1 multiplexer structure is used to select the clock. The eight sources for the clock multiplexer are as follows:

- Block CLK0

- Block CLK1

- Block CLK2

- Block CLK3

- PT Clock

- PT Clock Inverted

- Shared PT Clock

- Ground

### 4.9. Clock Enable Multiplexer

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the following four sources:

- PT Initialization/CE

- PT Initialization/CE Inverted

- Shared PT Clock

- Logic High

#### 4.10. Initialization Control

The LA-ispMACH 4000V/Z automotive family architecture accommodates both block-level and macrocell-level set and reset capability. There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell level, two product terms can be "stolen" from the cluster associated with a macrocell to be used for set/reset functionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the block-level initialization, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the block-level initialization or is not configured for set/reset, then that macrocell will RESET on power- up. To guarantee initialization values, the Vcc rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

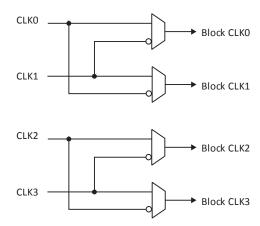

#### 4.11. GLB Clock Generator

Each LA-ispMACH 4000V/Z automotive device has up to four clock pins that are also routed to the GRP to be used as inputs. These pins drive a clock generator in each GLB, as shown in Figure 4.5. The clock generator provides four clock signals that can be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true and complement edges of the global clock signals.

Figure 4.5. GLB Clock Generator

### 4.12. Output Routing Pool (ORP)

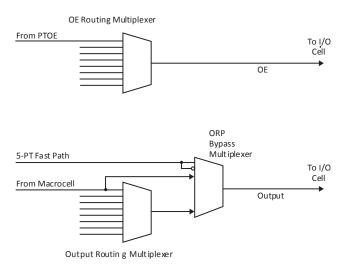

The Output Routing Pool allows macrocell outputs to be connected to any of several I/O cells within an I/O block. This provides greater flexibility in determining the pinout and allows design changes to occur without affecting the pinout. The output routing pool also provides a parallel capability for routing macrocell-level OE product terms. This allows the OE product term to follow the macrocell output as it is switched between I/O cells. Additionally, the output routing pool allows the macrocell output or true and complement forms of the 5-PT bypass signal to bypass the output routing multiplexers and feed the I/O cell directly. The enhanced ORP of the LA-ispMACH 4000V/Z family consists of the following elements:

- Output Routing Multiplexers

- OE Routing Multiplexers

- Output Routing Pool Bypass Multiplexers

Figure 4.6 shows the structure of the ORP from the I/O cell perspective. This is referred to as an ORP slice. Each ORP has as many ORP slices as there are I/O cells in the corresponding I/O block.

Figure 4.6. ORP Slice

### 4.13. Output Routing Multiplexers

The details of connections between the macrocells and the I/O cells vary across devices and within a device dependent on the maximum number of I/Os available. Table 4.4 to Table 4.6 provide the connection details.

Table 4.4. ORP Combinations for I/O Blocks with 8 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| 1/0 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M2, M3, M4, M5, M6, M7, M8, M9       |

| I/O 2    | M4, M5, M6, M7, M8, M9, M10, M11     |

| 1/0 3    | M6, M7, M8, M9, M10, M11, M12, M13   |

| I/O 4    | M8, M9, M10, M11, M12, M13, M14, M15 |

| I/O 5    | M10, M11, M12, M13, M14, M15, M0, M1 |

| 1/0 6    | M12, M13, M14, M15, M0, M1, M2, M3   |

| 1/0 7    | M14, M15, M0, M1, M2, M3, M4, M5     |

Table 4.5. ORP Combinations for I/O Blocks with 16 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| 1/0 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M1, M2, M3, M4, M5, M6, M7, M8       |

| 1/0 2    | M2, M3, M4, M5, M6, M7, M8, M9       |

| 1/0 3    | M3, M4, M5, M6, M7, M8, M9, M10      |

| 1/0 4    | M4, M5, M6, M7, M8, M9, M10, M11     |

| 1/0 5    | M5, M6, M7, M8, M9, M10, M11, M12    |

| 1/0 6    | M6, M7, M8, M9, M10, M11, M12, M13   |

| 1/0 7    | M7, M8, M9, M10, M11, M12, M13, M14  |

| 1/0 8    | M8, M9, M10, M11, M12, M13, M14, M15 |

| 1/0 9    | M9, M10, M11, M12, M13, M14, M15, M0 |

| I/O 10   | M10, M11, M12, M13, M14, M15, M0, M1 |

| I/O 11   | M11, M12, M13, M14, M15, M0, M1, M2  |

| I/O 12   | M12, M13, M14, M15, M0, M1, M2, M3   |

| I/O 13   | M13, M14, M15, M0, M1, M2, M3, M4    |

| I/O 14   | M14, M15, M0, M1, M2, M3, M4, M5     |

| I/O 15   | M15, M0, M1, M2, M3, M4, M5, M6      |

Table 4.6. ORP Combinations for I/O Blocks with 12 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| 1/0 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M1, M2, M3, M4, M5, M6, M7, M8       |

| 1/0 2    | M2, M3, M4, M5, M6, M7, M8, M9       |

| 1/0 3    | M4, M5, M6, M7, M8, M9, M10, M11     |

| I/O 4    | M5, M6, M7, M8, M9, M10, M11, M12    |

| I/O 5    | M6, M7, M8, M9, M10, M11, M12, M13   |

| 1/0 6    | M8, M9, M10, M11, M12, M13, M14, M15 |

| 1/0 7    | M9, M10, M11, M12, M13, M14, M15, M0 |

| I/O 8    | M10, M11, M12, M13, M14, M15, M0, M1 |

| 1/0 9    | M12, M13, M14, M15, M0, M1, M2, M3   |

| I/O 10   | M13, M14, M15, M0, M1, M2, M3, M4    |

| I/O 11   | M14, M15, M0, M1, M2, M3, M4, M5     |

### 4.14. ORP Bypass and Fast Output Multiplexers

The ORP bypass and fast-path output multiplexer is a 4:1 multiplexer and allows the 5-PT fast path to bypass the ORP and be connected directly to the pin with either the regular output or the inverted output. This multiplexer also allows the register output to bypass the ORP to achieve faster  $t_{co}$ .

### 4.15. Output Enable Routing Multiplexers

The OE Routing Pool provides the corresponding local output enable (OE) product term to the I/O cell.

### 5. I/O Cell

The I/O cell contains the following programmable elements: output buffer, input buffer, OE multiplexer and bus maintenance circuitry. Figure 5.1 details the I/O cell.

Figure 5.1. I/O Cell

Each output supports a variety of output standards dependent on the  $V_{CCO}$  supplied to its I/O bank. Outputs can also be configured for open drain operation. Each input can be programmed to support a variety of standards, independent of the  $V_{CCO}$  supplied to its I/O bank. The I/O standards supported are:

- LVTTL

- LVCMOS 1.8

- LVCMOS 3.3

- 3.3 V PCI Compatible

- LVCMOS 2.5

All of the I/Os and dedicated inputs have the capability to provide a bus-keeper latch, Pull-up Resistor or Pull-down Resistor. A fourth option is to provide none of these. The selection is done on a global basis. The default in both hardware and software is such that when the device is erased or if the user does not specify, the input structure is configured to be a Pull-up Resistor.

Each LA-ispMACH 4000V/Z automotive device I/O has an individually programmable output slew rate control bit. Each output can be individually configured for fast slew or slow slew. The typical edge rate difference between fast and slow slew setting is 20%. For high-speed designs with long, unterminated traces, the slow-slew rate will introduce fewer reflections, less noise and keep ground bounce to a minimum. For designs with short traces or well terminated lines, the fast slew rate can be used to achieve the highest speed.

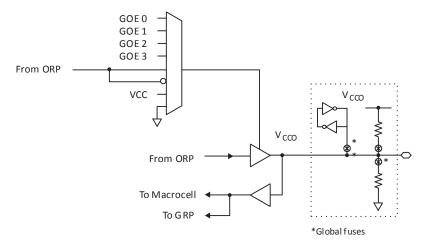

### 6. Global OE Generation

Most LA-ispMACH 4000V/Z automotive family devices have a 4-bit wide Global OE Bus, except the LA-ispMACH 4032V and LA-ispMACH4032Z devices that have a 2-bit wide Global OE Bus. This bus is derived from a 4-bit internal global OE PT bus and two dual purpose I/O or GOE pins. Each signal that drives the bus can optionally be inverted.

Each GLB has a block-level OE PT that connects to all bits of the Global OE PT bus with four fuses. Hence, for a 128-macrocell device (with 16 blocks), each line of the bus is driven from 8 OE product terms. Figure 6.1 and Figure 6.2 show a graphical representation of the global OE generation.

Figure 6.1. Global OE Generation for All Devices Except LA-ispMACH 4032V/Z

Figure 6.2. Global OE Generation for LA-ispMACH 4032V/Z

### 7. Zero Power/Low Power and Power Management

The LA-ispMACH 4000V/Z automotive family is designed with high speed low power design techniques to offer both high speed and low power. With an advanced E2 low power cell and nonsense-amplifier design approach (full CMOS logic approach), the LA-ispMACH 4000V/Z automotive family offers SuperFAST pin-to-pin speeds, while simultaneously delivering low standby power without needing any "turbo bits" or other power management schemes associated with a traditional sense-amplifier approach.

The zero power LA-ispMACH 4000Z is based on the 1.8 V ispMACH 4000C family. With innovative circuit design changes, the LA-ispMACH 4000Z family is able to achieve the industry's "lowest static power".

### 8. IEEE 1149.1-Compliant Boundary Scan Testability

All LA-ispMACH 4000V/Z automotive devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for more board-level testing. The test access port operates with an LVCMOS interface that corresponds to the power supply voltage.

# 9. I/O Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The LA-ispMACH 4000V/Z automotive family of devices allows this by offering the user the ability to quickly configure the physical nature of the I/O cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM™ System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

### 10. IEEE 1532-Compliant In-System Programming

Programming devices in-system provides a number of significant benefits including: rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. The LA-ispMACH 4000V/Z automotive devices provide In-System Programming (ISP™) capability through the Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains complaint to the IEEE 1149.1 standard. By using IEEE 1149.1 as the communication interface through which ISP is achieved, users get the benefit of a standard, well-defined interface. All LA-ispMACH 4000V/Z automotive devices are also compliant with the IEEE 1532 standard.

The LA-ispMACH 4000V/Z automotive devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of LA-ispMACH 4000V/Z automotive devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program LA- ispMACH 4000V/Z automotive devices during the testing of a circuit board.

# 11. User Electronic Signature

The User Electronic Signature (UES) allows the designer to include identification bits or serial numbers inside the device, stored in E2CMOS memory. The LA-ispMACH 4000V/Z automotive device contains 32 UES bits that can be configured by the user to store unique data such as ID codes, revision numbers or inventory control codes.

# 12. Security Bit

A programmable security bit is provided on the LA-ispMACH 4000V/Z automotive devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit. The bit can only be reset by erasing the entire device.

# 13. Hot Socketing

The LA-ispMACH 4000V/Z automotive devices are well-suited for applications that require hot socketing capability. Hot socketing a device requires that the device, during power-up and down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of I/O pin loading be minimal on active signals. The LA-ispMACH 4000V/Z automotive devices provide this capability for input voltages in the range 0 V to 3.0 V.

# 14. Density Migration

The LA-ispMACH 4000V/Z automotive family has been designed to ensure that different density devices in the same package have the same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

### 15. AEC-Q100 Tested and Qualified

The Automotive Electronics Council (AEC) consists of two committees: the Quality Systems Committee and the Component Technical Committee. These committees are composed of representatives from sustaining and other associate members. The AEC Component Technical Committee is the standardization body for establishing standards for reliable, high quality electronic components. In particular, the AEC-Q100 specification "Stress Test for Qualification for Integrated Circuits" defines qualification and re-qualification requirements for electronic components. Components meeting these specifications are suitable for use in the harsh automotive environment without additional component-level qualification testing. Lattice's LA-ispMACH 4000V/Z and LA-MachXO devices completed and passed the requirements of the AEC-Q100 specification.

# 16. Absolute Maximum Ratings<sup>1, 2, 3</sup>

#### **Table 16.1. Absolute Maximum Ratings**

| Parameter                                                 | Min              | Max              |

|-----------------------------------------------------------|------------------|------------------|

| Supply Voltage (V <sub>CC</sub> )                         | –0.5 V to 5.5 V  | −0.5 V to 2.5V   |

| Output Supply Voltage (V <sub>CCO</sub> )                 | –0.5 V to 4.5 V  | –0.5 V to 4.5 V  |

| Input or I/O Tristate Voltage Applied <sup>4, 5</sup>     | –0.5 V to 5.5 V  | –0.5 V to 5.5 V  |

| Storage Temperature                                       | −65 °C to 150 °C | −65 °C to 150 °C |

| Junction Temperature (T <sub>j</sub> ) with Power Applied | −55 °C to 150 °C | −55 °C to 150 °C |

#### Notes:

- Stress above those listed under the Absolute Maximum Ratings may cause permanent damage to the device. Functional

operation of the device at these or any other conditions above those indicated in the operational sections of this specification is

not implied.

- 2. Compliance with the Lattice Semiconductor Thermal Management document is required.

- 3. All voltages referenced to GND.

- 1. Undershoot of –2 V and overshoot of (VIH (MAX) + 2 V), up to a total pin voltage of 6.0 V, is permitted for a duration of < 20 ns.

- 5. Maximum of 64 I/Os per device with VIN > 3.6 V is allowed.

# 17. Recommended Operating Conditions

**Table 17.1. Recommended Operating Conditions**

| Symbol          | Parameter                                     | Min  | Max | Unit |

|-----------------|-----------------------------------------------|------|-----|------|

| V <sub>CC</sub> | LA-ispMACH 4000V Supply Voltage               | 3.0  | 3.6 | V    |

|                 | LA-ispMACH 4000Z Supply Voltage               | 1.7  | 1.9 | V    |

|                 | LA-ispMACH 4000Z, Extended Functional Voltage | 1.6* | 1.9 | V    |

| t <sub>A</sub>  | Ambient Temperature (Automotive)              | -40  | 125 | °C   |

<sup>\*</sup>Note: Devices operating at 1.6 V can expect performance degradation up to 35%.

# **18. Erase Reprogram Specifications**

### **Table 18.1. Erase Reprogram Specifications**

| Parameter             | Min   | Max | Unit   |

|-----------------------|-------|-----|--------|

| Erase/Reprogram Cycle | 1,000 | 1   | Cycles |

**Note**: Valid over commercial temperature range.

# 19. Hot Socketing Characteristics<sup>1, 2, 3</sup>

#### **Table 19.1. Hot Socketing Specifications**

| Symbol | Parameter                    | Condition                    | Min | Тур | Max  | Unit |

|--------|------------------------------|------------------------------|-----|-----|------|------|

|        | Input or I/O Leakage Current | 0 ≤ VIN ≤ 3.0 V, Tj = 105 °C | 1   | ±30 | ±150 | μΑ   |

| IDK    | Input of 170 Leakage Current | 0 ≤ VIN ≤ 3.0 V, Tj = 130 °C | -   | ±30 | ±200 | μΑ   |

- Insensitive to sequence of  $V_{CC}$  or  $V_{CCO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCO}$ , provided ( $V_{IN}$   $V_{CCO}$ )  $\leq 3.6 \text{ V}$ .

- $0 < V_{\text{CC}} < V_{\text{CC}}$  (MAX),  $0 < V_{\text{CCO}} < V_{\text{CCO}}$  (MAX). 2.

- $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ . Device defaults to pull-up until fuse circuitry is active.

# 20. I/O Recommended Operating Conditions

Table 20.1. sysI/O Recommended Operating Conditions

| Standard                         | V <sub>CCIO</sub> (V) <sup>1</sup> |      |  |  |  |

|----------------------------------|------------------------------------|------|--|--|--|

| Standard                         | Min                                | Max  |  |  |  |

| LVTTL                            | 3.0                                | 3.6  |  |  |  |

| LVCMOS 3.3                       | 3.0                                | 3.6  |  |  |  |

| Extended LVCMOS 3.3 <sup>2</sup> | 2.7                                | 3.6  |  |  |  |

| LVCMOS 2.5                       | 2.3                                | 2.7  |  |  |  |

| LVCMOS 1.8                       | 1.65                               | 1.95 |  |  |  |

| PCI 3.3                          | 3.0                                | 3.6  |  |  |  |

- 1. Typical values for  $V_{\text{CCO}}$  are the average of the min. and max. values.

- 2. LA-ispMACH 4000Z only.

### 21. DC Electrical Characteristics

**Over Recommended Operating Conditions**

**Table 21.1. DC Electrical Characteristics**

| Symbol                                            | Parameter                                               | Condition                                                                                                                                           | Min       | Тур | Max         | Unit |

|---------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input Leakage Current<br>(LA-ispMACH 4000Z)             | 0 ≤ V <sub>IN</sub> ≤ V <sub>CCO</sub>                                                                                                              | _         | 0.5 | 1           | μΑ   |

|                                                   | Input High Leakage Current                              | $3.6 \text{ V} < \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{Tj} = 105 \text{ °C}$<br>$3.0 \text{ V} \le \text{V}_{\text{CCO}} \le 3.6 \text{ V}$ | _         | _   | 20          | μΑ   |

| I <sub>IH</sub> 1, 2                              | (LA-ispMACH 4000V)                                      | $3.6 \text{ V} < \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{Tj} = 130 \text{ °C}$<br>$3.0 \text{ V} \le \text{V}_{\text{CCO}} \le 3.6 \text{ V}$ | _         | _   | 50          | μΑ   |

|                                                   | Input High Leakage Current (LA-ispMACH 4000Z)           | V <sub>CCO</sub> < V <sub>IN</sub> ≤ 5.5 V                                                                                                          | _         | _   | 10          | μΑ   |

|                                                   | I/O Weak Pull-up Resistor Current<br>(LA-ispMACH 4000V) | 0 ≤ V <sub>IN</sub> ≤ 0.7 V <sub>CCO</sub>                                                                                                          | -30       | _   | -200        | μΑ   |

| I <sub>PU</sub>                                   | I/O Weak Pull-up Resistor Current<br>(LA-ispMACH 4000Z) | 0 ≤ V <sub>IN</sub> ≤ 0.7 V <sub>CCO</sub>                                                                                                          | -30       |     | -150        |      |

| I <sub>PD</sub>                                   | I/O Weak Pull-down Resistor                             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MIN)                                                                                                      | 30        | _   | 150         | μΑ   |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current                         | V <sub>IN</sub> = V <sub>IL</sub> (MAX)                                                                                                             | 30        | _   | _           | μΑ   |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current                        | $V_{IN} = 0.7 V_{CCO}$                                                                                                                              | -30       | _   | _           | μΑ   |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current                          | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{BHT}}$                                                                                                | _         | _   | 150         | μΑ   |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current                         | $V_{BHT} \le V_{IN} \le V_{CCO}$                                                                                                                    | _         | _   | -150        | μΑ   |

| V <sub>BHT</sub>                                  | Bus Hold Trip Points                                    | _                                                                                                                                                   | VCCO*0.35 | _   | VCCO * 0.65 | V    |

| C <sub>1</sub>                                    | I/O Capacitance <sup>3</sup>                            | V <sub>CCO</sub> = 3.3 V, 2.5 V, 1.8 V                                                                                                              | _         | 8   | _           | pf   |

|                                                   |                                                         | $V_{CC} = 1.8 \text{ V}, V_{IO} = 0 \text{ to } V_{IH}$                                                                                             | _         |     | _           |      |

| C <sub>2</sub>                                    | Clock Capacitance <sup>3</sup>                          | V <sub>CCO</sub> = 3.3 V, 2. 5 V, 1.8 V                                                                                                             | _         | 6   | _           | pf   |

|                                                   |                                                         | $V_{CC} = 1.8 \text{ V}, V_{IO} = 0 \text{ to } V_{IH}$                                                                                             | _         |     | _           |      |

| C <sub>3</sub>                                    | Global Input Capacitance <sup>3</sup>                   | V <sub>CCO</sub> = 3.3 V, 2.5 V, 1.8 V                                                                                                              | _         | 6   | _           | pf   |

|                                                   |                                                         | V <sub>CC</sub> = 1.8 V, V <sub>IO</sub> = 0 to V <sub>IH</sub>                                                                                     | _         |     | _           |      |

- 1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

- 2. 2. 5 V tolerant inputs and I/O should only be placed in banks where 3.0 V  $\leq$  V<sub>CCO</sub>  $\leq$  3.6 V.

- 3.  $T_A = 25$  °C, f = 1.0 MHz.

- 4.  $I_{IH}$  excursions of up to 1.5  $\mu$ A maximum per pin above the spec limit may be observed for certain voltage conditions on no more than 10% of the device's I/O pins.

# 22. Supply Current, LA-ispMACH 4000V

Over recommended operating conditions.

### Table 22.1. Supply Current, LA-ispMACH 4000V

| Symbol   | Parameter                      | Condition               | Min. | Typical |   | Unit |  |

|----------|--------------------------------|-------------------------|------|---------|---|------|--|

| LA-ispMA | CH 4032V                       |                         |      |         |   |      |  |

| ICC      | Operating Power Supply Current | V <sub>CC</sub> = 3.3 V | _    | 11.8    | _ | mA   |  |

| ICC      | Standby Power Supply Current   | V <sub>CC</sub> = 3.3 V | _    | 11.3    | _ | mA   |  |

| LA-ispMA | LA-ispMACH 4064V               |                         |      |         |   |      |  |

| ICC      | Operating Power Supply Current | V <sub>CC</sub> = 3.3 V | _    | 12      | _ | mA   |  |

| ICC      | Standby Power Supply Current   | V <sub>CC</sub> = 3.3 V | _    | 11.5    | _ | mA   |  |

| LA-ispMA | LA-ispMACH 4128V               |                         |      |         |   |      |  |

| 100      | Operating Power Supply Current | V <sub>CC</sub> = 3.3 V | _    | 12      | _ | mA   |  |

| ICC      | Standby Power Supply Current   | V <sub>CC</sub> = 3.3 V | _    | 11.5    | _ | mA   |  |

# 23. Supply Current, LA-ispMACH 4000Z

Over recommended operating conditions.

Table 23.1. Supply Current, LA-ispMACH 4000Z

| Symbol                    | Parameter                      | Condition                                        | Min. | Typical | Max. | Unit |

|---------------------------|--------------------------------|--------------------------------------------------|------|---------|------|------|

| LA-ispMAC                 | H 4032Z                        | •                                                |      |         |      |      |

| ICC <sup>1, 2, 3, 5</sup> |                                | V <sub>CC</sub> = 1.8 V, T <sub>A</sub> = 25 °C  | _    | 50      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 70 °C  | _    | 58      | _    | μΑ   |

|                           | Operating Power Supply Current | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 85 °C  | _    | 60      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 125 °C | _    | 70      | _    | μΑ   |

| ICC <sup>4, 5</sup>       | Standby Power Supply Current   | $V_{CC} = 1.8 \text{ V, } T_A = 25 \text{ °C}$   | _    | 10      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 70 °C  | _    | 13      | 20   | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 85 °C  | _    | 15      | 25   | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 125 °C | _    | 22      |      | μΑ   |

| LA-ispMAC                 | H 4064Z                        |                                                  |      |         |      |      |

| ICC <sup>1, 2, 3, 5</sup> | Operating Power Supply Current | V <sub>CC</sub> = 1.8 V, T <sub>A</sub> = 25 °C  | _    | 80      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 70 °C  | _    | 89      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 85 °C  | _    | 92      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 125 °C | _    | 109     | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.8 V, T <sub>A</sub> = 25 °C  | _    | 11      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 70 °C  | _    | 15      | 25   | μΑ   |

| ICC <sup>4, 5</sup>       | Standby Power Supply Current   | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 85 °C  | _    | 18      | 35   | μΑ   |

|                           |                                | V <sub>CC</sub> = 1. 9V, T <sub>A</sub> = 125 °C | _    | 37      |      | μΑ   |

| LA-ispMAC                 | H 4128Z                        |                                                  |      |         |      |      |

| ICC <sup>1, 2, 3, 5</sup> | Operating Power Supply Current | V <sub>CC</sub> = 1.8 V, T <sub>A</sub> = 25 °C  | _    | 168     | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 70 °C  | _    | 190     | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 85 °C  | _    | 195     | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 125 °C | _    | 212     | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.8 V, T <sub>A</sub> = 25 °C  | _    | 12      | _    | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 70 °C  | _    | 16      | 35   | μΑ   |

| ICC <sup>4, 5</sup>       | Standby Power Supply Current   | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 85 °C  | _    | 19      | 50   | μΑ   |

|                           |                                | V <sub>CC</sub> = 1.9 V, T <sub>A</sub> = 125 °C | _    | 42      | _    | μΑ   |

- 1.  $T_A = 25$  °C, frequency = 1.0 MHz.

- 2. Device configured with 16-bit counters.

- 3. ICC varies with specific device configuration and operating frequency.

- 4. V<sub>CCO</sub> = 3.6 V, V<sub>IN</sub> = 0 V or V<sub>CCO</sub>, bus maintenance turned off. V<sub>IN</sub> above V<sub>CCO</sub> will add transient current above the specified standby ICC.

- 5. Includes V<sub>CCO</sub> current without output loading.

# 24. I/O DC Electrical Characteristics

1.0

V<sub>O</sub> Output Voltage (V)

1.5

Over recommended operating conditions.

Table 24.1. I/O DC Electrical Characteristics

| Input/Output    |         | V <sub>IL</sub>                        | VIII                                   | 1       | V <sub>OL</sub> Max  | V <sub>OH</sub> Min     | . * ( 6)               | 1 * ( 4)               |  |

|-----------------|---------|----------------------------------------|----------------------------------------|---------|----------------------|-------------------------|------------------------|------------------------|--|

| Standard        | Min (V) | Max (V)                                | Min (V)                                | Max (V) | (V)                  | (V)                     | I <sub>OL</sub> * (mA) | I <sub>OH</sub> * (mA) |  |

| LVTTI           | 0.2     | 0.00                                   | 2.0                                    |         | 0.40                 | V <sub>cco</sub> - 0.40 | 8.0                    | -4.0                   |  |

| LVTTL           | -0.3    | 0.80                                   | 2.0                                    | 5.5     | 0.20                 | V <sub>cco</sub> - 0.20 | 0.1                    | -0.1                   |  |

| LVCMOS 3.3      | 0.2     | 0.80                                   | 2.0                                    | E E     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0                    | -4.0                   |  |

| LVCIVIOS 3.3    | -0.3    | 0.80                                   | 2.0                                    | 5.5     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1                    | -0.1                   |  |

| LVCMOS 3 F      | 0.2     | 0.70                                   | 1.70                                   | 2.6     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0                    | -4.0                   |  |

| LVCMOS 2.5      | -0.3    | 0.70                                   | 1.70                                   | 3.6     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1                    | -0.1                   |  |

| LVCMOS 1.8      | 0.2     | 0.63                                   | 1 17                                   | 2.6     | 0.40                 | V <sub>cco</sub> - 0.45 | 2.0                    | -2.0                   |  |

| (4000V)         | -0.3    | 0.63                                   | 1.17                                   | 3.6     | 0.20                 | V <sub>cco</sub> - 0.20 | 0.1                    | -0.1                   |  |

| LVCMOS 1.8      | 0.2     | 0.25 * \/                              | 0.65 * 1/                              | 2.6     | 0.40                 | V <sub>cco</sub> - 0.45 | 2.0                    | -2.0                   |  |

| (4000Z)         | -0.3    | 0.35 * V <sub>cc</sub>                 | 0.65 * V <sub>CC</sub>                 | 3.6     | 0.20                 | V <sub>cco</sub> - 0.20 | 0.1                    | -0.1                   |  |

| PCI 3.3 (4000V) | -0.3    | 1.08                                   | 1.5                                    | 5.5     | 0.1 V <sub>cco</sub> | 0.9 V <sub>cco</sub>    | 1.5                    | -0.5                   |  |

| PCI 3.3 (4000Z) | -0.3    | 0.3 * 3.3 *<br>(V <sub>CC</sub> / 1.8) | 0.5 * 3.3 *<br>(V <sub>CC</sub> / 1.8) | 5.5     | 0.1 V <sub>CCO</sub> | 0.9 V <sub>cco</sub>    | 1.5                    | -0.5                   |  |

#### \*Note:

The average DC current drawn by I/Os between adjacent bank GND connections, or between the last GND in an I/O bank and the end of the I/O bank, as shown in the logic signals connection table, shall not exceed n\*8 mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

2.0

Figure 24.1. I/O DC Electrical Characteristics

# 25. LA-ispMACH 4000V/Z External Switching Characteristics

Over recommended operating conditions.

Table 25.1. LA-ispMACH 4000V/Z External Switching Characteristics

| Parameter                     | Description <sup>1, 2, 3</sup>                                             | •    | ACH 4000V<br>75 | -    | ACH 4000Z<br>75 | Unit |

|-------------------------------|----------------------------------------------------------------------------|------|-----------------|------|-----------------|------|

|                               |                                                                            | Min. | Max.            | Min. | Max.            |      |

| t <sub>PD</sub>               | 5-PT bypass combinatorial propagation delay                                | _    | 7.5             | _    | 7.5             | ns   |

| t <sub>PD_MC</sub>            | 20-PT combinatorial propagation delay through macrocell                    | _    | 8.0             | _    | 8.0             | ns   |

| ts                            | GLB register setup time before clock                                       | 4.5  | _               | 4.5  | _               | ns   |

| t <sub>ST</sub>               | GLB register setup time before clock with T-type register                  | 4.7  | _               | 4.7  | _               | ns   |

| t <sub>SIR</sub>              | GLB register setup time before clock, input register path                  | 1.7  | _               | 1.4  | _               | ns   |

| t <sub>SIRZ</sub>             | GLB register setup time before clock with zero hold                        | 2.7  | _               | 2.7  | _               | ns   |

| t <sub>H</sub>                | GLB register hold time after clock                                         | 0.0  | _               | 0.0  | _               | ns   |

| t <sub>HT</sub>               | GLB register hold time after clock with T-type register                    | 0.0  | _               | 0.0  | _               | ns   |

| t <sub>HIR</sub>              | GLB register hold time after clock, input register path                    | 1.0  | _               | 1.3  | _               | ns   |

| t <sub>HIRZ</sub>             | GLB register hold time after clock, input register path with zero hold     | 0.0  | _               | 0.0  | _               | ns   |

| tco                           | GLB register clock-to-output delay                                         | _    | 4.5             | _    | 4.5             | ns   |

| t <sub>R</sub>                | External reset pin to output delay                                         | _    | 9.0             | _    | 9.0             | ns   |

| t <sub>RW</sub>               | External reset pulse duration                                              | 4.0  | _               | 4.0  | _               | ns   |

| t <sub>PTOE/DIS</sub>         | Input to output local product term                                         | _    | 9.0             | _    | 9.0             | ns   |

| t <sub>GPTOE/DIS</sub>        | Input to output global product term output enable/disable                  | _    | 10.3            | _    | 10.5            | ns   |

| t <sub>GOE/DIS</sub>          | Global OE input to output enable/disable                                   | _    | 7.0             | _    | 7.0             | ns   |

| t <sub>CW</sub>               | Global clock width, high or low                                            | 2.8  | _               | 2.8  | _               | ns   |

| t <sub>GW</sub>               | Global gate width low (for low transparent) or high (for high transparent) | 2.8  | _               | 2.8  | _               | ns   |

| t <sub>WIR</sub>              | Input register clock width, high or low                                    | 2.8  | _               | 2.8  | _               | ns   |

| f <sub>MAX</sub> <sup>4</sup> | Clock frequency with internal feedback                                     | _    | 168             | _    | 168             | MHz  |

| f <sub>MAX</sub> (Ext.)       | Clock frequency with external feedback, $[1/(t_s + t_{CO})]$               | _    | 111             | _    | 111             | MHz  |

Timing v.3.2

- 1. Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

- 2. Measured using standard switching circuit, assuming GRP loading of 1 and 1 output switching.

- 3. Pulse widths and clock widths less than minimum will cause unknown behavior.

- 4. Standard 16-bit counter using GRP feedback

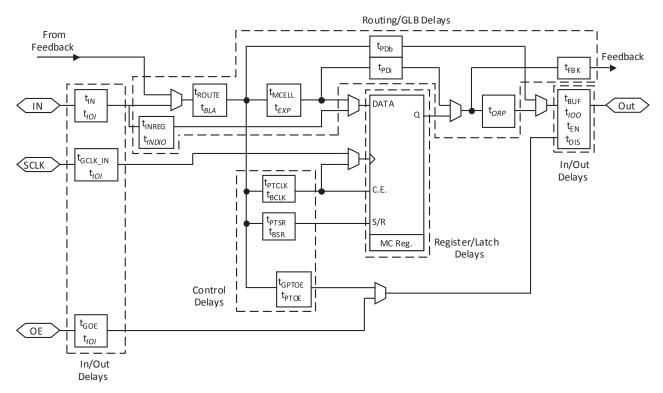

## 26. Timing Model

The task of determining the timing through the LA-ispMACH 4000V/Z automotive family, like any CPLD, is relatively simple. The timing model provided in Figure 26.1 shows the specific delay paths. Once the implementation of a given function is determined either conceptually or from the software report file, the delay path of the function can easily be determined from the timing model. The Lattice design tools report the timing delays based on the same timing model for a particular design. Note that the internal timing parameters are given for reference only, and are not tested. The external timing parameters are tested and guaranteed for every device. For more information on the timing model and usage, refer to TN1004, ispMACH 4000 Timing Model Design and Usage Guidelines.

Note: Italicized items are optional delay adders.

37

Figure 26.1. LA-ispMACH 4000V/Z Automotive Timing Model

## 27. LA-ispMACH 4000V/Z Internal Timing Parameters

Over recommended operating conditions.

Table 27.1. LA-ispMACH 4000V/Z Internal Timing Parameters

| Parameter            | Description                                                        | -    | ACH 4000V<br>-75 | _    | ACH 4000Z<br>75 | Units |

|----------------------|--------------------------------------------------------------------|------|------------------|------|-----------------|-------|

|                      |                                                                    | Min. | Max.             | Min. | Max.            |       |

| In/Out Delay         | /5                                                                 |      |                  |      |                 |       |

| t <sub>IN</sub>      | Input Buffer Delay                                                 | _    | 1.50             | _    | 1.80            | ns    |

| t <sub>GOE</sub>     | Global OE Pin Delay                                                | _    | 6.04             | _    | 4.30            | ns    |

| t <sub>GCLK_IN</sub> | Global Clock Input Buffer Delay                                    | _    | 2.28             | _    | 2.15            | ns    |

| t <sub>BUF</sub>     | Delay through Output Buffer                                        | _    | 1.50             | _    | 1.30            | ns    |

| t <sub>EN</sub>      | Output Enable Time                                                 | _    | 0.96             | _    | 2.70            | ns    |

| t <sub>DIS</sub>     | Output Disable Time                                                | _    | 0.96             | _    | 2.70            | ns    |

| Routing/GLB          | B Delays                                                           |      |                  | Ц    | П               |       |

| t <sub>ROUTE</sub>   | Delay through GRP                                                  | _    | 2.26             | _    | 2.50            | ns    |

| t <sub>MCELL</sub>   | Macrocell Delay                                                    | _    | 1.45             | _    | 1.00            | ns    |

| t <sub>INREG</sub>   | Input Buffer to Macrocell Register Delay                           | _    | 0.96             | _    | 1.00            | ns    |

| t <sub>FBK</sub>     | Internal Feedback Delay                                            | _    | 0.00             | _    | 0.05            | ns    |

| t <sub>PDb</sub>     | 5-PT Bypass Propagation Delay                                      | _    | 2.24             | _    | 1.90            | ns    |

| t <sub>PDi</sub>     | Macrocell Propagation Delay                                        | _    | 1.24             | _    | 1.00            | ns    |

| Register/Lat         | ch Delays                                                          |      |                  | I    | I               | l     |

| ts                   | D-Register Setup Time (Global Clock)                               | 1.57 | _                | 1.35 | _               | ns    |

| t <sub>S_PT</sub>    | D-Register Setup Time (Product Term<br>Clock)                      | 1.32 | _                | 2.45 | _               | ns    |

| t <sub>ST</sub>      | T-Register Setup Time (Global Clock)                               | 1.77 | _                | 1.55 | _               | ns    |

| t <sub>ST_PT</sub>   | T-Register Setup Time (Product Term<br>Clock)                      | 1.32 | _                | 2.75 | _               | ns    |

| t <sub>H</sub>       | D-Register Hold Time                                               | 2.93 | _                | 3.15 | _               | ns    |

| t <sub>HT</sub>      | T-Register Hold Time                                               | 2.93 | _                | 3.15 | _               | ns    |

| t <sub>SIR</sub>     | D-Input Register Setup Time (Global<br>Clock)                      | 1.57 | _                | 0.75 | _               | ns    |

| t <sub>SIR_PT</sub>  | D-Input Register Setup Time (Product<br>Term Clock)                | 1.45 | _                | 1.45 | _               | ns    |

| t <sub>HIR</sub>     | D-Input Register Hold Time (Global Clock)                          | 1.18 | _                | 1.95 | _               | ns    |

| t <sub>HIR_PT</sub>  | D-Input Register Hold Time (Product Term Clock)                    | 1.18 | _                | 1.18 | _               | ns    |

| t <sub>COi</sub>     | Register Clock to Output/Feedback MUX Time                         | _    | 0.67             | _    | 1.05            | ns    |

| t <sub>CES</sub>     | Clock Enable Setup Time                                            | 2.25 | _                | 2.00 | _               | ns    |

| t <sub>CEH</sub>     | Clock Enable Hold Time                                             | 1.88 | _                | 0.00 | _               | ns    |

| t <sub>SL</sub>      | Latch Setup Time (Global Clock)                                    | 1.57 | _                | 1.65 | _               | ns    |

| t <sub>SL_PT</sub>   | Latch Setup Time (Product Term Clock)                              | 1.32 | _                | 2.15 | _               | ns    |

| t <sub>HL</sub>      | Latch Hold Time                                                    | 1.17 | _                | 1.17 | _               | ns    |

| t <sub>GOi</sub>     | Latch Gate to Output/Feedback MUX Time                             | _    | 0.33             | _    | 0.33            | ns    |

| t <sub>PDLi</sub>    | Propagation Delay through Transparent Latch to Output/Feedback MUX | _    | 0.25             | _    | 0.25            | ns    |

| Parameter          | Description                                            | LA-ispMACH 4000V<br>-75 |      | LA-ispMACH 4000Z<br>-75 |      | Units |

|--------------------|--------------------------------------------------------|-------------------------|------|-------------------------|------|-------|

|                    |                                                        | Min.                    | Max. | Min.                    | Max. |       |

| t <sub>SRi</sub>   | Asynchronous Reset or Set to Output/Feedback MUX Delay | 0.28                    | _    | _                       | 0.28 | ns    |

| t <sub>SRR</sub>   | Asynchronous Reset or Set Recovery Time                | 1.67                    | _    | _                       | 1.67 | ns    |

| Control Delay      | ys                                                     |                         |      |                         |      |       |

| t <sub>BCLK</sub>  | GLB PT Clock Delay                                     | _                       | 1.12 | _                       | 1.25 | ns    |

| t <sub>PTCLK</sub> | Macrocell PT Clock Delay                               | _                       | 0.87 | _                       | 1.25 | ns    |

| t <sub>BSR</sub>   | GLB PT Set/Reset Delay                                 | _                       | 1.83 | _                       | 1.83 | ns    |

| t <sub>PTSR</sub>  | Macrocell PT Set/Reset Delay                           | _                       | 3.41 | _                       | 2.72 | ns    |

| t <sub>GPTOE</sub> | Global PT OE Delay                                     | _                       | 5.58 | _                       | 3.50 | ns    |

| t <sub>PTOE</sub>  | Macrocell PT OE Delay                                  | _                       | 4.28 | _                       | 2.00 | ns    |

Timing v.3.2