Product data sheet

## 1. General description

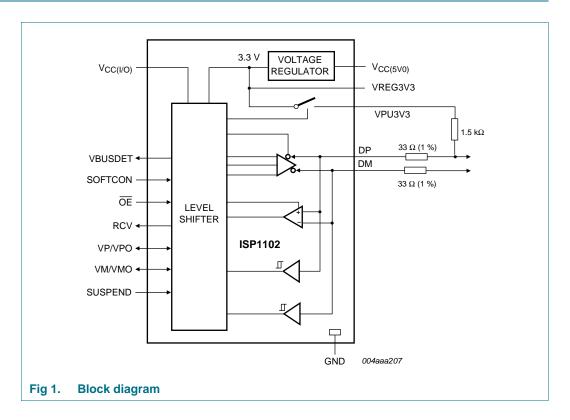

The ISP1102 Universal Serial Bus (USB) transceiver is fully compliant with *Universal Serial Bus Specification Rev. 2.0.* The ISP1102 can transmit and receive USB data at full-speed (12 Mbit/s).

The transceiver allows USB Application-Specific Integrated Circuits (ASICs) and Programmable Logic Devices (PLDs) with power supply voltages from 1.65 V to 3.6 V to interface with the physical layer of the USB. The transceiver has an integrated 5 V-to-3.3 V voltage regulator for direct powering through USB supply line  $V_{BUS}$ . The transceiver has an integrated voltage detector to detect the presence of the  $V_{BUS}$  voltage ( $V_{CC(5V0)}$ ). When  $V_{CC(5V0)}$  or VREG3V3 is lost, the DP and DM pins can be shared with other serial protocols.

The transceiver is a bidirectional differential interface and is available in HBCC16 and HVQFN14 packages.

The transceiver is ideal for use in portable electronic devices, such as mobile phones, digital still cameras, Personal Digital Assistants (PDAs) and Information Appliances (IAs).

#### 2. Features

- Complies with Universal Serial Bus Specification Rev. 2.0

- Supports data transfer at full-speed (12 Mbit/s)

- Integrated 5 V-to-3.3 V voltage regulator to power through USB line V<sub>BUS</sub>

- V<sub>BUS</sub> voltage presence indication on pin VBUSDET

- VP and VM pins function in bidirectional mode, allowing pin count saving for the ASIC interface

- Used as USB device transceiver or USB host transceiver

- Stable RCV output during Single-Ended Zero (SE0) condition

- Two single-ended receivers with hysteresis

- Low-power operation

- Supports I/O voltage range from 1.65 V to 3.6 V

- ±12 kV ElectroStatic Discharge (ESD) protection (for the ISP1102W) at the DP, DM, V<sub>CC(5V0)</sub> and GND pins

- Full industrial operating temperature range from -40 °C to +85 °C

- Available in HBCC16 and HVQFN14 lead-free and halogen-free packages

# **ST-NXP Wireless**

**Advanced USB transceiver**

# 3. Applications

- Portable electronic devices, such as:

- ◆ Mobile phone

- ◆ Digital still camera

- Personal Digital Assistant (PDA)

- ◆ Information Appliance (IA)

# 4. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                                                      |          |  |  |  |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|             | Name    | Description                                                                                                          | Version  |  |  |  |

| ISP1102W    | HBCC16  | plastic thermal enhanced bottom chip carrier; 16 terminals; body 3 $\times$ 3 $\times$ 0.65 mm                       | SOT639-2 |  |  |  |

| ISP1102BS   | HVQFN14 | plastic thermal enhanced very thin quad flat package; no leads; 14 terminals; body 2.5 $\times$ 2.5 $\times$ 0.85 mm | SOT773-1 |  |  |  |

<sup>[1]</sup> For new designs planning to use the ISP1102W, refer to the ISP1102A Advanced USB transceiver data sheet.

# 5. Block diagram

ISP1102\_6 © ST-NXP Wireless 2009. All rights reserved.

**ISP1102 ST-NXP Wireless**

**Advanced USB transceiver**

# **Pinning information**

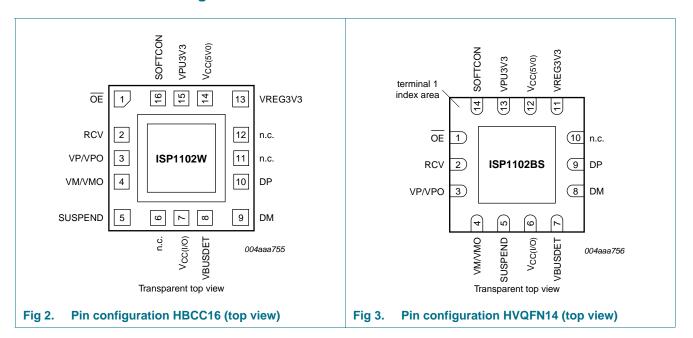

## 6.1 Pinning

## 6.2 Pin description

Table 2. Pin description

| Symbol[1] | Pin    |                | Туре | Description                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------|--------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           | HBCC16 | HBCC16 HVQFN14 |      |                                                                                                                                                                                                                                                                                                                              |  |  |

| ŌĒ        | 1      | 1              | I    | input for output enable (CMOS level with respect to $V_{CC(I/O)}$ , active LOW); enables the transceiver to transmit data on the USB bus input pad; push pull; CMOS                                                                                                                                                          |  |  |

| RCV       | 2      | 2              | 0    | differential data receiver output (CMOS level with respect to $V_{CC(I/O)}$ ); driven LOW when input SUSPEND is HIGH; the output state of RCV is preserved and stable during an SE0 condition                                                                                                                                |  |  |

|           |        |                |      | output pad; push pull; 4 mA output drive; CMOS                                                                                                                                                                                                                                                                               |  |  |

| VP/VPO    | 3      | 3              | I/O  | single-ended DP receiver output VP (CMOS level with respect to $V_{CC(I/O)}$ ); for external detection of SE0, error conditions and speed of connected device; this pin also acts as drive data input VPO; see <u>Table 3</u> and <u>Table 4</u>                                                                             |  |  |

|           |        |                |      | bidirectional pad; push-pull input; 3-state output; 4 mA output drive; CMOS                                                                                                                                                                                                                                                  |  |  |

| VM/VMO    | 4      | 4              | I/O  | single-ended DM receiver output VM (CMOS level with respect to $V_{CC(I/O)}$ ); for external detection of SE0, error conditions and speed of connected device; this pin also acts as drive data input VMO; see <u>Table 3</u> and <u>Table 4</u> bidirectional pad; push-pull input; 3-state output; 4 mA output drive; CMOS |  |  |

## **Advanced USB transceiver**

Table 2.

Pin description ...continued

| Symbol[1]            | Pin                |                 | Type | Description                                                                                                                                                                                                                                                   |

|----------------------|--------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | HBCC16             | HVQFN14         |      |                                                                                                                                                                                                                                                               |

| SUSPEND              | 5                  | 5               | I    | suspend input (CMOS level with respect to $V_{\text{CC(I/O)}}$ ); a HIGH level enables low-power state while the USB bus is inactive and drives output RCV to a LOW level                                                                                     |

|                      |                    |                 |      | input pad; push pull; CMOS                                                                                                                                                                                                                                    |

| n.c.                 | 6                  | -               | -    | not connected                                                                                                                                                                                                                                                 |

| V <sub>CC(I/O)</sub> | 7                  | 6               | -    | supply voltage for digital I/O pins (1.65 V to 3.6 V). When $V_{CC(I/O)}$ is not connected, the DP and DM pins are in 3-state. This supply pin is totally independent of $V_{CC(5V0)}$ and VREG3V3 and must never exceed the VREG3V3 voltage.                 |

| VBUSDET              | 8                  | 7               | 0    | $V_{BUS}$ indicator output (CMOS level with respect to $V_{CC(I/O)}$ ); when $V_{BUS} > 4.1$ V, VBUSDET = HIGH and when $V_{BUS} < 3.6$ V, VBUSDET = LOW; when SUSPEND = HIGH, the VBUSDET function is invalid output pad; push pull; 4 mA output drive; CMOS |

| DM                   | 9                  | 8               | AI/O | negative USB data bus connection (analog, differential)                                                                                                                                                                                                       |

| DP                   | 10                 | 9               | AI/O | positive USB data bus connection (analog, differential)                                                                                                                                                                                                       |

| n.c.                 | 11                 | -               | -    | not connected                                                                                                                                                                                                                                                 |

| n.c.                 | 12                 | -               | _    | not connected                                                                                                                                                                                                                                                 |

| n.c.                 | -                  | 10              | _    | not connected                                                                                                                                                                                                                                                 |

| VREG3V3              | 13                 | 11              | -    | internal regulator option: regulated supply voltage output (3.0 V to 3.6 V) during 5 V operation; a decoupling capacitor of at least 0.1 $\mu\text{F}$ is required                                                                                            |

|                      |                    |                 |      | <b>regulator bypass option</b> : used as a supply voltage input (3.3 V $\pm$ 10 %) for 3.3 V operation                                                                                                                                                        |

| V <sub>CC(5V0)</sub> | 14                 | 12              | -    | internal regulator option: supply voltage input (4.0 V to 5.5 V); can be directly connected to USB line $V_{BUS}$                                                                                                                                             |

|                      |                    |                 |      | regulator bypass option: connect to VREG3V3                                                                                                                                                                                                                   |

| VPU3V3               | 15                 | 13              | -    | pull-up supply voltage (3.3 V $\pm$ 10 %); connect an external 1.5 k $\!\Omega$ resistor on DP (full-speed)                                                                                                                                                   |

|                      |                    |                 |      | This pin function is controlled by the SOFTCON input:                                                                                                                                                                                                         |

|                      |                    |                 |      | <b>SOFTCON = LOW</b> — VPU3V3 floating (high-Z); ensures zero pull-up current                                                                                                                                                                                 |

|                      |                    |                 |      | <b>SOFTCON = HIGH</b> — VPU3V3 = 3.3 V; internally connected to VREG3V3                                                                                                                                                                                       |

| SOFTCON              | 16                 | 14              | I    | software controlled USB connection input; a HIGH level applies 3.3 V to pin VPU3V3, which is connected to an external 1.5 k $\Omega$ pull-up resistor; this allows USB connect or disconnect signaling to be controlled by software                           |

|                      |                    |                 |      | input pad; push pull; CMOS                                                                                                                                                                                                                                    |

| GND                  | exposed<br>die pad | exposed die pad | -    | ground supply; down bonded to the exposed die pad (heat sink); to be connected to the PCB ground                                                                                                                                                              |

<sup>[1]</sup> Symbol names with an overscore (for example,  $\overline{\text{OE}}$ ) indicate active LOW signals.

**Advanced USB transceiver**

## 7. Functional description

#### 7.1 Function selection

Table 3. Function selection

| SUSPEND | OE   | DP, DM                | RCV                     | VP/VPO    | VM/VMO    | Function                                                |

|---------|------|-----------------------|-------------------------|-----------|-----------|---------------------------------------------------------|

| LOW     | LOW  | driving or receiving  | active                  | VPO input | VMO input | normal driving (differential receiver active)           |

| LOW     | HIGH | receiving[1]          | active                  | VP output | VM output | receiving                                               |

| HIGH    | LOW  | driving               | inactive <sup>[2]</sup> | VPO input | VMO input | driving during suspend (differential receiver inactive) |

| HIGH    | HIGH | high-Z <sup>[1]</sup> | inactive <sup>[2]</sup> | VP output | VM output | low-power state                                         |

<sup>[1]</sup> Signal levels on the DP and DM pins are determined by other USB devices and external pull-up or pull-down resistors.

## 7.2 Operating functions

Table 4. Driving function using differential input data interface (pin  $\overline{OE} = LOW$ )

| VM/VMO | VP/VPO | Data                 |

|--------|--------|----------------------|

| LOW    | LOW    | SE0                  |

| LOW    | HIGH   | differential logic 1 |

| HIGH   | LOW    | differential logic 0 |

| HIGH   | HIGH   | illegal state        |

Table 5. Receiving function (pin  $\overline{OE} = HIGH$ )

| DP, DM               | RCV     | VP/VPO | VM/VMO |

|----------------------|---------|--------|--------|

| Differential logic 0 | LOW     | LOW    | HIGH   |

| Differential logic 1 | HIGH    | HIGH   | LOW    |

| SE0                  | RCV*[1] | LOW    | LOW    |

<sup>[1]</sup> RCV\* denotes the signal level on output RCV just before the SE0 state occurs. This level is stable during the SE0 period.

#### 7.3 Power supply configurations

The ISP1102 can be used with various power supply configurations, which can be changed dynamically. <u>Table 7</u> provides an overview of power supply configurations.

**Normal mode** —  $V_{CC(I/O)}$  is connected.  $V_{CC(5V0)}$  is connected only, or  $V_{CC(5V0)}$  and VREG3V3 are connected.

For the 5 V operation,  $V_{CC(5V0)}$  is connected to a 5 V source (4.0 V to 5.5 V). The internal voltage regulator then produces 3.3 V for USB connections.

For the 3.3 V operation, both  $V_{CC(5V0)}$  and VREG3V3 are connected to a 3.3 V source (3.0 V to 3.6 V).

$V_{CC(I/O)}$  is independently connected to a voltage source (1.65 V to 3.6 V), depending on the supply voltage of the external circuit.

<sup>[2]</sup> In suspend mode (SUSPEND = HIGH), the differential receiver is inactive and output RCV is always LOW. The resume signaling is detected through single-ended receivers VP/VPO and VM/VMO.

#### **Advanced USB transceiver**

**Sharing mode** —  $V_{CC(I/O)}$  is connected only,  $V_{CC(5V0)}$  is < 3.6 V and VREG3V3 is < 2.4 V. In this mode, the DP and DM pins are 3-stated and the ISP1102 allows external signals of up to 3.6 V to share the DP and DM lines. The internal circuits of the ISP1102 ensure that virtually no current (maximum 10  $\mu$ A) is drawn through the DP and DM lines. The power consumption through pin  $V_{CC(I/O)}$  drops to the low-power (suspended) state level.

Pins VBUSDET and RCV are driven to LOW to indicate this mode. The VBUSDET function is ignored during suspend mode of the ISP1102.

Some hysteresis is built into the detection of VREG3V3 lost.

Table 6. Pin states in sharing mode

| Pin                  | Sharing mode          |

|----------------------|-----------------------|

| V <sub>CC(5V0)</sub> | < 3.6 V               |

| VREG3V3              | < 2.4 V               |

| V <sub>CC(I/O)</sub> | 1.65 V to 3.6 V input |

| VPU3V3               | high-Z (off)          |

| DP, DM               | high-Z                |

| VP/VPO, VM/VMO[1]    | high-Z                |

| RCV                  | LOW                   |

| VBUSDET              | LOW                   |

| OE, SUSPEND, SOFTCON | high-Z                |

<sup>[1]</sup> VP/VPO and VM/VMO are bidirectional pins.

Table 7. Power supply configuration overview

| V <sub>CC(5V0)</sub> | Configuration | Special characteristics                         |

|----------------------|---------------|-------------------------------------------------|

| Connected            | normal mode   | -                                               |

| < 3.6 V              | sharing mode  | DP, DM and VPU3V3 high-Z; VBUSDET is driven LOW |

**ISP1102 ST-NXP Wireless**

#### Advanced USB transceiver

## 7.4 Power supply input options

The ISP1102 has two power supply input options.

Internal regulator — Pin  $V_{CC(5V0)}$  is connected to 4.0 V to 5.5 V. The internal regulator is used to supply the internal circuitry with 3.3 V (nominal). The VREG3V3 pin becomes a 3.3 V output reference.

**Regulator bypass** — Pins V<sub>CC(5V0)</sub> and VREG3V3 are connected to the same supply. The internal regulator is bypassed and the internal circuitry is supplied directly from pin VREG3V3. The voltage range is 3.0 V to 3.6 V to comply with Universal Serial Bus Specification Rev. 2.0.

The supply voltage range for each input option is specified in Table 8.

Table 8. **Power supply input options**

| Input option       | V <sub>CC(5V0)</sub>                                                           | VREG3V3                                             | V <sub>CC(I/O)</sub>                                |

|--------------------|--------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| Internal regulator | supply input for internal regulator (4.0 V to 5.5 V)                           | voltage reference output (3.3 V, 300 $\mu\text{A})$ | supply input for digital I/O pins (1.65 V to 3.6 V) |

| Regulator bypass   | connected to VREG3V3 with<br>maximum voltage drop of 0.3 V<br>(2.7 V to 3.6 V) | supply input (3.0 V to 3.6 V)                       | supply input for digital I/O pins (1.65 V to 3.6 V) |

Advanced USB transceiver

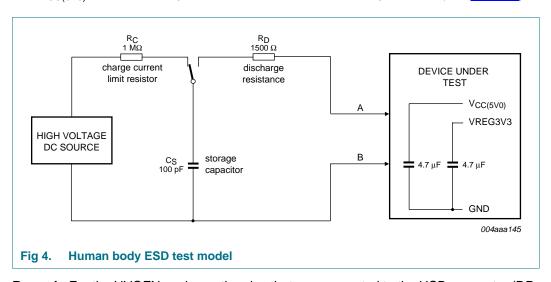

# 8. ElectroStatic Discharge (ESD)

## 8.1 ESD protection

For the HBCC package, the pins that are connected to the USB connector (DP, DM,  $V_{CC(5V0)}$  and GND) have a minimum of  $\pm 12$  kV ESD protection. The  $\pm 12$  kV measurement is limited by the test equipment. Capacitors of 4.7  $\mu$ F connected from VREG3V3 to GND and  $V_{CC(5V0)}$  to GND are required to achieve this  $\pm 12$  kV ESD protection (see Figure 4).

**Remark:** For the HVQFN package, the pins that are connected to the USB connector (DP, DM,  $V_{CC(5V0)}$  and GND) have a minimum of  $\pm 7$  kV ESD protection.

## 8.2 ESD test conditions

A detailed report on test set up and results is available on request.

**ISP1102 ST-NXP Wireless**

**Advanced USB transceiver**

9 of 25

# **Limiting values**

Table 9. **Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol               | Parameter                       | Conditions                                                                 | Min              | Max                 | Unit |

|----------------------|---------------------------------|----------------------------------------------------------------------------|------------------|---------------------|------|

| V <sub>CC(5V0)</sub> | supply voltage (5.0 V)          |                                                                            | -0.5             | +6.0                | V    |

| V <sub>CC(I/O)</sub> | input/output supply voltage     | )                                                                          | -0.5             | +4.6                | V    |

| VI                   | input voltage                   |                                                                            | -0.5             | $V_{CC(I/O)} + 0.5$ | V    |

| I <sub>lu</sub>      | latch-up current                | $V_I = -1.8 \text{ V to } +5.4 \text{ V}$                                  | -                | 100                 | mA   |

| V <sub>esd</sub>     | electrostatic discharge voltage | pins DP, DM, $V_{CC(5V0)}$ and GND; $I_{LI}$ < 3 $\mu$ A for HBCC package  | [1][2] -12000    | +12000              | V    |

|                      |                                 | pins DP, DM, $V_{CC(5V0)}$ and GND; $I_{LI}$ < 3 $\mu$ A for HVQFN package | [2] -7000        | +7000               | V    |

|                      |                                 | all other pins; $I_{LI}$ < 1 $\mu$ A                                       | <u>[2]</u> –2000 | +2000               | V    |

| T <sub>stg</sub>     | storage temperature             |                                                                            | -40              | +125                | °C   |

<sup>[1]</sup> Testing equipment limits measurement to only ±12 kV. Capacitors needed on V<sub>CC(5V0)</sub> and VREG3V3 (see Section 8).

## 10. Recommended operating conditions

Table 10. Recommended operating conditions

| Symbol               | Parameter                      | Conditions           | Min  | Тур | Max                  | Unit |

|----------------------|--------------------------------|----------------------|------|-----|----------------------|------|

| V <sub>CC(5V0)</sub> | supply voltage (5.0 V)         |                      | 4.0  | 5.0 | 5.5                  | V    |

| $V_{CC(I/O)}$        | input/output supply voltage    |                      | 1.65 | -   | 3.6                  | V    |

| VI                   | input voltage                  |                      | 0    | -   | V <sub>CC(I/O)</sub> | V    |

| V <sub>IA(I/O)</sub> | input voltage on analog I/O pi | ns on pins DP and DM | 0    | -   | 3.6                  | V    |

| Tj                   | junction temperature           |                      | -40  | -   | +125                 | °C   |

| T <sub>amb</sub>     | ambient temperature            |                      | -40  | -   | +85                  | °C   |

## 11. Static characteristics

Table 11. Static characteristics: supply pins

$V_{\text{CC}(5V0)} = 4.0 \text{ V to } 5.5 \text{ V or } V_{\text{(VREG3V3)}} = 3.0 \text{ V to } 3.6 \text{ V}; V_{\text{CC}(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{\text{GND}} = 0 \text{ V}; \text{ see } \frac{\text{Table 8}}{\text{N}} \text{ for valid voltage}$ level combinations;  $T_{amb} = -40$  °C to +85 °C; unless otherwise specified.

|                            |                                            | ·                                                                                                                    |              |     |     |      |

|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------|-----|-----|------|

| Symbol                     | Parameter                                  | Conditions                                                                                                           | Min          | Тур | Max | Unit |

| V <sub>(VREG3V3)</sub>     | voltage on pin VREG3V3                     | internal regulator option; $I_{load} \leq 300~\mu A$                                                                 | [1][2] 3.0   | 3.3 | 3.6 | V    |

| I <sub>CC</sub>            | supply current                             | transmitting and receiving at 12 Mbit/s; $C_L = 50$ pF on pins DP and DM                                             | [3] -        | 4   | 8   | mA   |

| I <sub>CC(I/O)</sub>       | supply current on pin $V_{CC(I/O)}$        | transmitting and receiving at 12 Mbit/s                                                                              | <u>[3]</u> _ | 1   | 2   | mA   |

| I <sub>CC(idle)</sub>      | idle and SE0 supply current                | idle: $V_{DP} > 2.7 \text{ V}$ , $V_{DM} < 0.3 \text{ V}$ ; SE0: $V_{DP} < 0.3 \text{ V}$ , $V_{DM} < 0.3 \text{ V}$ | [4] _        | -   | 300 | μА   |

| I <sub>CC(I/O)(stat)</sub> | static supply current on pin $V_{CC(I/O)}$ | idle, SE0 or suspend                                                                                                 | -            | -   | 20  | μΑ   |

<sup>[2]</sup> Equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  resistor (Human Body Model).

#### **Advanced USB transceiver**

Table 11.

Static characteristics: supply pins ...continued

$V_{CC(5V0)} = 4.0 \text{ V to } 5.5 \text{ V or } V_{(VREG3V3)} = 3.0 \text{ V to } 3.6 \text{ V}; V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{GND} = 0 \text{ V}; \text{ see } \frac{\text{Table 8}}{\text{C}} \text{ for valid voltage level combinations; } T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}; \text{ unless otherwise specified.}$

| Symbol                       | Parameter                                             | Conditions                                                                                                              | Min            | Тур  | Max | Unit |

|------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------|------|-----|------|

| I <sub>CC(susp)</sub>        | suspend supply current                                | SUSPEND = HIGH                                                                                                          | [4] -          | -    | 20  | μΑ   |

| $I_{CC(I/O)(sharing)}$       | sharing mode supply current on pin $V_{CC(I/O)}$      | $V_{CC(5V0)} < 3.6 \text{ V}$                                                                                           | -              | -    | 20  | μΑ   |

| $I_{load(sharing)DM}$        | sharing mode load current on pin DM                   | $V_{CC(5V0)}$ < 3.6 V; SOFTCON = LOW; $V_{DM}$ = 3.6 V                                                                  | -              | -    | 10  | μΑ   |

| I <sub>load(sharing)DP</sub> | sharing mode load current on pin DP                   | $V_{CC(5V0)}$ < 3.6 V; SOFTCON = LOW; $V_{DP}$ = 3.6 V                                                                  | -              | -    | 10  | μΑ   |

| V <sub>CC(5V0)th</sub>       | supply voltage detection                              | $1.65 \text{ V} \le V_{CC(I/O)} \le 3.6 \text{ V}$                                                                      |                |      |     |      |

|                              | threshold (5.0 V)                                     | supply lost                                                                                                             | -              | -    | 3.6 | V    |

|                              |                                                       | supply present                                                                                                          | 4.1            | -    | -   | V    |

| $V_{CC(5V0)hys}$             | supply voltage detection hysteresis (5.0 V)           | V <sub>CC(I/O)</sub> = 1.8 V                                                                                            | -              | 70   | -   | mV   |

| V <sub>CC(I/O)th</sub>       | supply voltage detection threshold (I/O)              | $V_{(VREG3V3)} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                       |                |      |     |      |

|                              |                                                       | supply lost                                                                                                             | -              | -    | 0.5 | V    |

|                              |                                                       | supply present                                                                                                          | 1.4            | -    | -   | V    |

| $V_{CC(I/O)(hys)}$           | supply voltage detection hysteresis (I/O)             | $V_{\text{(VREG3V3)}} = 3.3 \text{ V}$                                                                                  | -              | 0.45 | -   | V    |

| $V_{REG(3V3)th}$             | regulated supply voltage detection threshold (3.3 V)  | $\begin{array}{l} 1.65 \ V \leq V_{CC(I/O)} \leq V_{(VREG3V3)}; \\ 2.7 \ V \leq V_{(VREG3V3)} \leq 3.6 \ V \end{array}$ |                |      |     |      |

|                              |                                                       | supply lost                                                                                                             | -              | -    | 0.8 | V    |

|                              |                                                       | supply present                                                                                                          | <u>[5]</u> 2.4 | -    | -   | V    |

| V <sub>REG(3V3)hys</sub>     | regulated supply voltage detection hysteresis (3.3 V) | $V_{CC(I/O)} = 1.8 \text{ V}$                                                                                           | -              | 0.45 | -   | V    |

<sup>[1]</sup>  $I_{load}$  includes the pull-up resistor current through pin VPU3V3.

Table 12. Static characteristics: digital pins

$V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V; } V_{GND} = 0 \text{ V; } T_{amb} = -40 \text{ °C to } +85 \text{ °C; } unless otherwise specified.$

| Symbol                                 | Parameter                 | Conditions              | Min                     | Тур | Max                     | Unit |

|----------------------------------------|---------------------------|-------------------------|-------------------------|-----|-------------------------|------|

| V <sub>CC(I/O)</sub> = 1.65 V to 3.6 V |                           |                         |                         |     |                         |      |

| Input levels                           |                           |                         |                         |     |                         |      |

| V <sub>IL</sub>                        | LOW-level input voltage   |                         | -                       | -   | 0.3V <sub>CC(I/O)</sub> | V    |

| $V_{IH}$                               | HIGH-level input voltage  |                         | 0.6V <sub>CC(I/O)</sub> | -   | -                       | V    |

| Output leve                            | ls                        |                         |                         |     |                         |      |

| V <sub>OL</sub>                        | LOW-level output voltage  | $I_{OL} = 100 \mu A$    | -                       | -   | 0.15                    | V    |

|                                        |                           | $I_{OL} = 2 \text{ mA}$ | -                       | -   | 0.4                     | V    |

| V <sub>OH</sub>                        | HIGH-level output voltage | $I_{OH} = 100 \mu A$    | $V_{CC(I/O)} - 0.15$    | -   | -                       | V    |

|                                        |                           | $I_{OH} = 2 \text{ mA}$ | $V_{CC(I/O)}-0.4$       | -   | -                       | V    |

© ST-NXP Wireless 2009. All rights reserved.

<sup>[2]</sup> The minimum voltage is 2.7 V in suspend mode.

<sup>[3]</sup> Maximum value characterized only, not tested in production.

<sup>[4]</sup> Excluding any load current and VPU3V3 or  $V_{SW}$  source current to the 1.5 k $\Omega$  and 15 k $\Omega$  pull-up and pull-down resistors (200  $\mu$ A typ.).

<sup>[5]</sup> When  $V_{CC(I/O)}$  < 2.7 V, the minimum value for  $V_{REG(3V3)th}$  = 2.0 V for supply present condition.

**ISP1102 ST-NXP Wireless**

#### **Advanced USB transceiver**

Table 12.

Static characteristics: digital pins ...continued

$V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{GND} = 0 \text{ V}; T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}; unless otherwise specified.}$

| Symbol          | Parameter                            | Conditions              | Min           | Тур | Max  | Unit |

|-----------------|--------------------------------------|-------------------------|---------------|-----|------|------|

| Leakage cu      | ırrent                               |                         |               |     |      |      |

| I <sub>LI</sub> | input leakage current                |                         | <u>[1]</u> –1 | -   | +1   | μА   |

| Capacitano      | ce                                   |                         |               |     |      |      |

| C <sub>in</sub> | input capacitance                    | pin to GND              | -             | -   | 10   | pF   |

| Example 1       | : $V_{CC(I/O)}$ = 1.8 V $\pm$ 0.15 V |                         |               |     |      |      |

| Input levels    | )                                    |                         |               |     |      |      |

| $V_{IL}$        | LOW-level input voltage              |                         | -             | -   | 0.5  | V    |

| $V_{IH}$        | HIGH-level input voltage             |                         | 1.2           | -   | -    | V    |

| Output leve     | els                                  |                         |               |     |      |      |

| $V_{OL}$        | LOW-level output voltage             | $I_{OL} = 100 \mu A$    | -             | -   | 0.15 | V    |

|                 |                                      | $I_{OL} = 2 \text{ mA}$ | -             | -   | 0.4  | V    |

| $V_{OH}$        | HIGH-level output voltage            | $I_{OH} = 100 \mu A$    | 1.5           | -   | -    | V    |

|                 |                                      | $I_{OH} = 2 \text{ mA}$ | 1.25          | -   | -    | V    |

| Example 2       | : $V_{CC(I/O)}$ = 2.5 V $\pm$ 0.2 V  |                         |               |     |      |      |

| Input levels    | }                                    |                         |               |     |      |      |

| $V_{IL}$        | LOW-level input voltage              |                         | -             | -   | 0.7  | V    |

| $V_{IH}$        | HIGH-level input voltage             |                         | 1.7           | -   | -    | V    |

| Output leve     | els                                  |                         |               |     |      |      |

| $V_{OL}$        | LOW-level output voltage             | $I_{OL} = 100 \mu A$    | -             | -   | 0.15 | V    |

|                 |                                      | $I_{OL} = 2 \text{ mA}$ | -             | -   | 0.4  | V    |

| $V_{OH}$        | HIGH-level output voltage            | $I_{OH} = 100 \mu A$    | 2.15          | -   | -    | V    |

|                 |                                      | $I_{OH} = 2 \text{ mA}$ | 1.9           | -   | -    | V    |

| Example 3       | : $V_{CC(I/O)}$ = 3.3 V $\pm$ 0.3 V  |                         |               |     |      |      |

| Input levels    | 3                                    |                         |               |     |      |      |

| $V_{IL}$        | LOW-level input voltage              |                         | -             | -   | 0.9  | V    |

| $V_{IH}$        | HIGH-level input voltage             |                         | 2.15          | -   | -    | V    |

| Output leve     | els                                  |                         |               |     |      |      |

| $V_{OL}$        | LOW-level output voltage             | $I_{OL} = 100 \mu A$    | -             | -   | 0.15 | V    |

|                 |                                      | $I_{OL} = 2 \text{ mA}$ | -             | -   | 0.4  | V    |

| V <sub>OH</sub> | HIGH-level output voltage            | $I_{OH} = 100 \mu A$    | 2.85          | -   | -    | V    |

|                 |                                      | $I_{OH} = 2 \text{ mA}$ | 2.6           | -   | -    | V    |

<sup>[1]</sup> If  $V_{CC(I/O)} \ge V_{(VREG3V3)}$ , then the leakage current will be higher than the specified value.

Table 13. Static characteristics: analog I/O pins DP and DM

$V_{CC/5VO} = 4.0 \text{ V}$  to 5.5 V or  $V_{(VREG3V3)} = 3.0 \text{ V}$  to 3.6 V;  $V_{GND} = 0 \text{ V}$ ;  $T_{amb} = -40 ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; unless otherwise specified.

| *CC(5V0) = ***  | V to old to V V (VREG3V        | $3) = 3.3 \text{ to 3.3 t}, \text{ t}_{\text{GND}} = 3 \text{ t}, $ | amb — 10 C to 100 | o, arnooc | ouror moo op | oomoa. |

|-----------------|--------------------------------|---------------------------------------------------------------------|-------------------|-----------|--------------|--------|

| Symbol          | Parameter                      | Conditions                                                          | Min               | Тур       | Max          | Unit   |

| Input levels    |                                |                                                                     |                   |           |              |        |

| Differential re | eceiver                        |                                                                     |                   |           |              |        |

| V <sub>DI</sub> | differential input sensitivity | $ V_{I(DP)} - V_{I(DM)}  \\$                                        | 0.2               | -         | -            | V      |

ISP1102\_6 © ST-NXP Wireless 2009. All rights reserved. **Product data sheet**

#### **Advanced USB transceiver**

Table 13. Static characteristics: analog I/O pins DP and DM ...continued

$V_{\text{CC}(5V0)} = 4.0 \text{ V to } 5.5 \text{ V or } V_{\text{(VREG3V3)}} = 3.0 \text{ V to } 3.6 \text{ V}; V_{\text{GND}} = 0 \text{ V}; T_{\text{amb}} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}; unless otherwise specified.}$

| Symbol                    | Parameter                          | Conditions                                            |            | Min | Тур | Max | Unit      |

|---------------------------|------------------------------------|-------------------------------------------------------|------------|-----|-----|-----|-----------|

| $V_{CM}$                  | differential common mode voltage   | includes V <sub>DI</sub> range                        |            | 0.8 | -   | 2.5 | V         |

| Single-ended              | receiver                           |                                                       |            |     |     |     |           |

| V <sub>IL</sub>           | LOW-level input voltage            |                                                       |            | -   | -   | 0.8 | V         |

| $V_{IH}$                  | HIGH-level input voltage           |                                                       |            | 2.0 | -   | -   | V         |

| V <sub>hys</sub>          | hysteresis voltage                 |                                                       |            | 0.4 | -   | 0.7 | V         |

| Output levels             | 5                                  |                                                       |            |     |     |     |           |

| V <sub>OL</sub>           | LOW-level output voltage           | $R_L = 1.5 \text{ k}\Omega \text{ to } 3.6 \text{ V}$ |            | -   | -   | 0.3 | V         |

| V <sub>OH</sub>           | HIGH-level output voltage          | $R_L = 15 \text{ k}\Omega \text{ to GND}$             | <u>[1]</u> | 2.8 | -   | 3.6 | V         |

| Leakage curi              | rent                               |                                                       |            |     |     |     |           |

| I <sub>LZ</sub>           | off-state leakage current          |                                                       |            | -1  | -   | +1  | μΑ        |

| Capacitance               |                                    |                                                       |            |     |     |     |           |

| C <sub>in</sub>           | input capacitance                  | pin to GND                                            |            | -   | -   | 20  | pF        |

| Resistance                |                                    |                                                       |            |     |     |     |           |

| Z <sub>DRV</sub>          | driver output impedance            | steady-state drive                                    | [2]        | 34  | 39  | 44  | Ω         |

| Z <sub>INP</sub>          | input impedance                    |                                                       |            | 10  | -   | -   | $M\Omega$ |

| R <sub>swon(VPU3V3)</sub> | switch-on resistance on pin VPU3V3 |                                                       |            | -   | -   | 10  | Ω         |

| Termination               |                                    |                                                       |            |     |     |     |           |

| $V_{TERM}$                | termination voltage                | for upstream port pull-up (R <sub>pu</sub> )          | [3][4]     | 3.0 | -   | 3.6 | V         |

<sup>[1]</sup>  $V_{OH(min)} = V_{(VREG3V3)} - 0.2 V.$

## 12. Dynamic characteristics

Table 14. Dynamic characteristics: analog I/O pins DP and DM

$V_{CC(5V0)} = 4.0 \text{ V to } 5.5 \text{ V or } V_{(VREG3V3)} = 3.0 \text{ V to } 3.6 \text{ V}; V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{GND} = 0 \text{ V}; \text{ see } \frac{\text{Table 8}}{\text{C}} \text{ for valid voltage level combinations; } T_{amb} = -40 \text{ }^{\circ}\text{C to } +85 \text{ }^{\circ}\text{C}; \text{ unless otherwise specified.}$

| Symbol           | Parameter                                 | Conditions                                                                                               | Min | Тур | Max   | Unit |

|------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

| Driver chara     | cteristics                                |                                                                                                          |     |     |       |      |

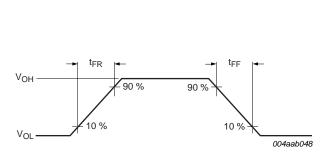

| t <sub>FR</sub>  | rise time                                 | $C_L$ = 50 pF to 125 pF;<br>10 % to 90 % of  V <sub>OH</sub> - V <sub>OL</sub>  ;<br>see <u>Figure 5</u> | 4   | -   | 20    | ns   |

| t <sub>FF</sub>  | fall time                                 | $C_L$ = 50 pF to 125 pF;<br>90 % to 10 % of  V <sub>OH</sub> - V <sub>OL</sub>  ;<br>see <u>Figure 5</u> | 4   | -   | 20    | ns   |

| FRFM             | differential rise time/fall time matching | excluding the first transition from idle state                                                           | 90  | -   | 111.1 | %    |

| V <sub>CRS</sub> | output signal crossover voltage           | excluding the first transition from idle state; see Figure 6                                             | 1.3 | -   | 2.0   | V    |

© ST-NXP Wireless 2009. All rights reserved.

<sup>[2]</sup> Includes external resistors of 33  $\Omega \pm 1$  % on both pins DP and DM.

<sup>[3]</sup> This voltage is available at pins VREG3V3 and VPU3V3.

<sup>[4]</sup> The minimum voltage is 2.7 V in suspend mode.

#### **Advanced USB transceiver**

Table 14. Dynamic characteristics: analog I/O pins DP and DM ...continued

$V_{CC(5V0)} = 4.0 \text{ V to } 5.5 \text{ V or } V_{(VREG3V3)} = 3.0 \text{ V to } 3.6 \text{ V}; V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{GND} = 0 \text{ V}; \text{ see } \frac{Table \ 8}{1000} \text{ For valid voltage level combinations; } T_{amb} = -40 \text{ °C to } +85 \text{ °C}; \text{ unless otherwise specified.}$

|                       |                                              | •                                                                        |     |     |     |      |

|-----------------------|----------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| Symbol                | Parameter                                    | Conditions                                                               | Min | Тур | Max | Unit |

| <b>Driver timir</b>   | ng                                           |                                                                          |     |     |     |      |

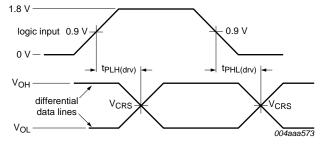

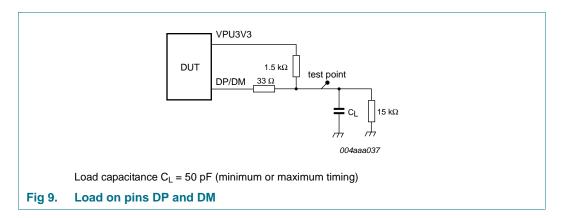

| t <sub>PLH(drv)</sub> | driver propagation delay (LOW to HIGH)       | VPO, VMO to DP, DM;<br>see <u>Figure 6</u> and <u>Figure 9</u>           | -   | -   | 18  | ns   |

| t <sub>PHL(drv)</sub> | driver propagation delay (HIGH to LOW)       | VPO, VMO to DP, DM;<br>see <u>Figure 6</u> and <u>Figure 9</u>           | -   | -   | 18  | ns   |

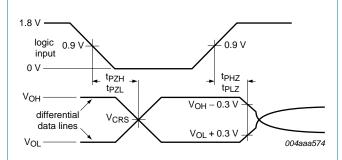

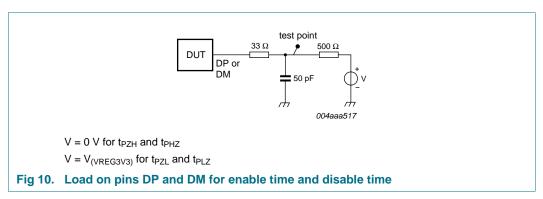

| t <sub>PHZ</sub>      | HIGH to OFF-state propagation delay          | OE to DP, DM; see Figure 7 and Figure 10                                 | -   | -   | 15  | ns   |

| t <sub>PLZ</sub>      | LOW to OFF-state propagation delay           | OE to DP, DM; see Figure 7 and Figure 10                                 | -   | -   | 15  | ns   |

| t <sub>PZH</sub>      | OFF-state to HIGH propagation delay          | OE to DP, DM; see Figure 7 and Figure 10                                 | -   | -   | 15  | ns   |

| t <sub>PZL</sub>      | OFF-state to LOW propagation delay           | OE to DP, DM; see Figure 7 and Figure 10                                 | -   | -   | 15  | ns   |

| Receiver til          | mings                                        |                                                                          |     |     |     |      |

| Differential r        | receiver                                     |                                                                          |     |     |     |      |

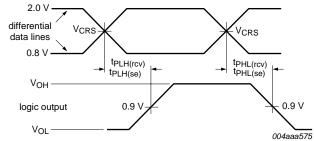

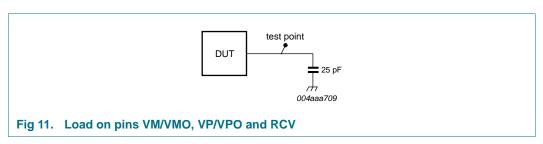

| t <sub>PLH(rcv)</sub> | receiver propagation delay (LOW to HIGH)     | DP, DM to RCV;<br>see <u>Figure 8</u> and <u>Figure 11</u>               | -   | -   | 15  | ns   |

| t <sub>PHL(rcv)</sub> | receiver propagation delay (HIGH to LOW)     | DP, DM to RCV;<br>see <u>Figure 8</u> and <u>Figure 11</u>               | -   | -   | 15  | ns   |

| Single-ende           | ed receiver                                  |                                                                          |     |     |     |      |

| t <sub>PLH(se)</sub>  | single-ended propagation delay (LOW to HIGH) | DP, DM to VP/VPO,<br>VM/VMO; see <u>Figure 8</u> and<br><u>Figure 11</u> | -   | -   | 18  | ns   |

| t <sub>PHL(se)</sub>  | single-ended propagation delay (HIGH to LOW) | DP, DM to VP/VPO,<br>VM/VMO; see <u>Figure 8</u> and<br><u>Figure 11</u> | -   | -   | 18  | ns   |

|                       |                                              |                                                                          |     |     |     |      |

<sup>[1]</sup> Characterized only, not tested. Limits guaranteed by design.

#### **Advanced USB transceiver**

Fig 5. Rise time and fall time

Fig 6. Timing of VPO and VMO to DP and DM

Fig 7. Timing of OE to DP and DM

Fig 8. Timing of DP and DM to RCV, VP/VPO and VM/VMO

#### **Advanced USB transceiver**

## 13. Test information

**Advanced USB transceiver**

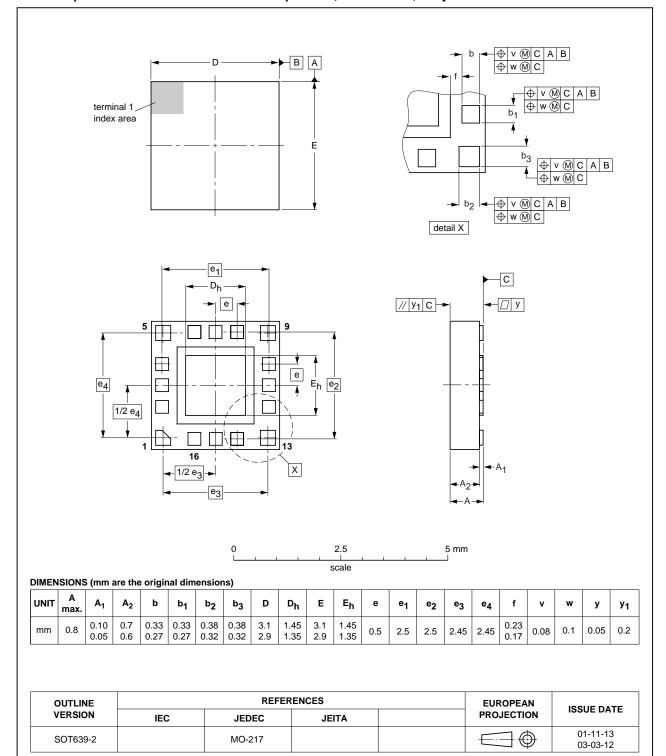

# 14. Package outline

HBCC16: plastic thermal enhanced bottom chip carrier; 16 terminals; body 3 x 3 x 0.65 mm

SOT639-2

Fig 12. Package outline SOT639-2 (HBCC16)

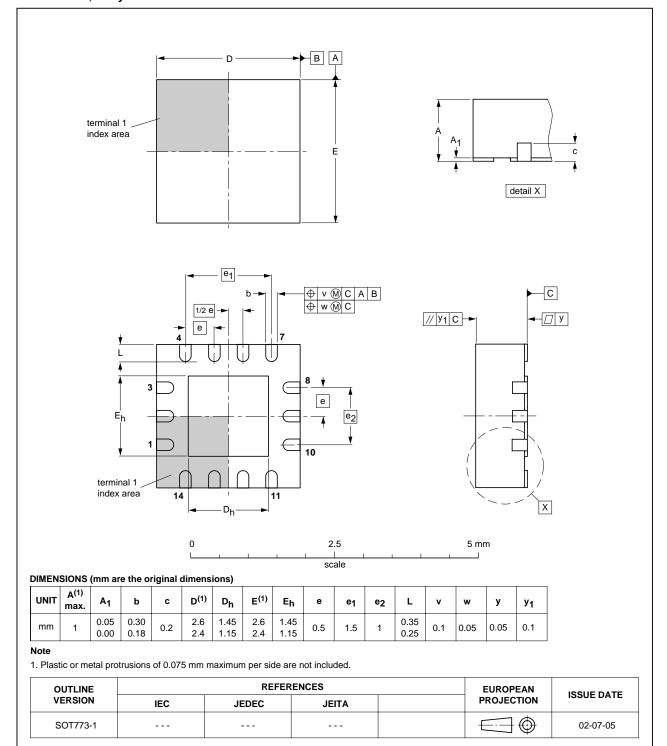

#### **Advanced USB transceiver**

HVQFN14: plastic thermal enhanced very thin quad flat package; no leads; 14 terminals; body 2.5 x 2.5 x 0.85 mm

SOT773-1

Fig 13. Package outline SOT773-1 (HVQFN14)

ig to: I dokage outline collino i (iivai ivi-

© ST-NXP Wireless 2009. All rights reserved.

**Advanced USB transceiver**

# 15. Packing information

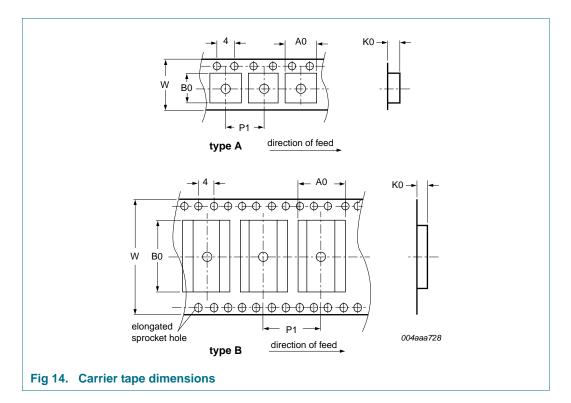

The ISP1102W (HBCC16 package) is delivered on a Type A carrier tape, see <u>Figure 14</u>. The tape dimensions are given in <u>Table 15</u>.

The reel diameter is 330 mm. The reel is made of polystyrene (PS) and is not designed for use in baking process.

The cumulative tolerance of 10 successive sprocket holes is  $\pm 0.02$  mm. The camber must not exceed 1 mm in 100 mm.

Table 15. Type A carrier tape dimensions for the ISP1102W

| Dimension | Value          | Unit |

|-----------|----------------|------|

| A0        | 3.3            | mm   |

| В0        | 3.3            | mm   |

| K0        | 1.1            | mm   |

| P1        | 8.0            | mm   |

| W         | $12.0 \pm 0.3$ | mm   |

# 16. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365* "Surface mount reflow soldering description".

ISP1102\_6 © ST-NXP Wireless 2009. All rights reserved.

#### Advanced USB transceiver

## 16.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

### 16.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- · Board specifications, including the board finish, solder masks and vias

- Package footprints, including solder thieves and orientation

- The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

## 16.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

#### 16.4 Reflow soldering

Key characteristics in reflow soldering are:

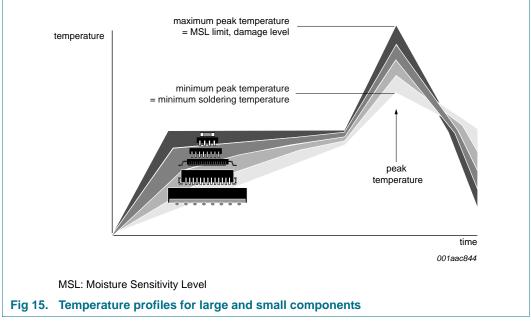

Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 15</u>) than a SnPb process, thus reducing the process window

#### **Advanced USB transceiver**

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 16 and 17

Table 16. SnPb eutectic process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |  |

|------------------------|---------------------------------|-------|--|--|

|                        | Volume (mm³)                    |       |  |  |

|                        | < 350                           | ≥ 350 |  |  |

| < 2.5                  | 235                             | 220   |  |  |

| ≥ 2.5                  | 220                             | 220   |  |  |

Table 17. Lead-free process (from J-STD-020C)

| Package thickness (mm) | ) Package reflow temperature (°C) |             |        |  |  |

|------------------------|-----------------------------------|-------------|--------|--|--|

|                        | Volume (mm <sup>3</sup> )         |             |        |  |  |

|                        | < 350                             | 350 to 2000 | > 2000 |  |  |

| < 1.6                  | 260                               | 260         | 260    |  |  |

| 1.6 to 2.5             | 260                               | 250         | 245    |  |  |

| > 2.5                  | 250                               | 245         | 245    |  |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 15.

ISP1102\_6

© ST-NXP Wireless 2009. All rights reserved.

#### **Advanced USB transceiver**

For further information on temperature profiles, refer to Application Note *AN10365* "Surface mount reflow soldering description".

## 17. Abbreviations

Table 18. Abbreviations

| Acronym | Description                             |

|---------|-----------------------------------------|

| ASIC    | Application-Specific Integrated Circuit |

| CMOS    | Complementary Metal-Oxide Semiconductor |

| ESD     | ElectroStatic Discharge                 |

| HBM     | Human Body Model                        |

| SE0     | Single-Ended Zero                       |

| USB     | Universal Serial Bus                    |

# 18. Revision history

Table 19. Revision history

| Document ID                    | Release date | Data sheet status                                   | Change notice | Supersedes                   |

|--------------------------------|--------------|-----------------------------------------------------|---------------|------------------------------|

| ISP1102_6                      | 20090119     | Product data sheet                                  | -             | ISP1102_5                    |

| Modifications:                 | •            | Semiconductors and NXP tmation": added Table note [ |               | Also updated the legal text. |

| ISP1102_5                      | 20071211     | Product data sheet                                  | -             | ISP1102_4                    |

| ISP1102_4                      | 20060703     | Product data sheet                                  | -             | ISP1102-03                   |

| ISP1102-03<br>(9397 750 11228) | 20030902     | Product data                                        | -             | ISP1102-02                   |

| ISP1102-02<br>(9397 750 10397) | 20030106     | Product data                                        | -             | ISP1102-01                   |

| ISP1102-01                     | 20000524     | Objective data                                      | -             | -                            |

## **Advanced USB transceiver**

## 19. Tables

| Table 1.  | Ordering information                             | .2 |

|-----------|--------------------------------------------------|----|

| Table 2.  | Pin description                                  |    |

| Table 3.  | Function selection                               |    |

| Table 4.  | Driving function using differential input data   |    |

|           | interface (pin $\overline{OE} = LOW$ )           | .5 |

| Table 5.  | Receiving function (pin $\overline{OE} = HIGH$ ) | .5 |

| Table 6.  | Pin states in sharing mode                       | .6 |

| Table 7.  | Power supply configuration overview              | .6 |

| Table 8.  | Power supply input options                       | .7 |

| Table 9.  | Limiting values                                  | .9 |

| Table 10. | Recommended operating conditions                 | .9 |

| Table 11. | Static characteristics: supply pins              | .9 |

| Table 12. | Static characteristics: digital pins             | 10 |

| Table 13. | Static characteristics: analog I/O pins DP and   |    |

|           | DM                                               | 11 |

| Table 14. | Dynamic characteristics: analog I/O pins DP      |    |

|           | and DM                                           | 12 |

| Table 15. | Type A carrier tape dimensions for the           |    |

|           | ISP1102W                                         | 18 |

| Table 16. | SnPb eutectic process (from J-STD-020C) 2        | 20 |

| Table 17. | Lead-free process (from J-STD-020C)2             | 20 |

| Table 18. | Abbreviations                                    | 21 |

| Table 19. | Revision history                                 | 21 |

|           |                                                  |    |

## Advanced USB transceiver

# 20. Figures

| Fig 1.  | Block diagram                              |

|---------|--------------------------------------------|

| Fig 2.  | Pin configuration HBCC16 (top view)3       |

| Fig 3.  | Pin configuration HVQFN14 (top view) 3     |

| Fig 4.  | Human body ESD test model8                 |

| Fig 5.  | Rise time and fall time                    |

| Fig 6.  | Timing of VPO and VMO to DP and DM 14      |

| Fig 7.  | Timing of OE to DP and DM14                |

| Fig 8.  | Timing of DP and DM to RCV, VP/VPO and     |

|         | VM/VMO                                     |

| Fig 9.  | Load on pins DP and DM15                   |

| Fig 10. | Load on pins DP and DM for enable time and |

|         | disable time                               |

| Fig 11. | Load on pins VM/VMO, VP/VPO and RCV 15     |

| Fig 12. | Package outline SOT639-2 (HBCC16) 16       |

|         | Package outline SOT773-1 (HVQFN14) 17      |

| Fig 14. | Carrier tape dimensions18                  |

| Fig 15. | Temperature profiles for large and small   |

|         | components                                 |

#### **Advanced USB transceiver**

## 21. Contents

| 1    | General description                |

|------|------------------------------------|

| 2    | Features                           |

| 3    | Applications                       |

| 4    | Ordering information               |

| 5    | Block diagram 2                    |

| 6    | Pinning information 3              |

| 6.1  | Pinning                            |

| 6.2  | Pin description                    |

| 7    | Functional description 5           |

| 7.1  | Function selection 5               |

| 7.2  | Operating functions 5              |

| 7.3  | Power supply configurations        |

| 7.4  | Power supply input options         |

| 8    | ElectroStatic Discharge (ESD) 8    |

| 8.1  | ESD protection                     |

| 8.2  | ESD test conditions 8              |

| 9    | Limiting values9                   |

| 10   | Recommended operating conditions 9 |

| 11   | Static characteristics 9           |

| 12   | Dynamic characteristics            |

| 13   | Test information                   |

| 14   | Package outline                    |

| 15   | Packing information 18             |

| 16   | Soldering of SMD packages          |

| 16.1 | Introduction to soldering          |

| 16.2 | Wave and reflow soldering 19       |

| 16.3 | Wave soldering19                   |

| 16.4 | Reflow soldering                   |

| 17   | Abbreviations                      |

| 18   | Revision history 21                |

| 19   | Tables                             |

| 20   | Figures                            |

| 21   | Contents                           |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© ST-NXP Wireless 2009.

All rights reserved.

For more information, please visit: http://www.stnwireless.com

Date of release: 19 January 2009 Document identifier: ISP1102\_6

#### **Advanced USB transceiver**

#### Please Read Carefully:

Information in this document is provided solely in connection with ST-NXP products. ST-NXP Wireless NV and its subsidiaries ("ST-NXP") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST-NXP products are sold pursuant to ST-NXP's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST-NXP products and services described herein, and ST-NXP assumes no liability whatsoever relating to the choice, selection or use of the ST-NXP products and services described herein. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST-NXP for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST-NXP'S TERMS AND CONDITIONS OF SALE ST-NXP DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST-NXP PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST-NXP REPRESENTATIVE, ST-NXP PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST-NXP PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST-NXP products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST-NXP for the ST-NXP product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST-NXP.

ST-NXP and the ST-NXP logo are trademarks or registered trademarks of ST-NXP in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST-NXP logo is a registered trademark of ST-NXP Wireless. All other names are the property of their respective owners.

© 2009 ST-NXP Wireless - All rights reserved

ST-NXP Wireless group of companies

Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - India - Italy - Japan - Korea - Malaysia - Mexico - Netherlands - Singapore - Sweden - Switzerland - Taiwan - United Kingdom - United States of America

www.stnwireless.com

ISP1102\_6 © ST-NXP Wireless 2009. All rights reserved.