#### • Memory interfaces

- 32-bit DRAM Controller with support for LPDDR2/DDR3/DDR3L Data rate of up to 1066 MT/s at 533 MHz clock frequency with ECC (SEC-DED-TED) triple error detection support for subregion

- QuadSPI supporting Execute-In-Place (XIP)

- Boot flash fault detection and correction using two-dimensional parity.

- Triple fault detection and single fault correction scheme for external DDR-RAM including address/page fault detection.

- Video input interfaces, Image processing, graphics processing, display

- Display Control Unit (2D-ACE) with 24-bit RGB, GPU frame buffer decoding

- GPU GC3000 with frame buffer compression

- 2x VIU (Video interface unit) for camera input

- 2x MIPICSI2 with four lanes for camera input (support 1080 pixel @ 30 fps)

- Image signal processor (ISP), supporting 2x1 or 1x2 megapixel @ 30 fps and 4x2 megapixel for subset of functions (exposure control, gamma correction)

- 2x APEX2-CL Image cognition processor. APEX-642CL comprises two Array Processing Unit (APU) cores

configurable as single SIMD engine with 64 16-bit Computational Units (CU), or configurable as two core MIMD

engines with 32 16-bit CUs each.

- CUs are comprised of four Functional Units: 16-bit Multiplier, Load Store Unit, ALU, and Shifter

- JPEG video decoder (8/12-bit)

- H.264 video decoder (8/10/12-bit), High-intra and constrained baseline formats

- H.264 video encode (8/10/12-bit), High-intra only

- Fast DMA for data transfers between DRAM and System RAM with CRC

- Human-Machine Interface (HMI)

- GPIO pins with interrupt support, DMA request capability, digital glitch filter

- Configurable slew rate and drive strength on all output pins

- System RAM

- 4 MB On-Chip System RAM with ECC

# **Table of Contents**

| 1 | Block | k diagrar | n            |                                    | 5  | 6.3 | Memor  | ry interfaces                               | 25 |

|---|-------|-----------|--------------|------------------------------------|----|-----|--------|---------------------------------------------|----|

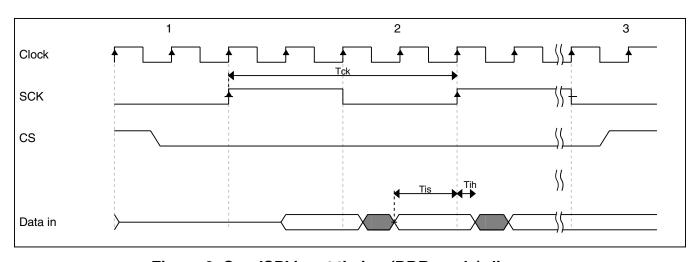

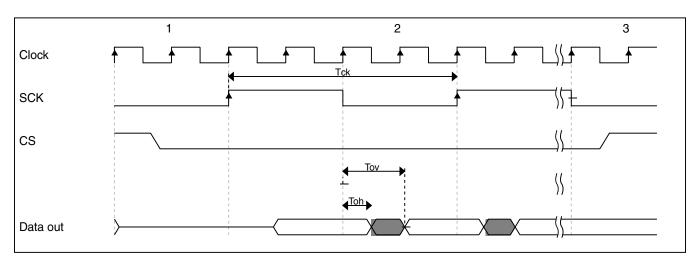

| 2 | Fami  | ly compa  | arison       |                                    | 5  |     | 6.3.1  | QuadSPI AC specifications                   | 25 |

|   | 2.1   | Feature   | Set          |                                    | 5  | 6.4 | DDR S  | SDRAM Specific Parameters (DDR3, DDR3L, and |    |

| 3 | Orde  | ring part | s            |                                    | 8  |     | LPDD   | R2)                                         | 30 |

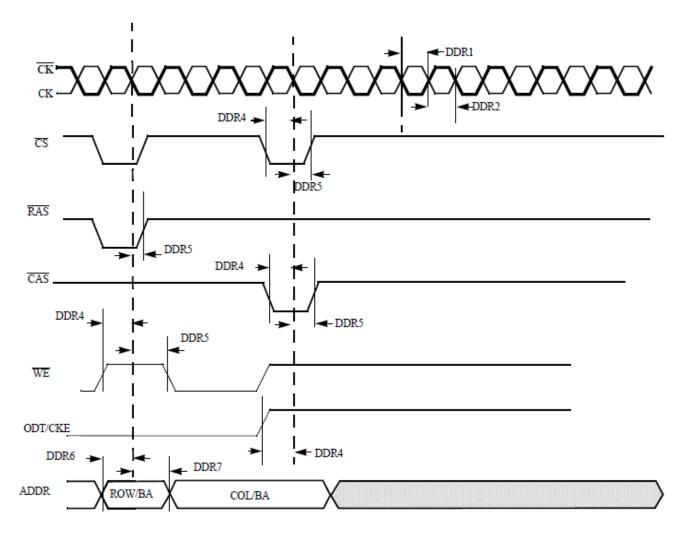

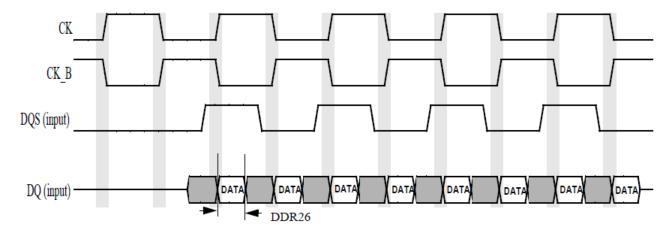

|   | 3.1   | Orderin   | ng informat  | ion                                | 8  |     | 6.4.1  | DDR3 and DDR3L timing parameters            | 30 |

| 4 | Gene  | ral       |              |                                    | 8  |     | 6.4.2  | DDR3 and DDR3L read cycle                   | 32 |

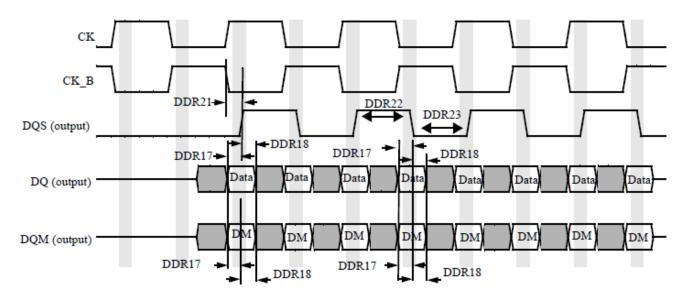

|   | 4.1   | Operat    | ion above n  | naximum operating conditions       | 8  |     | 6.4.3  | DDR3 and DDR3L write cycle                  | 33 |

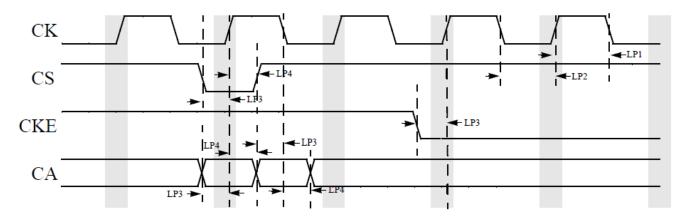

|   | 4.2   | Recom     | mended op    | erating conditions                 | 9  |     | 6.4.4  | LPDDR2 timing parameter                     | 34 |

|   | 4.3   | Power     | Manageme     | nt Controller (PMC) electrical     |    |     | 6.4.5  | LPDDR2 read cycle                           | 36 |

|   |       | specifi   | cations      |                                    | 10 |     | 6.4.6  | LPDDR2 write cycle                          | 36 |

|   | 4.4   | Power     | consumptio   | on                                 | 11 | 6.5 | Comm   | nunication modules                          | 38 |

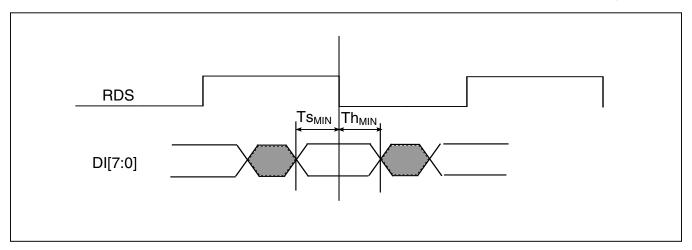

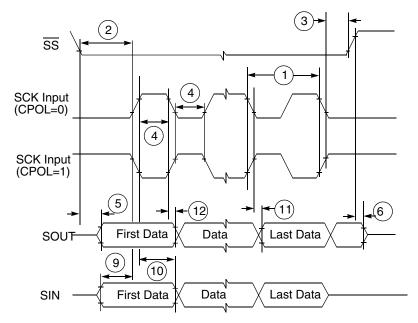

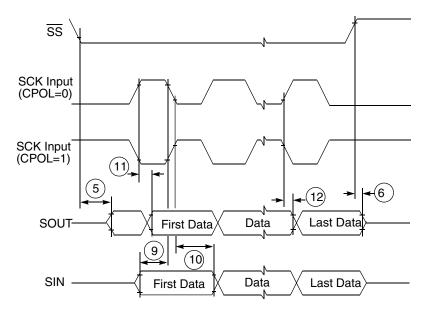

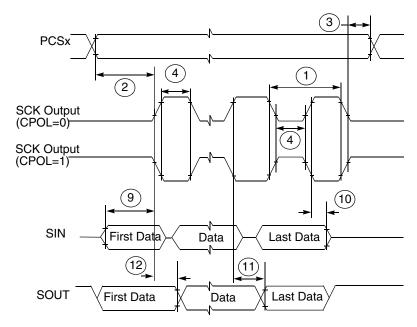

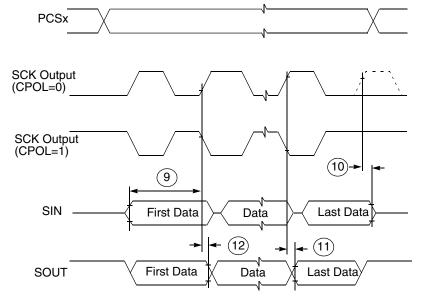

|   | 4.5   | Electro   | static disch | arge (ESD) specifications          | 13 |     | 6.5.1  | DSPI timing                                 | 38 |

|   | 4.6   | Electro   | magnetic C   | Compatibility (EMC) specifications | 13 |     | 6.5.2  | Ultra High Speed SD/SDIO/MMC Host Interface |    |

|   | 4.7   | PCB ro    | outing guide | elines                             | 13 |     |        | (uSDHC)                                     | 42 |

| 5 | I/O p | arametei  | 's           |                                    | 15 |     |        | 6.5.2.1 SDR mode timing specifications      | 42 |

|   | 5.1   | Genera    | l purpose L  | O parameters                       | 15 |     |        | 6.5.2.2 DDR mode timing specifications      | 43 |

|   |       | 5.1.1     | GPIO spe     | ed at various voltage levels       | 15 |     | 6.5.3  | LFAST electrical characteristics            | 46 |

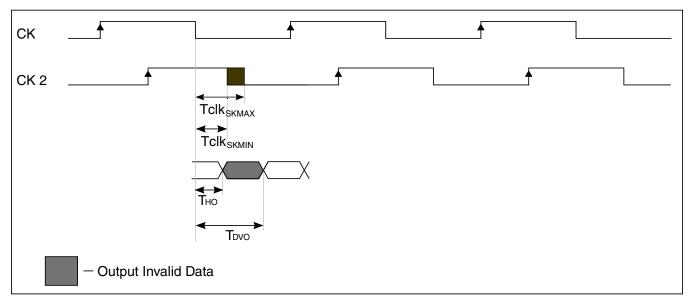

|   |       | 5.1.2     | DC electr    | ical specifications                | 16 |     |        | 6.5.3.1 LFAST interface timing diagrams     | 46 |

|   | 5.2   | DDR p     | ads          |                                    | 17 |     |        | 6.5.3.2 LFAST Interface electrical          |    |

|   |       | 5.2.1     | Boot Con     | figuration Pins Specification      | 17 |     |        | characteristics                             | 47 |

|   |       | 5.2.2     | DDR3 mo      | ode                                | 17 |     | 6.5.4  | FlexRay                                     | 48 |

|   |       |           | 5.2.2.1      | DDR3 mode DC electrical            |    |     |        | 6.5.4.1 FlexRay timing parameters           | 48 |

|   |       |           |              | specifications                     | 17 |     |        | 6.5.4.2 TxEN                                | 48 |

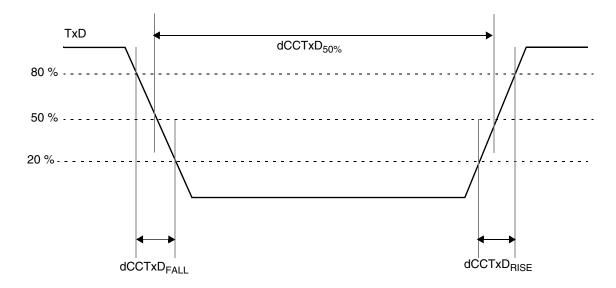

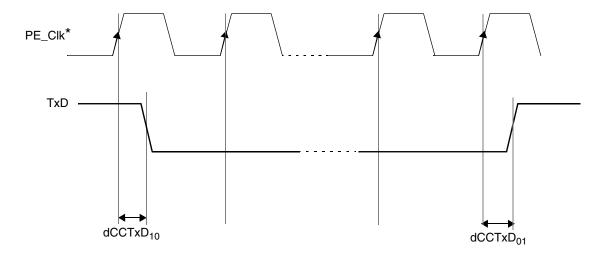

|   |       | 5.2.3     | DDR3L n      | node                               | 18 |     |        | 6.5.4.3 TxD                                 | 49 |

|   |       |           | 5.2.3.1      | DDR3L mode DC electrical           |    |     |        | 6.5.4.4 RxD                                 | 50 |

|   |       |           |              | specifications                     | 18 |     | 6.5.5  | Ethernet Controller (ENET) Parameters       | 51 |

|   |       | 5.2.4     | LPDDR2       | mode                               | 18 |     |        | 6.5.5.1 Ethernet Switching Specifications   | 51 |

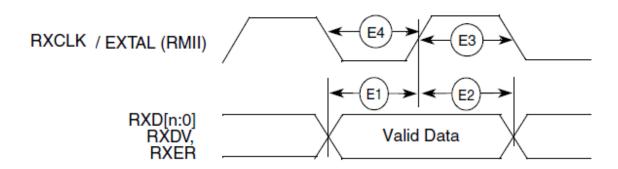

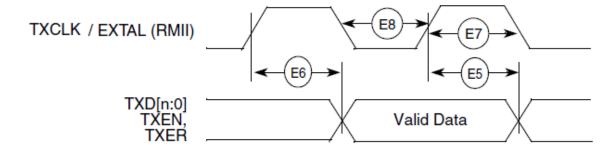

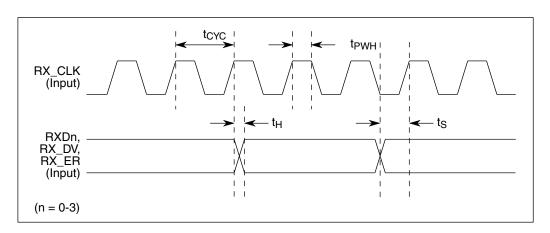

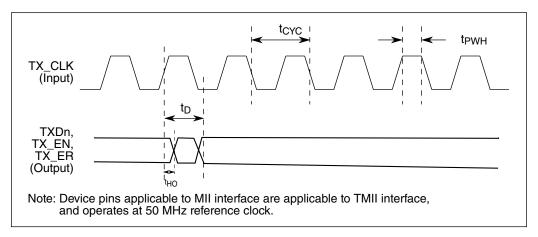

|   |       |           | 5.2.4.1      | LPDDR2 mode DC electrical          |    |     |        | 6.5.5.2 Receive and Transmit signal timing  |    |

|   |       |           |              | specifications                     | 18 |     |        | specifications for RMII interfaces          | 51 |

| 6 | Perip | heral op  | erating requ | irements and behaviors             | 19 |     |        | 6.5.5.3 Receive and Transmit signal timing  |    |

|   | 6.1   | Analog    | modules      |                                    | 19 |     |        | specifications for MII interfaces           | 52 |

|   |       | 6.1.1     | ADC elec     | trical specifications              | 19 |     |        | 6.5.5.4 Receive and Transmit signal timing  |    |

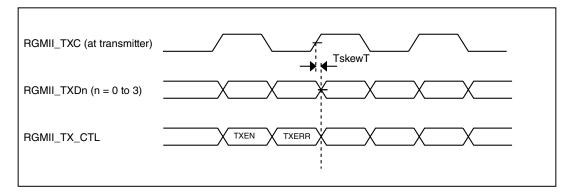

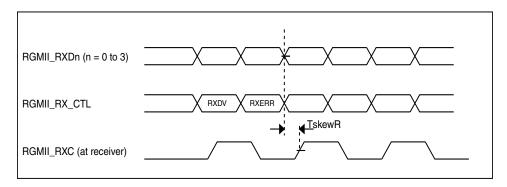

|   |       |           | 6.1.1.1      | Input equivalent circuit           | 20 |     |        | specifications for RGMII interfaces         | 53 |

|   |       | 6.1.2     | Thermal l    | Monitoring Unit (TMU)              | 22 |     |        | 6.5.5.5 MII/RMII Serial Management channel  | el |

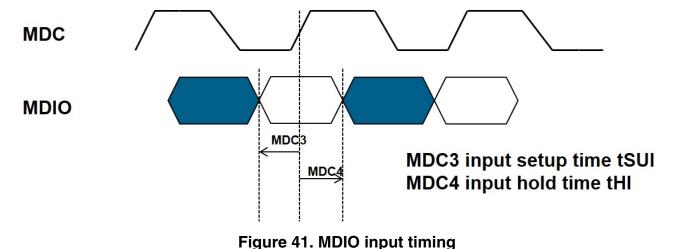

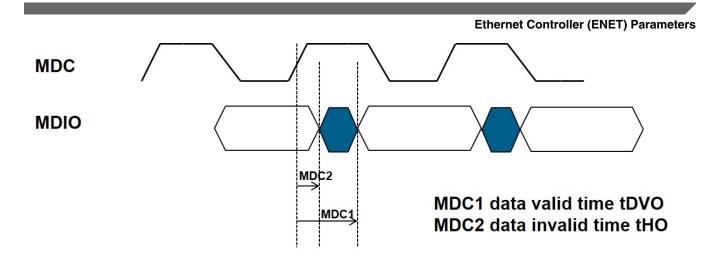

|   | 6.2   | Clocks    | and PLL in   | nterfaces modules                  | 22 |     |        | timing (MDC/MDIO)                           | 54 |

|   |       | 6.2.1     | Main osci    | llator electrical characteristics  | 22 |     | 6.5.6  | PCI Express specifications                  | 55 |

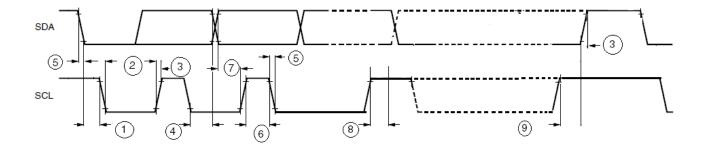

|   |       | 6.2.2     | 48 MHz I     | FIRC electrical characteristics    | 23 |     | 6.5.7  | IIC timing                                  | 56 |

|   |       | 6.2.3     | PLL elect    | rical specifications               | 23 |     | 6.5.8  | LINFlex timing                              | 58 |

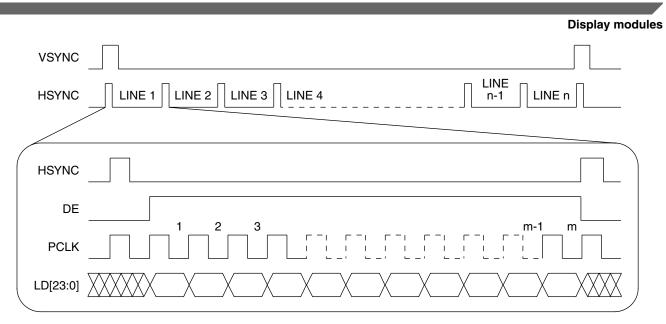

|   |       | 6.2.4     | DFS elect    | rical specifications               | 24 | 6.6 | Displa | y modules                                   | 58 |

|   |       | 6.2.5     | LFAST P      | LL Electrical Specifications       | 24 |     | 6.6.1  | Display Control Unit (2D-ACE) Parameters    | 58 |

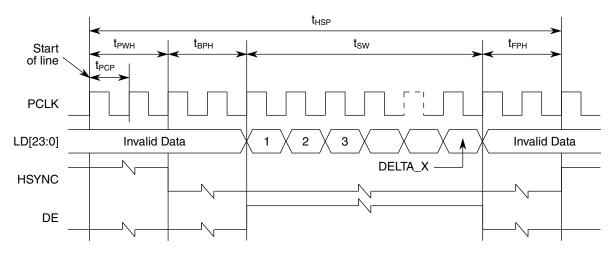

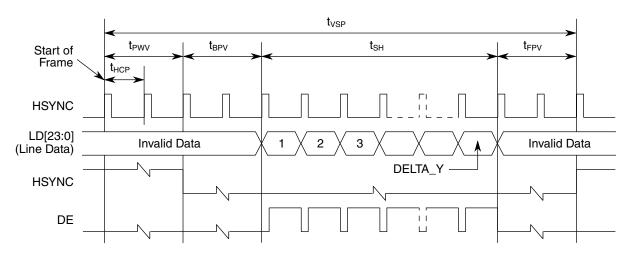

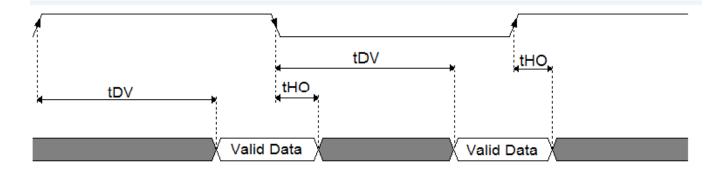

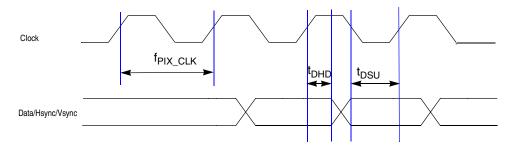

|     |       | 6.6.1.1       | Interface to TFT panels58                  |    | 6.10  | External interrupt timing (IRQ pin)     | 71 |

|-----|-------|---------------|--------------------------------------------|----|-------|-----------------------------------------|----|

|     |       | 6.6.1.2       | Interface to TFT LCD Panels—Pixel          | 7  | Therr | nal attributes                          | 72 |

|     |       |               | Level Timings59                            |    | 7.1   | Thermal attributes                      | 72 |

|     |       | 6.6.1.3       | Interface to TFT LCD panels—access         | 8  | Dime  | nsions                                  | 72 |

|     |       |               | level60                                    |    | 8.1   | Obtaining package dimensions            | 72 |

|     | 6.6.2 | Video inpu    | t unit (VIU) timing specifications61       | 9  | Pinou | ts                                      | 73 |

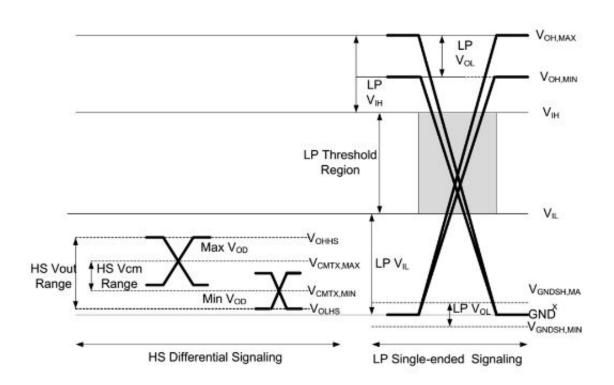

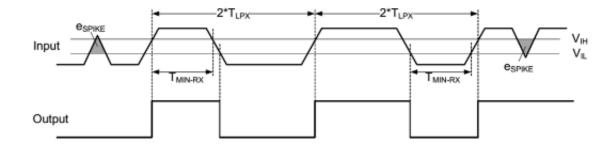

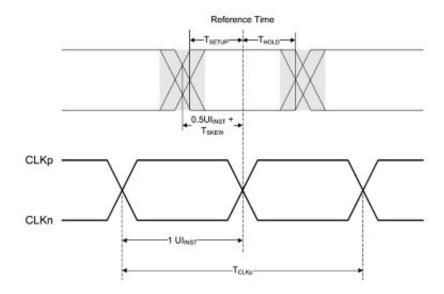

|     | 6.6.3 | MIPICSI2      | D-PHY electrical and timing parameters. 62 |    | 9.1   | Package pinouts and signal descriptions | 73 |

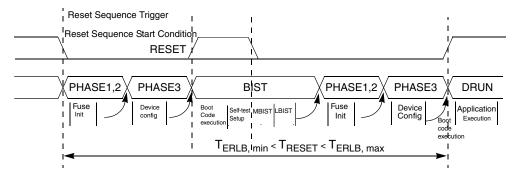

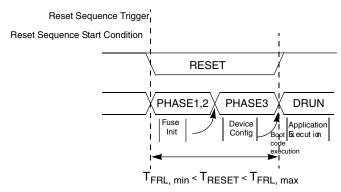

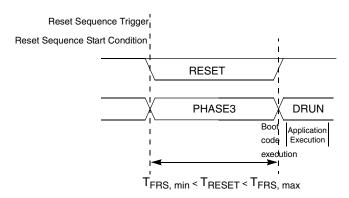

|     |       | 6.6.3.6       | NOTICE OF DISCLAIMER65                     | 10 | Reset | sequence                                | 73 |

| 6.7 | Debug | specification | ns66                                       |    | 10.1  | Reset sequence duration                 | 73 |

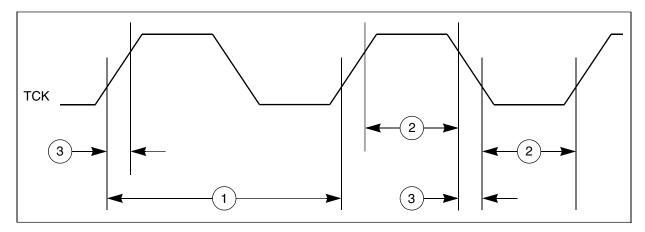

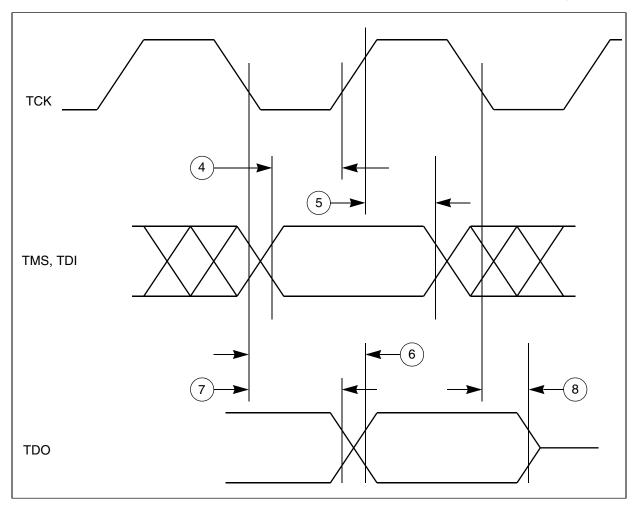

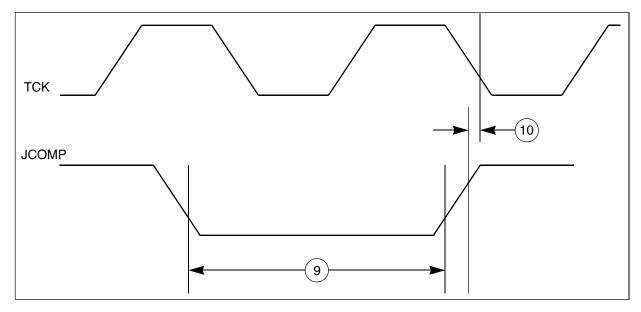

|     | 6.7.1 | JTAG inte     | rface timing66                             |    | 10.2  | Boot performance matrix                 | 73 |

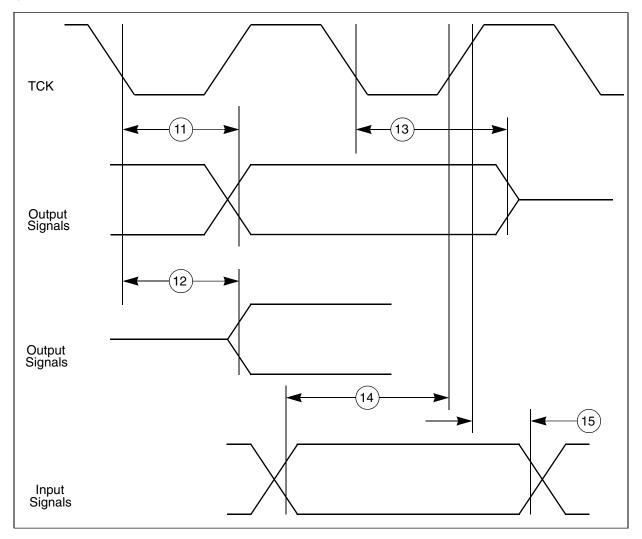

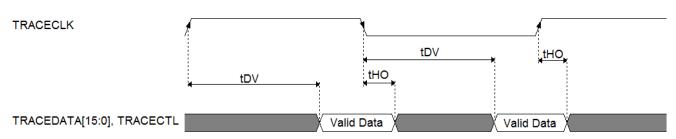

|     | 6.7.2 | Debug trac    | e timing specifications70                  |    | 10.3  | Reset sequence description              | 74 |

| 5.8 | Wakeu | p Unit (WK    | PU) AC specifications71                    | 11 | Powe  | r sequencing requirements               | 77 |

| 5.9 | RESET | pin glitch f  | ilter specifications71                     | 12 | Revis | ion history                             | 78 |

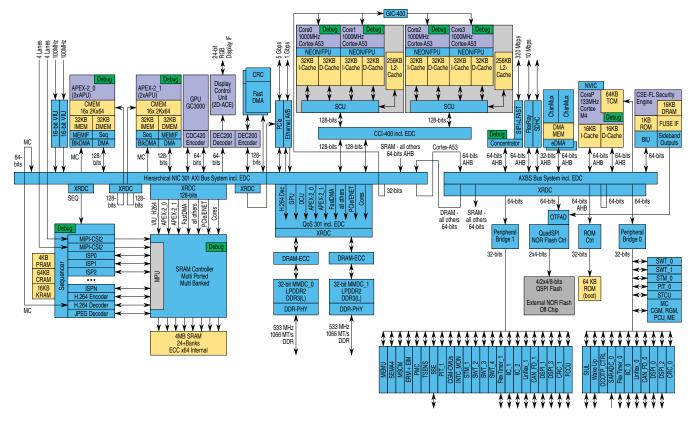

# 1 Block diagram

Figure 1. Block diagram

# 2 Family comparison

## 2.1 Feature Set

This family of devices supports the following features:

Table 1. Feature Set

| Feature             | S32V234                                                                                                                                                                                                                                   | S32V232                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| ARM Cortex-A53 Core | <ul> <li>Up to 1000 MHz Quad ARM Cortex-A53</li> <li>32 KB/32 KB I-/D- L1 Cache</li> <li>NEON MPE co-processor</li> <li>Dual precision FPU</li> <li>256 KB L2 Cache per cluster</li> <li>MMU</li> <li>GIC interrupt controller</li> </ul> | <ul> <li>Up to 800 MHz Dual ARM Cortex-A53<br/>(single cluster)</li> <li>Rest all features same as S32V234</li> </ul> |

Table continues on the next page...

#### Family comparison

Table 1. Feature Set (continued)

| Feature                                          | S32V234                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | S32V232           |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                  | <ul> <li>ECC/parity error support for its<br/>memories</li> <li>Generic timers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| ARM Cortex-M4 Core                               | <ul> <li>Up to 133 MHz</li> <li>16 KB/16 KB I-/D- L1 Cache</li> <li>32+32 KB tightly coupled memory<br/>(TCM)</li> <li>ECC/parity support for its memories</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Same as S32V234   |

| Clocks                                           | <ul><li>Phase Locked Loops (PLLs)</li><li>1 external crystal ocillators (FXOSC)</li><li>1 FIRC</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Same as S32V234   |

| System, protection and power management features | <ul> <li>Flexible run modes to consume lower power based on application needs.</li> <li>Peripheral clock enable registers can disable clocks to unused modules, thereby reducing currents</li> <li>Low and high voltage warning and detect</li> <li>Hardware CRC module to support fast cyclic redundancy checks (CRC)</li> <li>120-bit unique chip identifier</li> <li>Hardware watchdog</li> <li>Safe eDMA controller with 32 channels (with DMAMUX)</li> <li>Extended Resource Domain Controller</li> </ul>                                                                                                                                                                                                                                                                                                               | • Same as S32V234 |

| Safety concept                                   | <ul> <li>ISO 26262, ASIL level target as per safety concept</li> <li>Measures detecting faults in memory and logic</li> <li>Measures to detect single point and latent faults</li> <li>Quantitative out of context analysis of functional safety (FMEDA) tailored to application specifics</li> <li>Safety manual and FMEDA report available</li> <li>Boot flash authentication and fault detection and correction using AES-128 and two-dimensional parity.</li> <li>Double and triple fault detection and single fault correction scheme for external DDR-RAM including address/ page fault detection.</li> <li>Fault encapsulation by hardware for redundant executed application software on multiple core cluster.</li> <li>Structural software based self test routines providing high diagnostic coverage.</li> </ul> | • Same as S32V234 |

| Debug                                            | <ul> <li>Standard JTAG</li> <li>16-bit Trace port, Serial Wire Output<br/>port</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Same as S32V234   |

| Timers                                           | General purpose timers (FTM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Same as S32V234   |

Table continues on the next page...

# Table 1. Feature Set (continued)

| Feature                                                                | S32V234                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S32V232                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                        | <ul> <li>Two Periodic Interrupt Timer (PIT)</li> <li>IEEE 1588 Timers (part of Ethernet<br/>Subsystem)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |

| Communications                                                         | <ul> <li>UART(w/ LIN2.1I)</li> <li>Serial peripheral interface (SPI)</li> <li>I2C blocks</li> <li>PCI express 2.0 with endpoint and root complex support</li> <li>LFAST serial link</li> <li>1 GBit Ethernet with PTP IEEE 1588</li> <li>FD-CAN</li> <li>Flexray Dual Channel, Version 2.1 RevA</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>UART(w/ LIN2.1l)</li> <li>Serial peripheral interface (SPI)</li> <li>I2C blocks</li> <li>LFAST serial link</li> <li>1 GBit Ethernet with PTP IEEE 1588</li> <li>FD-CAN</li> <li>Flexray Dual Channel, Version 2.1<br/>RevA</li> </ul> |

| Memory Interfaces                                                      | 32-bit DRAM Controller with support for LPDDR2/DDR3/DDR3L - Data rate of up to 1066 MT/s at 533 MHz clock frequency with ECC (SEC-DED-TED) single error correction, double error detection, and triple error detection support for subregion     Dual QuadSPI supporting Execute-In-Place (XIP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Same as S32V234                                                                                                                                                                                                                                |

| Video input interfaces, Image processing, graphics processing, display | <ul> <li>Display Control Unit (2D-ACE) with 24-bit RGB, GPU framebuffer decoding</li> <li>GPU GC3000 with frame buffer compression</li> <li>2x Video interface unit (VIU) for camera input</li> <li>2x CSI with 4 lanes for camera input (support 1080p @ 30fps)</li> <li>Image signal processor (ISP), supporting 2x1 or 1x2 MPixel @ 30fps and 4x1 MPixel for subset of functions (exposure control, gamma correction)</li> <li>2x APEX2-CL Image cognition processor (dual 32-bit array processor)</li> <li>JPEG video decoder (8/10/12-bit)</li> <li>H.264 video decoder (8/10/12-bit), Highintra and constrained baseline formats</li> <li>H.264 video encoder (8/10/12-bit), I-frames only</li> <li>Safe Fast DMA for data transfers between DRAM and System RAM with CRC</li> </ul> | Same as S32V234                                                                                                                                                                                                                                |

| Analog                                                                 | 1x 12-bit SAR ADC with self-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Same as S32V234                                                                                                                                                                                                                                |

| Human-Machine Interface<br>(HMI)                                       | <ul> <li>SIUL, GPIO pins with interrupt support,<br/>DMA request capability, digital glitch<br/>filter.</li> <li>Configurable slew rate and drive<br/>strength on all output pins</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Same as S32V234                                                                                                                                                                                                                                |

| System RAM                                                             | 4 MB On-Chip System RAM with ECC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 MB On-Chip System RAM with ECC                                                                                                                                                                                                               |

| Power Consumption                                                      | Run modes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Same as S32V234                                                                                                                                                                                                                                |

#### **Ordering parts**

Table 1. Feature Set

| Feature | S32V234                                                                                                          | S32V232 |

|---------|------------------------------------------------------------------------------------------------------------------|---------|

|         | <ul> <li>Frequency scaling and clock<br/>gating for processing blocks and<br/>peripherals in run mode</li> </ul> |         |

# 3 Ordering parts

## 3.1 Ordering information

The orderable part numbers of this chip are in the table below:

**Table 2. Ordering information**

| Part number     | ISP | GPU | CSE | Low power (leakage based) | No. of cores | Frequency |

|-----------------|-----|-----|-----|---------------------------|--------------|-----------|

| FS32V234CMN1VUB | Yes | Yes | No  | No                        | 4            | 1 GHz     |

| FS32V234CON1VUB | Yes | Yes | Yes | No                        | 4            | 1 GHz     |

| FS32V234BMN1VUB | Yes | Yes | No  | No                        | 4            | 800 MHz   |

| FS32V234BJN1VUB | Yes | No  | No  | Yes                       | 4            | 800 MHz   |

| FS32V232BMN1VUB | Yes | Yes | No  | No                        | 2            | 800 MHz   |

| FS32V234BLN1VUB | Yes | No  | Yes | Yes                       | 4            | 800 MHz   |

| FS32V234CKN1VUB | Yes | No  | Yes | No                        | 4            | 1 GHz     |

## 4 General

# 4.1 Operation above maximum operating conditions

Table 3. Operation above maximum operating conditions

| 1.8 V DGO Voltage Domain        |        |            |            |  |  |  |  |

|---------------------------------|--------|------------|------------|--|--|--|--|

| Electrical Specifications       | Value  | Conditions | Junct Temp |  |  |  |  |

| Absolute Maximum Supply Voltage | 3.0 V  | < 60 s     | 25 °C      |  |  |  |  |

| Absolute Maximum Supply Voltage | 2.3 V  | < 10 hr    | 25 °C      |  |  |  |  |

| Operating Max Supply<br>Voltage | 1.98 V | _          | _          |  |  |  |  |

Table continues on the next page...

Table 3. Operation above maximum operating conditions (continued)

| Core Voltage Domain             |        |            |            |

|---------------------------------|--------|------------|------------|

| Electrical Specifications       | Value  | Conditions | Junct Temp |

| Absolute Maximum Supply Voltage | 1.29 V | < 60 s     | 25 °C      |

| Absolute Maximum Supply Voltage | 1.1 V  | < 10 hr    | 25 °C      |

| Operating Max Supply<br>Voltage | 1.05 V | _          | _          |

| 3.3 V DGO Voltage Domain        | 1      | '          |            |

| Electrical Specifications       | Value  | Conditions | Junct Temp |

| Absolute Maximum Supply Voltage | 4.95 V | < 60 s     | 25 °C      |

| Absolute Maximum Supply Voltage | 4.29 V | < 10 hr    | 25 °C      |

| Operating Max Supply<br>Voltage | 3.6 V  | _          | _          |

# 4.2 Recommended operating conditions

Table 4. Recommended operating conditions

| Symbol                                                      | Parameter                                        | Conditions | Min   | Max   | Unit |

|-------------------------------------------------------------|--------------------------------------------------|------------|-------|-------|------|

| V <sub>DD_GPIO0</sub>                                       | 3.3 V I/O segment GPIO0 supply voltage           | _          | 3.15  | 3.6   | V    |

| V <sub>DD_GPIO<n=1,2></n=1,2></sub>                         | 1.8 V input/output supply voltage                | _          | 1.71  | 1.95  | V    |

| V <sub>DD_HV_IO_VIU0</sub>                                  | 3.3 V input/output supply voltage                | _          | 3.15  | 3.6   | V    |

| V <sub>DD_HV_IO_VIU1</sub>                                  |                                                  |            |       |       |      |

| V <sub>DD_HV_IO_DIS</sub>                                   |                                                  |            |       |       |      |

| V <sub>DD_HV_IO_FLA</sub>                                   |                                                  |            |       |       |      |

| V <sub>DD_HV_IO_ETH</sub>                                   | 1.5 V I/O supply voltage                         | _          | 1.425 | 1.575 | V    |

|                                                             | 1.8 V I/O supply voltage                         | _          | 1.71  | 1.95  | V    |

|                                                             | 2.5 V I/O supply voltage                         | _          | 2.375 | 2.625 | V    |

|                                                             | 3.3 V I/O supply voltage                         | _          | 3.15  | 3.6   | V    |

| V <sub>SS</sub>                                             | Common ground voltage <sup>1</sup>               | _          | 0     | 0     | V    |

| VDD_LV_CORE_SOC, VDD_LV_CORE_ARM, VDD_LV_CORE_GPU           | 1.0 V core domain supply voltage <sup>2</sup>    | _          | 0.95  | 1.05  | V    |

| V <sub>DD_HV_CSI</sub>                                      | 1.8 V supply voltage (for MIPICSI2 D PHY)        | _          | 1.71  | 1.95  | V    |

| V <sub>DD_LV_CSI</sub>                                      | 1.0 V supply voltage (for MIPICSI2 D PHY)        | _          | 0.95  | 1.05  | V    |

| V <sub>DD_HV_PLL</sub> ,                                    | 1.8 V supply voltage (for analog circuits, PLLs) | _          | 1.71  | 1.95  | V    |

| V <sub>DD_HV_LFASTPLL</sub> ,<br>V <sub>DD_HV_FXOSC</sub> , |                                                  |            |       |       |      |

Table continues on the next page...

Table 4. Recommended operating conditions (continued)

| Symbol                     | Parameter                                        | Conditions | Min   | Max              | Unit |

|----------------------------|--------------------------------------------------|------------|-------|------------------|------|

| $V_{DD\_HV\_PMC}$ ,        |                                                  |            |       |                  |      |

| V <sub>DDIO_LFAST</sub> ,  |                                                  |            |       |                  |      |

| V <sub>DD_HV_EFUSE</sub> , |                                                  |            |       |                  |      |

| V <sub>DD_HV_DDR</sub>     |                                                  |            |       |                  |      |

| V <sub>DD_LV_PLL</sub>     | 1.0 V supply voltage (for analog circuits, PLLs) | _          | 0.95  | 1.05             | V    |

| V <sub>DD_LV_POST</sub>    |                                                  |            |       |                  |      |

| V <sub>REFH_ADC</sub>      | 1.8 V ADC high reference voltage                 | _          | 1.71  | 1.95             | V    |

| V <sub>DD_HV_ADV</sub>     | 1.8 V ADC supply voltage                         | _          | 1.71  | 1.95             | V    |

| V <sub>SS_HV_ADV</sub>     | ADC ground and low reference voltage             | _          | 0     | 0                | V    |

| V <sub>REFL_ADC</sub>      | 1.8 V ADC supply ground                          | _          | 0     | 0                | V    |

| V <sub>DD_DDR_IO</sub>     | DDR I/O supply voltage LPDDR2                    | _          | 1.14  | 1.30             | V    |

|                            | DDR I/O supply voltage DDR3                      | _          | 1.425 | 1.575            | V    |

|                            | DDR I/O supply voltage DDR3L                     | _          | 1.283 | 1.45             | V    |

| P <sub>CIE_VP</sub>        | PCIe supply voltages                             | _          | 0.95  | 1.05             | V    |

| P <sub>CIE_VPH</sub>       |                                                  | _          | 1.71  | 1.95             | V    |

| T <sub>A</sub>             | Ambient temperature                              | _          | -40   | 105 <sup>3</sup> | °C   |

| T <sub>J</sub>             | Junction temperature under bias                  | _          | -40   | 125              | °C   |

| TV <sub>DD</sub>           | Supply ramp rate for all supplies on the device  | _          | 0.05  | 25               | V/ms |

- 1. All the grounds viz.  $V_{SS}$ ,  $V_{SS\_XOSC}$ , and  $V_{SS\_HV\_ADV}$  are tied together at the package level.

- 2. V<sub>DD\_LV\_CORE\_SOC</sub>, V<sub>DD\_LV\_CORE\_ARM</sub>, and V<sub>DD\_LV\_CORE\_GPU</sub> supply balls should all be connected together to one power plane and one regulator to avoid voltage level differences. If the GPU is power gated as it is not used, the V<sub>DD\_LV\_CORE\_GPU</sub> supply balls have to be statically connected to the ground plane. If the second ARM CPUs per cluster is power gated as they are not used, the V<sub>DD\_LV\_CORE\_ARM</sub> supply balls have to be statically connected to the ground plane.

- 3. Maximum ambient temperature requires management of the heat dissipation to ensure the device junction temperature does not exceed the maximum.

## 4.3 Power Management Controller (PMC) electrical specifications

PMC is composed of the following blocks:

- Low voltage detector (LVD\_33\_PMC) for 3.3 V VDD\_GPIO0 supply (GPIO segment and PMC) and Low Voltage Detector for FIRC (VDD\_HV\_OSC)

- Low voltage detector (LVD\_18) for VDD\_HV\_PMC

- Low voltage detector (LVD\_18) for VDD\_HV\_FXOSC

- High voltage detector (HVD\_18) for VDD\_HV\_PMC

- Low voltage detector (LVD\_CORE) for VDD\_LV\_CORE\_SOC

- High voltage detector (HVD\_CORE) for VDD\_LV\_CORE\_SOC

- Power on Reset (POR)

Table 5. PMC electrical specifications

| Supply          | Parameter                             | Conditions | Threshold        | Min  | Typical | Max  | Status<br>during<br>power-up | Unit |

|-----------------|---------------------------------------|------------|------------------|------|---------|------|------------------------------|------|

| VDD_LV_CORE_SOC | low voltage                           | Native     | VTL <sup>1</sup> | 836  | 880     | 924  | Enabled                      | mV   |

|                 | monitoring                            |            | VTH <sup>2</sup> | 850  | 895     | 940  |                              |      |

|                 |                                       | Trimmed    | VTL              | 896  | 910     | 924  |                              |      |

|                 |                                       |            | VTH              | 911  | 925     | 946  | 1                            |      |

| VDD_LV_CORE_SOC | high                                  | Trimmed    | VTL              | 1049 | 1065    | 1093 | Disabled                     | mV   |

|                 | voltage<br>monitoring                 |            | VTH              | 1064 | 1080    | 1093 |                              |      |

| VDD_HV_PMC      | PMC                                   | Native     | VTL              | 1511 | 1590    | 1670 | Enabled                      | mV   |

|                 | supply low<br>voltage<br>monitor      |            | VTH              | 1525 | 1605    | 1685 |                              |      |

|                 |                                       | Trimmed    | VTL              | 1620 | 1650    | 1680 |                              |      |

|                 |                                       |            | VTH              | 1635 | 1665    | 1695 |                              |      |

| VDD_HV_PMC      | PMC                                   | Trimmed    | VTL              | 2004 | 2045    | 2086 | Disabled                     | mV   |

|                 | supply high<br>voltage<br>monitor     |            | VTH              | 2019 | 2060    | 2101 |                              |      |

| VDD_GPIO0       | low voltage                           | Native     | VTL              | 2727 | 2870    | 3014 | Enabled                      | mV   |

|                 | monitor                               |            | VTH              | 2746 | 2890    | 3035 |                              |      |

|                 |                                       | Trimmed    | VTL              | 2857 | 2915    | 2973 |                              |      |

|                 |                                       |            | VTH              | 2876 | 2935    | 2994 |                              |      |

| VDD_HV_OSC      | OSC                                   | Native     | VTL              | 1511 | 1590    | 1670 | Enabled                      | mV   |

|                 | supply low voltage                    |            | VTH              | 1525 | 1605    | 1685 |                              |      |

|                 | monitor                               | Trimmed    | VTL              | 1620 | 1650    | 1680 |                              |      |

|                 |                                       |            | VTH              | 1635 | 1665    | 1695 |                              |      |

| PMC_BGREF       | PMC Band<br>Gap<br>Reference<br>value | Trimmed    | _                | 1176 | 1200    | 1224 | Enabled                      | mV   |

<sup>1.</sup> Lower threshold/assert point

# 4.4 Power consumption

The following table shows the power consumption data. These specifications are subject to change per device characterization.

Table 6. Power consumption

| Parameter | Description                                                  | Max Values |

|-----------|--------------------------------------------------------------|------------|

|           | S32V234 Device in reset 'front view/low power part' @ 125 °C | 3 A        |

Table continues on the next page...

<sup>2.</sup> Upper threshold/release point

#### General

## Table 6. Power consumption (continued)

| Parameter       | Description                                                                         | Max Values          |

|-----------------|-------------------------------------------------------------------------------------|---------------------|

|                 | S32V232 Device in reset 'low power part' w/o GPU and w/o A53 CPU3 and CPU4 @ 125 °C | 2.7 A               |

|                 | S32V234 Device in reset 'high speed part' with GPU @ 125 °C                         | 6.4 A               |

|                 | S32V234 Device in reset 'high speed part' without GPU @ 125 °C                      | 4.8 A               |

|                 | Adder 4x A53 CPU with Dhrystone MIPS running on each CPU @1 GHz <sup>3</sup>        | 1.4 A               |

| VDD_HV_CSI      | Current for both MIPICSI2 interfaces operating as per                               | 1) 10 mA<br>2) 1 mA |

|                 | 1) RX Operation at 1.5 Gbps per<br>MIPICSI2                                         | 2, 1                |

|                 | 2) MIPICSI2 not used (IP Powered and Disabled)                                      |                     |

| VDD_LV_CSI      | Current for both MIPICSI2 interfaces operating as per                               | 1) 40 mA            |

|                 | NRX Operation at 1.5 Gbps per     MIPICSI2                                          | 2) 13 mA            |

|                 | 2) MIPICSI2 not used (IP Powered and Disabled)                                      |                     |

| VDD_HV_PLL      | All five PLLs operating at 1 GHz VCO frequency                                      | 35 mA               |

| VDD_HV_LFASTPLL | Use case:                                                                           | 1) 26 mA            |

|                 | 1) PLL operating with 320 MHz (LFAST used)                                          | 2) .1 mA            |

|                 | 2) PLL not operational (LFAST not used)                                             |                     |

| VDD_HV_FXOSC    | Shared supply for FXOSC operating with 40 MHz crystal and FIRC oscillator           | 5 mA                |

| VDD_HV_PMC      | As per default usage (no use case differentiation)                                  | 10 mA               |

| VDD_HV_EFUSE    | Use case:                                                                           | 1) 10 mA            |

|                 | 1) eFuse programming happening                                                      |                     |

| VDD_LV_PLL      | All five PLLs operating at 1 GHz VCO frequency                                      | 80 mA               |

| PCIE_VP         | Use case:                                                                           | 1) 80 mA            |

|                 | 1) 5 GHz operation (PCIe 2.0)                                                       | 2) 30 mA            |

|                 | 2) Reset/idle                                                                       |                     |

| PCIE_VPH        | Use case:                                                                           | 1) 50 mA            |

|                 | 1) 5 GHz operation (PCIe 2.0)                                                       | 2) 20 mA            |

|                 | 2) Reset/idle                                                                       |                     |

<sup>1.</sup> Data represented is at 125  $^{\circ}\text{C}$  and 1.01 V vdd conditions

<sup>2.</sup> Includes SoC, GPU, and ARM supply combinations depending on use case description.

Adder to the static idd current component. 4xCortex A53 executing Dhrystone MIPS in AArch64 and the interconnect, System RAM, FastDMA, Cortex M4, peripheral bridges, FCCU, CSE, MEMU, PCIe, and STCU are clocked - static power consumption excluded.

## 4.5 Electrostatic discharge (ESD) specifications

Electrostatic discharges are applied to the pins of each sample in conformity with AEC-Q100-002/-011 to meet the HBM and CDM ratings described below.

Table 7. ESD ratings<sup>1</sup>

| Symbol                | Parameter                                     | Conditions                                        | Class | Max value <sup>2</sup> | Unit |

|-----------------------|-----------------------------------------------|---------------------------------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>(Human Body Model) | T <sub>A</sub> = 25 °C conforming to AEC-Q100-002 | H1C   | 2000                   | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge                       | T <sub>A</sub> = 25 °C conforming to AEC-         | СЗА   | 500                    | V    |

|                       | (Charged Device Model)                        | Q100-011                                          |       | 750 (corners)          | V    |

<sup>1.</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

## 4.6 Electromagnetic Compatibility (EMC) specifications

EMC measurements to IC-level IEC standards are available from NXP on request.

## 4.7 PCB routing guidelines

## DDR3/DDR3L PCB design

- CLK/Addess/Commands

- Route with 50 ohm controlled impedance and differential pair (CLK) with 100 ohm controlled impedance

- Use Fly by topology in case of multiple memory components

- Address and command lines Terminated to VTT with 50 ohm

- To be referenced with Power, not Ground

- Address/Cmd to be routed within 66 mils with respect to CLK and to be matched from controller to memory; memory to memory as well

- All traces to be routed in internal layers

- Preference is to use only two layers for routing this group

- Limit the via number to less than three

<sup>2.</sup> Data based on characterization results, not tested in production.

#### **NOTE**

The differential clock lines on the DDR3 interface should use AC termination scheme, with a 0.1  $\mu$ F series capacitor and referenced to DDR IO supply (V<sub>DD\_DDR\_IO</sub>).

#### Data/Strobe

- Route with 50 ohm controlled impedance and differential pair (DQS strobe) with 100 ohm controlled impedance

- Data to be routed within 33 mils with respect to respective strobe

- To be referenced with Ground

- All traces to be routed in internal layers

- Strictly to be routed in only two layers

- Avoid more than two vias

## LPDDR2 PCB design

- CLK/Addess/Commands

- Route with 50 ohm controlled impedance and differential pair (CLK) with 100 ohm controlled impedance

- To be referenced with Power, not Ground

- Address/Cmd to be routed within 66 mils with respect to CLK and to be matched from controller to memory

- All traces to be routed in internal layers and delay should be less than 150 ps

- Preference is to use only two layers for routing this group

- Limit the via number to less than three

- Data/Strobe

- Route with 50 ohm controlled impedance and differential pair (DQS strobe) with 100 ohm controlled impedance

- Data to be routed within 33 mils with respect to respective strobe

- To be referenced with Ground

- All traces to be routed in internal layers and delay should be less than 150 ps

- Strictly to be routed in only two layers

- Avoid more than two vias

#### **GPIO Interfaces**

- QuadSPI

- Put 22 ohm series termination on board when operating with DSE <2:0> 111

- TRACE

- Put 22 ohm series termination on board when operating with DSE <2:0> 111

- ENET

- Put 22 ohm series termination on board when operating with DSE <2:0> 111

## 5 I/O parameters

## 5.1 General purpose I/O parameters

# 5.1.1 GPIO speed at various voltage levels

#### **NOTE**

Rise/fall times numbers in Datasheet are guaranteed by design; to obtain actual rise/fall times parameters with specific packages and boards, use appropriate I/O IBIS model.

Table 8. GPIO rise/fall times (1.8 V range)

| Parameter                                  | Symbol | Drive strength ipp_dse<1:0> | Slew rate | Test conditions                 | Тур | Max       | Unit |

|--------------------------------------------|--------|-----------------------------|-----------|---------------------------------|-----|-----------|------|

| IO output                                  | tpr    | 011                         | slow      | 15 pF Cload                     |     | 2.56/2.51 | ns   |

| transition<br>time, rise/fall <sup>1</sup> |        |                             | fast      | on pad                          |     | 1.97/2.20 |      |

| limo, moorian                              |        | 100                         | slow      | ipp_do input<br>transition time |     | 3.08/3.02 |      |

|                                            |        |                             | fast      | 120 ps                          |     | 2.59/2.58 |      |

|                                            |        | 101                         | slow      |                                 |     | 2.56/2.42 |      |

|                                            |        |                             | fast      |                                 |     | 1.84/1.96 |      |

|                                            |        | 111                         | slow      |                                 |     | 1.82/1.67 |      |

|                                            |        |                             | fast      |                                 |     | 1.13/1.24 |      |

Max condition: wcs model, 0.9 V vddi, 1.62 V ovdd, and 125 °C. Input transition time is 120 ps.

Slow slew rate means ipp\_fsel = '00', fast slew rate means ipp\_fsel = '11'

Table 9. GPIO rise/fall times (2.5 V range)

| Parameter                                  | Symbol | Drive strength ipp_dse<1:0> | Slew rate | Test conditions                 | Тур | Max       | Unit |

|--------------------------------------------|--------|-----------------------------|-----------|---------------------------------|-----|-----------|------|

| IO output                                  | tpr    | 011                         | slow      | 15 pF Cload                     |     | 3.44/3.04 | ns   |

| transition<br>time, rise/fall <sup>1</sup> |        |                             | fast      | on pad                          |     | 2.75/2.55 |      |

| limo, moorian                              |        | 100                         | slow      | ipp_do input<br>transition time |     | 4.05/3.54 |      |

|                                            |        |                             | fast      | 120 ps                          |     | 3.56/2.97 |      |

|                                            |        | 101                         | slow      |                                 |     | 3.39/2.93 |      |

|                                            |        |                             | fast      |                                 |     | 2.72/2.47 |      |

|                                            |        | 111                         | slow      | ]                               |     | 2.31/2.03 |      |

|                                            |        |                             | fast      |                                 |     | 1.80/1.75 |      |

1. Max condition for tpr: wcs model, 0.9 V vddi, 2.25 V ovdd, and 125 °C. Input transition time is 125 ps. Slow slew rate means ipp\_fsel = '00', fast slew rate means ipp\_fsel = '11'

NXP Semiconductors 15

#### General purpose I/O parameters

Table 10. GPIO rise/fall times (3.3 V range)

| Parameter                                  | Symbol | Drive strength ipp_dse<1:0> | Slew<br>rate | Test<br>conditions              | Тур | Max       | Unit |

|--------------------------------------------|--------|-----------------------------|--------------|---------------------------------|-----|-----------|------|

| IO output                                  | tpr    | 011                         | slow         | 15 pF Cload                     |     | 3.47/3.16 | ns   |

| transition<br>time, rise/fall <sup>1</sup> |        |                             | fast         | on pad                          |     | 2.90/2.73 |      |

| limo, noorian                              |        | 100                         | slow         | ipp_do input<br>transition time |     | 4.09/3.58 |      |

|                                            |        |                             | fast         | 120 ps                          |     | 3.73/3.07 |      |

|                                            |        | 101                         | slow         |                                 |     | 3.29/3.00 |      |

|                                            |        |                             | fast         |                                 |     | 2.68/2.37 |      |

|                                            |        | 111                         | slow         |                                 |     | 2.23/2.18 |      |

|                                            |        |                             | fast         |                                 |     | 1.47/1.57 |      |

<sup>1.</sup> Max condition for tpr: wcs model, 0.9 V vddi, 2.97 V ovdd, and 125 °C. Input transition time is 120 ps. slow slew rate means ipp\_fsel = '00', fast slew rate means ipp\_fsel = '11'

## 5.1.2 DC electrical specifications

Table 11. DC electrical specifications

| Symbol                 | Parameter                       | Test conditions | Min                     | Тур | Max      | Unit |

|------------------------|---------------------------------|-----------------|-------------------------|-----|----------|------|

| Voh                    | High-level output voltage       | loh=-100 μA     | ovdd <sup>1</sup> -0.15 | _   | _        | V    |

| Vol                    | Low-level output voltage        | Iol=100 μA      | _                       | _   | 0.15     | V    |

| Vihf                   | High-Level DC input voltage     | _               | 0.7*ovdd                | _   | ovdd     | V    |

| Vil                    | Low-Level DC input voltage      | _               | 0                       | _   | 0.2*ovdd | V    |

| lin <sup>2</sup>       | Input current (no pull-up/down) | Vin = ovdd or 0 | _                       | _   | 8        | μA   |

| lin_33pu <sup>2</sup>  | Input current (33 kilohm PU)    | Vin = 0         | _                       | _   | 220      | μA   |

|                        |                                 | Vin = ovdd      |                         |     | 6        |      |

| lin_50pu <sup>2</sup>  | Input current (50 kilohm PU)    | Vin = 0         | _                       | _   | 150      | μA   |

|                        |                                 | Vin = ovdd      |                         |     | 6        |      |

| lin_100pu <sup>2</sup> | Input current (100 kilohm PU)   | Vin = 0         | _                       | _   | 60       | μA   |

|                        |                                 | Vin = ovdd      |                         |     | 6        |      |

| lin_100pd <sup>2</sup> | Input current (100 kilohm PD)   | Vin = 0         | _                       | _   | 8        | μΑ   |

|                        |                                 | Vin = ovdd      |                         |     | 50       |      |

<sup>1.</sup> ovdd is the IO supply for the pads.

#### NOTE

After bootup, application software should switch to manual voltage detect mode using VSEL\_x settings of SRC\_GPR14 register to ensure optimum performance of the GPIO pads.

<sup>2.</sup> Max condition: bcs model, 3.6 V, and 125 °C. These values are for I/O buffers.

Please refer to SRC chapter in the Reference Manual for the register details.

Table 12. Current-draw Characteristics for DDR\_VREF

| Symbol   | Parameter                                 | Min | Max | Unit |

|----------|-------------------------------------------|-----|-----|------|

| DDR_VREF | Current-draw characteristics for DDR_VREF | _   | 1   | mA   |

## 5.2 DDR pads

# 5.2.1 Boot Configuration Pins Specification

Value driven on RCON and BOOTMOD pins should be stable for atleast 1 µs after RESET pin is deasserted.

## 5.2.2 DDR3 mode

## 5.2.2.1 DDR3 mode DC electrical specifications

Table 13. DDR3 mode DC electrical specifications

| Parameter                                       | Symbol                | Test<br>conditions          | Min        | Тур      | Max        | Unit |

|-------------------------------------------------|-----------------------|-----------------------------|------------|----------|------------|------|

| High-level output voltage                       | Voh                   | loh=-100 μA                 | 0.8*ovdd   | _        | _          | V    |

| Low-level output voltage                        | Vol                   | Iol=100 μA                  | _          | _        | 0.2*ovdd   | V    |

| High-level DC input voltage                     | Vih (DC)              | _                           | Vref + 0.2 | _        | ovdd       | V    |

| High-level DC input voltage                     | Vil (DC)              | _                           | ovss       | _        | Vref - 0.2 | V    |

| Input reference voltage                         | Vref                  | _                           | 0.49*ovdd  | 0.5*ovdd | 0.51*ovdd  | V    |

| Termination voltage <sup>1</sup>                | Vtt                   | _                           | 0.49*ovdd  | 0.5*ovdd | 0.51*ovdd  | V    |

| Input current (no pullup/pulldown) <sup>2</sup> | lin                   | Vi = 0 or ovdd              | _          | _        | 5          | μΑ   |

| Pullup/pulldown impedance mismatch              | MMpupd                | 34 Ohm full strength driver | -10        | _        | +10        | %    |

| Driver 240 Ohm unit calibration resolution      | Rres                  | _                           | _          | _        | 10         | Ω    |

| Rkeep <sup>3</sup>                              | Pad keeper resistance | _                           | 20         | _        | 50         | kΩ   |

<sup>1.</sup> Vtt is expected to track ovdd/2.

S32V234 Data Sheet, Rev. 5, 03/2018

NXP Semiconductors 17

<sup>2.</sup> Typ condition: typ model, 1.5V, and 25 °C. Max condition: bcs model, 1.575V, and -40 °C. Min condition: wcs model, 1.425V, and 125 °C.

#### LPDDR2 mode

3. Typ condition: typ model, 1.5 V, and 25 °C, max condition: wcs model, 1.425 V, and 125 °C, min condition: bcs model, 1.575 V, and -40 °C.

## 5.2.3 DDR3L mode

## 5.2.3.1 DDR3L mode DC electrical specifications

Table 14. DDR3L mode DC electrical specifications

| Parameter                                                 | Symbol                   | Test conditions | Min        | Тур      | Max        | Unit |

|-----------------------------------------------------------|--------------------------|-----------------|------------|----------|------------|------|

| High-level output voltage                                 | Voh                      | loh = -100 μA   | 0.8*ovdd   | _        | _          | V    |

| Low-level output voltage                                  | Vol                      | lol = 100 μA    | _          | _        | 0.2*ovdd   | V    |

| High-level DC input voltage                               | Vih (DC)                 | _               | Vref + 0.2 | _        | ovdd       | V    |

| High-level DC input voltage                               | Vil (DC)                 | _               | ovss       | _        | Vref - 0.2 | V    |

| Input reference voltage                                   | Vref                     | _               | 0.49*ovdd  | 0.5*ovdd | 0.51*ovdd  | V    |

| Vref current draw                                         | Icc-vref                 | _               | _          | _        | 1          | mA   |

| Termination voltage                                       | Vtt                      | _               | 0.49*ovdd  | 0.5*ovdd | 0.51*ovdd  | V    |

| Input current (no pullup/pulldown)                        | lin                      | Vi = 0 or ovdd  | _          | _        | 5          | μΑ   |

| Pullup/pulldown impedance mismatch (full strength driver) | MMpupd                   | _               | -10        | _        | +10        | %    |

| Driver unit (240 Ohm) calibration resolution              | Rres                     | _               | _          | _        | 10         | Ω    |

| Rkeep                                                     | Pad keeper<br>resistance | _               | 20         | _        | 50         | kΩ   |

## 5.2.4 LPDDR2 mode

## 5.2.4.1 LPDDR2 mode DC electrical specifications

Table 15. LPDDR2 mode DC electrical specifications

| Parameter                                           | Symbol   | Test conditions             | Min         | Тур      | Max         | Unit |

|-----------------------------------------------------|----------|-----------------------------|-------------|----------|-------------|------|

| High-level output voltage                           | Voh      | loh = -100 μA               | 0.9*ovdd    | _        | _           | V    |

| Low-level output voltage                            | Vol      | lol = 100 μA                | _           | _        | 0.1*ovdd    | V    |

| Input reference voltage                             | Vref     | _                           | 0.49*ovdd   | 0.5*ovdd | 0.51*ovdd   | V    |

| High-level DC input voltage                         | Vih (DC) | _                           | Vref + 0.17 | _        | ovdd        | V    |

| High-level DC input voltage                         | Vil (DC) | _                           | ovss        | _        | Vref - 0.17 | V    |

| Input current (no pullup/<br>pulldown) <sup>1</sup> | lin      | Vi = ovdd or 0              | _           | _        | 5           | μΑ   |

| Pullup/pulldown impedance mismatch                  | MMpupd   | 34 Ohm full strength driver | -15         |          | +15         | %    |

Table continues on the next page...

Table 15. LPDDR2 mode DC electrical specifications (continued)

| Parameter                                  | Symbol                | Test conditions | Min | Тур | Max | Unit |

|--------------------------------------------|-----------------------|-----------------|-----|-----|-----|------|

| Driver 240 Ohm unit calibration resolution | Rres                  | _               | _   | _   | 10  | Ω    |

| Rkeep <sup>2</sup>                         | Pad keeper resistance | _               | 20  | _   | 50  | kΩ   |

<sup>1.</sup> Typ condition: typ model, 1.2 V, and 25 °C. Max condition: bcs model, 1.32 V, and -40 °C. Min condition: wcs model, 1.14 V, and 125 °C.

# 6 Peripheral operating requirements and behaviors

## 6.1 Analog modules

## 6.1.1 ADC electrical specifications

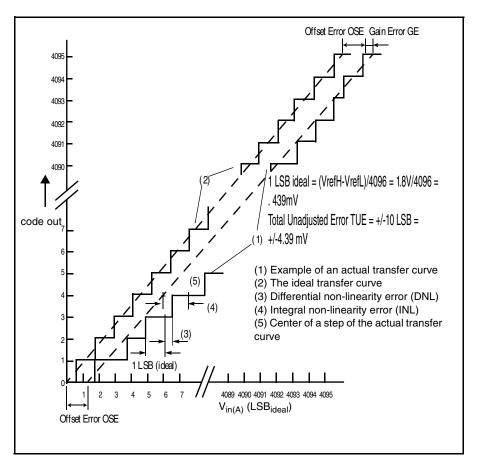

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

<sup>2.</sup> Typ condition: typ model, 1.2 V, and 25 °C, max condition: wcs model, 1.14 V, and 125 °C, min condition: bcs model, 1.32 V, and -40 °C.

#### **Analog modules**

Figure 2. ADC characteristics and error definitions

#### **NOTE**

While measuring scaled supply voltages on ADC Channels, Maximum (+5/-10%) variation can be expected.

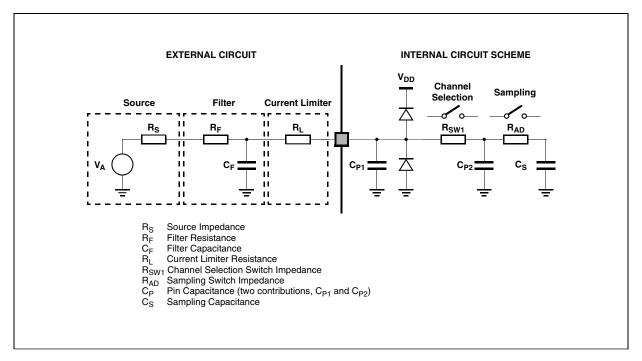

# 6.1.1.1 Input equivalent circuit

Figure 3. Input equivalent circuit

Table 16. ADC conversion characteristics

| Symbol                     | Parameter                                   | Conditions | Min  | Тур | Max  | Unit |

|----------------------------|---------------------------------------------|------------|------|-----|------|------|

| f <sub>CK</sub>            | ADC Input Clock frequency (Bus clock)       | _          | 20   |     | 80   | MHz  |

| f <sub>AD_clk</sub>        | ADC Conversion clock frequency <sup>1</sup> |            | 20   |     | 40   | MHz  |

| f <sub>s</sub>             | Sampling frequency                          | _          | _    | _   | 0.5  | MHz  |

| t <sub>sample</sub>        | Sample time <sup>2</sup>                    |            | 500  | _   | _    | ns   |

| t <sub>conv</sub>          | Conversion time <sup>3</sup>                |            | 1400 | _   | _    | ns   |

| C <sub>S</sub>             | ADC input sampling capacitance              | _          | _    | _   | 5    | pF   |

| C <sub>P1</sub>            | ADC input pin capacitance 1                 | _          | _    | _   | 5    | pF   |

| C <sub>P2</sub>            | ADC input pin capacitance 2                 | _          | _    | _   | 0.8  | pF   |

| R <sub>SW1</sub>           | Internal resistance of analog source        | _          | _    | _   | 875  | Ω    |

| R <sub>AD</sub>            | Internal resistance of analog source        | _          | _    | _   | 825  | Ω    |

| INL <sup>4</sup>           | Integral non linearity                      | _          | -3   | _   | 3    | LSB  |

| DNL                        | Differential non linearity                  | _          | -2   | _   | 2    | LSB  |

| OFS                        | Offset error                                | _          | -6   | _   | 6    | LSB  |

| GNE                        | Gain error                                  | _          | -6   | _   | 6    | LSB  |

| Input (single ADC channel) | Max leakage                                 | 125C       |      | _   | 2000 | nA   |

| TUE                        | Total unadjusted error                      | _          | -8   | _   | 8    | LSB  |

#### Clocks and PLL interfaces modules

- Please see description of Clock & reset section in ADC chapter in Reference Manual for details. User need to generate AD\_clk = 40 MHz for 0.5 MSPS operation. For example, if f<sub>ck</sub> = 80 MHz, configure MCR[8].ADCLKSE = 0 and MCR[4].ADCLKDIV = 0 (default).

- 2. During the sample time the input capacitance CS can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>sample</sub> depend on programming. For internal ADC channels, the minimum sampling time required is 3 microsecond.

- 3. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 4. Specifications are quoted here for input signal ranging from 150 mV to VDD\_HV\_ADC 150 mV. For signals outside this range, the Specifications may degrade beyond limits specified in this table.

## **6.1.2 Thermal Monitoring Unit (TMU)**

The following table describes TMU electrical characteristics.

**Symbol Parameter Conditions** Value Unit Min Max Typ ٥С  $T_{i}$ -40 125 Temperature monitoring range mV/°C Sensitivity T<sub>SENS</sub> 2.5 °С  $T_{ACC}$ Accuracy  $T_{.1} = -40 \, ^{\circ}\text{C}$  to 40  $^{\circ}\text{C}$ -10 +10 °С  $T_1 = 40 \, ^{\circ}\text{C} \text{ to } 125 \, ^{\circ}\text{C}$ -6 +6

Table 17. TMU electrical characteristics

## 6.2 Clocks and PLL interfaces modules

## 6.2.1 Main oscillator electrical characteristics

The device provides an oscillator/resonator driver of a Pierce-type structure.

Table 18. Main oscillator electrical characteristics

| Symbol                 | Parameter                                | Conditions                                                      |          | Value |            |     |

|------------------------|------------------------------------------|-----------------------------------------------------------------|----------|-------|------------|-----|

|                        |                                          |                                                                 | Min      | Тур   | Max        |     |

| f <sub>FXOSCHS</sub>   | Oscillator frequency                     | _                                                               | _        | 40.0  | n/a        | MHz |

| T <sub>FXOSCHSSU</sub> | Oscillator start-up time                 | f <sub>FXOSCHS</sub> = 40 MHz                                   | _        | _     | 21         | ms  |

| V <sub>IH</sub>        | Input high level CMOS<br>Schmitt Trigger | Vref = 0.5*VDD_HV_OSC<br>where VDD_HV_OSC is<br>FXOSC HV Supply | Vref+0.5 | _     | VDD_HV_OSC | V   |

| V <sub>IL</sub>        | Input low level CMOS<br>Schmitt Trigger  | Vref = 0.5*VDD_HV_OSC<br>where VDD_HV_OSC is<br>FXOSC HV Supply | 0        | _     | Vref – 0.5 | V   |

1. The start-up time is dependent upon crystal characteristics, board leakage, etc, high ESR and excessive capacitive loads can cause long start-up time

Following crystals are used in internal crystal oscillator validation:

- NX3225 40 MHz; Load capacitance = 8 pF

- NX5032 40 MHz; Load capacitance = 8 pF

#### 6.2.2 48 MHz FIRC electrical characteristics

## Table 19. FIRC electrical specifications

| Symbol              | Parameter                                                                                                | Conditions | Value |     |     | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------|------------|-------|-----|-----|------|

|                     |                                                                                                          |            | Min   | Тур | Max |      |

| F <sub>Target</sub> | FIRC target frequency (trimmed)                                                                          | _          | _     | 48  | _   | MHz  |

| δF <sub>var_T</sub> | FIRC frequency<br>variation with<br>respect to<br>supply and<br>temperature<br>after process<br>trimming | _          | -10   | _   | +10 | %    |

## 6.2.3 PLL electrical specifications

#### Table 20. PLL electrical characteristics 1

| Symbol               | Parameter                               | Conditions | Value           |     |                 | Unit |

|----------------------|-----------------------------------------|------------|-----------------|-----|-----------------|------|

|                      |                                         |            | Min             | Тур | Max             | ]    |

| f <sub>PLLIN</sub>   | PLL input clock <sup>2</sup>            | _          | 20 <sup>3</sup> | _   | 40 <sup>3</sup> | MHz  |

| $\Delta_{PLLIN}$     | PLL input clock duty cycle <sup>2</sup> | _          | 40              | _   | 60              | %    |

| t <sub>PLLLOCK</sub> | PLL lock time                           | _          | _               | _   | 100             | μs   |

| $\Delta_{PLLT}$      | Period jitter                           | _          | _               | _   | 150             | ps   |

| $\Delta_{PLLTIE}$    | TIE                                     | _          | _               | _   | 560             | ps   |

| f <sub>PLLMOD</sub>  | SSCG modulation frequency               | _          | _               | _   | 32              | kHz  |

| δ <sub>PLLMOD</sub>  | SSCG modulation depth (Down Spread)     | _          | 0.50            | _   | 2.74            | %    |

- 1. The jitter values are gauranteed for following conditions:

- 1. Measurement being done on LFAST TX pad with observed frequency greater than 250 M and less than 320 M

- 2. Minimum SOC activity Operations required to observe clock must be functional.

- 3. Maximum frequency change in SSCG modulation is limited by following relation: Modulation Depth \* VCO Frequency < PLL Reference (PFD) Frequency

- 2. PLL0IN clock retrieved from either internal RCOSC or external FXOSC clock. Input characteristics are granted when using internal RCOSC or external oscillator is used in functional mode.

- 3. The PLLIN clock is the frequency after the PREDIV(Pre-divider) value division, and before the Phase detector block. Please refer to the PLLs section of clocking chapter in the Reference Manual.

#### Clocks and PLL interfaces modules

4. STEPSIZE x STEPNO < 18432

For the PLL frequencies supported by this device, refer to the Table - "PLL frequencies" in the "Clocking" chapter of the Reference Manual.

## 6.2.4 DFS electrical specifications

DFS takes input clock from PLL output. Here is relation between input and output clock of each phase divider:

F(dfsclkout) = F(dfsclkin)/[mfi+(mfn/256)]

mfi: integer part of division [1:255]

mfn: Fractional part of division [1:255]

Table 21. DFS electrical specification<sup>1</sup>

| Parameter       | Min | Typical | Max  | Unit |

|-----------------|-----|---------|------|------|

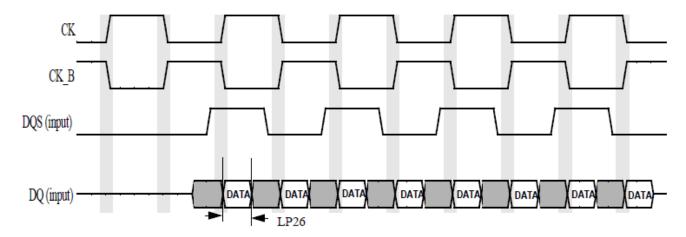

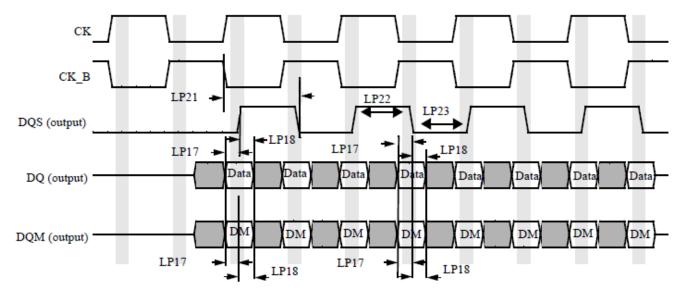

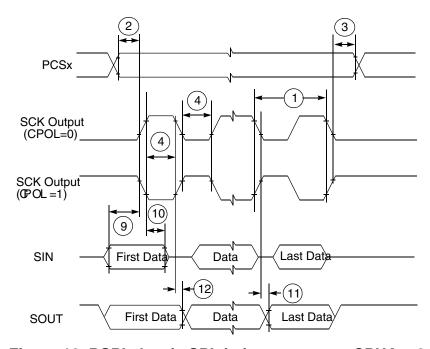

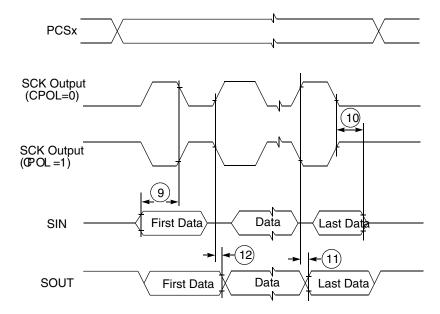

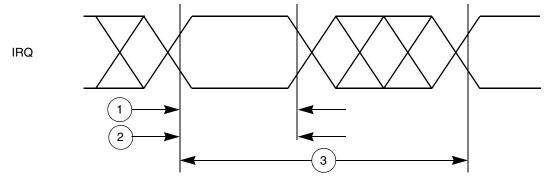

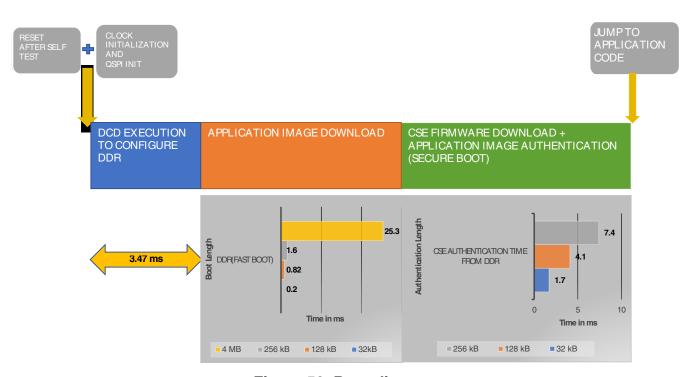

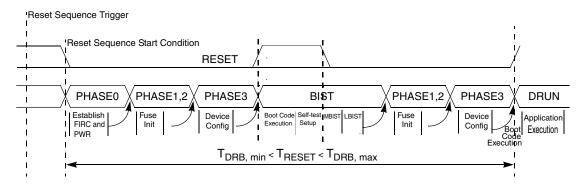

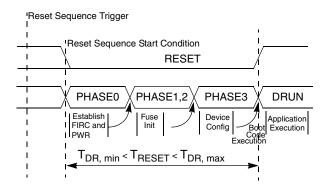

| Input Frequency | 800 | _       | 1066 | MHz  |