#### FEATURES AND BENEFITS (continued)

- Pre-bias startup compatible

- Power OK (POK) output

- Dynamic overvoltage protection, pulse-by-pulse current limit, hiccup mode short-circuit, and thermal protections

- · Open-circuit and adjacent pin short-circuit tolerant

- Short-to-ground tolerant at every pin

- USB3 charging capability: 2.6 A (A8653)

- USB2 capability: 1 A (A8652)

#### **DESCRIPTION** (continued)

frequency, and a Power OK output to indicate when  $V_{OUT}$  is within regulation and there is no load-side current limit condition. Protection features include  $V_{IN}$  undervoltage lockout, pulse-by-pulse current limit, hiccup mode short-circuit protection, dynamic overvoltage protection, and thermal shutdown. The A8652/53 provides open-circuited, adjacent pin short-circuit, and short-to-ground protection at every pin to satisfy the most demanding automotive and non-automotive applications.

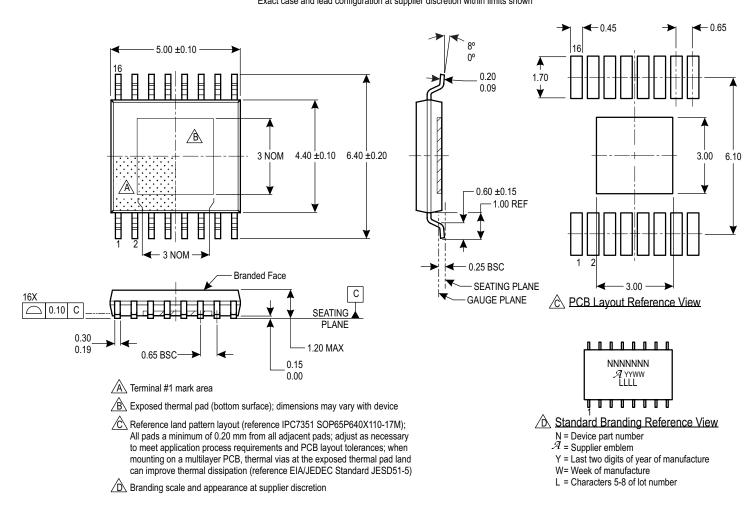

The A8652/53 device is available in a 16-pin eTSSOP package with exposed pads for enhanced thermal dissipation. It is lead (Pb) free, with 100% matte-tin lead frame plating. The maximum junction temperature  $(T_{J(max)})$  is 150°C.

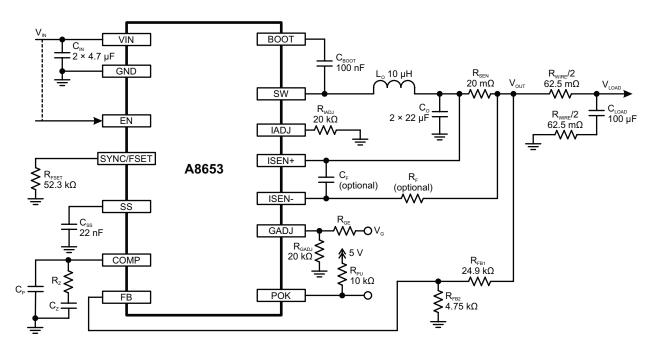

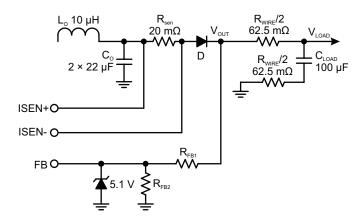

Typical Application Diagram 2 with Dynamic Voltage Correction Control at Pin GADJ

#### **Selection Guide**

| Part Number  | Packing                      | Package                                |  |  |

|--------------|------------------------------|----------------------------------------|--|--|

| A8652KLPTR-T | 4000 piagga par 12 ipah ragi | 4.4 mm × 5 mm, 1.2 mm nominal height   |  |  |

| A8653KLPTR-T | 4000 pieces per 13-inch reel | 16-pin eTSSOP with exposed thermal pad |  |  |

## Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

#### **SPECIFICATIONS**

#### Absolute Maximum Ratings<sup>1</sup>

| Characteristic                      | Symbol              | Notes                             | Rating                                            | Unit |

|-------------------------------------|---------------------|-----------------------------------|---------------------------------------------------|------|

| VIN, EN, SS                         |                     |                                   | -0.3 to 40                                        | V    |

| SW to GND <sup>2</sup>              |                     | Continuous                        | -0.3 to V <sub>IN</sub> + 0.3                     | V    |

| SW to GND 2                         | V <sub>SW</sub>     | V <sub>IN</sub> ≤ 36 V, t < 50 ns | –1 to V <sub>IN</sub> + 2                         | V    |

| DOOT Bin Alexus CW Bin              | .,                  | Continuous                        | V <sub>SW</sub> – 0.3 to<br>V <sub>SW</sub> + 5.5 | V    |

| BOOT Pin Above SW Pin               | V <sub>BOOT</sub>   | < 1 ms                            | V <sub>SW</sub> - 0.3 to<br>V <sub>SW</sub> + 7   | V    |

| ISEN+ and ISEN– Pins                |                     | ISEN+ and ISEN- Pins              | -0.3 to 6.5                                       | V    |

| ISEN+ to ISEN- Differential Voltage |                     |                                   | -0.3 to 0.3                                       | V    |

| All other pins                      |                     |                                   | -0.3 to 5.5                                       | V    |

| Maximum Junction Temperature        | T <sub>J(max)</sub> |                                   | 150                                               | °C   |

| Storage Temperature Range           | T <sub>stg</sub>    |                                   | -55 to 150                                        | °C   |

<sup>&</sup>lt;sup>1</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

#### **Thermal Characteristics**

| Characteristic Symbol      |                 | Test Conditions <sup>3</sup>                    | Value | Unit |

|----------------------------|-----------------|-------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | LP Package, 4-layer PCB based on JEDEC standard | 34    | °C/W |

<sup>&</sup>lt;sup>3</sup> Additional thermal information available on the Allegro website.

<sup>2</sup> SW has internal clamp diodes to GND and VIN. Applications that forward bias these diodes should take care not to exceed the IC package power dissipation limits.

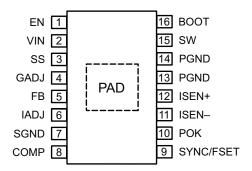

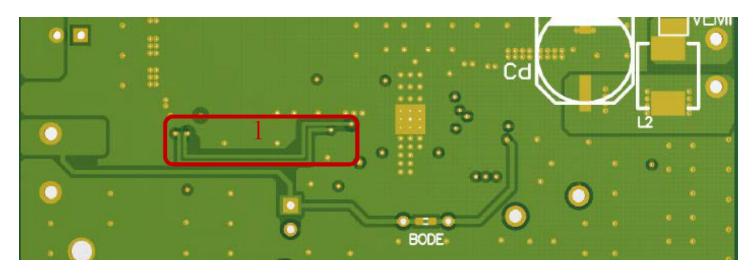

#### PINOUT DIAGRAM AND TERMINAL LIST TABLE

Package LP, 16-Pin eTSSOP Pinout Diagram

#### Terminal List Table

| Symbol    | Number | Function                                                                                                                                                                                                                                                                                                                        |

|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN        | 1      | Enable input. This pin is used to turn the converter on or off: set this pin high to turn the converter on or set this pin low to turn the converter off. May be connected to VIN.                                                                                                                                              |

| VIN       | 2      | Power input for the control circuits and the drain of the internal high-side N-channel MOSFET. A high-quality ceramic capacitor should be placed very close to this pin.                                                                                                                                                        |

| SS        | 3      | Soft-Start pin. Connect a capacitor, $C_{SS}$ , from this pin to GND to set the soft-start time. This capacitor also determines the hiccup period during overcurrent.                                                                                                                                                           |

| GADJ      | 4      | This pin is used to set the gain of the differential current sense amplifier with ISEN+/ISEN- pins. A resistor from this pin to GND set the amplifier gain. Together with load sense resistor, it sets the desired voltage correction at the specified load condition. Grounding GADJ disables Remote Load Regulation function. |

| FB        | 5      | Feedback (negative) input to the error amplifier. Connect a resistor divider from the converter output node (V <sub>OUT</sub> ) to this pin to program the output voltage.                                                                                                                                                      |

| IADJ      | 6      | Active current limit adjust pin. A resistor from this pin to GND sets the current limit. When the load current exceeds this limit, the output voltage will decrease at the predefined slope.                                                                                                                                    |

| SGND      | 7      | Signal (quiet) GND.                                                                                                                                                                                                                                                                                                             |

| COMP      | 8      | Output of the error amplifier and compensation node for the control loop. Connect a series RC network from this pin to GND for loop compensation.                                                                                                                                                                               |

| SYNC/FSET | 9      | Frequency setting and synchronization pin. A resistor, R <sub>FSET</sub> , from this pin to GND sets the PWM switching frequency.                                                                                                                                                                                               |

| POK       | 10     | Power OK output signal. This pin is an open-drain output that transitions from low impedance to high impedance when the output is within the final regulation voltage and no load side current limit exists.                                                                                                                    |

| ISEN-     | 11     | Negative current-sensing pin to the internal current sense amplifier, connected to the load side of the external current sensing resistor.                                                                                                                                                                                      |

| ISEN+     | 12     | Positive current-sensing pin to the internal current sense amplifier, connected to the inductor side of the external current sensing resistor.                                                                                                                                                                                  |

| PGND      | 13, 14 | Power GND.                                                                                                                                                                                                                                                                                                                      |

| SW        | 115    | The source of the high-side N-channel MOSFET. The output inductor (L <sub>O</sub> ) should be connected to this pin. L <sub>O</sub> should be placed as close as possible to this pin and connected with relatively wide traces.                                                                                                |

| воот      | 16     | High-side gate drive boost input. Connect a 100 nF ceramic capacitor from BOOT to SW.                                                                                                                                                                                                                                           |

| PAD       | _      | Exposed pad of the package providing enhanced thermal dissipation. This pad must be connected to the ground plane(s) of the PCB with at least 6 vias, directly in the pad.                                                                                                                                                      |

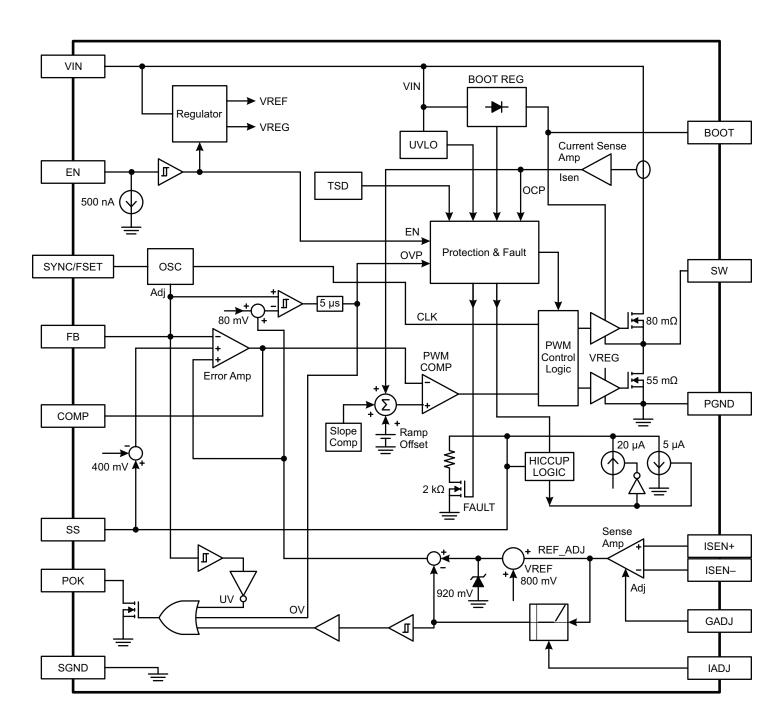

**Functional Block Diagram**

# Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

### ELECTRICAL CHARACTERISTICS: Valid at 4 V $\leq$ V<sub>IN</sub> $\leq$ 36 V; T<sub>A</sub> = 25°C; • indicates specifications guaranteed -40°C $\leq$ T<sub>A</sub> = T<sub>J</sub> $\leq$ 150°C (unless noted otherwise).

| Characteristics                                                | Symbol                   | Test Conditions                                                                                                                                  |                    |     | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|------|------|------|------|

| INPUT VOLTAGE SPECIFICATIONS                                   |                          |                                                                                                                                                  |                    |     |      |      |      |      |

| Operating Input Voltage Range <sup>2</sup>                     | V <sub>IN</sub>          |                                                                                                                                                  |                    | •   | 4    | _    | 36   | V    |

| UVLO Start Threshold                                           | V <sub>UVLO(START)</sub> | V <sub>IN</sub> rising                                                                                                                           |                    |     | _    | 3.4  | 3.7  | V    |

| UVLO Stop Threshold                                            | V <sub>UVLO(STOP)</sub>  | V <sub>IN</sub> falling                                                                                                                          |                    |     | _    | 2.6  | 2.9  | V    |

| UVLO Hysteresis                                                | V <sub>UVLO(HYS)</sub>   |                                                                                                                                                  |                    |     | _    | 800  | _    | mV   |

| INPUT CURRENTS                                                 |                          |                                                                                                                                                  |                    |     |      |      |      |      |

| Input Quiescent Current <sup>1</sup>                           | IQ                       | $V_{EN}$ = 5 V, $V_{FB}$ = 1 V, no PWM switching                                                                                                 | ng                 | •   | _    | 3    | 6.5  | mA   |

| Input Sleep Supply Current <sup>1</sup>                        | I <sub>QSLEEP</sub>      | $V_{IN} = 12 \text{ V}, V_{EN} \le 0.4 \text{ V}, -40^{\circ}\text{C} < T_{A} = 85^{\circ}\text{C}$                                              | T <sub>J</sub> <   |     | -    | 1    | 240  | μA   |

|                                                                |                          | $V_{IN} = 12 \text{ V}, V_{EN} \le 0.4 \text{ V}, T_A = T_J = 125^{\circ}\text{C}$                                                               |                    |     | _    | 40   | 900  | μΑ   |

| VOLTAGE REGULATION                                             |                          |                                                                                                                                                  |                    |     |      |      |      |      |

| Feedback Voltage Accuracy <sup>3</sup>                         | V <sub>FB</sub>          | $V_{FB} = V_{COMP}, V_{GADJ} = 0 \text{ V}, -40^{\circ}\text{C} < T_{A}$<br>125°C                                                                | = T <sub>J</sub> < |     | 792  | 800  | 808  | mV   |

|                                                                |                          | V <sub>FB</sub> = V <sub>COMP</sub> , V <sub>GADJ</sub> = 0 V                                                                                    | •                  | 788 | 800  | 812  | mV   |      |

| Feedback Voltage Accuracy with Cable Compensation <sup>3</sup> | V <sub>FB(ACC)</sub>     | $V_{FB} = V_{COMP}, V_{ISEN+} - V_{ISEN-} = 25 \text{ mV}$ $V_{OUT} = 5 \text{ V}, R_{GADJ} = 20 \text{ k}\Omega, R_{IADJ} = 20 \text{ k}\Omega$ | •                  | 808 | 825  | 842  | mV   |      |

| Error Amp Clamp Voltage <sup>3</sup>                           | V <sub>FB(CLAMP)</sub>   | $V_{FB} = V_{COMP}, V_{ISEN+} - V_{ISEN-} = 55 \text{ m} V_{OUT} = 5 \text{ V}, R_{GADJ} = 7.5 \text{ k}\Omega, R_{IADJ} = 20 \text{ M}$         |                    | 900 | 920  | 940  | mV   |      |

| Output Voltage Setting Range <sup>3</sup>                      | V <sub>OUT</sub>         |                                                                                                                                                  |                    |     | 3.3  | -    | 5.75 | V    |

|                                                                |                          | V <sub>IN</sub> = 5.7 V, I <sub>O</sub> = 2.6 A, f <sub>SW</sub> = 500 kHz                                                                       |                    |     | 4.9  | -    | -    | V    |

| Output Dropout Voltage <sup>3</sup>                            |                          | $V_{IN} = 7.3 \text{ V}, I_{O} = 2.6 \text{ A}, f_{SW} = 2 \text{ MHz}$                                                                          | A0003              | •   | 4.9  | _    | -    | V    |

| Output Dropout Voltage                                         | V <sub>O(PWM)</sub>      | $V_{IN} = 5.5 \text{ V}, I_{O} = 1 \text{ A}, f_{SW} = 500 \text{ kHz}$                                                                          | A8652              | •   | 4.9  | _    | _    | V    |

|                                                                |                          | V <sub>IN</sub> = 6.8 V, I <sub>O</sub> = 1 A, f <sub>SW</sub> = 2 MHz                                                                           | A0052              | •   | 4.9  | _    | _    | V    |

| ERROR AMPLIFIER                                                |                          |                                                                                                                                                  |                    |     |      |      |      |      |

| Feedback Input Bias Current <sup>1</sup>                       | I <sub>FB</sub>          |                                                                                                                                                  |                    |     | -100 | _    | -8   | nA   |

| Open-Loop Voltage Gain                                         | A <sub>VOL</sub>         | V <sub>COMP</sub> = 1.2 V                                                                                                                        |                    |     | _    | 65   | _    | dB   |

| Transconductance                                               | am                       | 400 mV < V <sub>FB</sub>                                                                                                                         |                    |     | 550  | 750  | 950  | μA/V |

| Transconductance                                               | gm <sub>EA</sub>         | 0 V < V <sub>FB</sub> < 400 mV                                                                                                                   |                    |     | 275  | 375  | 475  | μΑ/ν |

| Output Current                                                 | I <sub>EA</sub>          | V <sub>COMP</sub> = 1.2 V                                                                                                                        |                    |     | _    | ±75  | _    | μA   |

| INTERNAL MOSFET PARAMETERS                                     |                          |                                                                                                                                                  |                    |     |      |      |      |      |

| High-Side MOSFET On-Resistance 3                               | R <sub>DSON(HS)</sub>    | T <sub>A</sub> = 25°C, I <sub>DS</sub> = 100 mA                                                                                                  |                    |     | _    | 80   | _    | mΩ   |

| SW Node Rising Slew Rate                                       | dV/dt                    | 12 V < V <sub>IN</sub> < 16 V                                                                                                                    |                    |     | _    | 0.75 | _    | V/ns |

| SW Leakage <sup>1</sup>                                        | I <sub>SW(LEAK)</sub>    | $V_{EN} \le 0.4 \text{ V}, V_{SW} = 5 \text{ V}, V_{IN} = 12 \text{ V}, T_{J}$                                                                   | = 25°C             |     | -10  | 0    | 10   | μΑ   |

| Low-Side MOSFET On-Resistance <sup>3</sup>                     | R <sub>DSON(LS)</sub>    | $T_A = 25^{\circ}C, I_{DS} = 100 \text{ mA}$                                                                                                     |                    |     | _    | 55   | _    | mΩ   |

Continued on the next page...

# Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

ELECTRICAL CHARACTERISTICS (continued): Valid at 4 V  $\leq$  V<sub>IN</sub>  $\leq$  36 V; T<sub>A</sub> = 25°C; • indicates specifications guaranteed –40°C  $\leq$  T<sub>A</sub> = T<sub>J</sub>  $\leq$  150°C (unless noted otherwise).

| Characteristics                              | Symbol                     | Test Conditions                                                | Min.  | Тур. | Max. | Unit  |      |      |

|----------------------------------------------|----------------------------|----------------------------------------------------------------|-------|------|------|-------|------|------|

| OSCILLATOR                                   |                            |                                                                |       |      |      | *     |      |      |

|                                              |                            | R <sub>FSET</sub> = 261 kΩ                                     |       | _    | 100  | _     | kHz  |      |

| PWM Switching Frequency                      | f <sub>SW</sub>            | R <sub>FSET</sub> = 61.9 kΩ                                    |       |      | 375  | 415   | 457  | kHz  |

|                                              |                            | R <sub>FSET</sub> = 10.5 kΩ                                    |       | _    | 2000 | _     | kHz  |      |

| PWM Frequency Dithering                      | f <sub>DITHER</sub>        | No dithering with FSET synchroniza                             | ition |      | _    | ±13   | _    | %    |

| Minimum Controllable On-Time                 | t <sub>ON(MIN)</sub>       | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 1 A                 |       |      | _    | 95    | 135  | ns   |

| Minimum Switch Off-Time                      | t <sub>OFF(MIN)</sub>      | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 1 A                 |       |      | _    | 100   | 135  | ns   |

| FSET SYNCHRONIZATION TIMING                  |                            |                                                                |       |      |      | *     |      |      |

| Synchronization Frequency Range              | f <sub>SW_MULT</sub>       |                                                                |       |      | 100  | _     | 2200 | kHz  |

| Synchronization Input Off-Time               | t <sub>SYNC_OFF</sub>      |                                                                |       |      | 0.2  | _     | 1.3  | μs   |

| Synchronization Input Rise Time <sup>3</sup> | t <sub>r(SYNC)</sub>       |                                                                |       |      | _    | 10    | 15   | ns   |

| Synchronization Input Fall Time <sup>3</sup> | t <sub>f(SYNC)</sub>       |                                                                |       |      | _    | 10    | 15   | ns   |

| Synchronization Rising Threshold             | V <sub>SYNC(HI)</sub>      | V <sub>SYNC</sub> rising                                       | _     | -    | 2    | V     |      |      |

| Synchronization Falling Threshold            | V <sub>SYNC(LO)</sub>      | V <sub>SYNC</sub> falling                                      |       |      | 0.5  | _     | 0.7  | V    |

| CURRENT LOOP                                 |                            |                                                                |       |      |      |       |      |      |

|                                              |                            | A8653                                                          |       | •    | 3.3  | 4     | 4.62 | Α    |

| Peak Inductor (Pulse-by-Pulse) Current       | I <sub>PK_LIM(MINON)</sub> | $t_{ON} = t_{ON(MIN)}$                                         | A8652 | •    | 1.5  | 1.8   | 2.1  | А    |

| Limit                                        |                            | t = 1/f t No Syno                                              | A8653 | •    | 2.4  | 3.2   | 4    | А    |

|                                              | PK_LIM(MINOFF)             | $t_{ON} = 1/f_{SW} - t_{OFF(MIN)}$ , No Sync                   | A8652 | •    | 0.9  | 1     | 1.5  | А    |

| Load-Side Current Limit                      |                            | $R_{IADJ} = 20 \text{ k}\Omega, R_{SEN} = 20 \text{ m}\Omega,$ | A8653 |      | 2.5  | 3     | 3.3  | А    |

| Load-Side Current Limit                      | I <sub>OUT_LIM</sub>       | V <sub>OUT</sub> = 5 V                                         | A8652 |      | 1    | 1.2   | 1.4  | Α    |

| COMP to SW Current Gain                      |                            |                                                                | A8653 |      | _    | 6.3   | _    | A/V  |

| COMP to SW Current Gain                      | gm <sub>POWER</sub>        |                                                                | A8652 |      | _    | 3.2   | _    | A/V  |

|                                              |                            | R <sub>FSET</sub> = 261 kΩ, 100 kHz                            |       |      | _    | 0.056 | _    | A/µs |

|                                              |                            | $R_{FSET}$ = 61.9 kΩ, 415 kHz                                  |       |      | 0.09 | 0.24  | 0.43 | A/µs |

| Slane Compensation                           |                            | R <sub>FSET</sub> = 10.5 kΩ, 2 MHz                             |       |      | _    | 1.3   | _    | A/µs |

| Slope Compensation                           | S <sub>E</sub>             | R <sub>FSET</sub> = 261 kΩ, 100 kHz                            |       |      | _    | 0.035 | _    | A/µs |

|                                              |                            | R <sub>FSET</sub> = 61.9 kΩ, 415 kHz                           | A8652 |      | 0.07 | 0.15  | 0.23 | A/µs |

|                                              |                            | R <sub>FSET</sub> = 10.5 kΩ, 2 MHz                             |       |      | _    | 0.8   | _    | A/µs |

Continued on the next page...

# Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

ELECTRICAL CHARACTERISTICS (continued): Valid at 4 V  $\leq$  V<sub>IN</sub>  $\leq$  36 V; T<sub>A</sub> = 25°C; • indicates specifications guaranteed –40°C  $\leq$  T<sub>A</sub> = T<sub>J</sub>  $\leq$  150°C (unless noted otherwise).

| Characteristics                          | Symbol                    | Test Conditions                                                                                                             |   | Min. | Тур.               | Max. | Unit          |

|------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|---|------|--------------------|------|---------------|

| SOFT-START                               |                           |                                                                                                                             |   |      |                    |      |               |

| SS FAULT/HICCUP Reset Voltage            | V <sub>SS(RST)</sub>      | V <sub>SS</sub> falling due to R <sub>SS(FLT)</sub>                                                                         |   | _    | 200                | 275  | mV            |

| SS Maximum Charge Voltage                | V <sub>SS(MAX)</sub>      |                                                                                                                             |   | _    | 3.3                | _    | V             |

| SS Startup (Source) Current <sup>1</sup> | I <sub>SS(SU)</sub>       | HICCUP = FAULT = 0                                                                                                          |   | -30  | -20                | -10  | μA            |

| SS Hiccup (Sink) Current <sup>1</sup>    | I <sub>SS(HIC)</sub>      | HICCUP = 1                                                                                                                  |   | 1    | 2.2                | 5    | μA            |

| SS Pull-Down Resistance                  | R <sub>SS(FLT)</sub>      | FAULT = 1 or EN = 0                                                                                                         |   | _    | 2                  | _    | kΩ            |

|                                          |                           | 0 V < V <sub>FB</sub> < 200 mV                                                                                              |   | _    | f <sub>SW</sub> /4 | _    | _             |

| SS Switching Frequency                   | f <sub>SS</sub>           | 200 mV < V <sub>FB</sub> < 400 mV                                                                                           |   | -    | f <sub>SW</sub> /2 | _    | _             |

|                                          |                           | 400 mV < V <sub>FB</sub>                                                                                                    |   | _    | f <sub>SW</sub>    | _    | _             |

| HICCUP MODE                              |                           |                                                                                                                             |   |      |                    |      |               |

| Hiccup OCP Enable Threshold              | V <sub>HIC(EN)</sub>      | V <sub>SS</sub> rising                                                                                                      |   | _    | 2.3                | _    | V             |

| Hiccup, OCP Count                        | OCP <sub>LIM</sub>        | V <sub>SS</sub> > 2.3 V, OCP pulses                                                                                         |   | _    | 240                | _    | counts        |

| Hiccup, BOOT Shorted Count               | BOOT <sub>UV</sub>        |                                                                                                                             |   | _    | 64                 | _    | counts        |

| Hiccup, BOOT Open Count                  | BOOT <sub>OPEN</sub>      |                                                                                                                             |   | _    | 7                  | _    | counts        |

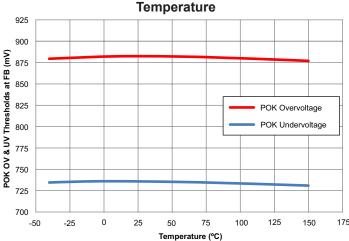

| POWER OK (POK) OUTPUT                    |                           |                                                                                                                             |   |      |                    |      |               |

| POK Output Voltage                       | V <sub>POK</sub>          | I <sub>POK</sub> = 4 mA                                                                                                     |   | _    | _                  | 0.4  | V             |

| POK Leakage <sup>1</sup>                 | I <sub>POK(LEAK)</sub>    | V <sub>POK</sub> = 5 V                                                                                                      | • | _    | _                  | 5    | μΑ            |

| POK UV Threshold                         | V <sub>POK(UV)</sub>      | V <sub>FB</sub> falling                                                                                                     | • | 715  | 740                | 760  | mV            |

| POK UV Hysteresis                        | V <sub>POK(UV,HYS)</sub>  |                                                                                                                             |   | _    | 10                 | _    | mV            |

|                                          |                           | V <sub>FB</sub> rising, V <sub>GADJ</sub> = 0 V                                                                             |   | 840  | 880                | 920  | mV            |

| POK OV Threshold                         | V <sub>POK(OV)</sub>      | $V_{FB}$ rising, $V_{ISEN+} - V_{ISEN-} = 25$ mV,<br>$V_{OUT} = 5$ V, $R_{GADJ} = 20$ k $\Omega$                            |   | 865  | 905                | 950  | mV            |

|                                          |                           | $V_{FB}$ rising, $V_{ISEN+} - V_{ISEN-} = 55$ mV, $V_{OUT} = 5$ V, $R_{GADJ} = 7.5$ k $\Omega$ , $R_{IADJ} = 20$ k $\Omega$ |   | _    | 1                  | _    | V             |

| POK OV Hysteresis                        | V <sub>POK(OV,HYS)</sub>  |                                                                                                                             |   | _    | 10                 | _    | mV            |

|                                          |                           | I <sub>SEN+</sub> rising, V <sub>GADJ</sub> = 0 V                                                                           |   | 5.4  | 5.65               | 6    | V             |

| ISEN+ OV Threshold                       | V <sub>ISEN(OV)</sub>     | $I_{SEN+}$ rising, $V_{ISEN+} - V_{ISEN-} = 25$ mV,<br>$V_{OUT} = 5$ V, $R_{GADJ} = 20$ kΩ, $R_{IADJ} = 20$ kΩ              |   | 5.6  | 5.8                | 6.1  | V             |

|                                          |                           | $I_{SEN+}$ rising, $V_{ISEN+} - V_{ISEN-} = 55$ mV,<br>$V_{OUT} = 5$ V, $R_{GADJ} = 7.5$ kΩ, $R_{IADJ} = 20$ kΩ             |   | _    | 6.45               | _    | V             |

| ISEN+ OV Hysteresis                      | V <sub>ISEN(OV,HYS)</sub> |                                                                                                                             |   | -    | 60                 | _    | mV            |

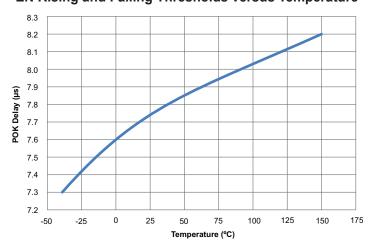

| POK Delay                                | t <sub>d(POK)</sub>       | V <sub>FB</sub> rising only                                                                                                 |   | -    | 7                  | _    | PWM<br>cycles |

| THERMAL PROTECTION                       |                           |                                                                                                                             |   |      |                    |      |               |

| TSD Rising Threshold                     | TSD                       | PWM stops immediately and COMP is pulled low and SS is reset                                                                |   | 155  | 170                | 185  | °C            |

| TSD Hysteresis <sup>3</sup>              | TSD <sub>HYS</sub>        |                                                                                                                             |   | _    | 20                 | _    | °C            |

Continued on the next page...

## Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

ELECTRICAL CHARACTERISTICS (continued): Valid at 4 V  $\leq$  V<sub>IN</sub>  $\leq$  36 V; T<sub>A</sub> = 25°C; • indicates specifications guaranteed –40°C  $\leq$  T<sub>A</sub> = T<sub>J</sub>  $\leq$  150°C (unless noted otherwise).

| Characteristics Symbol Test Conditions |                      |                                              |  |     | Тур. | Max. | Unit          |

|----------------------------------------|----------------------|----------------------------------------------|--|-----|------|------|---------------|

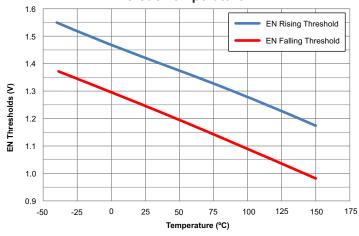

| EN INPUT THRESHOLDS                    |                      |                                              |  |     |      |      |               |

| EN High Threshold                      | V <sub>EN(H)</sub>   | EN rising                                    |  | _   | 1.41 | 2    | V             |

| EN Low Threshold                       | V <sub>EN(L)</sub>   | EN falling                                   |  | 0.7 | 1.36 | _    | V             |

| EN Delay                               | t <sub>d(EN)</sub>   | EN transitioning low, V <sub>OUT</sub> < 25% |  | -   | 60   | -    | PWM<br>cycles |

| EN Input Bias Current <sup>1</sup>     | I <sub>EN BIAS</sub> | EN = 5 V                                     |  | _   | 500  | _    | nA            |

<sup>1</sup> For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin or node.

<sup>&</sup>lt;sup>2</sup> Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>&</sup>lt;sup>3</sup> Ensured by design and characterization, not production tested.

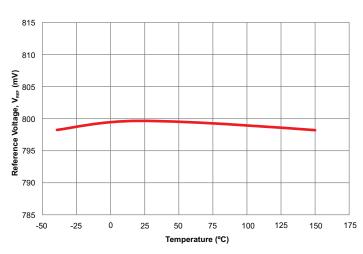

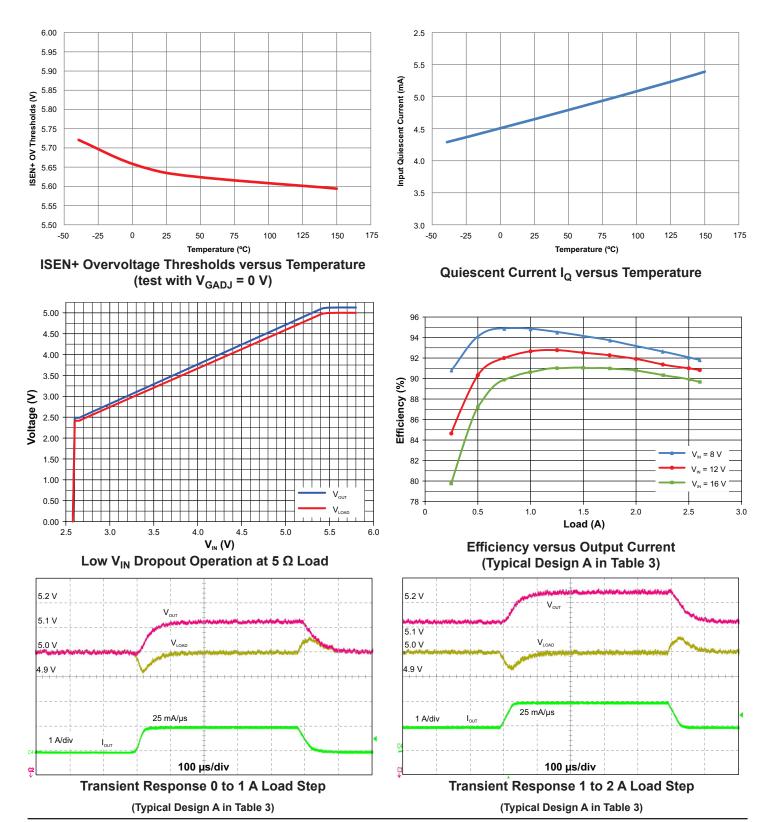

#### TYPICAL PERFORMANCE CHARACTERISTICS

**Reference Voltage versus Temperature**

3.50

3.25

START, UVLOSTART

STOP, UVLOSTART

2.75

-50 -25 0 25 50 75 100 125 150 175

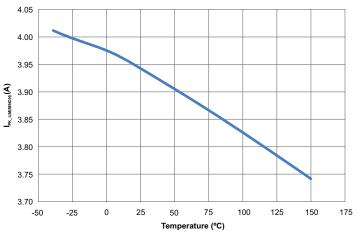

Pulse-by-Pulse Current Limit at t<sub>ON(MIN)</sub> (I<sub>PK\_LIM(MINON)</sub>) versus Temperature

VIN UVLO START and STOP Thresholds versus

Temperature

Temperature (°C)

**EN Rising and Falling Thresholds versus Temperature**

POK Overvoltage and Undervoltage Thresholds at FB versus Temperature (POK OV test with  $V_{GADJ} = 0 V$ )

**POK Delay Time versus Temperature**

#### **FUNCTIONAL DESCRIPTION**

#### Overview

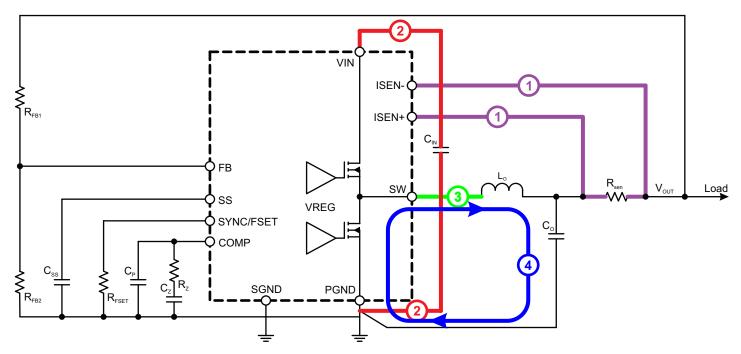

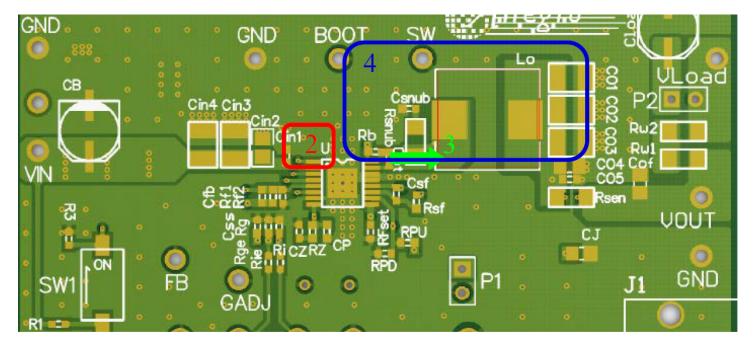

The A8652/53 is a synchronous PWM buck regulator that integrates low  $R_{DS(on)}\, high\mbox{-side}$  and low-side N-channel MOSFETs. It is designed to remain operational when input voltage falls as low as 2.6 V. The A8652/53 employs peak current mode control to provide superior line and load regulation, pulse-by-pulse current limit, fast transient response and simple compensation. The A8652/53 incorporates a Cable Drop Compensation (Remote Load Regulation) function in its current mode control architecture to adjust the output voltage according to the load current, offsetting the voltage drop introduced by the wiring harness. The reference voltage in the feedback loop is adjusted relative to the voltage across the sensing resistor at the load side. When the load current increases, it causes the reference voltage at the error amplifier to increase and the output voltage to follow. The gain of the voltage correction is configurable using the GADJ and IADJ pins. Such features provide flexibility in setting the amount of output voltage correction and the load current limit.

The features of the A8652/53 include Remote Load Regulation, an internal precision reference, an adjustable switching frequency, a transconductance error amplifier, an enable input, integrated top and bottom switching MOSFETs, adjustable soft-start time, pre-bias startup, and a Power OK output. Protection features of A8652/53 include  $\rm V_{IN}$  undervoltage lockout, pulse-by-pulse overcurrent protection, BOOT overvoltage and undervoltage protection, hiccup mode short-circuit protection, dynamic overvoltage protection, and thermal shutdown. In addition, the A8652/53 provides open-circuit, adjacent pin short-circuit, and pin-to-ground short-circuit protection.

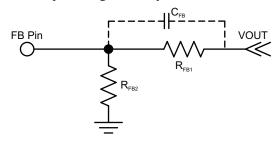

#### Reference Voltage

The A8652/53 incorporates an internal precision reference that allows output voltages as low as 0.8 V. The accuracy of the internal reference is  $\pm 1\%$  from  $-40^{\circ}\mathrm{C}$  to 125°C and  $\pm 1.5\%$  across from  $-40^{\circ}\mathrm{C}$  to 150°C when the Remote Load Regulation is disabled. The output voltage of the regulator is programmed with a resistor divider between  $V_{OUT}$  and the FB pin of the A8652/53.

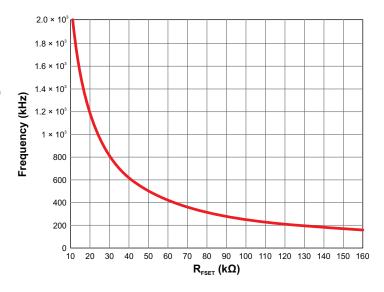

### Oscillator/Switching Frequency and Synchronization

The PWM switching frequency of the A8652/53 is adjustable from 100 kHz to 2.2 MHz and has an accuracy of about  $\pm 10\%$

over the operating temperature range. Connecting a resistor from the FSET/SYNC pin to GND, as shown in the Applications Schematic, sets the switching frequency. An FSET resistor with  $\pm 1\%$  tolerance is recommended. A graph of switching frequency versus FSET resistor value is shown in the Component Selection section of this datasheet. The A8652/53 will suspend operation if the FSET pin is shorted to GND or left open.

FSET/SYNC pin also can be used as a synchronization input that accepts an external clock to switch the A8652/53 from 100 kHz to 2.2 MHz and scales the slope compensation according to the synchronization frequency. When being used as a synchronization input, the applied clock pulses must satisfy the pulse width, duty cycle, and rise/fall time requirements shown in the Electrical Characteristics shown in this datasheet.

### Remote Load Regulation Control and Transconductance Error Amplifier

The Remote Load Regulation control in the A8652/53 provides improved load regulation at the remote load by increasing the voltage reference of the error amplifier to correct for the voltage drop introduced by wiring harness to the load. The amount of voltage correction is user-programmable with external configuration resistors, allowing the A8652/53 to be applied to wiring harnesses that have up to 750 mV IR drops at full load. The Remote Load Regulation controller has a variety of protection features, including a load-side current limit, a maximum regulation voltage, and protection in the event of open pin or shorted pin conditions.

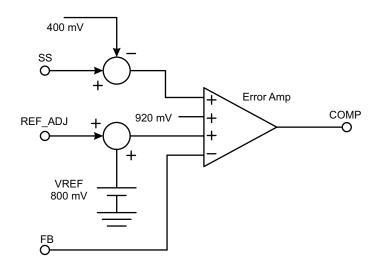

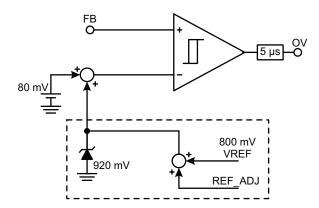

The Remote Load Regulation voltage correction and protection features interface with the error amplifier, which is a four terminal input device with three positive inputs and one negative input, as shown in Figure 1. The negative input is simply connected to the FB pin and is used to sense the feedback voltage for regulation. The error amplifier performs an "analog OR" selection between its positive inputs, operating according to the positive input with the lowest potential. The three positive inputs are used for soft-start, steady-state regulation, and the 15% maximum regulation voltage. The error amplifier regulates to the soft-start pin voltage minus 400 mV during startup, the sum of A8652/53 internal reference (VREF) and the Remote Load Regulation correction (REF\_ADJ) during normal operation, or the 920 mV maximum.

Figure 1: A8652/53 Error Amplifier

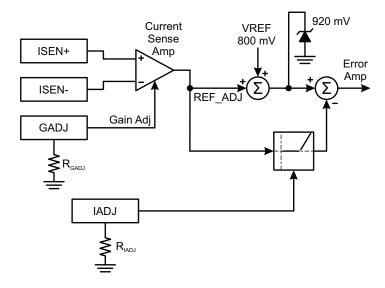

Figure 2: Remote Load Regulation Control

The amount of the voltage correction for the wiring harness is generated by the Remote Load Regulation control circuit and fed to the error amplifier via the REF\_ADJ signal, as shown in Figures 1 and 2. The Remote Load Regulation controller generates REF\_ADJ according to the load current sensed by ISEN+ and ISEN- and the gain set by the configuration resistors. The current sense resistor ( $R_{\rm sen}$ ) is connected on the load side between the regulator output capacitor and the load terminal and can have a value between 20 and 50  ${\rm m}\Omega$ .

The gain of the current sense to the REF\_ADJ ( $G_{ADJ}$ ) signal is set by the ratio of resistance to GND on the GADJ pin and the IADJ pin in conjunction with  $R_{sen}$ :

$$G_{ADJ} = \frac{REF\_ADJ}{I_{OUT}} = \frac{R_{sen} \times R_{IADJ}}{R_{GADJ}}$$

(1)

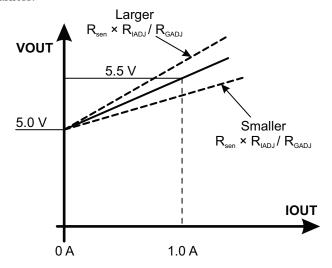

This allows the user to calibrate the voltage correction to the IR drop of the wiring harness, as shown in Figure 3. This calibration results in improved load regulation at the end of the wiring harness.

Figure 3: Voltage Correction Gain Adjustment

To configure the voltage correction gain, the load-side current limit ( $I_{OUT\_LIM}$ ) must first be set by the following equation (also referring to Table 1):

$$R_{IADJ} = \frac{1200}{I_{OUT,IJM} \times R_{crit}} \tag{2}$$

The voltage correction gain is based on  $R_{WIRE}$ , which is the sum of the wiring harness supply and return resistive paths as detailed in the typical application diagram. Given the gain of the FB pin voltage divider ( $A_{FB} = V_{OUT}/V_{FB}$ ),  $R_{WIRE}$  and  $R_{IADJ}$  the desired voltage correction gain is set by the following equation (referring to Figure 4):

$$R_{GADJ} = \frac{R_{sen}}{R_{WIRE}} \times A_{FB} \times R_{LADJ} \tag{3}$$

For example, for a 5 V application with a 20 m $\Omega$  current sense resistor and a 3 A load side current limit the IADJ configuration resistor would be 20 k $\Omega$ . To correct for a 125 mV wire harness drop at 1 A ( $R_{WIRE}$  =125 m $\Omega$ ) given  $R_{IADJ}$  = 20 k $\Omega$ , the GADJ configuration resistor should be 20 k $\Omega$ .

Table 1: R<sub>IADJ</sub> Resistor Selection vs. I<sub>OUT LIM</sub>

| R <sub>IADJ</sub> (kΩ) | R <sub>sen</sub> = 20 mΩ | R <sub>sen</sub> = 50 mΩ |

|------------------------|--------------------------|--------------------------|

| 15.8                   | 3.80                     | 1.52                     |

| 16.9                   | 3.55                     | 1.42                     |

| 17.4                   | 3.45                     | 1.38                     |

| 17.8                   | 3.37                     | 1.35                     |

| 18.2                   | 3.30                     | 1.32                     |

| 18.7                   | 3.21                     | 1.28                     |

| 19.1                   | 3.14                     | 1.26                     |

| 19.6                   | 3.06                     | 1.22                     |

| 20.0                   | 3.00                     | 1.20                     |

| 20.5                   | 2.93                     | 1.17                     |

| 21.0                   | 2.86                     | 1.14                     |

| 21.5                   | 2.79                     | 1.12                     |

| 22.1                   | 2.71                     | 1.09                     |

| 22.6                   | 2.65                     | 1.06                     |

| 23.2                   | 2.59                     | 1.03                     |

| 23.7                   | 2.53                     | 1.01                     |

| 24.3                   | 2.47                     | 0.99                     |

| 26.7                   | 2.25                     | 0.90                     |

| 30.1                   | 1.99                     | 0.80                     |

| 34.8                   | 1.72                     | 0.69                     |

| 40.2                   | 1.49                     | 0.60                     |

As will be discussed in further detail below, altering the GADJ resistance with an external voltage proportionally adjusts the voltage correction gain (Method 1, refer to Typical Application Diagram 2). On the other hand, altering the IADJ resistance with an external voltage proportionally adjusts the load-side current limit, and inversely proportionally adjusts the voltage correction gain (Method 2).

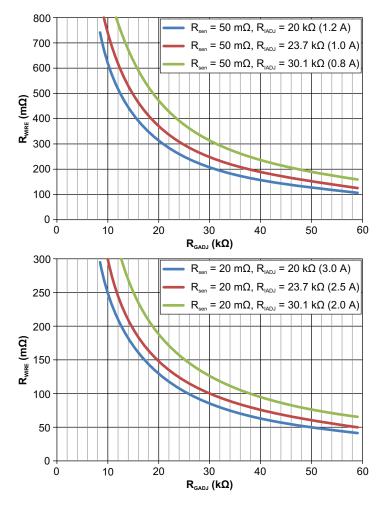

Figure 4: R<sub>GADJ</sub> Selection vs R<sub>WIRE</sub> for Given R<sub>sen</sub>, R<sub>IADJ</sub>

This can be very useful, for instance when one "universal" design is created for multiple platforms, where the expected wiring resistance can vary widely. The design can use this method in conjunction with the system controller such that the degree of voltage correction can be set via software.

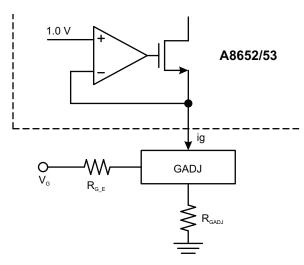

Figure 5: Dynamic Voltage Correction Adjustment at Pin GADJ

Figure 5 above illustrates how to adjust the amount of voltage correction by controlling  $V_G$ . The equivalent resistance  $R_{G\_eqv}$  at pin GADJ with respect to GND now becomes:

$$R_{G_{\_eqv}} = \frac{1}{\left(\frac{1}{R_{GADJ}} - \frac{V_G - 1}{R_{GE}}\right)}$$

(4)

The voltage correction gain  $(G_{ADJ})$  then varies linearly with the applied  $V_G$  for given  $R_{GADJ}$  and  $R_{G\_E}$ . Normalizing this gain to the case with only  $R_{GADJ}$  connecting to pin GADJ results in:

$$G_{norm} = 1 + \frac{R_{GADJ}}{R_{G.E}} - \frac{R_{GADJ}}{R_{G.E}} V_G$$

(5)

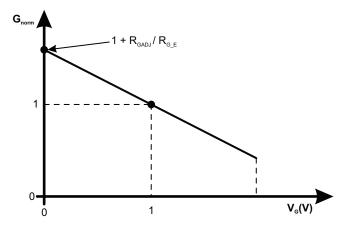

Figure 6: Normalized Gain G<sub>norm</sub> vs. V<sub>G</sub>

The minimum and maximum voltage correction can be adjusted with the ratio of  $R_{GADJ}$  and  $R_{G\_E}$  for a given controlling voltage  $(V_G)$  range.

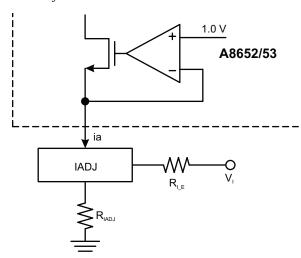

Similarly, as shown in Figure 7, Method 2 can inversely proportionally adjust the voltage correction gain for a fixed GADJ resistance, at the same time proportionally adjusts the load side current limit ( $I_{OUT\_LIM}$ ) by applying the control voltage ( $V_I$ ) to the IADJ pin. The equivalent resistance RIADJ at pin IADJ is:

$$R_{I_{\underline{eqv}}} = \frac{1}{\left(\frac{1}{R_{MDI}} - \frac{V_{I} - 1}{R_{I,F}}\right)} \tag{6}$$

Thus, the voltage correction gain can be kept the same by applying a separate control voltage to the GADJ pin to keep the GADJ and IADJ resistor ratio the same if only load-side current limit needs to be adjusted.

Figure 7: Simultaneous Voltage Correction and Load-Side Current Limit Adjustment at Pin IADJ

If a fixed load-side current limit is desired it is simpler to use GADJ pin to dynamically control the amount of voltage correction because of linear control and only altering the voltage correction gain.

The GADJ and IADJ pins are designed for a resistance range of 10 to 34 k $\Omega$ , and therefore the controlling voltage  $V_G$  and  $V_I$  must be limited as follows:

$$10 k\Omega < R_{G eqv} < 34 k\Omega \tag{7}$$

and

$$10 k\Omega < R_{Leav} < 34 k\Omega \tag{8}$$

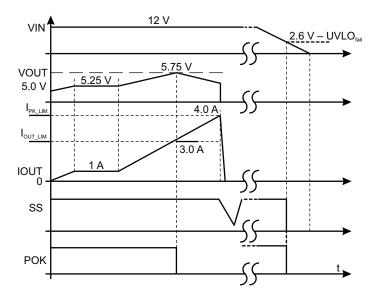

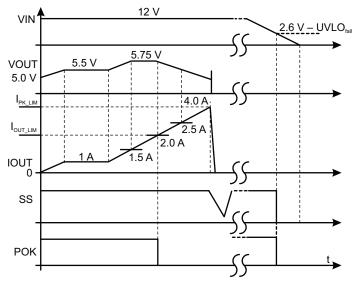

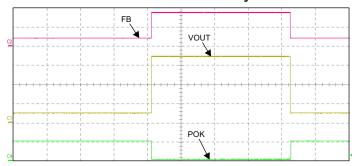

In addition to the voltage correction circuitry, Figure 2 also details the load-side current limit ( $I_{OUT\_LIM}$ ), which is configured independently by the resistance to GND on the IADJ pin. As shown by Figure 8 and 9, when the load current exceeds  $I_{OUT\_LIM}$ , POK is pulled low to flag the condition, and the output voltage is decreased at the same rate as the voltage correction (set by Rsen,  $R_{GADJ}$  and  $R_{IADJ}$ ) to protect against unstable behavior. Figure 8 and 9 also details the operation of peak inductor current limit ( $I_{PK\_LIM}$ ), which monitors the inductor current and will enter into hiccup mode after 240 counts of exceeding  $I_{PK\_LIM}$  for robust protection and against the output voltage shorted to GND.

Figure 8: POK and Load-Side Current Limit Timing

In addition to current protection, the A8652/53 also includes a 115% (5.75 V) regulation voltage limit on the error amplifier. This protection feature prevents the excessive output voltages during fault conditions and is therefore set above the operating range of the Remote Load Regulation. However, if the voltage correction gain is too high, the 115% voltage limit will impede the Remote Load Regulation operation, as shown in Figure 9. The VOUT waveform shows the operation point of the Remote Load Regulation controller set by REF\_ADJ, but as illustrated, the 115% voltage regulation limit at the error amplifier clips the output voltage to 5.75 V.

Figure 9: Excessive Voltage Correction Gain

The Remote Load Regulation controller is also robust against pin faults, such as adjacent pins shorting, shorting pins to GND, or pin open faults. When a pin fault is detected, either the IADJ or GADJ pin, the A8652/53 will default to the 800 mV reference, not applying any voltage correction to the output voltage. Given this, the GADJ pin can be connected to GND to disable the Remote Load Regulation function.

#### **Compensation Components**

To stabilize the regulator, a series RC compensation network  $(R_Z \text{ and } C_Z)$  must be connected from the error amplifier output (COMP pin) to GND as shown in the applications schematic. In most instances, an additional low-value capacitor  $(C_P)$  should be connected in parallel with the  $R_Z$ - $C_Z$  compensation network to reduce the loop gain at very high frequencies. However, if the  $C_P$  capacitor is too large, the phase margin of the converter may be reduced. How to calculate  $R_Z$ ,  $C_Z$  and  $C_P$  is covered in the Component Selection section of this datasheet. When selecting the compensation components, the load decoupling capacitance and the wiring resistance must be taken into consideration.

If a fault occurs or the regulator is disabled, the COMP pin is pulled to GND via the approximately 1  $k\Omega$  internal resistor and PWM switching is inhibited.

### Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

#### **Slope Compensation**

The A8652/53 incorporates internal slope compensation to allow PWM duty cycles above 50% for a wide range of input/output voltages, switching frequencies, and inductor values. As shown in the functional block diagram, the slope compensation signal is added to the sum of the current sense and PWM Ramp Offset. The amount of slope compensation is scaled with the switching frequency when programming the frequency with a resistor or with an external clock.

The value of the output inductor should be chosen such that slope compensation rate  $S_E$  is between  $0.5 \times$  and  $1 \times$  the falling slope of the inductor current  $(S_F)$ .

#### **Current Sense Amplifier**

The A8652/53 incorporates a high-bandwidth current sense amplifier to monitor the current through the top MOSFET. This current signal is used to regulate the peak current when the top MOSFET is turned on. The current signal is also used by the protection circuitry for the pulse-by-pulse current limit ( $I_{PK\_LIM}$ ) and hiccup mode short-circuit protection.

#### Low Dropout Operation and Undervoltage Lockout

The Undervoltage Lockout behavior is described in the following Protection Features section.

The A8652/53 is designed to allow operation when input voltage drops as low as 2.6 V, which is the UVLO STOP threshold. When the input voltage falls towards the nominal output voltage, the high-side switch can remain on for maximum on-time to keep regulating the output. This is accomplished by decreasing the  $f_{\rm SW}$  switching frequency. In this way, the dropout from the input to output voltage is minimized.

#### Sleep Mode with Enable input

The A8652/53 provides a shutdown function via the EN pin. When this pin is low, the A8652/53 is shut down and the A8652/53 will enter a "sleep mode" where the internal control circuits will be shut off and draw less current from VIN. If EN goes high, the A8652/53 will turn on and provided there are no fault conditions, soft-start will be initiated and  $V_{OUT}$  will ramp to its final voltage in a time set by the soft-start capacitor ( $C_{SS}$ ). To automatically enable the A8652/53, the EN pin may be connected directly to VIN.

#### **Power MOSFETs**

The A8652/53 includes an 80 m $\Omega$ , high-side N-channel MOSFET capable of delivering up to 4 A typical. The A8652/53 also includes a 55 m $\Omega$ , low-side N-channel MOSFET to provide synchronous rectification.

When the A8652/53 is disabled via the EN input being low or a Fault condition, the A8652/53 output stage is tri-stated by turning off both the upper and lower MOSFETs.

#### Pulse-Width Modulation (PWM) Mode

The A8652/53 employs fixed-frequency, peak current mode control to provide excellent load and line regulation, fast transient response, and simple compensation.

A high-speed comparator and control logic is included in A8652/53. The inverting input of the PWM comparator is connected to the output of the error amplifier. The non-inverting input is connected to the sum of the current sense signal, the slope compensation signal, and a DC PWM Ramp offset voltage (V<sub>PWM(OFFSET)</sub>).

At the beginning of each PWM cycle, the CLK signal sets the PWM flip-flop, the bottom MOSFET is turned off, the top MOSFET is turned on, and the inductor current increases. When the voltage at the non-inverting of PWM comparator rises above the error amplifier output COMP, the PWM flip-flop is reset and the top MOSFET is turned off, the bottom MOSFET is turned on and the inductor current decreases.

The PWM flip-flop is reset-dominant, so the error amplifier may override the CLK signal in certain situations.

#### **BOOT Regulator**

The A8652/53 includes a regulator to charge its boot capacitor. The voltage across the boot capacitor is typically 5 V. If the boot capacitor is missing, the A8652/53 will detect a boot overvoltage. Similarly, if the boot capacitor is shorted, the A8652/53 will detect a boot undervoltage. Also, the boot regulator has a current limit to protect itself during a short-circuit condition.

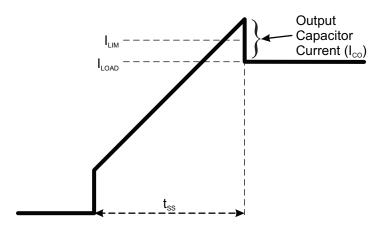

#### Soft-Start (Startup) and Inrush Current Control

The soft-start function controls the inrush current at startup. The soft-start pin, SS, is connected to GND via a capacitor. When the A8652/53 is enabled and all faults are cleared, the soft-start pin will source the charging current  $I_{\rm SS(SU)}$ , and the voltage on the

### Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

soft-start capacitor,  $C_{SS}$ , will ramp upward from 0 V. When the voltage at the soft-start pin exceeds the Soft-Start COMP Release Threshold ( $V_{SS(RELEASE)}$ , typically 400 mV) the error amplifier will ramp up its output voltage above the PWM Ramp Offset. At that instant, the top and bottom MOSFETs will begin switching. There is a small delay ( $t_{d(SS)}$ ) between the moments of EN pin transitioning high and the soft-start voltage reaching 400mV to initiate PWM switching.

Once the A8652/53 begins PWM switching, the error amplifier will regulate the voltage at the FB pin to the soft-start pin voltage minus approximately 400 mV. During the active portion of soft-start, the voltage at the SS pin will rise from 400 mV to 1.2 V (a difference of 800 mV), the voltage at the FB pin will rise from 0 V to 800 mV, and the regulator output voltage will rise from 0 V to the setpoint determined by the feedback resistor divider.

During startup, the PWM switching frequency is reduced to 25% of  $f_{SW}$  while  $V_{FB}$  is below 200 mV. If  $V_{FB}$  is above 200 mV but below 400 mV, the switching frequency is 50% of  $f_{SW}$ . At the same time, the transconductance of the error amplifier,  $gm_{EA}$ , is reduced to 1/2 of nominal value when  $V_{FB}$  is below 400 mV. When  $V_{FB}$  is above 400 mV, the switching frequency will be  $f_{SW}$  and the error amplifier gain will be the nominal value. The reduced switching frequencies and error amplifier gain are necessary to help improve output regulation and stability when  $V_{OUT}$  is at very low voltage. When  $V_{OUT}$  is very low, the PWM control loop requires on-time near the minimum controllable on-time and extra low duty cycles that are not possible at the nominal switching frequency.

When the voltage at the soft-start pin reaches approximately 1.2 V, the error amplifier will "switch over" and begin regulating the voltage at the FB pin to the A8652/53 adjusted reference voltage. The voltage at the soft-start pin will continue to rise to the internal LDO regulator output voltage.

If the A8652/53 is disabled or a fault occurs, the internal fault latch is set and the capacitor at the SS pin is discharged to ground very quickly through a 2 k $\Omega$  pull-down resistor. The A8652/53 will clear the internal fault latch when the voltage at the SS pin decays to approximately 200 mV. However, if the A8652/53 enters hiccup mode, the capacitor at the SS pin is slowly discharged through a current sink,  $I_{\rm SS(HIC)}$ . Therefore, the soft-start capacitor  $C_{\rm SS}$  not only controls the startup time but also the time between soft-start attempts in hiccup mode.

#### **Pre-Biased Startup**

If the output of the buck regulator is pre-biased at certain output voltage level, the A8652/53 will modify the normal startup routine to prevent discharging the output capacitors. As described in the Soft-Start (Startup) and Inrush Current Control section, the error amplifier usually becomes active when the voltage at the soft-start pin exceeds 400 mV. If the output is pre-biased, the voltage at the FB pin will be non-zero. The A8652/53 will not start switching until the voltage at SS pin rises to approximately  $V_{\rm FB}+400$  mV. From then on, the error amplifier becomes active, the voltage at the COMP pin rises, PWM switching starts, and  $V_{\rm OUT}$  will ramp upward from the pre-bias level.

#### Power OK (POK) Output

The Power OK (POK) output is an open-drain output, so an external pull-up resistor must be connected. POK remains high when the voltage at the FB pin is within regulation and the load-side current limit  $I_{out\_LIM}$  is not triggered. The POK output is pulled low under the conditions below:

- 1.  $V_{FB(RISING)} < 92.5\%$  of the reference voltage  $V_{REF}$

- 2.  $V_{FB(RISING)}$  is larger than the sum of the adjusted reference voltage (i.e.  $V_{REF} + V_{REF\_ADJ}$  or 920 mV, whichever is lower) and 80 mV

- 3. Load current exceeds the load-side current limit I<sub>out LIM</sub>

- 4. EN is low for more than 32 PWM cycles

- 5. V<sub>IN</sub> UVLO event occurs

- 6. Thermal shutdown event occurs

Once the load-side current limit is triggered, POK will go low even if the output voltage has not yet dropped due to the current limit. If the A8652/53 is running and EN is kept low for more than 32 PWM cycles, POK will fall low and remain low only as long as the internal circuitry is able to enhance the open-drain output device. Once  $V_{\rm IN}$  fully collapses, POK will return to the high-impedance state. Hysteresis is included in POK comparators to prevent chattering due to the ripple effects on comparators' input terminals.

#### **PROTECTION FEATURES**

The A8652/53 was designed to satisfy the most demanding automotive and nonautomotive applications. In this section, a description of each protection feature is described, and Table 2 summarizes the protections and their operation.

#### **Undervoltage Lockout Protection (UVLO)**

An Undervoltage Lockout (UVLO) comparator in the A8652/53 monitors the voltage at the VIN pin and keeps the regulator disabled if the voltage is below the START threshold ( $V_{\rm UVLO(START)}$ ,  $V_{\rm IN}$  rising) or the STOP threshold ( $V_{\rm UVLO(STOP)}$ ,  $V_{\rm IN}$  falling). The UVLO comparator incorporates some hysteresis,  $V_{\rm UVLO(HYS)}$ , to help reduce ON/OFF cycling of the regulator due to the resistive or inductive drops in the VIN path during heavy loading or during startup.

#### **Pulse-by-Pulse Overcurrent Protection (OCP)**

The A8652/53 monitors the current in the upper MOSFET, and if this current exceeds the pulse-by-pulse overcurrent threshold ( $I_{PK\_LIM}$ ), then the upper MOSFET is turned off. Normal PWM operation resumes on the next clock pulse from the oscillator. The A8652/53 includes leading-edge blanking to prevent falsely triggering the pulse-by-pulse current limit when the upper MOSFET is turned on.

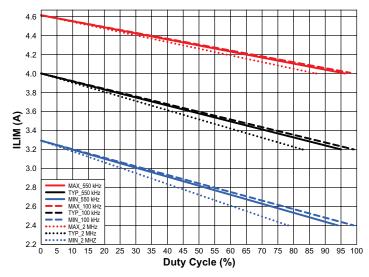

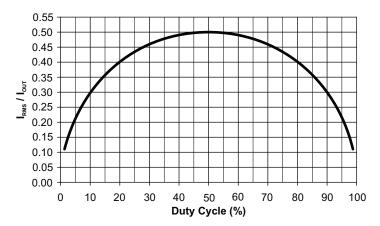

Figure 10: Pulse-by-Pulse Current Limit vs. Duty Cycle at 100 kHz (long dashed lines), 550 kHz (solid lines) and 2 MHz (short dashed lines)

Because of the addition of the slope compensation ramp to the inductor current, the A8652/53 can deliver more current at lower duty cycles than at higher duty cycles to activate pulse-by-pulse overcurrent protection. Also, the slope compensation is not a perfectly linear function of switching frequency, so the current limit at lower switching frequency is larger compared with the limit at higher switching frequency for a given duty cycle.

Figure 10 shows the typical and worst-case pulse-by-pulse current limits versus duty cycles at 2 MHz, 550 kHz, and 100 kHz.

The exact current the buck regulators can support is heavily dependent on duty cycle ( $V_{IN}, V_{OUT}$ ), ambient temperature, thermal resistance of the PCB, airflow, component selection, and nearby heat sources.

### Overcurrent Protection (OCP) and Hiccup Mode

An OCP counter and hiccup mode circuit protect the buck regulator when the output of the regulator is shorted to ground or when the load current is too high. When the voltage at the SS pin is below the Hiccup OCP Threshold, the hiccup mode counter is disabled. Two conditions must be met for the OCP counter to be enabled and begin counting:

- 1.  $V_{SS} > V_{HIC(EN)}$  (2.3 V) and

- 2.  $V_{COMP}$  clamped at its maximum voltage (OCL = 1)

As long as these two conditions are met, the OCP counter remains enabled and will count pulses from the overcurrent comparator. If the COMP voltage decreases (OCL = 0) the OCP counter is cleared. If the OCP counter reaches OCP<sub>LIM</sub> counts (240), a hiccup latch is set, and the COMP pin is quickly pulled down by a relatively low resistance (1 k $\Omega$ ).

The hiccup latch also enables a small current sink connected to the SS pin ( $I_{SS(HIC)}$ ). This causes the voltage at the soft start pin to slowly ramp downward. When the voltage at the soft-start pin decays to a low-enough level ( $V_{SS(RST)}$ , 200 mV $_{TYP}$ ), the hiccup latch is cleared and the small current sink turned off. At that instant, the SS pin will begin to source current ( $I_{SS(SU)}$ ) and the voltage at the SS pin will ramp upward. This marks the beginning of a new, normal soft-start cycle as described earlier. When the voltage at the soft-start pin exceeds the error amp voltage by approximately 400 mV, the error amp will force the voltage at the COMP pin to quickly slew upward and PWM switching will resume. If the short circuit at the regulator's output remains,

### Wide Input Voltage, Synchronous USB Buck Regulator with Remote Load Regulation

another hiccup cycle will occur. Hiccups will repeat until the short circuit is removed or the converter is disabled. If the short circuit is removed, the A8652/53 will soft-start normally and the output voltage will automatically recover to the desired level.

Thus, Hiccup mode is a very effective protection for the overload condition. It can avoid false trigger for a short-term overload. On the other hand, for the extended overload, the average power dissipation during Hiccup operation is very low to keep the controller cool and enhance the reliability.

Note that OCP is the only fault that results in Hiccup mode being ignored while  $V_{SS} \le 2.3 \text{ V}$ .

#### **BOOT Capacitor Protection**

The A8652/53 monitors the voltage across the BOOT capacitor to detect if the capacitor is missing or short-circuited. If the BOOT capacitor is missing, the regulator will enter Hiccup mode after 7 PWM cycles. If the BOOT capacitor is short-circuited, the regulator will enter Hiccup mode after 64 PWM cycles.

For a BOOT fault, Hiccup mode will operate virtually the same as described previously for an output short-circuit fault (OCP), with SS ramping up and down as a timer to initiate repeated soft-start attempts. BOOT faults are nonlatched condition, so the A8652/53 will automatically recover when the fault is corrected.

#### **Dynamic Overvoltage Protection (OVP)**

In addition to the error amp regulation voltage clamp ( $V_{EA(CLAMP)}$ ) at 115%, the A8652/53 includes a dynamic overvoltage protection feature where the overvoltage threshold changes with the correction voltage. As shown in Figure 11 below, the A8652/53 also includes an overvoltage comparator that monitors the FB pin and the sum of the adjusted reference voltage (i.e.  $V_{REF} + V_{REF\_ADJ}$  or 920 mV, whichever is lower) and 80 mV. In this way, the overvoltage threshold will dynamically change with the amount of the correction voltage and the threshold is always 0.5 V above the output voltage. For example, OVP threshold is 5.5 V when  $V_{OUT} = 5$  V at  $I_{OUT} = 0$  A; the OVP threshold will be 5.75 V when  $V_{OUT} = 5.25$  V at  $I_{OUT} = 1$  A; if  $V_{OUT} = 5.75$  V at certain load, the OVP threshold will become 6.25 V. When the Remote Load Regulation function is disabled due to some reason (e.g., IADJ or GADJ pin fault or general non-

Figure 11: Dynamic Overvoltage Protection

USB buck application), the OVP threshold will be 5.5 V; when the output voltage reaches the 115% regulation limit, the OVP threshold will reach the maximum value of 6.25 V.

When the voltage at the FB pin exceeds the overvoltage threshold (V<sub>POK(OV)</sub>), A8652/53 will stop PWM switching, i.e. both high and side switches will be turned off, and POK will be pulled low. In most cases, the error amplifier will be able to maintain regulation since the synchronous output stage has excellent sink and source capability. However, the error amplifier and its regulation voltage clamp are not effective when the FB pin is disconnected or when the output is shorted to the input supply. When the FB pin is disconnected from the feedback resistor divider, a tiny internal current source will force the voltage at the FB pin to rise above V<sub>POK(OV)</sub> and disable the regulator, preventing the load from being significantly overvoltage. If a higher external voltage is accidently shorted to the A8652/53's output, V<sub>FB</sub> will rise above the overvoltage threshold, triggering an OVP event and thus protecting the low-side switch. In either case, if the conditions causing the overvoltage are corrected, the regulator will automatically recover.

To provide additional protection when the battery is shorted to the load terminal, a 40 V Schottky diode (D) can be inserted after sensing resistor  $R_{sen}$  to block the high voltage entering into IC, and a Zener diode is placed at FB pin, as shown in Figure 12. The test result was shown in Figure 12b when Battery = 36 V was shorted to  $V_{OUT}$ .

Figure 12a: Protection Circuitry for Load Short-to-Battery

Figure 12b: Test Results when Battery = 36 V is Shorted to V<sub>OUT</sub>

Ch1: V<sub>OUT</sub> (10 V/div); Ch2: V<sub>FB</sub> (2 V/div); Ch4: V<sub>POK</sub> (5 V/div); 50 ms/div

#### Thermal Shutdown (TSD)

The A8652/53 monitors its junction temperature and will stop PWM switching and pull POK low if it becomes too hot. Also, to prepare for a restart, the SS and COMP pins will be pulled low until  $V_{\rm SS} < V_{\rm SS(RST)}$ . TSD is a non-latched fault so the A8652/53 will automatically recover if the junction temperature decreases by approximately 20°C.

### Pin-to-Ground and Pin-to-Pin Short Protections

The A8652/53 was designed to satisfy the most demanding automotive and nonautomotive applications. For example, the A8652/53 was carefully designed "up front" to withstand a short circuit to ground at each pin without suffering damage.

In addition, care was taken when defining the A8652/53's pinouts to optimize protection against pin-to-pin adjacent short-circuits. For example, logic pins and high-voltage pins were separated as much as possible. Inevitably, some low-voltage pins were located adjacent to high-voltage pins. In these instances, the low-voltage pins were designed to withstand increased voltages, with clamps and/or series input resistance, to prevent damage to the A8652/53.

Table 2: Summary of A8652/53 Fault Modes and Operation

|                                          |                                                                                         |                                                                                        | During Far                                                                             | ult Count, before           | Hiccup                         | Dues: 1                                                              |                                      | POOT                         |                                 |                               |

|------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------|--------------------------------|----------------------------------------------------------------------|--------------------------------------|------------------------------|---------------------------------|-------------------------------|

| Fault Mode                               | Fault Cases                                                                             | V <sub>SS</sub>                                                                        | V <sub>COMP</sub>                                                                      | High-Side<br>Switch         | Low-Side<br>Switch             | - Dropout<br>Foldback                                                | РОК                                  | BOOT<br>Charging             | LATCH                           | RESET                         |

| Positive<br>Overcurrent<br>Protection    | Excessive I <sub>OUT</sub> V <sub>OUT</sub> Shorted to GND     SW Soft Short     To GND | Hiccup, after 240 faults of OCL                                                        | Clamped to<br>achieve I <sub>LIM</sub> , and<br>pulled low only by<br>hiccup           | CCM<br>according to<br>COMP | CCM<br>according to<br>COMP    | f <sub>SW</sub> /4 or f <sub>SW</sub> /2<br>based on V <sub>FB</sub> | Depends on V <sub>OUT</sub> and ISEN | Not<br>affected              | No                              | Auto,<br>remove<br>short      |

| Load-Side<br>Current Limit               | Excessive I <sub>OUT</sub>                                                              | Not affected                                                                           | Not affected                                                                           | CCM<br>according to<br>COMP | CCM according to COMP          | Not affected                                                         | Pulled Low immediately               | Not<br>affected              | No                              | Auto                          |

| Negative<br>Overcurrent<br>Protection    | Excessive     Negative I <sub>OUT</sub> Inductor Short                                  | Hiccup, after 1 fault of LSOC                                                          | Pulled low only by hiccup                                                              | Forced off<br>Immediately   | Forced off<br>Immediately      | Dropout<br>Foldback<br>Reset                                         | Depends on V <sub>OUT</sub> and ISEN | Not<br>affected              | No                              | Auto,<br>remove<br>short      |

| SW Hard<br>Short to GND                  | SW to GND hard<br>Short                                                                 | Hiccup at the end of blankOn                                                           | Pulled low only by hiccup                                                              | Forced off<br>Immediately   | One Shot<br>Diode<br>Emulation | Dropout<br>Foldback<br>Reset                                         | Depends on V <sub>OUT</sub> and ISEN | Not<br>affected              | No<br>(option<br>avail<br>able) | Auto,<br>remove<br>short      |

| Thermal<br>Shutdown                      | Die is too hot                                                                          | Pulled Low<br>Immediately &<br>latched until V <sub>SS</sub><br>< V <sub>SS(RST)</sub> | Pulled Low<br>Immediately &<br>latched until V <sub>SS</sub><br>< V <sub>SS(RST)</sub> | Forced off<br>Immediately   | Forced off<br>Immediately      | Dropout<br>Foldback<br>Reset                                         | Pulled Low<br>Immediately            | Off                          | No                              | Auto,<br>Cool<br>Down         |

| Boot<br>Capacitor<br>Greater than<br>7 V | BOOT capacitor<br>Open                                                                  | Hiccup, after 7 latched faults                                                         | Pulled low by hiccup                                                                   | CCM<br>according to<br>COMP | CCM<br>according to<br>COMP    | Dropout<br>Foldback<br>Disabled by<br>Hiccup                         | Depends on V <sub>OUT</sub> and ISEN | Off for rest of period       | -                               | -                             |

| Boot<br>Capacitor On<br>Fault            | BOOT Capacitor<br>Open                                                                  | Hiccup, after 7 latched faults                                                         | Pulled low by hiccup                                                                   | CCM<br>according to<br>COMP | CCM<br>according to<br>COMP    | Dropout<br>Foldback<br>Disabled by<br>Hiccup                         | Depends on V <sub>OUT</sub> and ISEN | Off only<br>during<br>hiccup | No                              | Auto,<br>replace<br>capacitor |

| Boot<br>Capacitor<br>Overcurrent         | BOOT to GND<br>Short                                                                    | Not affected                                                                           | Not affected                                                                           | Not affected                | Pulsed at minOff               | Not affected                                                         | Depends on V <sub>OUT</sub> and ISEN | Off until fault clears       | -                               | -                             |