# 16-bit Proprietary Microcontroller

CMOS

# F<sup>2</sup>MC-16FX MB96340 Series

### MB96345/346 MB96F345 \*1 MB96F346/F347/F348

### DESCRIPTION

MB96340 series is based on Fujitsu's advanced 16FX architecture (16-bit with instruction pipeline for RISC-like performance). The CPU uses the same instruction set as the established 16LX series - thus allowing for easy migration of 16LX Software to the new 16FX products. 16FX improvements compared to the previous generation include significantly improved performance - even at the same operation frequency, reduced power consumption and faster start-up time.

For highest processing speed at optimized power consumption an internal PLL can be selected to supply the CPU with up to 56MHz operation frequency from an external 4MHz resonator. The result is a minimum instruction cycle time of 17.8ns going together with excellent EMI behavior. An on-chip clock modulation circuit significantly reduces emission peaks in the frequency spectrum. The emitted power is minimized by the on-chip voltage regulator that reduces the internal CPU voltage. A flexible clock tree allows to select suitable operation frequencies for peripheral resources independent of the CPU speed.

\*1: These devices are under development and specification is preliminary. These products under development may change its specification without notice.

Note: F<sup>2</sup>MC is the abbreviation of Fujitsu Flexible Microcontroller

For the information for microcontroller support, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

Copyright©2009 FUJITSU MICROELECTRONICS LIMITED All rights reserved 2009.6

#### ■ FEATURES

| Feature                        | Description                                                                                                                                                                                          |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                     | • 0.18μm CMOS                                                                                                                                                                                        |

|                                | • F <sup>2</sup> MC-16FX CPU                                                                                                                                                                         |

|                                | <ul> <li>Up to 56 MHz internal, 17.8 ns instruction cycle time</li> </ul>                                                                                                                            |

| CPU                            | • Optimized instruction set for controller applications (bit, byte, word and long-word data types; 23 different addressing modes; barrel shift; variety of pointers)                                 |

|                                | 8-byte instruction execution queue                                                                                                                                                                   |

|                                | <ul> <li>Signed multiply (16-bit × 16-bit) and divide (32-bit/16-bit) instructions available</li> </ul>                                                                                              |

|                                | <ul> <li>On-chip PLL clock multiplier (x1 - x25, x1 when PLL stop)</li> </ul>                                                                                                                        |

|                                | • 3 MHz - 16 MHz external crystal oscillator clock (maximum frequency when using ceramic resonator depends on Q-factor).                                                                             |

|                                | <ul> <li>Up to 56 MHz external clock for devices with fast clock input feature</li> </ul>                                                                                                            |

|                                | <ul> <li>32-100 kHz subsystem quartz clock</li> </ul>                                                                                                                                                |

| System clock                   | <ul> <li>100kHz/2MHz internal RC clock for quick and safe startup, oscillator stop<br/>detection, watchdog</li> </ul>                                                                                |

|                                | <ul> <li>Clock source selectable from main- and subclock oscillator (part number suffix<br/>"W") and on-chip RC oscillator, independently for CPU and 2 clock domains of<br/>peripherals.</li> </ul> |

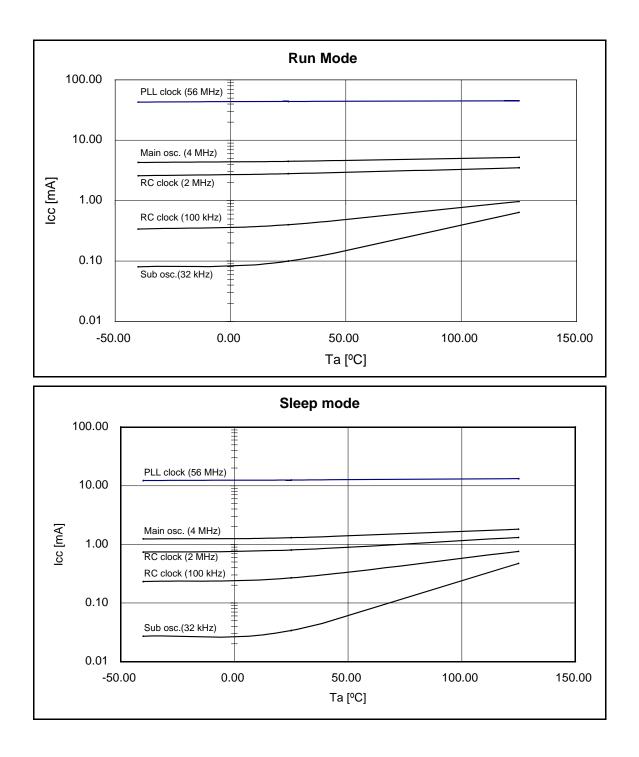

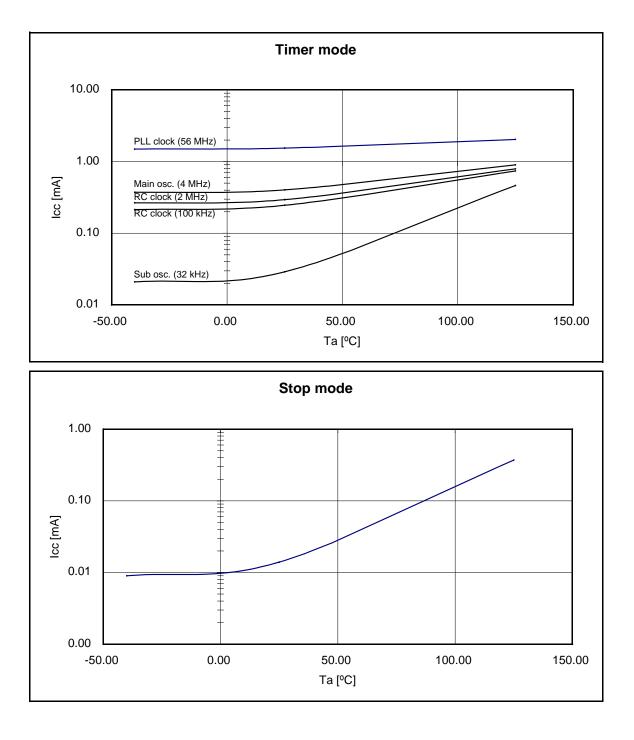

|                                | Low Power Consumption - 13 operating modes : (different Run, Sleep, Timer modes, Stop mode)                                                                                                          |

|                                | Clock modulator                                                                                                                                                                                      |

| On-chip voltage regula-<br>tor | <ul> <li>Internal voltage regulator supports reduced internal MCU voltage, offering low EMI<br/>and low power consumption figures</li> </ul>                                                         |

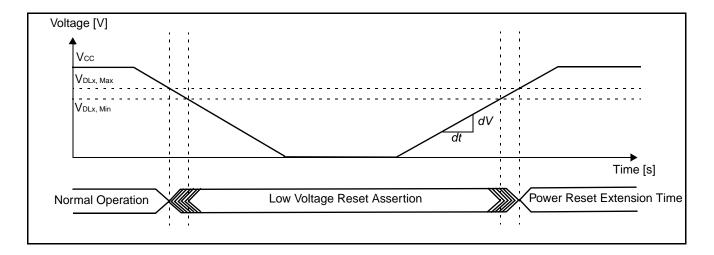

| Low voltage reset              | <ul> <li>Reset is generated when supply voltage is below minimum.</li> </ul>                                                                                                                         |

| Code Security                  | Protects ROM content from unintended read-out                                                                                                                                                        |

| Momony Dotah Function          | Replaces ROM content                                                                                                                                                                                 |

| Memory Patch Function          | <ul> <li>Can also be used to implement embedded debug support</li> </ul>                                                                                                                             |

| DMA                            | Automatic transfer function independent of CPU, can be assigned freely to resources                                                                                                                  |

|                                | Fast Interrupt processing                                                                                                                                                                            |

| Interrupts                     | 8 programmable priority levels                                                                                                                                                                       |

|                                | Non-Maskable Interrupt (NMI)                                                                                                                                                                         |

|                                | Three independent clock timers (23-bit RC clock timer, 23-bit Main clock timer,                                                                                                                      |

| Timers                         | 17-bit Sub clock timer)                                                                                                                                                                              |

|                                | Watchdog Timer                                                                                                                                                                                       |

| Feature                                     | Description                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | Supports CAN protocol version 2.0 part A and B                                                                                                                                                                                                                                                                  |

|                                             | ISO16845 certified                                                                                                                                                                                                                                                                                              |

|                                             | Bit rates up to 1 Mbit/s                                                                                                                                                                                                                                                                                        |

|                                             | 32 message objects                                                                                                                                                                                                                                                                                              |

| CAN                                         | Each message object has its own identifier mask                                                                                                                                                                                                                                                                 |

|                                             | Programmable FIFO mode (concatenation of message objects)                                                                                                                                                                                                                                                       |

|                                             | Maskable interrupt                                                                                                                                                                                                                                                                                              |

|                                             | Disabled Automatic Retransmission mode for Time Triggered CAN applications                                                                                                                                                                                                                                      |

|                                             | Programmable loop-back mode for self-test operation                                                                                                                                                                                                                                                             |

|                                             | Full duplex USARTs (SCI/LIN)                                                                                                                                                                                                                                                                                    |

|                                             | Wide range of baud rate settings using a dedicated reload timer                                                                                                                                                                                                                                                 |

| USART                                       | Special synchronous options for adapting to different synchronous serial protocols                                                                                                                                                                                                                              |

|                                             | LIN functionality working either as master or slave LIN device                                                                                                                                                                                                                                                  |

| 120                                         | Up to 400 kbps                                                                                                                                                                                                                                                                                                  |

| l <sup>2</sup> C                            | <ul> <li>Master and Slave functionality, 8-bit and 10-bit addressing</li> </ul>                                                                                                                                                                                                                                 |

|                                             | • SAR-type                                                                                                                                                                                                                                                                                                      |

|                                             | 10-bit resolution                                                                                                                                                                                                                                                                                               |

| A/D converter                               | <ul> <li>Signals interrupt on conversion end, single conversion mode, continuous<br/>conversion mode, stop conversion mode, activation by software, external trigger or<br/>reload timer</li> </ul>                                                                                                             |

| A/D Converter Refer-<br>ence Voltage switch | 2 independent positive A/D converter reference voltages available                                                                                                                                                                                                                                               |

|                                             | 16-bit wide                                                                                                                                                                                                                                                                                                     |

| Reload Timers                               | • Prescaler with 1/2 <sup>1</sup> , 1/2 <sup>2</sup> , 1/2 <sup>3</sup> , 1/2 <sup>4</sup> , 1/2 <sup>5</sup> , 1/2 <sup>6</sup> of peripheral clock frequency                                                                                                                                                  |

|                                             | Event count function                                                                                                                                                                                                                                                                                            |

| Free Running Timers                         | <ul> <li>Signals an interrupt on overflow, supports timer clear upon match with Output<br/>Compare (0, 4), Prescaler with 1, 1/2<sup>1</sup>, 1/2<sup>2</sup>, 1/2<sup>3</sup>, 1/2<sup>4</sup>, 1/2<sup>5</sup>, 1/2<sup>6</sup>, 1/2<sup>7</sup>,1/2<sup>8</sup> of<br/>peripheral clock frequency</li> </ul> |

|                                             | 16-bit wide                                                                                                                                                                                                                                                                                                     |

| Input Capture Units                         | <ul> <li>Signals an interrupt upon external event</li> </ul>                                                                                                                                                                                                                                                    |

|                                             | Rising edge, falling edge or rising & falling edge sensitive                                                                                                                                                                                                                                                    |

|                                             | 16-bit wide                                                                                                                                                                                                                                                                                                     |

| Output Compare Units                        | <ul> <li>Signals an interrupt when a match with 16-bit I/O Timer occurs</li> </ul>                                                                                                                                                                                                                              |

|                                             | <ul> <li>A pair of compare registers can be used to generate an output signal.</li> </ul>                                                                                                                                                                                                                       |

| Feature                |   | Description                                                                                                                |

|------------------------|---|----------------------------------------------------------------------------------------------------------------------------|

|                        | • | 16-bit down counter, cycle and duty setting registers                                                                      |

|                        | • | Interrupt at trigger, counter borrow and/or duty match                                                                     |

| Programmable Pulse     | • | PWM operation and one-shot operation                                                                                       |

| Generator              | • | Internal prescaler allows 1, 1/4, 1/16, 1/64 of peripheral clock as counter clock and Reload timer overflow as clock input |

|                        | • | Can be triggered by software or reload timer                                                                               |

|                        | • | Can be clocked either from sub oscillator (devices with part number suffix "W"), main oscillator or from the RC oscillator |

| Real Time Clock        | • | Facility to correct oscillation deviation of Sub clock or RC oscillator clock (clock calibration)                          |

|                        | • | Read/write accessible second/minute/hour registers                                                                         |

|                        | • | Can signal interrupts every half second/second/minute/hour/day                                                             |

|                        | • | Internal clock divider and prescaler provide exact 1s clock                                                                |

|                        | • | Edge sensitive or level sensitive                                                                                          |

| External Interrupts    | • | Interrupt mask and pending bit per channel                                                                                 |

|                        | • | Each available CAN channel RX has an external interrupt for wake-up                                                        |

|                        | • | Selected USART channels SIN have an external interrupt for wake-up                                                         |

|                        | • | Disabled after reset                                                                                                       |

| Non Maskable Interrupt | • | Once enabled, can not be disabled other than by reset.                                                                     |

| Non Maskable Interrupt | • | Level high or level low sensitive                                                                                          |

|                        | • | Pin shared with external interrupt 0.                                                                                      |

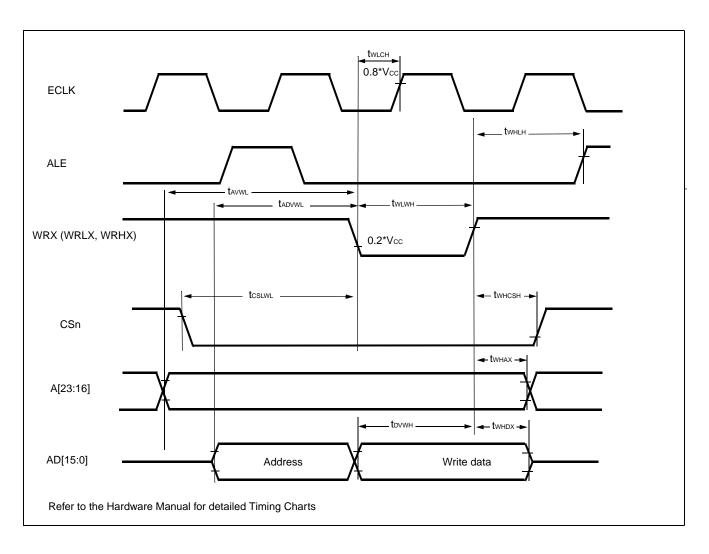

|                        | • | 8-bit or 16-bit bidirectional data                                                                                         |

|                        | • | Up to 24-bit addresses                                                                                                     |

|                        | • | 6 chip select signals                                                                                                      |

| External bus interface | • | Multiplexed address/data lines                                                                                             |

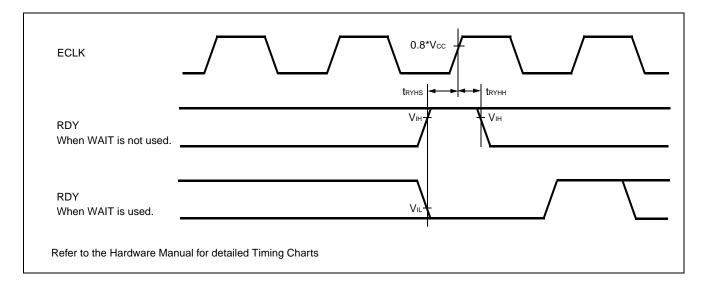

|                        | • | Wait state request                                                                                                         |

|                        | • | External bus master possible                                                                                               |

|                        | • | Timing programmable                                                                                                        |

|                        | • | Monitors an external voltage and generates an interrupt in case of a voltage lower or higher than the defined thresholds   |

| Alarm comparator       | • | Threshold voltages defined externally or generated internally                                                              |

|                        |   | Status is readable, interrupts can be masked separately                                                                    |

| Feature      | Description                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------|

|              | Virtually all external pins can be used as general purpose I/O                                                        |

|              | All push-pull outputs (except when used as I2C SDA/SCL line)                                                          |

|              | Bit-wise programmable as input/output or peripheral signal                                                            |

| I/O Ports    | Bit-wise programmable input enable                                                                                    |

|              | Bit-wise programmable input levels: Automotive / CMOS-Schmitt trigger / TTL (TTI levels not supported by all devices) |

|              | Bit-wise programmable pull-up resistor                                                                                |

|              | Bit-wise programmable output driving strength for EMI optimization                                                    |

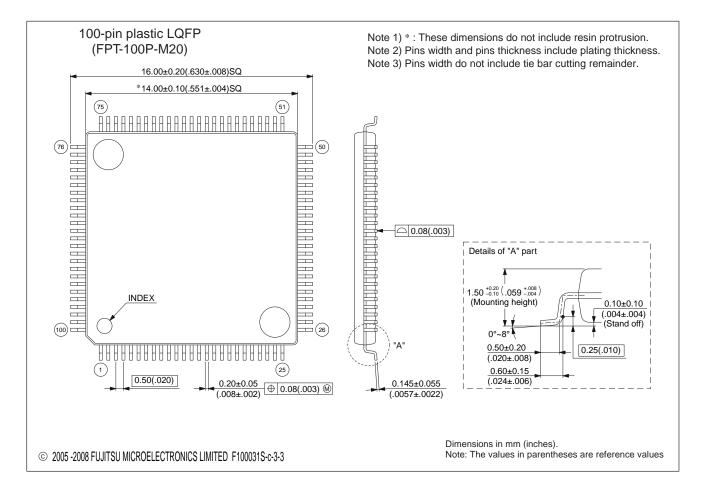

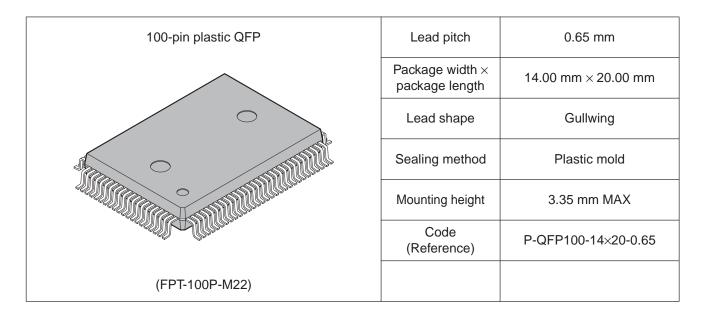

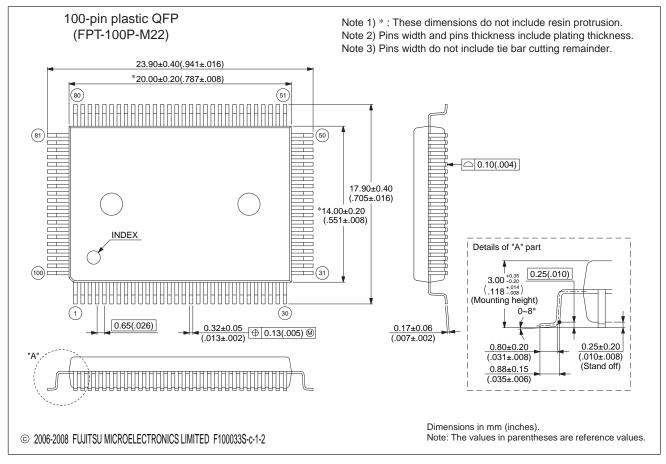

| Packages     | 100-pin plastic QFP and LQFP                                                                                          |

|              | Supports automatic programming, Embedded Algorithm                                                                    |

|              | Write/Erase/Erase-Suspend/Resume commands                                                                             |

|              | A flag indicating completion of the algorithm                                                                         |

|              | Number of erase cycles: 10,000 times                                                                                  |

| Flash Memory | Data retention time: 20 years                                                                                         |

|              | Erase can be performed on each sector individually                                                                    |

|              | Sector protection                                                                                                     |

|              | Flash Security feature to protect the content of the Flash                                                            |

|              | Low voltage detection during Flash erase                                                                              |

### ■ PRODUCT LINEUP

| Features                                         |                                                                                                            | MB96V300B         | MB96(F)34x                                                                       |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------|--|--|

| Product type                                     |                                                                                                            | Evaluation sample | Flash product: MB96F34x<br>Mask ROM product: MB9634x                             |  |  |

| Product options                                  | 6                                                                                                          |                   |                                                                                  |  |  |

| YS<br>RS                                         |                                                                                                            |                   | Low voltage reset persistently on / Single clock                                 |  |  |

|                                                  |                                                                                                            |                   | Low voltage reset can be disabled / Single clock                                 |  |  |

| YW                                               |                                                                                                            |                   | Low voltage reset persistently on / Dual clock                                   |  |  |

| RW                                               |                                                                                                            |                   | Low voltage reset can be disabled / Dual clock                                   |  |  |

| TS                                               |                                                                                                            |                   | indep. 32KB Flash / Low voltage reset persistently on / Single clock             |  |  |

| HS                                               |                                                                                                            |                   | indep. 32KB Flash / Low voltage reset can be disabled / Single clock             |  |  |

| TW                                               |                                                                                                            |                   | indep. 32KB Flash / Low voltage reset persistently on / Dual clock               |  |  |

| HW                                               |                                                                                                            |                   | indep. 32KB Flash / Low voltage reset can be disabled / Dual clock               |  |  |

| FS                                               |                                                                                                            | NA                | 64KB Data Flash / Low voltage reset persistently on / Single clock               |  |  |

| DS                                               | DS                                                                                                         |                   | 64KB Data Flash / Low voltage reset can be disabled / Single clock               |  |  |

| FW<br>DW<br>AS                                   |                                                                                                            |                   | 64KB Data Flash / Low voltage reset persistently on / Dual clock                 |  |  |

|                                                  |                                                                                                            |                   | 64KB Data Flash / Low voltage reset can be disabled / Dual clock                 |  |  |

|                                                  |                                                                                                            |                   | No CAN / Low voltage reset can be disabled / Single clock devices                |  |  |

| CS                                               |                                                                                                            |                   | No CAN / indep. 32KB Flash / Low voltage reset can be disabled /<br>Single clock |  |  |

| AW                                               |                                                                                                            |                   | No CAN / Low voltage reset can be disabled / Dual clock                          |  |  |

| CW                                               |                                                                                                            |                   | No CAN / indep. 32KB Flash / Low voltage reset can be disabled /<br>Dual clock   |  |  |

| Flash/ROM                                        | RAM                                                                                                        |                   |                                                                                  |  |  |

| 160KB                                            | 8KB                                                                                                        |                   | MB96345Y <sup>+1</sup> , MB96345R <sup>+1</sup>                                  |  |  |

| 224KB<br>[Flash A: 160KB,<br>Data Flash A: 64KB] | 8KB                                                                                                        | ROM/Flash         | MB96F345F <sup>-1</sup> , MB96F345D <sup>-1</sup>                                |  |  |

| 288KB                                            | 16KB                                                                                                       | memory emulation  | MB96F346Y, MB96346Y *1, MB96F346R, MB96346R *1, MB96F346A                        |  |  |

| 416KB                                            | 416KB16KBby external RAM,<br>92KB internal<br>RAM544KB24KB576KB576KB[Flash A: 544KB,<br>Flash B: 32KB]24KB |                   | MB96F347Y, MB96F347R, MB96F347A                                                  |  |  |

| 544KB                                            |                                                                                                            |                   | MB96F348Y, MB96F348R, MB96F348A                                                  |  |  |

| [Flash A: 544KB,                                 |                                                                                                            |                   | MB96F348T, MB96F348H, MB96F348C                                                  |  |  |

| Package                                          |                                                                                                            | BGA416            | FPT-100P-M20 FPT-100P-M22                                                        |  |  |

| Features                                  | MB96V300B                                                                                                       | MB96(F)34x                                           |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| DMA                                       | 16 channels                                                                                                     | 6 channels                                           |  |

| USART                                     | 10 channels                                                                                                     | 7 channels                                           |  |

| I2C                                       | 2 channels                                                                                                      | 2 channels                                           |  |

| A/D Converter                             | 40 channels                                                                                                     | 24 channels                                          |  |

| A/D Converter Reference<br>Voltage switch | yes                                                                                                             | yes (except MB96F345Dyy or MB96F345Fyy)              |  |

| 16-bit Reload Timer                       | 6 channels + 1<br>channel (for PPG)                                                                             | 4 channels + 1 channel (for PPG)                     |  |

| 16-bit Free-Running Timer                 | 4 channels                                                                                                      | 2 channels                                           |  |

| 16-bit Output Compare                     | 12 channels                                                                                                     | 8 channels                                           |  |

| 16-bit Input Capture                      | 12 channels                                                                                                     | 8 channels                                           |  |

| 16-bit Programmable Pulse<br>Generator    | 20 channels                                                                                                     | 16 channels                                          |  |

| CAN Interface                             | 5 channels<br>MB96(F)34xAyy or MB96(F)34xCyy: no<br>MB96F345Dyy or MB96F345Fyy: 1 channel<br>others: 2 channels |                                                      |  |

| External Interrupts                       |                                                                                                                 | 16 channels                                          |  |

| Non-Maskable Interrupt                    |                                                                                                                 | 1 channel                                            |  |

| Real Time Clock                           |                                                                                                                 | 1                                                    |  |

| I/O Ports                                 | 136 80 for part number with suffix "W", 82 for part number with suffix "S"                                      |                                                      |  |

| Alarm comparator                          | 2 channels                                                                                                      | MB96F345Dyy or MB96F345Fyy: no<br>others: 2 channels |  |

| External bus interface                    | Yes                                                                                                             | Yes (multiplexed address/data)                       |  |

| Chip select                               | 6 signals                                                                                                       |                                                      |  |

| Clock output function                     | 2 channels                                                                                                      |                                                      |  |

| Low voltage reset                         | Yes                                                                                                             |                                                      |  |

| On-chip RC-oscillator                     | Yes                                                                                                             |                                                      |  |

\*1: These devices are under development and specification is preliminary. These products under development may change its specification without notice.

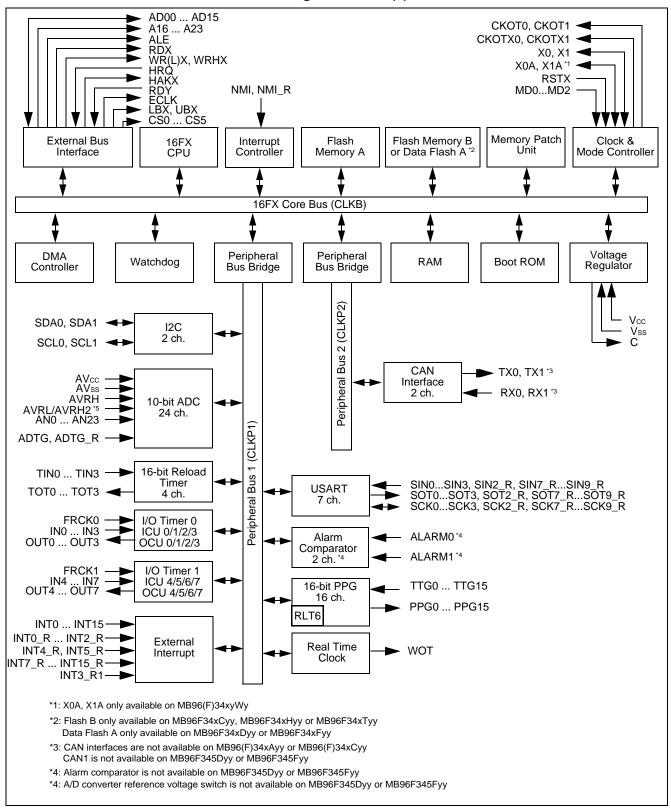

■ BLOCK DIAGRAM

Block diagram of MB96(F)34x

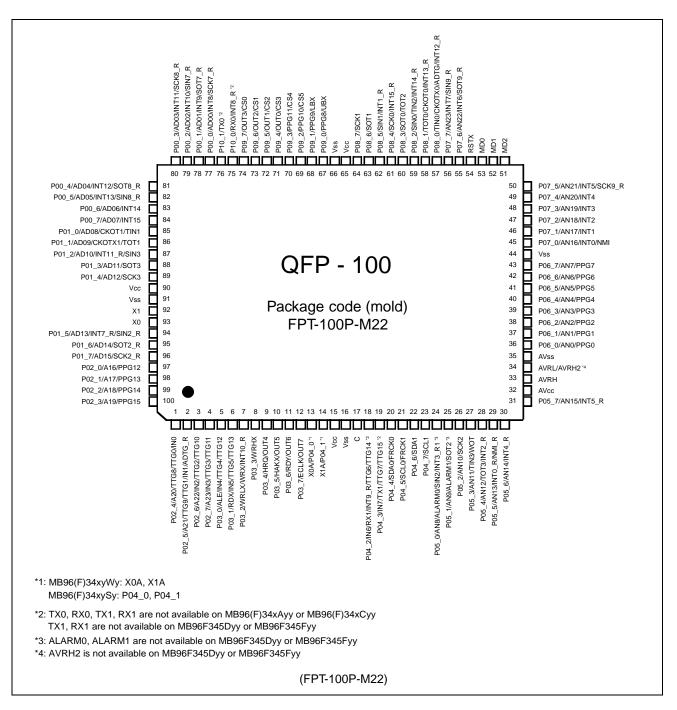

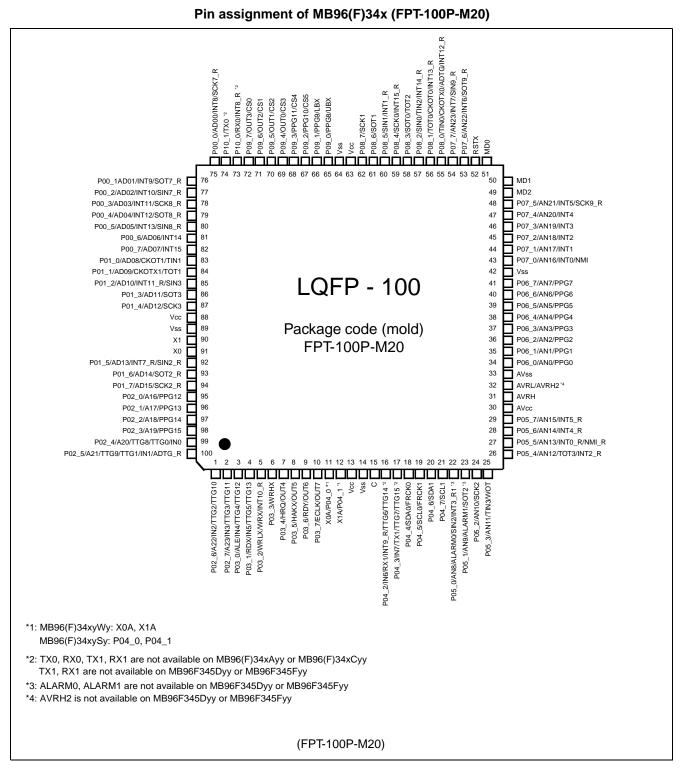

#### PIN ASSIGNMENTS

Pin assignment of MB96(F)34x (FPT-100P-M22)

#### Remark:

MB96(F)34x products are pin-compatible to F<sup>2</sup>MC-16LX family MB90340 series.

#### Remark:

MB96(F)34x products are pin-compatible to F<sup>2</sup>MC-16LX family MB90340 series.

10

### ■ PIN FUNCTION DESCRIPTION

#### Pin Function description (1/2)

| Pin name | Feature               | Description                                                                    |

|----------|-----------------------|--------------------------------------------------------------------------------|

| ADn      | External bus          | External bus interface (multiplexed mode) address output and data input/output |

| ADTG     | ADC                   | A/D converter trigger input                                                    |

| ADTG_R   | ADC                   | Relocated A/D converter trigger input                                          |

| ALARMn   | Alarm comparator      | Alarm Comparator n input                                                       |

| ALE      | External bus          | External bus Address Latch Enable output                                       |

| An       | External bus          | External bus address output                                                    |

| ANn      | ADC                   | A/D converter channel n input                                                  |

| AVcc     | Supply                | Analog circuits power supply                                                   |

| AVRH     | ADC                   | A/D converter high reference voltage input                                     |

| AVRH2    | ADC                   | Alternative A/D converter high reference voltage input                         |

| AVRL     | ADC                   | A/D converter low reference voltage input                                      |

| AVss     | Supply                | Analog circuits power supply                                                   |

| С        | Voltage regulator     | Internally regulated power supply stabilization capacitor pin                  |

| CKOTn    | Clock output function | Clock Output function n output                                                 |

| CKOTXn   | Clock output function | Clock Output function n inverted output                                        |

| ECLK     | External bus          | External bus clock output                                                      |

| CSn      | External bus          | External bus chip select n output                                              |

| FRCKn    | Free Running Timer    | Free Running Timer n input                                                     |

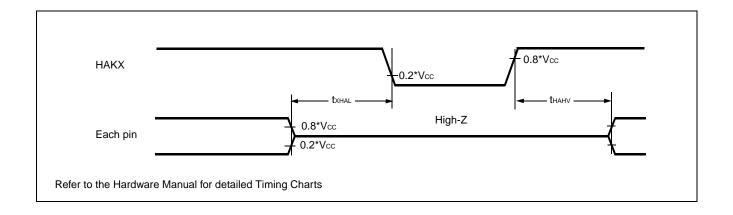

| HAKX     | External bus          | External bus Hold Acknowledge                                                  |

| HRQ      | External bus          | External bus Hold Request                                                      |

| INn      | ICU                   | Input Capture Unit n input                                                     |

| INTn     | External Interrupt    | External Interrupt n input                                                     |

| INTn_R   | External Interrupt    | Relocated External Interrupt n input                                           |

| LBX      | External bus          | External Bus Interface Lower Byte select strobe output                         |

| MDn      | Core                  | Input pins for specifying the operating mode.                                  |

| NMI      | External Interrupt    | Non-Maskable Interrupt input                                                   |

| NMI_R    | External Interrupt    | Relocated Non-Maskable Interrupt input                                         |

| OUTn     | OCU                   | Output Compare Unit n waveform output                                          |

### Pin Function description (2/2)

| Pin name | Feature      | Description                                                   |  |

|----------|--------------|---------------------------------------------------------------|--|

| Pxx_n    | GPIO         | General purpose IO                                            |  |

| PPGn     | PPG          | Programmable Pulse Generator n output                         |  |

| RDX      | External bus | External bus interface read strobe output                     |  |

| RDY      | External bus | External bus interface external wait state request input      |  |

| RSTX     | Core         | Reset input                                                   |  |

| RXn      | CAN          | CAN interface n RX input                                      |  |

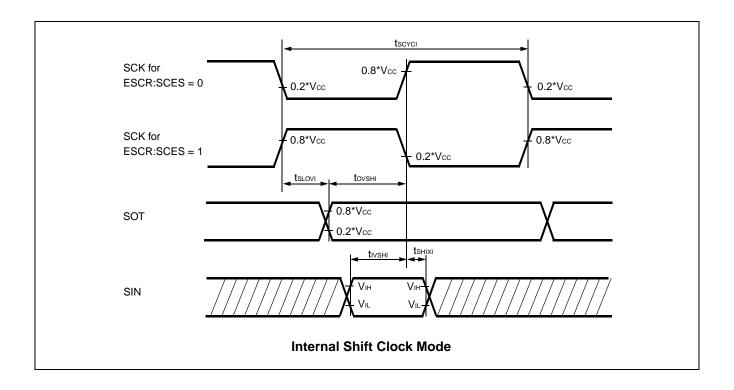

| SCKn     | USART        | USART n serial clock input/output                             |  |

| SCKn_R   | USART        | Relocated USART n serial clock input/output                   |  |

| SCLn     | I2C          | I2C interface n clock I/O input/output                        |  |

| SDAn     | I2C          | I2C interface n serial data I/O input/output                  |  |

| SINn     | USART        | USART n serial data input                                     |  |

| SINn_R   | USART        | Relocated USART n serial data input                           |  |

| SOTn     | USART        | USART n serial data output                                    |  |

| SOTn_R   | USART        | Relocated USART n serial data output                          |  |

| TINn     | Reload Timer | Reload Timer n event input                                    |  |

| TOTn     | Reload Timer | Reload Timer n output                                         |  |

| TTGn     | PPG          | Programmable Pulse Generator n trigger input                  |  |

| TXn      | CAN          | CAN interface n TX output                                     |  |

| UBX      | External bus | External Bus Interface Upper Byte select strobe output        |  |

| Vcc      | Supply       | Power supply                                                  |  |

| Vss      | Supply       | Power supply                                                  |  |

| WOT      | RTC          | Real Timer clock output                                       |  |

| WRHX     | External bus | External bus High byte write strobe output                    |  |

| WRLX/WRX | External bus | External bus Low byte / Word write strobe output              |  |

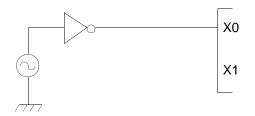

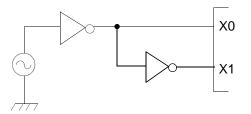

| X0       | Clock        | Oscillator input                                              |  |

| X0A      | Clock        | Subclock Oscillator input (only for devices with suffix "W")  |  |

| X1       | Clock        | Oscillator output                                             |  |

| X1A      | Clock        | Subclock Oscillator output (only for devices with suffix "W") |  |

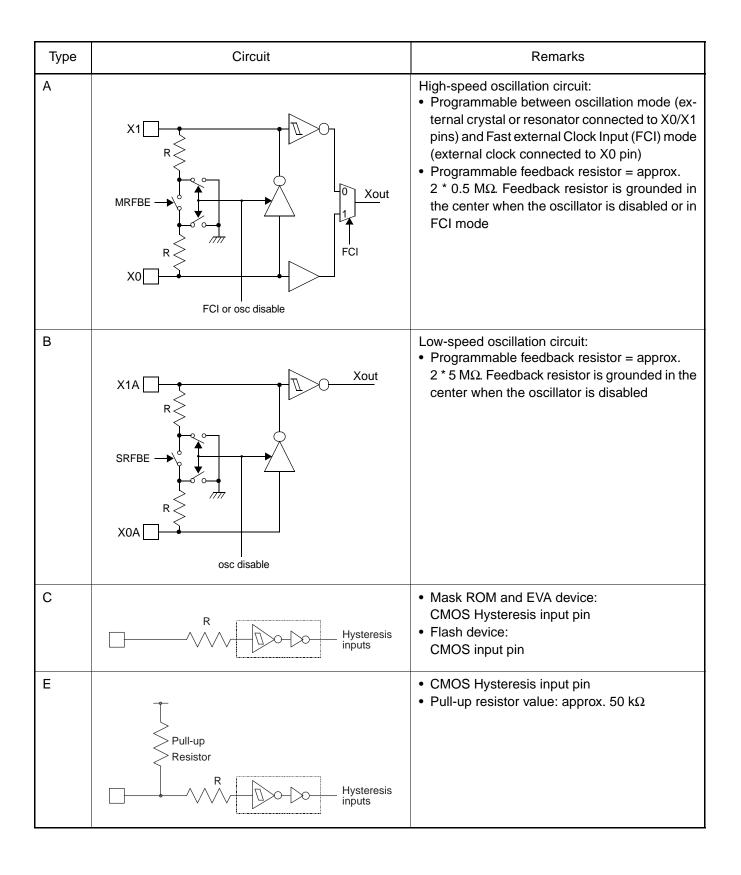

#### ■ PIN CIRCUIT TYPE

#### Pin circuit types

| FPT-100P-M20 |                               |  |  |

|--------------|-------------------------------|--|--|

| Pin no.      | Circuit<br>type <sup>*1</sup> |  |  |

| 1-10         | Н                             |  |  |

| 11,12        | B*2                           |  |  |

| 11,12        | H *3                          |  |  |

| 13,14        | Supply                        |  |  |

| 15           | F                             |  |  |

| 16,17        | Н                             |  |  |

| 18-21        | Ν                             |  |  |

| 22-29        | I                             |  |  |

| 30           | Supply                        |  |  |

| 31-32        | G                             |  |  |

| 33           | Supply                        |  |  |

| 34 to 41     | I                             |  |  |

| 42           | Supply                        |  |  |

| 43 to 48     | I                             |  |  |

| 49 to 51     | С                             |  |  |

| 52           | E                             |  |  |

| 53 to 54     | I                             |  |  |

| 55 to 62     | Н                             |  |  |

| 63, 64       | Supply                        |  |  |

| 65 to 87     | Н                             |  |  |

| 88,89        | Supply                        |  |  |

| 90, 91       | А                             |  |  |

| 92-100       | Н                             |  |  |

| FPT-100P-M22 |                    |  |  |

|--------------|--------------------|--|--|

| Pin no.      | Circuit<br>type *1 |  |  |

| 1-12         | Н                  |  |  |

| 13, 14       | B*2                |  |  |

| 13, 14       | H *3               |  |  |

| 15,16        | Supply             |  |  |

| 17           | F                  |  |  |

| 18,19        | Н                  |  |  |

| 20-23        | Ν                  |  |  |

| 24-31        | I                  |  |  |

| 32           | Supply             |  |  |

| 33-34        | G                  |  |  |

| 35           | Supply             |  |  |

| 36 to 43     | I                  |  |  |

| 44           | Supply             |  |  |

| 45 to 50     | I                  |  |  |

| 51 to 53     | С                  |  |  |

| 54           | E                  |  |  |

| 55 to 56     | I                  |  |  |

| 57 to 64     | Н                  |  |  |

| 65, 66       | Supply             |  |  |

| 67 to 89     | Н                  |  |  |

| 90, 91       | Supply             |  |  |

| 92, 93       | А                  |  |  |

| 94 to 100    | Н                  |  |  |

\*1: Please refer to "■ I/O CIRCUIT TYPE" for details on the I/O circuit types

\*2: Devices with suffix "W"

\*3: Devices without suffix "W"

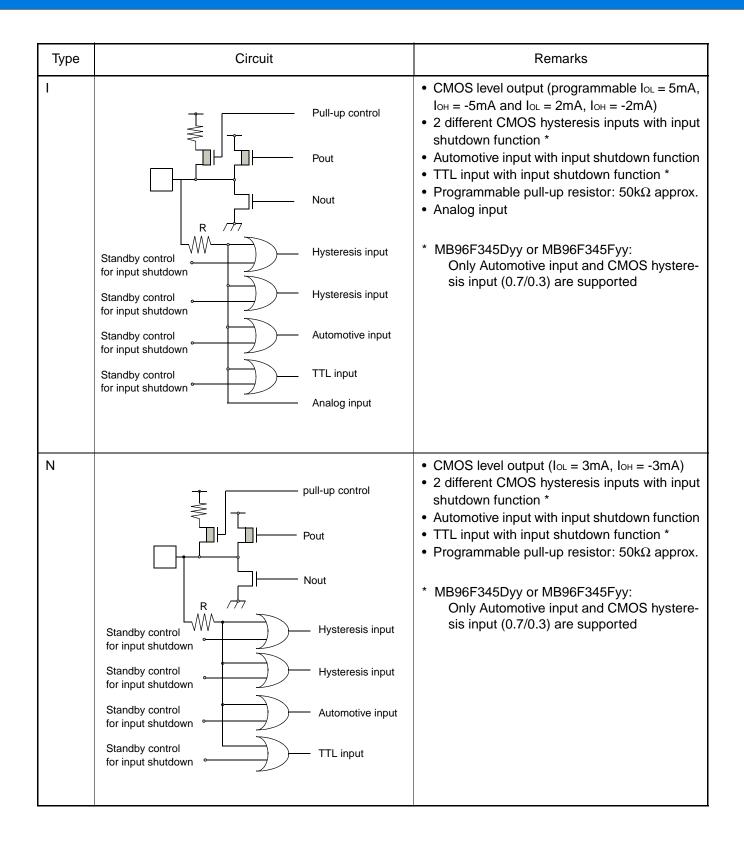

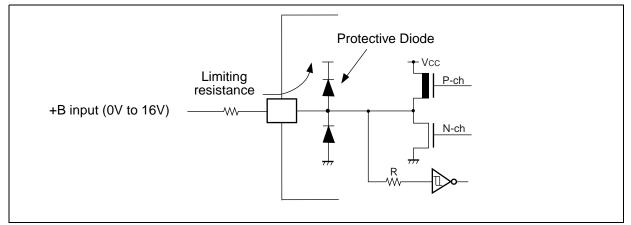

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                                                                                                                                                                                                                                                  | Remarks                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    |                                                                                                                                                                                                                                                                                                          | Power supply input protection circuit                                                                                                                                                                                                                                                                                                                                                                            |

| G    |                                                                                                                                                                                                                                                                                                          | <ul> <li>A/D converter ref+ (AVRH/AVRH2) power supply input pin with protection circuit</li> <li>Flash devices do not have a protection circuit against VCC for pins AVRH/AVRH2</li> <li>Devices without AVRH reference switch do not have an analog switch for the AVRL pin</li> </ul>                                                                                                                          |

| Η    | Standby control<br>for input shutdown<br>Standby control<br>for input shutdown<br>TTL input | <ul> <li>CMOS level output (programmable loL = 5mA, loH = -5mA and loL = 2mA, loH = -2mA)</li> <li>2 different CMOS hysteresis inputs with input shutdown function *</li> <li>Automotive input with input shutdown function *</li> <li>Programmable pull-up resistor: 50kΩ approx.</li> <li>* MB96F345Dyy or MB96F345Fyy:<br/>Only Automotive input and CMOS hysteresis input (0.7/0.3) are supported</li> </ul> |

#### ■ MEMORY MAP

|                         | MB96V300B              |                                                 | MB96(F)34x                                     |                                               |

|-------------------------|------------------------|-------------------------------------------------|------------------------------------------------|-----------------------------------------------|

| FF:FFFFH<br>DE:0000H    | Emulation ROM          |                                                 | USER ROM /<br>External Bus <sup>-4</sup>       |                                               |

| 10:0000н                | External Bus           |                                                 | External Bus                                   |                                               |

| 0F:Е000н                | Boot-ROM               |                                                 | Boot-ROM                                       |                                               |

| 01.2000                 | Deserved               | 0 <b>F</b> :0000н                               | Reserved                                       |                                               |

| 0E:0000н                | Reserved               |                                                 | DATA FLASH /<br>Reserved <sup>∵₄</sup>         |                                               |

| 02:0000 <b>⊦</b>        | External RAM           | 0C:0000 <sub>H</sub>                            | Reserved                                       |                                               |

| 01:0000н                | Internal RAM<br>bank 1 | RAMEND1 <sup>*2</sup><br>RAMSTART1 <sup>2</sup> | Reserved<br>Internal RAM<br>bank 1<br>Reserved | RAM availability de-<br>pending on the device |

| 00:8000н                | ROM/RAM MIRROR         |                                                 | ROM/RAM MIRROR                                 |                                               |

|                         | Internal RAM           | RAMSTART0 <sup>-2</sup>                         | Internal RAM<br>bank 0                         |                                               |

|                         | bank 0                 |                                                 | Reserved                                       | External Bus end                              |

| RAMSTART0 <sup>-3</sup> |                        |                                                 | External Bus                                   | address*2                                     |

| 00:0С00н                | External Bus           |                                                 |                                                |                                               |

| 00:0 <b>380</b> н       | Peripherals            |                                                 | Peripherals                                    |                                               |

| 00:0180н                | GPR <sup>*1</sup>      |                                                 | GPR <sup>∗1</sup>                              |                                               |

| 00:0100н                | DMA                    |                                                 | DMA                                            |                                               |

| 00:00F0н                | External Bus           |                                                 | External Bus                                   |                                               |

| 00:000н                 | Peripheral             |                                                 | Peripheral                                     |                                               |

| *1: Unused G            | PR banks can be used   | as RAM area                                     |                                                |                                               |

\*2: For External Bus end address and RAMSTART/END addresses, please refer to the table on the next page.

\*3: For EVA device, RAMSTART0 depends on the configuration of the emulated device.

\*4: For details about USER ROM area or DATA FLASH area, see the ■ USER ROM MEMORY MAP FOR FLASH DEVICES and ■ USER ROM MEMORY MAP FOR MASK ROM DEVICES on the following pages. The External Bus area and DMA area are only available if the device contains the corresponding resource.

The available RAM and ROM area depends on the device.

### ■ RAMSTART/END AND EXTERNAL BUS END ADDRESSES

| Devices                 | Bank 0<br>RAM size | Bank 1<br>RAM size | External Bus<br>end address | RAMSTART0 | RAMSTART1 | RAMEND1 |

|-------------------------|--------------------|--------------------|-----------------------------|-----------|-----------|---------|

| MB96(F)345              | 8KByte             | -                  | 00:21FFн                    | 00:6240н  | -         | -       |

| MB96(F)346,<br>MB96F347 | 16KByte            | -                  | 00:21FFн                    | 00:4240н  | -         | -       |

| MB96F348                | 24KByte            | -                  | 00:21FFн                    | 00:2240н  | -         | -       |

#### ■ USER ROM MEMORY MAP FOR FLASH DEVICES

|                                 |                           | MB96F345D<br>MB96F345F                     |              |

|---------------------------------|---------------------------|--------------------------------------------|--------------|

| Alternative mode<br>CPU address | Flash memory mode address | Flash size 160kByte<br>+64KByte Data Flash |              |

| FF:FFFF                         | 3F:FFFFH                  | S39 - 64K                                  |              |

| FF:0000H<br>FE:FFFFH            | 3F:0000н<br>3E:FFFFн      | C20 C4K                                    | Flash A      |

| FE:0000H                        | 3Е:0000н                  | S38 - 64K                                  |              |

| FD:FFFFH                        | 3D:FFFFH                  |                                            |              |

| FD:0000H                        | 3D:0000H                  |                                            |              |

| FC:FFFFH                        | 3C:FFFFн                  |                                            |              |

| FC:0000H<br>FB:FFFFH            | 3C:0000н<br>3B:FFFFн      |                                            |              |

| FB:0000H                        | 3B:0000H                  |                                            |              |

| FA:FFFFH                        | 3A:FFFFH                  |                                            |              |

| FA:0000H                        | 3А:0000н                  |                                            |              |

| F9:FFFF                         | 39:FFFFн                  |                                            |              |

| F9:0000н<br>F8:FFFFн            | 39:0000н<br>38:FFFFн      |                                            |              |

| F8:0000H                        | 38:0000H                  |                                            |              |

| F7:FFFFH                        | 37:FFFFH                  |                                            |              |

| F7:0000H                        | 37:0000н                  |                                            |              |

| F6:FFFF                         | 36:FFFFн                  |                                            |              |

| F6:0000H                        | 36:0000H                  | <ul> <li>External bus</li> </ul>           |              |

| F5:FFFFн<br>F5:0000н            | 35:FFFFн<br>35:0000н      |                                            |              |

| F4:FFFFH                        | 34:FFFFH                  |                                            |              |

| F4:0000H                        | 34:0000H                  |                                            |              |

| F3:FFFF                         | 33:FFFFH                  |                                            |              |

| F3:0000H                        | 33:0000H                  |                                            |              |

| F2:FFFFн<br>F2:0000н            | 32:FFFFн<br>32:0000н      |                                            |              |

| F1:FFFFH                        | 31:FFFFH                  |                                            |              |

| F1:0000H                        | 31:0000                   |                                            |              |

| F0:FFFFH                        | 30:FFFFн                  |                                            |              |

| F0:0000н<br>E0:FFFFн            | 30:0000н                  |                                            |              |

| LU.IIIIH                        |                           |                                            |              |

| E0:0000H                        |                           |                                            |              |

| DF:FFFF<br>DF:8000⊦             |                           | Reserved                                   |              |

| DF:7FFFH                        | 1F:7FFFH                  |                                            |              |

| DF:6000H                        | 1F:6000H                  | SA3 - 8K                                   |              |

| DF:5FFFH                        | 1F:5FFFH                  | SA2 - 8K                                   |              |

| DF:4000H                        | 1F:4000H                  |                                            | Flash A      |

| DF:3FFFH<br>DF:2000H            | 1F:3FFFн<br>1F:2000н      | SA1 - 8K                                   |              |

| DF:1FFFH                        | 1F:1FFFH                  | SA0 - 8K *1                                |              |

| DF:0000H                        | 1F:0000н                  | SAU - OK                                   |              |

| DE:FFFFH                        |                           | Reserved                                   |              |

| DE:0000H                        |                           |                                            |              |

| 0E:FFFFн                        | (0E:FFFF <sub>H</sub> )   | SDA0-256 *2                                | Data Flash A |

| 0E:FF00H                        | (0E:FF00H)                |                                            |              |

| 0E:FEFFн<br>0E:0000н            |                           | Reserved                                   |              |

| 0D:FFFFH                        | (0F:FFFF <sub>H</sub> )   | SDA4-16K                                   |              |

| 0D:C000H                        | (0F:C000H)                |                                            |              |

| 0D:BFFFH                        | (OF:BFFFH)                | SDA3-16K                                   |              |

| 0D:8000н<br>0D:7FFFн            | (0F:8000н)<br>(0F:7FFFн)  |                                            | Data Flash A |

| 0D:7FFFH<br>0D:4000H            | (0F:4000н)                | SDA2-16K                                   |              |

| 0D:3FFFH                        | (0F:3FFFH)                | SDA1-16K                                   |              |

| 0D:0000H                        | (0F:0000н)                | SDAT-TOR                                   |              |

| 0C:FFFFH                        |                           | Reserved                                   |              |

| 0С:000н                         |                           |                                            |              |

|                                 |                           |                                            |              |

|                                 |                              | MB96F346Y<br>MB96F346R<br>MB96F346A | MB96F347Y<br>MB96F347R<br>MB96F347A |          |

|---------------------------------|------------------------------|-------------------------------------|-------------------------------------|----------|

| Alternative mode<br>CPU address | Flash memory<br>mode address | Flash size<br>288kByte              | Flash size<br>416kByte              |          |

| FF:FFFF                         | 3F:FFFFH                     | S39 - 64K                           | S39 - 64K                           |          |

| FF:0000H<br>FE:FFFFH            | 3F:0000н<br>3E:FFFFн         | 000 0416                            |                                     |          |

| FE:0000H                        | 3Е:0000н                     | S38 - 64K                           | S38 - 64K                           |          |

| FD:FFFFH                        | 3D:FFFFH                     | S37 - 64K                           | S37 - 64K                           |          |

| FD:0000H                        | 3D:0000H                     |                                     |                                     | Flash A  |

| FC:FFFFH<br>FC:0000H            | 3C:FFFFн<br>3C:0000н         | S36 - 64K                           | S36 - 64K                           |          |

| FB:FFFFH                        | 3B:FFFFH                     |                                     | 0.05 0.414                          |          |

| FB:0000H                        | 3B:0000H                     |                                     | S35 - 64K                           |          |

| FA:FFFFh                        | 3A:FFFFh                     |                                     | S34 - 64K                           |          |

| FA:0000H                        | 3A:0000н                     |                                     | 004 - 0413                          |          |

| F9:FFFFH                        | 39:FFFFн                     | I Ī                                 |                                     |          |

| F9:0000H                        | 39:000H                      |                                     |                                     |          |

| F8:FFFFH                        | 38:FFFFн<br>38:0000н         |                                     |                                     |          |

| F8:0000н<br>F7:FFFFн            | 37:FFFFH                     |                                     |                                     |          |

| F7:0000H                        | 37:0000H                     |                                     |                                     |          |

| F6:FFFFH                        | 36:FFFFH                     |                                     |                                     |          |

| F6:0000H                        | 36:0000H                     |                                     |                                     |          |

| F5:FFFFH                        | 35:FFFFH                     | -1 1-                               |                                     |          |

| F5:0000H                        | 35:0000н                     | External bus                        |                                     |          |

| F4:FFFF                         | 34:FFFFh                     |                                     |                                     |          |

| F4:0000H                        | 34:0000н                     |                                     | External bus                        |          |

| F3:FFFF                         | 33:FFFFH                     |                                     | External bao                        |          |

| F3:0000H                        | 33:0000H                     |                                     |                                     |          |

| F2:FFFFH                        | 32:FFFFH                     |                                     |                                     |          |

| F2:0000н<br>F1:FFFFн            | 32:0000н<br>31:FFFFн         |                                     |                                     |          |

| F1:0000H                        | 31:0000H                     |                                     |                                     |          |

| F0:FFFFH                        | 30:FFFFH                     |                                     | —                                   |          |

| F0:0000H                        | 30:0000H                     |                                     |                                     |          |

| E0:FFFFH                        |                              |                                     |                                     |          |

| E0:0000н<br>DF:FFFFн            |                              |                                     |                                     |          |

|                                 |                              | Reserved                            | Reserved                            |          |

| DF:8000H                        |                              |                                     |                                     | _        |

| DF:7FFFH                        | 1F:7FFFH                     | SA3 - 8K                            | SA3 - 8K                            |          |

| DF:6000H<br>DF:5FFFH            | 1F:6000н<br>1F:5FFFн         |                                     |                                     |          |

| DF:5FFFH<br>DF:4000H            | 1F:4000н                     | SA2 - 8K                            | SA2 - 8K                            | <b>-</b> |

| DF:3FFFH                        | 1F:3FFFH                     | SA1 - 8K                            | SA1 - 8K                            | Flash A  |

| DF:2000H                        | 1F:2000H                     | SAT-8K                              | SAT - OK                            |          |

| DF:1FFFH                        | 1F:1FFFH                     | SA0 - 8K *1                         | SA0 - 8K *1                         |          |

| DF:0000H                        | 1F:0000н                     | SAU-ON                              | SAU-ON '                            |          |

| DE:FFFFH                        |                              | Record                              | Beconvod                            |          |

| DE:0000H                        |                              | Reserved                            | Reserved                            |          |

|                                 |                             | MB96F348Y<br>MB96F348R<br>MB96F348A | MB96F348T<br>MB96F348H<br>MB96F348C              |         |

|---------------------------------|-----------------------------|-------------------------------------|--------------------------------------------------|---------|

| Alternative mode<br>CPU address | Flash memory mode address   | Flash size<br>544kByte              | Flash size<br>576kByte                           |         |

| FF:FFFFн<br>FF:0000н            | 3F:FFFFн<br>3F:0000н        | S39 - 64K                           | S39 - 64K                                        |         |

| FE:FFFF                         | 3E:FFFFн                    | S38 - 64K                           | S38 - 64K                                        |         |

| FE:0000н<br>FD:FFFFн            | 3E:0000н<br>3D:FFFFн        | S37 - 64K                           | S37 - 64K                                        |         |

| FD:0000H<br>FC:FFFFH            | 3D:0000н<br>3C:FFFFн        | S36 - 64K                           | S36 - 64K                                        |         |

| FC:0000H                        | 3C:0000H                    |                                     |                                                  | Flash A |

| FB:FFFFн<br>FB:0000н            | 3B:FFFFн<br>3B:0000н        | S35 - 64K                           | S35 - 64K                                        |         |

| FA:FFFFн<br>FA:0000н            | 3A:FFFFн<br>3A:0000н        | S34 - 64K                           | S34 - 64K                                        |         |

| F9:FFFF                         | 39:FFFF                     | S33 - 64K                           | S33 - 64K                                        |         |

| F9:0000н<br>F8:FFFFн            | 39:0000н<br>38:FFFFн        | S32 - 64K                           | S32 - 64K                                        |         |

| F8:0000H                        | 38:0000н                    | 332 - 04M                           | 332 - 04N                                        |         |

| F7:FFFFн<br>F7:0000н            | 37:FFFFн<br>37:0000н        |                                     |                                                  |         |

| F6:FFFFн<br>F6:0000н            | 36:FFFFн<br>36:0000н        |                                     |                                                  |         |

| F5:FFFF                         | 35:FFFF                     |                                     |                                                  |         |

| F5:0000н<br>F4:FFFFн            | 35:0000н<br>34:FFFFн        | -                                   | _                                                |         |

| F4:0000H                        | 34:0000н                    |                                     |                                                  |         |

| F3:FFFFн<br>F3:0000н            | 33:FFFFн<br>33:0000н        | External bus                        | External bus                                     |         |

| F2:FFFFн<br>F2:0000н            | 32:FFFFн<br>32:000н         |                                     |                                                  |         |

| F1:FFFF                         | 32:0000н<br>31:FFFFн        |                                     |                                                  |         |

| F1:0000н<br>F0:FFFFн            | 31:0000н<br>30:FFFFн        |                                     |                                                  |         |

| F0:0000H<br>E0:FFFFH            | 30:0000н                    |                                     |                                                  |         |

| Е0:000н                         |                             |                                     |                                                  |         |

| DF:FFFFн<br>DF:8000н            |                             | Reserved                            | Reserved                                         |         |

| DF:7FFFн<br>DF:6000н            | 1F:7FFFн<br>1F:6000н        | SA3 - 8K                            | SA3 - 8K                                         |         |

| DF:5FFFH                        | 1F:5FFFH                    | SA2 - 8K                            | SA2 - 8K                                         |         |

| DF:4000н<br>DF:3FFFн            | 1F:4000н<br>1F:3FFFн        | SA1 - 8K                            | SA1 - 8K                                         | Flash A |

| DF:2000H                        | 1F:2000H                    |                                     |                                                  |         |

| DF:1FFFн<br>DF:0000н            | 1F:1FFFн<br>1F:0000н        | SA0 - 8K *1                         | SA0 - 8K *1                                      |         |

| DE:FFFF <sub>H</sub>            |                             |                                     | Reserved                                         |         |

| DE:8000H                        |                             |                                     |                                                  |         |

| DE:7FFFн<br>DE:6000н            | 1E:7FFFн<br>1E:6000н        |                                     | SB3 - 8K                                         |         |

| DE:5FFFH                        | 1E:5FFFH                    | Reserved                            | SB2 - 8K                                         |         |

| DE:4000н<br>DE:3FFFн            | 1E:4000н<br>1E:3FFFн        |                                     | SB1 - 8K                                         | Flash B |

| DE:2000H                        | 1E:2000H                    |                                     |                                                  |         |

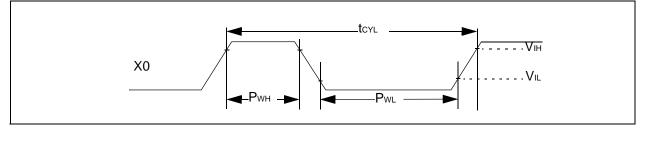

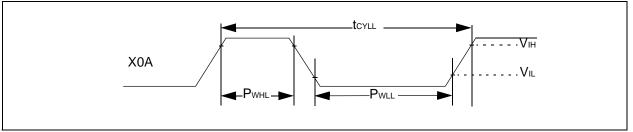

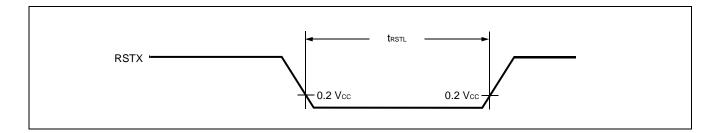

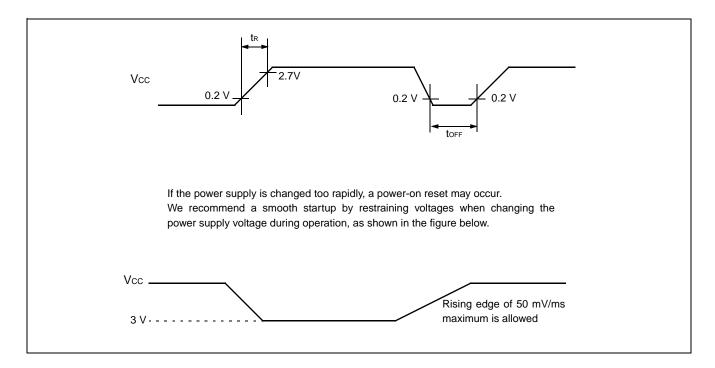

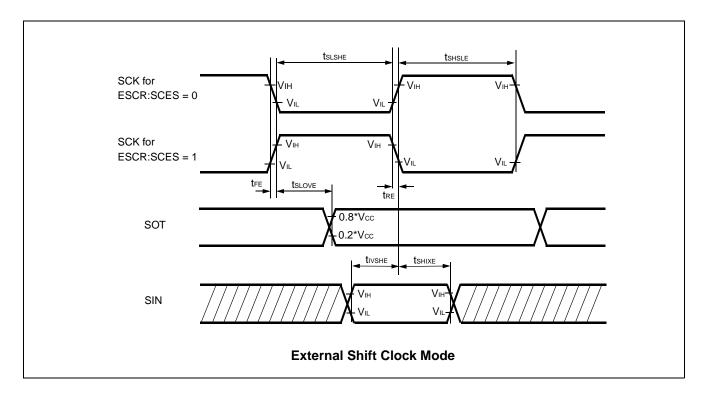

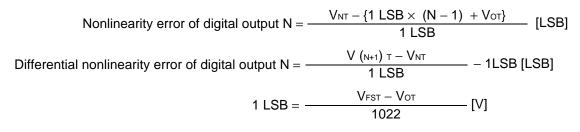

| DE:1FFFн<br>DE:0000н            | 1E:1FFFн<br>1E:0000н        |                                     | SB0 - 8K *2                                      |         |