# **TABLE OF CONTENTS**

| Features                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                                                                                          |

| Functional Block Diagram 1                                                                                                                                                            |

| Revision History 2                                                                                                                                                                    |

| General Description                                                                                                                                                                   |

| Specifications                                                                                                                                                                        |

| Analog Front-End Specifications 4                                                                                                                                                     |

| Switch Matrix Specifications                                                                                                                                                          |

| Transimpedance Amplifier Specifications                                                                                                                                               |

| ADC Specifications                                                                                                                                                                    |

| Temperature Sensor Specifications                                                                                                                                                     |

| Temperature content of content one manual of                                                                                                                                          |

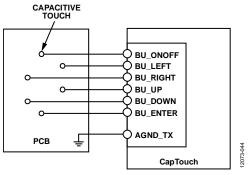

| CapTouch                                                                                                                                                                              |

|                                                                                                                                                                                       |

| CapTouch                                                                                                                                                                              |

| CapTouch6DFT-Based Impedance Measurements7Digital Platform7System Clocks/Timers10Power Management Specifications12Trickle Charger12Timing Characteristics13Absolute Maximum Ratings19 |

# **REVISION HISTORY**

| 5/2017—Rev. A to Rev. B   |    |

|---------------------------|----|

| Changes to Table 24       | 12 |

| Changes to Ordering Guide |    |

5/2014—Revision A: Initial Version

| Typical Performance Characteristics | 25 |

|-------------------------------------|----|

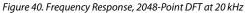

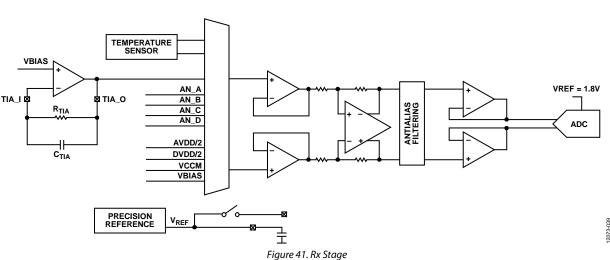

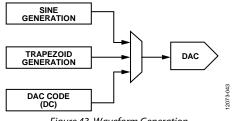

| Analog Front End                    | 30 |

| Excitation Stage                    | 30 |

| Measurement Stage                   | 32 |

| AFE Control                         | 33 |

| CapTouch Features                   | 33 |

| MicroSubSystem                      |    |

| Memories                            |    |

| Debug Capability                    |    |

| Programmable GPIOs                  |    |

| Timers                              |    |

| USB                                 |    |

| Power Management and Clocking       | 35 |

| Display Options                     | 35 |

| Audio Options                       | 36 |

| Development Support                 | 37 |

| Documentation                       | 37 |

| Hardware                            | 37 |

| Software                            | 37 |

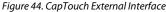

| Packaging and Ordering Information  | 38 |

| Outline Dimensions                  | 38 |

| Ordering Guide                      | 38 |

|                                     |    |

# **GENERAL DESCRIPTION**

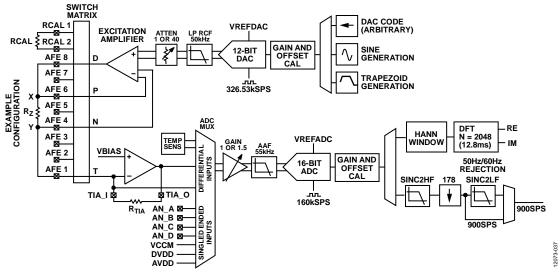

The ADuCM350 is a complete, coin cell powered, high precision, meter-on-chip for portable device applications for applications such as point-of-care diagnostics and body-worn devices for monitoring vital signs. The ADuCM350 is designed for high precision amperometric, voltametric, and impedometric measurement capabilities.

The ADuCM350 analog front end (AFE) features a 16-bit, precision, 160 kSPS analog-to-digital converter (ADC); 0.17% precision voltage reference; 12-bit, no missing codes digital-toanalog converter (DAC); and a reconfigurable ultralow leakage switch matrix. The ADuCM350 also includes an ARM\* Cortex-M3-based processor, memory, and all I/O connectivity to support portable meters with display, USB communication, and active sensors. The ADuCM350 is available in a 120-lead, 8 mm  $\times$  8 mm CSP\_BGA and operates from -40°C to +85°C.

To support extremely low dynamic and hibernate power management, the ADuCM350 provides a collection of power modes and features, such as dynamic and software controlled clock gating and power gating.

The AFE is connected to the ARM Cortex-M3 via an advanced high performance bus (AHB) slave interface on the advanced microcontroller bus architecture (AMBA) matrix, as well as direct memory access (DMA) and interrupt connections.

# **SPECIFICATIONS**

All characterization is at VCCM = 2.5 V to 3.6 V, specifications below 2.5 V are for functionality only, all minimum and maximum specifications are specified for a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.

## ANALOG FRONT-END SPECIFICATIONS

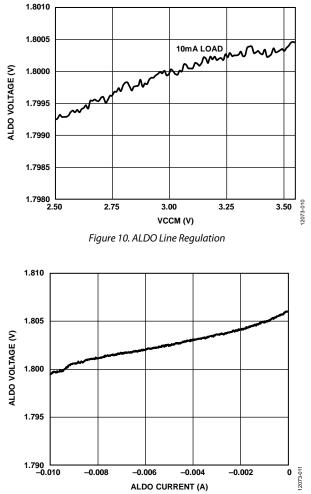

### **AFE LDO Specifications**

#### Table 1. AFE LDO Specifications

| Parameter      | Min  | Тур  | Max  | Unit  | Test Conditions/Comments                                                                                                                   |

|----------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| VOLTAGE        |      |      |      |       |                                                                                                                                            |

| Output Voltage | 1.71 | 1.8  | 1.89 | V     | Measured with a load capacitance ( $C_{LOAD}$ ) = 0.47 $\mu$ F; measured with 1 mA load current on AVDD_RX/TX; all AFE blocks powered down |

| Dropout        |      | 150  | 200  | mV    | 10 mA load applied; no AFE blocks enabled                                                                                                  |

| REGULATION     |      |      |      |       |                                                                                                                                            |

| Line           |      | 1080 |      | μV/V  | 10 mA load applied                                                                                                                         |

| Load           |      | 0.65 |      | mV/mA | 10 mA load applied                                                                                                                         |

| POWER UP       |      |      |      |       |                                                                                                                                            |

| Power-Up Time  |      | 500  |      | μs    | Measured with a $C_{LOAD} = 0.47 \ \mu$ F; current limit enabled                                                                           |

## High Precision Internal Reference Specifications

#### Table 2. High Precision Internal Reference Specifications

| Parameter                                       | Min   | Тур   | Max   | Unit   | Test Conditions/Comments                                                                                              |

|-------------------------------------------------|-------|-------|-------|--------|-----------------------------------------------------------------------------------------------------------------------|

| ADC V <sub>REF</sub>                            |       |       |       |        |                                                                                                                       |

| Reference Voltage Initial Accuracy <sup>1</sup> | 1.797 | 1.8   | 1.803 | V      | For a temperature range of 0°C to 50°C                                                                                |

|                                                 | 1.79  | 1.8   | 1.803 | V      | For a temperature range of -40°C to +85°C                                                                             |

| Output Impedance                                |       |       | 570   | mΩ     | LDO and reference enabled; all other AFE blocks disabled; reference loaded with 50 $\mu A$ on VREF                    |

| Temperature Coefficient <sup>2</sup>            | -52   |       | +90   | ppm/°C | For a temperature range of -40°C to<br>+85°C, maximum value from -40°C to<br>+25°C, and from +25°C to +85°C specified |

|                                                 | -45   |       | +48   | ppm/°C | For a temperature range of 0°C to 50°C,<br>maximum value from –40°C to +25°C, and<br>from 25°C to 85°C specified      |

| VREF Thermal Hysteresis                         |       | 50    |       | ppm    |                                                                                                                       |

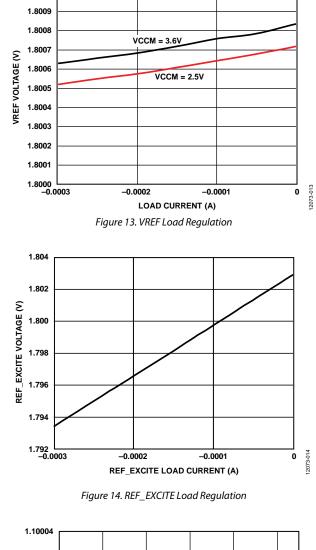

| REF_EXCITE Switching Load                       | 1.789 | 1.793 | 1.797 | V      | $I_{LOAD} = 200 \ \mu$ A; internal ADC measurement                                                                    |

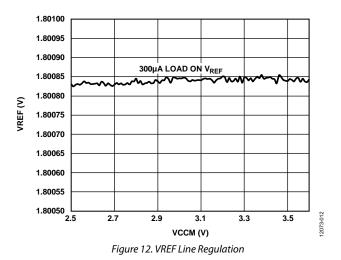

| Line Regulation                                 |       | 50    |       | μ٧/٧   | $V_{CCM1} = 2.5 V$ , $V_{CCM2} = 3.6 V$ ; reference loaded with 300 $\mu$ A                                           |

| Short-Circuit Current to Ground                 |       | 10    |       | mA     | Current limit off                                                                                                     |

| DAC V <sub>REF</sub>                            |       |       |       |        |                                                                                                                       |

| Reference Voltage                               | 1.77  | 1.8   | 1.83  | V      |                                                                                                                       |

| VBIAS                                           |       |       |       |        |                                                                                                                       |

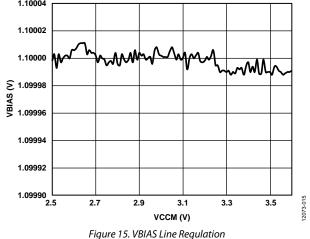

| VBIAS Voltage                                   | 1.095 | 1.1   | 1.102 | V      | Measured with a $C_{LOAD} = 0.47 \ \mu\text{F}$ ; no current load                                                     |

$^{1}$  Reference voltage is trimmed unloaded. Measured with  $C_{\text{LOAD}}\,{=}\,4.7\,\mu\text{F}.$  Measured at 25°C.

<sup>2</sup> Guaranteed by design and/or characterization.

## DAC/RCF/PGA Specifications

Table 3. DAC/PGA/RCF Specifications

| Parameter <sup>1</sup>            | Min   | Тур   | Мах    | Unit  | Test Conditions/Comments                                                                                               |

|-----------------------------------|-------|-------|--------|-------|------------------------------------------------------------------------------------------------------------------------|

| DAC                               |       |       |        |       |                                                                                                                        |

| Output Range                      | -600  |       | +600   | mV    | As seen by sensor                                                                                                      |

| Resolution                        |       |       | 12     | Bits  |                                                                                                                        |

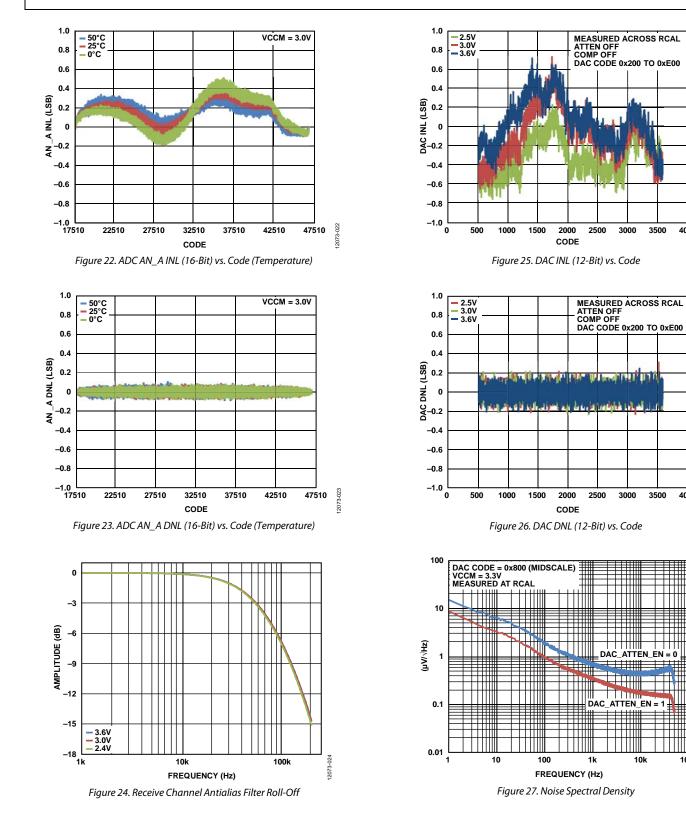

| Integral Nonlinearity (INL)       |       | ±0.85 |        | LSB   | Measured at an output of the excitation<br>loop, using gain = 1 and default DAC clock<br>(16 MHz ÷ 49 DAC clock speed) |

| Differential Nonlinearity (DNL)   | -1    |       | +1     | LSB   | Measured at an output of the excitation<br>loop, using gain = 1 and default DAC clock<br>(16 MHz ÷ 49 DAC clock speed) |

| Full-Scale Error                  |       |       |        |       |                                                                                                                        |

| Positive                          |       | ±0.2  |        | % FSR | PGA (gain = 1), measured at an output of the excitation loop, DAC code = 0xE00                                         |

|                                   |       | ±1    |        | % FSR | PGA (gain = 0.025), measured at an output of the excitation loop, DAC code = 0xE00                                     |

| Negative                          |       | ±0.2  |        | % FSR | PGA (gain = 1), measured at an output of the excitation loop, DAC code = 0x200                                         |

|                                   |       | ±1    |        | % FSR | PGA (gain = 0.025), measured at an output of the excitation loop, DAC code = 0x200                                     |

| Offset Error, Midscale            |       | ±1    |        | mV    | PGA (gain = 1 or gain = 0.025), measured<br>at an output of the excitation loop across<br>RCAL                         |

| Clocking Frequency                | 280.7 | 320   | 380.95 | kHz   |                                                                                                                        |

| PROGRAMMABLE GAIN AMPLIFIER (PGA) |       |       |        |       |                                                                                                                        |

| Gain from PGA in State 0          |       | 1     |        |       | Covered by DAC full-scale error measured on an output of the excitation loop                                           |

| Gain from PGA in State 1          |       | 0.025 |        |       | Covered by DAC full-scale error measured on an output of the excitation loop                                           |

| RECONSTRUCTION FILTER (RCF)       |       |       |        |       |                                                                                                                        |

| 3 dB Corner Frequency             |       | 50    |        | kHz   |                                                                                                                        |

<sup>1</sup> There may be some system offsets and gain errors that can be calibrated at the system level to improve dc accuracy. Hence, the voltage swing at the output of the DAC is ±800 mV to guarantee ±600 mV swing on the sensor.

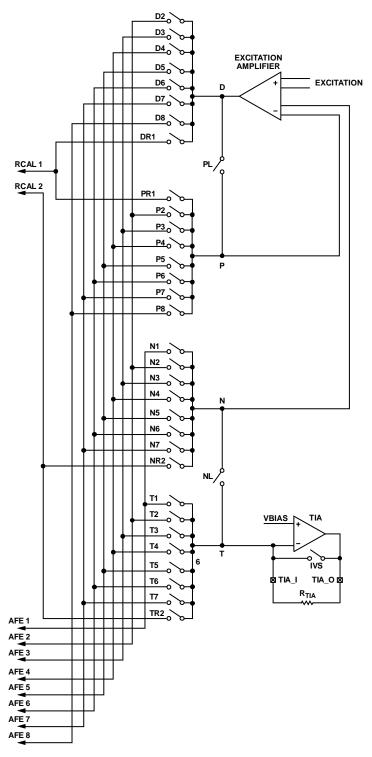

# SWITCH MATRIX SPECIFICATIONS

### Table 4. Switch Matrix Specifications

| Parameter                    | Min | Тур | Max | Unit | Test Conditions/Comments                         |

|------------------------------|-----|-----|-----|------|--------------------------------------------------|

| R <sub>ON</sub> <sup>1</sup> |     |     |     |      |                                                  |

| Current Carrying Switches    |     |     |     |      |                                                  |

| Dx, DR1, Tx, and TR2         |     | 40  | 50  | Ω    |                                                  |

| IVS                          |     | 40  | 75  | Ω    |                                                  |

| Noncurrent Carrying Switches |     |     |     |      |                                                  |

| Px, Nx, and NR2              | 600 |     | 900 | Ω    |                                                  |

| PR1                          | 600 |     | 950 | Ω    |                                                  |

| NL                           | 260 |     | 350 | Ω    |                                                  |

| PL                           | 210 |     | 260 | Ω    |                                                  |

| DC OFF LEAKAGE <sup>2</sup>  |     |     |     |      |                                                  |

| T and N Switches             |     | 370 |     | рА   | Sum value of four T switches and four N switches |

| P Switches                   |     | 340 |     | pА   | Sum value of four P switches                     |

| D Switches                   |     | 350 |     | pА   | Sum value of four D switches                     |

| Parameter                  | Min | Тур | Max | Unit | Test Conditions/Comments                |

|----------------------------|-----|-----|-----|------|-----------------------------------------|

| DC ON LEAKAGE <sup>2</sup> |     |     |     |      |                                         |

| T, N, and P Switches       |     | 530 |     | рА   | Sum value for 25 switches, including NL |

| D Switches                 |     | 340 |     | pА   | Sum value for eight switches            |

$^1$  Ron characterized with a voltage sweep from 0 V to VCCM. Production tested at 1.8 V.  $^2$  See Figure 38 as a reference. The AFE x pin is driven to 0.2 V.

### TRANSIMPEDANCE AMPLIFIER SPECIFICATIONS

#### Table 5. Transimpedance Amplifier Specifications

| Parameter                              | Min | Тур | Max | Unit | Test Conditions/Comments                                                                              |

|----------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------|

| TRANSIMPEDANCE AMPLIFIER               |     |     |     |      |                                                                                                       |

| Maximum Current Sink/Source            |     | ±5  |     | mA   | Ensure an $R_{\text{TIA}}$ selection to generate $\pm 750$ mV swing for optimal linearity performance |

| Short-Circuit Protection Functionality |     | 10  |     | mA   |                                                                                                       |

## ADC SPECIFICATIONS

#### Table 6. ADC Specifications<sup>1</sup>

| Parameter                    | Min  | Тур  | Мах  | Unit | Test Conditions/Comments                                                                 |

|------------------------------|------|------|------|------|------------------------------------------------------------------------------------------|

| ADC                          |      |      |      |      |                                                                                          |

| Input Range                  | 0.35 |      | 1.85 | V    | Internal reference                                                                       |

| No Missing Codes             |      | 16   |      | Bits |                                                                                          |

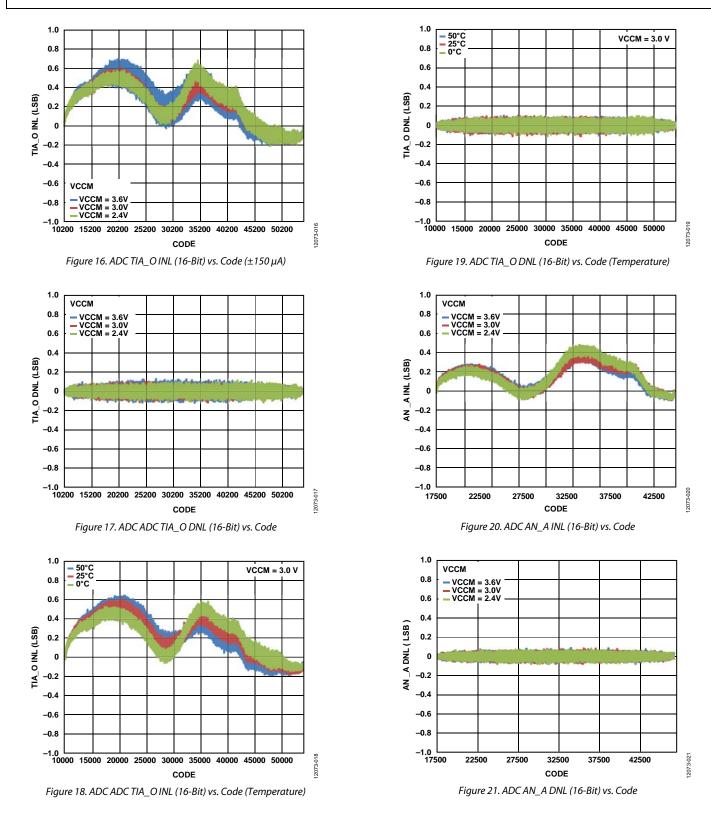

| DNL                          |      | ±0.9 |      | LSB  |                                                                                          |

| INL                          |      | ±0.7 |      | LSB  | @ 160 kSPS with respect to an optimal voltage range of $\pm$ 750 mV, from 0°C to 50°C    |

|                              |      | ±1   |      | LSB  | @ 160 kSPS with respect to an optimal voltage range of $\pm$ 750 mV, from –40°C to +85°C |

| Sample Rate After Decimation |      | 160  |      | kSPS |                                                                                          |

| 3 dB Bandwidth               |      | 54   |      | kHz  |                                                                                          |

$^1$   $R_{\text{TIA}}$  = 7.5 kΩ,  $C_{\text{TIA}}$  = 220 pF; ±100  $\mu\text{A}$  current measurement.

### **TEMPERATURE SENSOR SPECIFICATIONS**

#### **Table 7. Temperature Sensor Specifications**

| Parameter          | Min | Тур | Max | Unit | Test Conditions/Comments         |

|--------------------|-----|-----|-----|------|----------------------------------|

| TEMPERATURE SENSOR |     |     |     |      |                                  |

| Accuracy           |     | ±1  |     | °C   | 0°C to 50°C, trimmed at 25°C     |

|                    |     | ±2  |     | °C   | –40°C to +85°C, trimmed at +25°C |

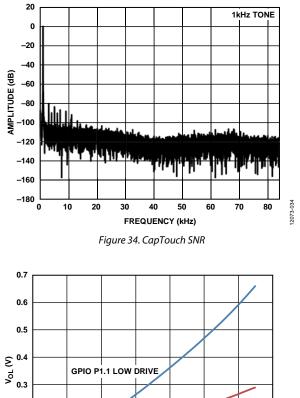

## CapTouch

#### **Table 8. CapTouch Specifications**

| Parameter                             | Min | Тур | Max | Unit | Test Conditions/Comments                                               |

|---------------------------------------|-----|-----|-----|------|------------------------------------------------------------------------|

| CapTouch <sup>™</sup> CHARACTERISTICS |     |     |     |      |                                                                        |

| Core Resolution                       |     | 14  |     | Bits |                                                                        |

| Core SNR                              | 60  |     |     | dB   | 1 kHz test tone, input range of ADC = $1.8$ V                          |

| CAPT_x                                |     | ±10 |     | nA   | GPIO leakage test                                                      |

| Update Rate                           | 7.5 |     | 1E6 | μs   | Programmable, dependent on configuration                               |

| Update Rate per Sensor                | 7.5 |     |     | μs   | No filtering enabled, clock = 16 MHz                                   |

| CAPT_x Input Range                    |     | ±8  |     | pF   | $\Delta C_{\mathbb{N}}$ is register programmable from 0.5 pF to 9.3 pF |

| CAPT_x Offset (CapDAC) Range          |     | 75  |     | pF   |                                                                        |

# **Data Sheet**

# ADuCM350

| Parameter         | Min | Тур | Max | Unit  | Test Conditions/Comments |

|-------------------|-----|-----|-----|-------|--------------------------|

| CapDAC Resolution |     | 0.1 |     | pF    |                          |

| Output Noise      |     |     |     |       |                          |

| Peak-to-Peak      |     | 8   |     | Codes |                          |

| RMS               |     | 1.3 |     | Codes |                          |

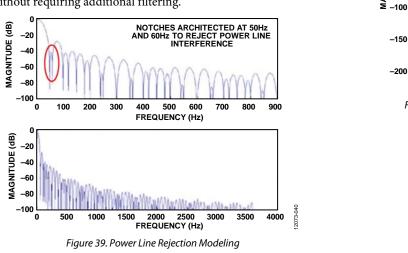

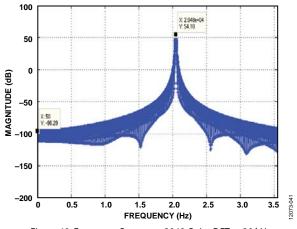

## **DFT-BASED IMPEDANCE MEASUREMENTS**

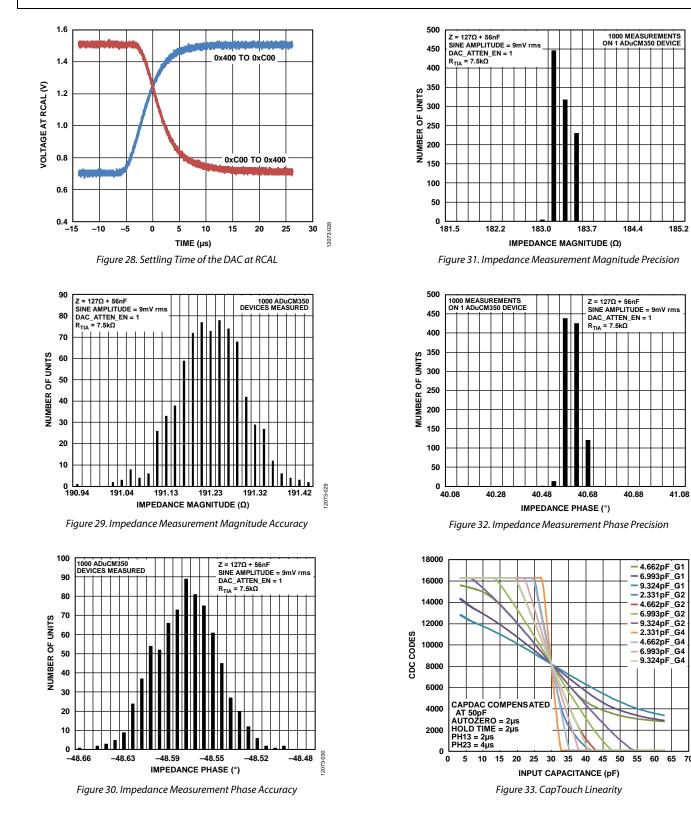

#### Table 9. DFT-Based Impedance Measurements<sup>1</sup>

| Parameter              | Min | Тур | Max  | Unit    | Test Conditions/Comments             |

|------------------------|-----|-----|------|---------|--------------------------------------|

| IMPEDANCE              |     |     |      |         |                                      |

| Accuracy <sup>2</sup>  |     |     |      |         |                                      |

| Magnitude              |     |     | 0.33 | %       | Standard deviation as a percent of Z |

| Phase                  |     |     | 0.17 | Degrees | Standard deviation of Z              |

| Precision <sup>3</sup> |     |     |      |         |                                      |

| Magnitude              |     |     | 0.17 | %       | Standard deviation as a percent of Z |

| Phase                  |     |     | 0.08 | Degrees | Standard deviation of Z              |

<sup>1</sup> For a Z of 181 Ω (0.02% tolerant resistor). Excitation frequency = 20 kHz, sine amplitude = 9 mV<sub>RMS</sub>, R<sub>CAL</sub> = 1 kΩ, R<sub>TIA</sub> = 7.5 kΩ, C<sub>TIA</sub> = 220 pF. Measurements at 25°C. Single DFT measurement.

<sup>2</sup> Device-to-device repeatability for 1000 devices.

<sup>3</sup> Single device, repeatable measurements.

# **DIGITAL PLATFORM**

### Digital LDO

Table 10. Digital LDO Specifications

| Parameter      | Min  | Тур  | Max  | Unit  | Test Conditions/Comments                                                                                            |

|----------------|------|------|------|-------|---------------------------------------------------------------------------------------------------------------------|

| OUTPUT VOLTAGE | 1.71 | 1.8  | 1.89 | V     | Measured with a $C_{LOAD} = 0.47 \ \mu$ F, measured with a 10 mA load current on DVDD                               |

| DROPOUT        |      | 150  | 200  | mV    | 10 mA load applied, no AFE blocks enabled                                                                           |

| REGULATION     |      |      |      |       |                                                                                                                     |

| Line           |      | 1.4  |      | mV/V  | 10 mA load current on DVDD                                                                                          |

| Load           |      | 0.41 |      | mV/mA | 0 mA to 10 mA load current                                                                                          |

| POWER-UP TIME  |      | 42   |      | μs    | Time taken from LDO enable to when LDO voltage is within specification, $C_{LOAD} = 0.47 \mu$ F, regulator unloaded |

### Low Power LDO

#### Table 11. Low Power LDO Specifications

| Parameter      | Min  | Тур  | Max  | Unit  | Test Conditions/Comments |

|----------------|------|------|------|-------|--------------------------|

| OUTPUT VOLTAGE | 1.71 | 1.8  | 1.89 | V     |                          |

| REGULATION     |      |      |      |       |                          |

| Line           |      | 0.45 |      | mV/V  | VCCM = 2.0 V to 3.6 V    |

| Load           |      | 28.5 |      | mV/mA | 0 μA to 100 μA load      |

### Flash/General-Purpose Flash

#### Table 12. Flash/General-Purpose Flash Specifications

| Parameter                   | Min    | Тур | Max | Unit   | Test Conditions/Comments |

|-----------------------------|--------|-----|-----|--------|--------------------------|

| FLASH/GP FLASH              |        |     |     |        |                          |

| Endurance <sup>1</sup>      | 20,000 |     |     | Cycles |                          |

| Erase Time                  |        | 20  |     | ms     | @ 1.8 V                  |

| Program Time                |        | 20  |     | μs     | @ 1.8 V                  |

| Data Retention <sup>2</sup> |        | 100 |     | Years  | Below room temperature   |

<sup>1</sup> Endurance is qualified to 10,000 cycles as per JEDEC Std. 22 Method A117 and measured at -40°C, +25°C, and +125°C. Typical endurance at 25°C is 170,000 cycles. <sup>2</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 85°C as per JEDEC Std. 22 Method A117. Retention lifetime derates with junction temperature.

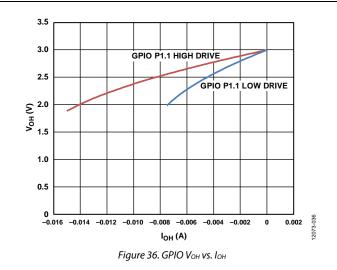

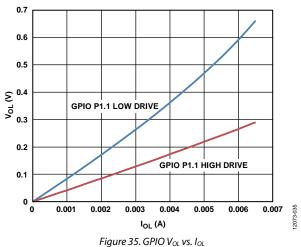

### Digital Inputs/Outputs: Specified

Specified pin supply range from 2.5 V to 3.6 V.

### Table 13. Digital Inputs and Outputs<sup>1</sup> Specifications

| Parameter                                               | Min                  | Тур | Max                  | Unit | Test Conditions/Comments   |

|---------------------------------------------------------|----------------------|-----|----------------------|------|----------------------------|

| PIN SUPPLY                                              | 2.5                  | 3   | 3.6                  | V    |                            |

| Impedance                                               |                      |     |                      |      |                            |

| Pull-Down                                               |                      | 20  |                      | kΩ   | I <sub>SINK</sub> < 10 μA  |

| Pull-Up                                                 |                      | 15  |                      | kΩ   | $I_{SOURCE} < 10  \mu A$   |

| Internal Pull-Up/Pull-Down Enabled Leakage <sup>2</sup> |                      | 200 |                      | μΑ   |                            |

| Digital I/O Leakage Current                             |                      | .01 | 1                    | μΑ   |                            |

| Input Capacitance                                       |                      | 10  |                      | рF   |                            |

| Input Voltage                                           |                      |     |                      |      |                            |

| Low (V <sub>INL</sub> )                                 |                      |     | 0.3 	imes pin supply | V    |                            |

| High (V <sub>INH</sub> )                                | 0.7 	imes pin supply |     |                      | V    |                            |

| Output Voltage                                          |                      |     |                      |      |                            |

| Low (V <sub>OL</sub> )                                  |                      |     | 0.4                  | V    | I <sub>SINK</sub> = 1.0 mA |

| Vol High Drive                                          |                      | 0.4 |                      | V    | I <sub>SINK</sub> = 1.6 mA |

| High (V <sub>он</sub> ) <sup>3</sup>                    | Pin supply – 0.4     |     |                      | V    | Isource = 1.0 mA           |

| V <sub>он</sub> High Drive                              |                      | 2.4 |                      | V    | Isource = 1.6 mA           |

<sup>1</sup> Includes GPIO, debug, SPI, I<sup>2</sup>C, PDI, LCD, I<sup>2</sup>S, and beeper.

<sup>2</sup> See Table 35 for details regarding bumps/pins that have pull-up resistors.

<sup>3</sup> I<sup>2</sup>C does not drive out a high voltage; it uses external pull-up resistors.

### Digital Inputs/Outputs: Functional

Functional pin supply range from 1.65 V to 2.5 V.

#### Table 14. Digital Inputs/Outputs: Functional Specifications

| Parameter                            | Min  | Тур                  | Max | Unit | <b>Test Conditions/Comments</b> |

|--------------------------------------|------|----------------------|-----|------|---------------------------------|

| PIN SUPPLY                           | 1.65 |                      | 2.5 | V    |                                 |

| Input Voltage                        |      |                      |     |      |                                 |

| Low (V <sub>INL</sub> )              |      | 0.3 	imes pin supply |     | v    |                                 |

| High (V <sub>INH</sub> )             |      | 0.7 	imes pin supply |     | V    |                                 |

| Output Voltage                       |      |                      |     |      |                                 |

| Low (V <sub>OL</sub> )               |      | 0.45                 |     | V    | $I_{SINK} = 1.0 \text{ mA}$     |

| High (V <sub>он</sub> ) <sup>1</sup> |      | Pin supply – 0.5     |     | V    | I <sub>SOURCE</sub> = 1.0 mA    |

<sup>1</sup> I<sup>2</sup>C does not drive out a high voltage; it uses external pull-up resistors.

## Universal Serial Bus Regulator Specifications

| Table 15.  | Universal | Serial Bus | Regulator S  | specifications |

|------------|-----------|------------|--------------|----------------|

| 1 4010 15. | Chiverbal | our Duo    | iteguiator c | pecifications  |

| Parameter                | Min | Тур    | Max  | Unit | Test Conditions/Comments                   |

|--------------------------|-----|--------|------|------|--------------------------------------------|

| SERIAL BUS REGULATOR     |     |        |      |      |                                            |

| Input Voltage Range      | 3.6 |        | 5.25 | V    |                                            |

| Regulated Output Voltage | 3.2 |        | 3.4  | V    |                                            |

| Dropout                  |     | 440    |      | mV   | 40 mA continuous current                   |

| Regulation               |     |        |      |      |                                            |

| Line                     |     | 0.0043 |      | %/V  | 4.5 V to 5.5 V                             |

| Load                     |     | 0.0093 |      | %/mA | @ 5 V, 220 nF ceramic decoupling capacitor |

| Power-Up Time            |     | 37     |      | μs   |                                            |

## **Universal Serial Bus DC Specifications**

### Table 16. Universal Serial Bus DC Specifications

| Parameter                           | Min   | Тур | Max   | Unit | Test Conditions/Comments                                                |

|-------------------------------------|-------|-----|-------|------|-------------------------------------------------------------------------|

| RECEIVER                            |       |     |       |      |                                                                         |

| Single-Ended Input Voltage (Driven) |       |     |       |      |                                                                         |

| High                                | 2.0   |     |       | V    |                                                                         |

| Low                                 |       |     | 0.8   | V    |                                                                         |

| Differential Receiver Input         |       |     |       |      |                                                                         |

| Common Mode                         | 0.8   |     | 2.5   | V    |                                                                         |

| Sensitivity                         | 0.2   |     |       | V    | V(USB DP) – V(USB DM)                                                   |

| TRANSMITTER                         |       |     |       |      |                                                                         |

| Output Voltage                      |       |     |       |      |                                                                         |

| Low (V <sub>OL</sub> )              | 0     |     | 0.3   | V    | Pull-up resistor asserted on the USB pin, USB DP, RPU to AVDD           |

| High (V <sub>он</sub> )             | 2.8   |     | 3.6   | V    | Pull-down resistor asserted on USB DP and USB DM (15 k $\Omega$ to GND) |

| Driver Output Impedance             | 28    |     | 44    | Ω    | R <sub>driver</sub> + R <sub>series</sub>                               |

| Term Series Resistor                |       | 40  |       | Ω    |                                                                         |

| Pull-Up Resistor (D+ High)          | 1.425 | 1.5 | 3.095 | kΩ   | Termination voltage = USB regulator voltage                             |

| Pull-Up Resistor (D+ Low)           | 0.9   |     | 1.575 | kΩ   | Termination voltage = USB regulator voltage                             |

| Pull-Down Resistors                 | 14.25 | 15  | 24.8  | kΩ   |                                                                         |

# Universal Serial Bus AC Specifications

Meeting USB 2.0 compliance electrical tests.

### Table 17. Universal Serial Bus AC Specifications

| Parameter                | Min    | Тур | Max   | Unit | <b>Test Conditions/Comments</b>                            |

|--------------------------|--------|-----|-------|------|------------------------------------------------------------|

| FULL SPEED DRIVER TIMING |        |     |       |      | $C_{LOAD} = 50 \text{ pF}$                                 |

| Signaling Rate           | 11.988 | 12  |       | MHz  |                                                            |

| Output Time              |        |     |       |      |                                                            |

| Rise                     | 4      |     | 20    | ns   | $V_{OH} - V_{OL}$ (10% to 90%), $C_{LOAD} = 50 \text{ pF}$ |

| Fall                     | 4      |     | 20    | ns   | $V_{OH} - V_{OL}$ (10% to 90%), $C_{LOAD} = 50 \text{ pF}$ |

| Rise and Fall Matching   | 90     |     | 111.1 | %    | Exclude transition from idle                               |

| Output Voltage Crossover | 1.3    |     | 2.0   | V    | Exclude transition from idle                               |

| FULL SPEED JITTER        |        |     |       |      | $C_{LOAD} = 50 \text{ pF}$                                 |

| Driver Jitter Generated  | -2     |     | +2    | ns   | Next transitions                                           |

|                          | -1     |     | +1    | ns   | Paired transitions                                         |

| Load Capacitance         |        |     | 50    | рF   | Testing slew rate                                          |

## LCD, Charge Pump

Table 18. LCD, Charge Pump Specifications

| Parameter                                             | Min           | Тур  | Max           | Unit | Test Conditions/Comments                                                                                      |

|-------------------------------------------------------|---------------|------|---------------|------|---------------------------------------------------------------------------------------------------------------|

| CAPACITANCE                                           |               | ·    |               |      |                                                                                                               |

| Reservoir Capacitance Between<br>VLCDVDD and VLCD_GND | 0.47          | 1    |               | μF   |                                                                                                               |

| Flying Capacitance                                    | 2.2           |      | 4.7           | nF   | Between VLCD FLY1 and VLCD FLY2                                                                               |

| VLCD                                                  |               |      |               |      |                                                                                                               |

| Switching Voltage                                     |               |      |               |      |                                                                                                               |

| VLCD FLY1                                             | -0.7          |      | VLCD + 0.2    | V    | Top of flying capacitor                                                                                       |

| VLCD FLY2                                             | 0             |      | VCCM          | V    | Bottom of flying capacitor                                                                                    |

| VLCD Charge Pump Switching<br>Frequency               |               | 32   |               | kHz  |                                                                                                               |

| Minimum VLCD with Respect to<br>VCCM_ANA and VCCM_DIG | 2.1           |      |               | V    | When <2.1 V after 62.5 ms elapses indicates fault condition                                                   |

| VLCDVDD                                               |               |      |               |      |                                                                                                               |

| VLCDVDD Voltage Range                                 | 2.4           |      | 3.65          | V    | 5-bit programmable in steps of 40 mV                                                                          |

| VLCDVDD Pin Leakage                                   |               | 3    |               | nA   | To VCCM                                                                                                       |

|                                                       |               | 0.2  |               | nA   | To GND                                                                                                        |

| VLCDVDD Start-Up Time                                 |               | 5    |               | ms   | VLCDVDD = 0 V to 3.6 V, reservoir = 1 $\mu$ F,<br>flying capacitor = 2.2 nF (minimum) and<br>4.7 nF (maximum) |

| VLCDVDD Line Regulation                               |               | 0.32 |               | %    |                                                                                                               |

| V_LCD_xx VOLTAGE RANGE                                |               |      |               |      |                                                                                                               |

| V_LCD_13 Voltage Range                                | VLCD ÷ 3 – 10 |      | VLCD ÷ 3 + 10 | mV   |                                                                                                               |

| V_LCD_23 Voltage Range                                | 2/3 VLCD – 13 |      | 2/3 VLCD + 13 | mV   |                                                                                                               |

| COMx PINS                                             |               |      |               |      |                                                                                                               |

| DC Voltage Across Segment and<br>COMx Pins            |               |      | 50            | mV   |                                                                                                               |

| PIN OUTPUT IMPEDANCE                                  |               |      |               |      |                                                                                                               |

| Segment                                               |               | 2000 |               | Ω    |                                                                                                               |

| Common                                                |               | 130  |               | Ω    |                                                                                                               |

## SYSTEM CLOCKS/TIMERS

The following tables document the system clock specifications in the ADuCM350.

## Platform External Crystal Oscillator

## Table 19. Platform External Crystal Oscillator Specifications

| Parameter             | Min | Тур Мах |    | Unit | Test Conditions/Comments                       |  |  |

|-----------------------|-----|---------|----|------|------------------------------------------------|--|--|

| LOW FREQUENCY         |     |         |    |      |                                                |  |  |

| $C_{EXT}1 = C_{EXT}2$ | 12  | 15      | 18 | pF   | External capacitor, C1 = C2 (symmetrical load) |  |  |

| Frequency             |     | 32,768  |    | Hz   |                                                |  |  |

| HIGH FREQUENCY        |     |         |    |      |                                                |  |  |

| $C_{EXT}1 = C_{EXT}2$ | 10  | 12      | 15 | pF   | External capacitor                             |  |  |

| Frequency             |     | 8 or 16 |    | MHz  |                                                |  |  |

# **On-Chip RC Oscillators**

Table 20. On-Chip RC Oscillators Specifications

| Parameter                    | Min | Тур    | Мах | Unit | Test Conditions/Comments |

|------------------------------|-----|--------|-----|------|--------------------------|

| HIGH FREQUENCY RC OSCILLATOR |     |        |     |      |                          |

| Frequency                    |     | 16     |     | MHz  |                          |

| Accuracy                     | -5  |        | +5  | %    |                          |

| Start-Up Time                |     | 35     |     | μs   |                          |

| LOW FREQUENCY RC OSCILLATOR  |     |        |     |      |                          |

| Frequency                    |     | 32,768 |     | Hz   |                          |

| Accuracy                     | -20 |        | +20 | %    |                          |

| Start-Up Time                |     | 980    |     | μs   |                          |

# PLLs

### Table 21. PLL Specifications

| Parameter        | Min | Тур | Max  | Unit | Test Conditions/Comments |  |  |

|------------------|-----|-----|------|------|--------------------------|--|--|

| SYSTEM PLL       |     |     |      |      |                          |  |  |

| Input Frequency  | 8   | 16  |      | MHz  |                          |  |  |

| Output Frequency |     | 16  | 32   | MHz  |                          |  |  |

| Frequency Error  |     |     | 2500 | ppm  |                          |  |  |

| RMS Jitter       |     |     | 92   | ps   | @ 32 MHz, external XTAL  |  |  |

| USB PLL          |     |     |      |      |                          |  |  |

| Input Frequency  | 8   | 16  |      | MHz  |                          |  |  |

| Output Frequency | 16  |     | 60   | MHz  | 16 MHz input             |  |  |

| Frequency Error  |     |     | 2500 | ppm  |                          |  |  |

| Period Jitter    |     |     | 68   | ps   | @ 60 MHz, external XTAL  |  |  |

### Watchdog, Wake-Up, and General-Purpose Timers

### Table 22. Watchdog, Wake-Up, and General-Purpose Timers Specifications

| Parameter <sup>1</sup>     | Min | Min Typ Ma |    | Unit  | Test Conditions/Comments            |

|----------------------------|-----|------------|----|-------|-------------------------------------|

| WATCHDOG TIMERS            |     |            |    |       |                                     |

| Timeout Period             |     |            |    |       |                                     |

| Shortest                   |     | 0.03       |    | ms    | 32,768 Hz clock, prescaler = 1      |

| Longest                    |     | 8191       |    | sec   | 32,768 Hz clock, prescaler = 4096   |

| WAKE-UP TIMERS             |     |            |    |       |                                     |

| Timeout Period             |     |            |    |       |                                     |

| Shortest                   |     | 62.5       |    | ns    | 16 MHz clock, prescaler = 1         |

| Longest                    |     | 136        |    | Years | 32,768 Hz clock, prescaler = 32,768 |

| GENERAL-PURPOSE TIMER × 3  |     |            |    |       |                                     |

| Timeout Period             |     |            |    |       |                                     |

| Shortest                   |     | 62.5       |    | ns    | 16 MHz clock, prescaler = 1         |

| Longest                    |     | 65,535     |    | sec   | 32,768 Hz clock, prescaler = 32,768 |

| Timer Output PWM Frequency | 1   |            | 16 | MHz   |                                     |

<sup>1</sup> Guaranteed by design.

## POWER MANAGEMENT SPECIFICATIONS

The following tables cover the specifications for the power management section of the ADuCM350.

## **Power Supplies**

#### **Table 23. Power Supplies Specifications**

| Parameter         | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                      |

|-------------------|------|-----|------|------|-------------------------------------------------------------------------------|

| SUPPLIES          |      |     |      |      |                                                                               |

| VCCM_ANA/VCCM_DIG | 2    |     | 3.6  | V    | VCCM_x pins connected to the CR2032 battery, main supply for ADuCM350         |

| VCCM_ANA/VCCM_DIG | 2.5  |     | 3.6  | V    | Battery operating range                                                       |

| VBACK             | 1.62 |     | 3.6  | V    | Super capacitor pin, back-up mode supply                                      |

| VBUS              | 4.75 | 5   | 5.25 | V    | USB 5 V supply                                                                |

| VDD_IO            | 1.8  |     | 3.6  | V    | Supply for some digital I/O pads; see Table 35, I/O supply column for details |

| VLCDVDD           | 1.8  |     | 3.6  | V    | Supply for LCD I/O                                                            |

#### Power Supply Monitoring

### Table 24. Power Supply Monitoring Specifications

| Parameter <sup>1</sup>        | Min  | Тур | Max            | Unit | Test Conditions/Comments |

|-------------------------------|------|-----|----------------|------|--------------------------|

| VCCM PSM                      |      |     |                |      |                          |

| Voltage Detection Range       | 1.7  |     | 3.2            | V    | 100 mV step size         |

| Hysteresis                    | ±10  |     | ±100           | mV   |                          |

| Trip Point Detection Accuracy |      |     | Hysteresis ±70 | mV   |                          |

| VRTC PSM                      |      |     |                |      |                          |

| Voltage Detection Range       | 1.55 |     | 1.7            | V    | 100 mV step size         |

| Hysteresis                    | ±25  |     | ±100           | mV   |                          |

| Trip Point Detection Accuracy |      |     | Hysteresis ±70 | mV   |                          |

| VBACK PSM                     |      |     |                |      |                          |

| Voltage Detection Range       | 1.7  |     | 3.2            | V    | 100 mV step size         |

| Hysteresis                    |      |     | ±100           | mV   |                          |

| Trip Point Detection Accuracy |      |     | Hysteresis ±70 | mV   |                          |

$^{\rm 1}$  For details regarding these parameters, see the UG-587 hardware reference manual.

## **TRICKLE CHARGER**

#### Table 25. Trickle Charger Specifications

| Parameter       | Min | Тур  | Max | Unit | Test Conditions/Comments               |  |  |

|-----------------|-----|------|-----|------|----------------------------------------|--|--|

| CURRENT         |     |      |     |      |                                        |  |  |

| Charge Current  |     | 0.48 |     | mA   | Limits load on button cell at power-up |  |  |

| Reverse Current |     |      | 1   | μA   |                                        |  |  |

| VOLTAGE         |     |      |     |      |                                        |  |  |

| Forward Voltage |     | 40   | 120 | mV   | Where forward current reduces to zero  |  |  |

Unit

μs

ns

μs ns

μs

μs

### TIMING CHARACTERISTICS

LCD Segment/Common Timing Specifications

|             |             |             |             | Static Mux            |                 |                       | 4× Mux          |

|-------------|-------------|-------------|-------------|-----------------------|-----------------|-----------------------|-----------------|

| FRAMESEL[3] | FRAMESEL[2] | FRAMESEL[1] | FRAMESEL[0] | f <sub>LCD</sub> (Hz) | Frame Rate (Hz) | f <sub>LCD</sub> (Hz) | Frame Rate (Hz) |

| 0           | 0           | 0           | 0           | 256                   | 128             | 1024                  | 128             |

| 0           | 0           | 0           | 1           | 204.8                 | 102.4           | 819.2                 | 102.4           |

| 0           | 0           | 1           | 0           | 170.7                 | 85.3            | 682.7                 | 85.3            |

| 0           | 0           | 1           | 1           | 146.3                 | 73.1            | 585.1                 | 73.1            |

| 0           | 1           | 0           | 0           | 128                   | 64              | 512                   | 64              |

| 0           | 1           | 0           | 1           | 113.8                 | 56.9            | 455.1                 | 56.9            |

| 0           | 1           | 1           | 0           | 102.4                 | 51.2            | 409.6                 | 51.2            |

| 0           | 1           | 1           | 1           | 93.1                  | 46.5            | 372.4                 | 46.5            |

| 1           | 0           | 0           | 0           | 85.3                  | 42.7            | 341.3                 | 42.7            |

| 1           | 0           | 0           | 1           | 78.8                  | 39.4            | 315.1                 | 39.4            |

| 1           | 0           | 1           | 0           | 73.1                  | 36.6            | 292.6                 | 36.6            |

| 1           | 0           | 1           | 1           | 68.3                  | 34.1            | 273.1                 | 34.1            |

| 1           | 1           | 0           | 0           | 64                    | 32              | 256                   | 32              |

| 1           | 1           | 0           | 1           | 60.2                  | 30.1            | 240.9                 | 30.1            |

| 1           | 1           | 1           | 0           | 56.9                  | 28.4            | 227.6                 | 28.4            |

| 1           | 1           | 1           | 1           | 53.9                  | 26.9            | 215.6                 | 26.9            |

$^1$  f<sub>LCD</sub> = f<sub>BCLK</sub>/(FRAMESEL + 4). See the UG-587 hardware reference manual for details  $^2$  FRAMESEL[3], FRAMESEL[2], FRAMESEL[1], and FRAMESEL[0] indicate the bit numbers in the LCD\_COM register.

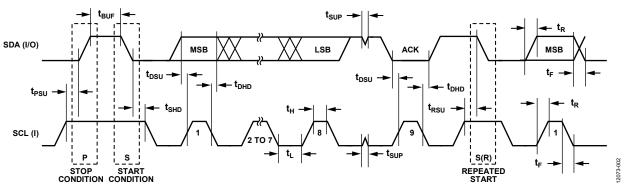

#### I<sup>2</sup>C Timing

Capacitive load for each of the I<sup>2</sup>C bus lines (C<sub>B</sub>) = 400 pF maximum as per I<sup>2</sup>C bus specifications; I<sup>2</sup>C timing is guaranteed by design and not production tested.

#### Table 27. I<sup>2</sup>C Timing in Fast Mode (400 kHz)

| Parameter                     | Description                                                  | Min         | Max | Unit |

|-------------------------------|--------------------------------------------------------------|-------------|-----|------|

| tL                            | Clock low pulse width                                        | 1300        |     | ns   |

| tн                            | Clock high pulse width                                       | 600         |     | ns   |

| t <sub>SHD</sub>              | Start condition hold time                                    | 600         |     | ns   |

| t <sub>DSU</sub>              | Data setup time                                              | 100         |     | ns   |

| t <sub>DHD</sub> <sup>1</sup> | Data hold time                                               | 0           |     | ns   |

| t <sub>RSU</sub>              | Setup time for repeated start                                | 600         |     | ns   |

| t <sub>PSU</sub>              | Stop condition setup time                                    | 600         |     | ns   |

| t <sub>BUF</sub>              | Bus-free time between a stop condition and a start condition | 1.3         |     | μs   |

| t <sub>R</sub>                | Rise time for both clock and data                            | 20 + 0.1 Cb | 300 | ns   |

| tF                            | Fall time for both clock and data                            | 20 + 0.1 Cb | 300 | ns   |

| tsup                          | Pulse width of spike suppressed                              | 0           | 50  | ns   |

<sup>1</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>INH</sub> (minimum) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

| 1 able 28.1 C 1               | Table 28. I'C Timing in Standard Mode (100 KHz) |     |     |  |  |  |

|-------------------------------|-------------------------------------------------|-----|-----|--|--|--|

| Parameter                     | Description                                     | Min | Max |  |  |  |

| t∟                            | Clock low pulse width                           | 4.7 |     |  |  |  |

| t <sub>H</sub>                | Clock high pulse width                          | 4.0 |     |  |  |  |

| <b>t</b> <sub>SHD</sub>       | Start condition hold time                       | 4.7 |     |  |  |  |

| t <sub>DSU</sub>              | Data setup time                                 | 250 |     |  |  |  |

| t <sub>DHD</sub> <sup>1</sup> | Data hold time                                  | 0   |     |  |  |  |

| t <sub>RSU</sub>              | Setup time for repeated start                   | 4.0 |     |  |  |  |

## Table 28 J<sup>2</sup>C Timing in Standard Mode (100 kHz)

# **Data Sheet**

| Parameter      | Description                                                  | Min | Max | Unit |

|----------------|--------------------------------------------------------------|-----|-----|------|

| <b>t</b> PSU   | Stop condition setup time                                    | 4.0 |     | μs   |

| tBUF           | Bus-free time between a stop condition and a start condition | 4.7 |     | μs   |

| t <sub>R</sub> | Rise time for both clock and data                            |     | 1   | μs   |

| t <sub>F</sub> | Fall time for both clock and data                            |     | 300 | ns   |

<sup>1</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>INH</sub> (minimum) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

Figure 2. I<sup>2</sup>C-Compatible Interface Timing

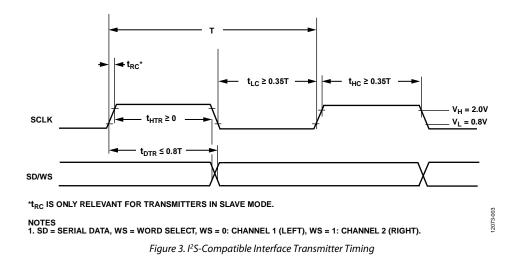

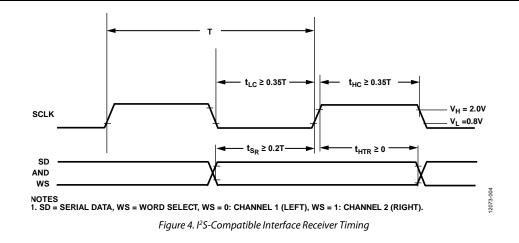

### **I<sup>2</sup>S Timing Specifications**

I<sup>2</sup>S timing is guaranteed by design and not production tested; timing specifications are given for a standard I<sup>2</sup>S data rate of 2.5 MHz; the I<sup>2</sup>S bus is designed to operate up to 25 MHz.

#### Table 29. I<sup>2</sup>S Timing: Master Transmitter

| Parameter                                  | Symbol                  | Min | Тур | Max | Unit | Test Conditions/Comments <sup>1</sup>                                                                                   |

|--------------------------------------------|-------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> S MASTER TRANSMITTER TIMING |                         |     |     |     |      |                                                                                                                         |

| SCLK Period                                | Т                       | 360 | 400 | 440 | ns   |                                                                                                                         |

| Minimum Clock Period                       | T <sub>TR</sub>         | 360 |     |     | ns   | $T_{TR}$ is the minimum allowed clock period for the transmitter, T > $T_{TR}$                                          |

| Clock High Period                          | t <sub>HC</sub>         | 160 |     |     | ns   | Minimum > 0.35 × T = 140 ns                                                                                             |

| Clock Low Period                           | t <sub>LC</sub>         | 160 |     |     | ns   | Minimum > 0.35 × T = 140 ns                                                                                             |

| Delay                                      | <b>t</b> <sub>DTR</sub> |     |     | 300 | ns   | Minimum < 0.80 × T = 320 ns                                                                                             |

| Data Hold Time                             | <b>t</b> <sub>HTR</sub> | 100 |     |     | ns   | Minimum > 0 ns                                                                                                          |

| Clock Rise Time                            | t <sub>RC</sub>         |     |     | 60  | ns   | $\label{eq:minimum} \begin{array}{l} \mbox{Minimum} > 0.15 \times T_{TR} = 54 \mbox{ ns (slave mode only)} \end{array}$ |

<sup>1</sup> T refers to the typical value listed for the SCLK period; therefore, T = 400 ns in this case.

### Table 30. I<sup>2</sup>S Timing: Slave Receiver

| Parameter                              | Symbol           | Min | Тур | Max | Unit | Test Conditions/Comments <sup>1</sup>     |

|----------------------------------------|------------------|-----|-----|-----|------|-------------------------------------------|

| I <sup>2</sup> S SLAVE RECEIVER TIMING |                  |     |     |     |      |                                           |

| SCLK Period                            | Т                | 360 | 400 | 440 | ns   | T <sub>TR</sub> = 360 ns                  |

| Clock High Period                      | t <sub>HC</sub>  | 110 |     |     | ns   | Minimum < 0.35 × T = 126 ns               |

| Clock Low Period                       | t∟c              | 160 |     |     | ns   | Minimum < 0.35 × T = 126 ns               |

| Data Setup Time                        | t <sub>sr</sub>  |     |     | 300 | ns   | $Minimum < 0.20 \times T = 72 \text{ ns}$ |

| Data Hold Time                         | t <sub>HTR</sub> | 100 |     |     | ns   | Minimum < 0 ns                            |

<sup>1</sup> T refers to the typical value listed for the SCLK period; therefore, T = 400 ns in this case.

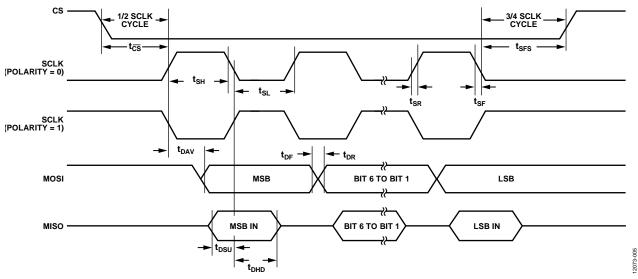

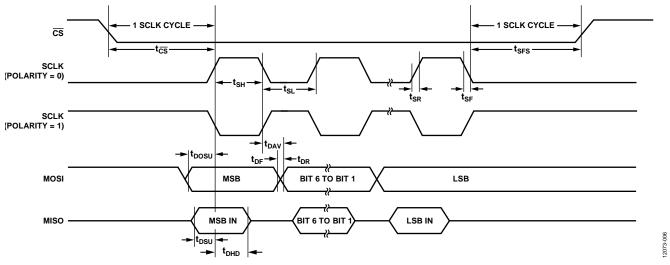

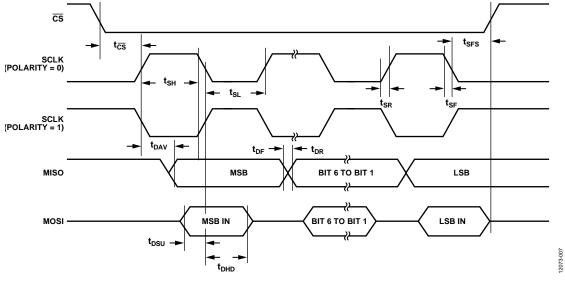

## SPI Timing

SPIH can be used for high data rate peripherals.

| Parameter         | Description                                     | Min                            | Тур                                  | Max  | Unit |

|-------------------|-------------------------------------------------|--------------------------------|--------------------------------------|------|------|

| t <sub>sL</sub>   | SCLK low pulse width <sup>2</sup>               |                                | $(SPIXDIV[5:0] + 1) \times t_{UCLK}$ |      | ns   |

| t <sub>sH</sub>   | SCLK high pulse width <sup>2</sup>              |                                | $(SPIXDIV[5:0] + 1) \times t_{UCLK}$ |      | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLK edge               |                                | 0                                    | 35.5 | ns   |

| t <sub>DOSU</sub> | Data output setup before SCLK edge <sup>2</sup> | $(SPIDIV + 1) \times t_{UCLK}$ |                                      |      | ns   |

| <b>t</b> DSU      | Data input setup time before SCLK edge          | 58.7                           |                                      |      | ns   |

| <b>t</b> DHD      | Data input hold time after SCLK edge            | 16                             |                                      |      | ns   |

| t <sub>DF</sub>   | Data output fall time                           |                                | 12                                   | 35.5 | ns   |

| t <sub>DR</sub>   | Data output rise time                           |                                | 12                                   | 35.5 | ns   |

| t <sub>sr</sub>   | SCLK rise time                                  |                                | 12                                   | 35.5 | ns   |

| tsF               | SCLK fall time                                  |                                | 12                                   | 35.5 | ns   |

<sup>1</sup> Guaranteed by design.

$^{2}$  t<sub>UCLK</sub> = 62.5 ns. It corresponds to the maximum internal clock frequency before clock dividers.

Figure 5. SPI Master Mode Timing (Phase Mode = 1)

# Data Sheet

# ADuCM350

Figure 6. SPI Master Mode Timing (Phase Mode = 0)

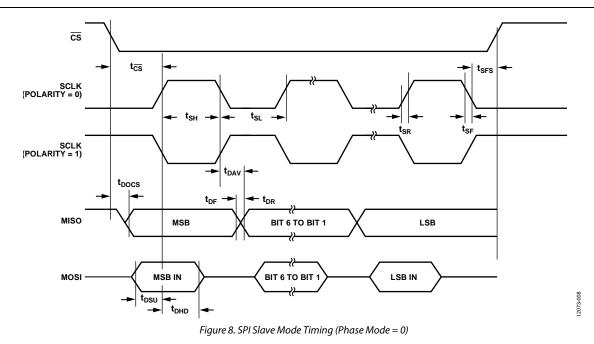

| Table 32. | SPI Slave | Mode Timing |

|-----------|-----------|-------------|

|-----------|-----------|-------------|

| Parameter        | Description                            | Min  | Тур                          | Max             | Unit |

|------------------|----------------------------------------|------|------------------------------|-----------------|------|

| t <sub>cs</sub>  | CS to SCLK edge                        | 38   |                              |                 | ns   |

| tsL              | SCLK low pulse width <sup>1</sup>      |      | (SPIXDIV[5:0] + 1) >         | < <b>t</b> υclκ | ns   |

| t <sub>sн</sub>  | SCLK high pulse width <sup>1</sup>     | 62.5 | $(SPIDIV[5:0] + 1) \times 1$ | tuclk           | ns   |

| t <sub>DAV</sub> | Data output valid after SCLK edge      |      |                              | 49.1            | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge | 20.2 |                              |                 | ns   |

| t <sub>DHD</sub> | Data input hold time after SCLK edge   | 10.1 |                              |                 | ns   |

| t <sub>DF</sub>  | Data output fall time                  |      | 12                           | 35.5            | ns   |

| t <sub>DR</sub>  | Data output rise time                  |      | 12                           | 35.5            | ns   |

| tsr              | SCLK rise time                         |      | 12                           | 35.5            | ns   |

| t <sub>sF</sub>  | SCLK fall time                         |      | 12                           | 35.5            | ns   |

| tDOCS            | Data output valid after CS edge        |      |                              | 25              | ns   |

| t <sub>SFS</sub> | CS high after SCLK edge                | 0    |                              |                 | ns   |

$^{1}$  t<sub>UCLK</sub> = 62.5 ns. It corresponds to the maximum internal clock frequency before clock dividers.

Figure 7. SPI Slave Mode Timing (Phase Mode = 1)

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 33.

| Table 33.                                  |                   |

|--------------------------------------------|-------------------|

| Parameter                                  | Rating            |

| Supplies                                   |                   |

| VCCM_ANA, VCCM_DIG, VLCDVDD,               | –0.3 V to +3.6 V  |

| VDD_IO, VBACK to AGND_x/DGNDx              |                   |

| Decoupling                                 |                   |

| DVDD, AVDD_RX/TX, VBIAS, VREF, VUSB        | –0.3 V to +2.0 V  |

| Digital Input/Output                       |                   |

| P0.x, P1.x, P2.x, P3.x, P4.x, BOOT, RESETX | –0.3 V to +3.6 V  |

| TRACEx                                     | –0.3 V to +3.6 V  |

| Switch Matrix (RCAL 1, RCAL 2, AFE x)      | –0.3 V to +3.6 V  |

| TIA (TIA_I, TIA_O)                         | –0.3 V to +3.6 V  |

| Analog Inputs (AN_x)                       | –0.3 V to +3.6 V  |

| REF_EXCITE                                 | –0.3 V to +1.98 V |

| VLCD FLY1, VLCD FLY2                       | –0.3 V to +3.6 V  |

| V_LCD_13, V_LCD_23                         | –0.3 V to +3.6 V  |

| VBUS to DGND                               | –0.3 V to +5.25 V |

| USB DM, USB DP to DGND                     | –0.3 V to +3.6 V  |

| HF_XTALx, LF_XTALx                         | –0.3 V to +1.98 V |

| Analog Ground to Digital Ground            |                   |

| AGND CTOUCH, AGND_RX/TX, AGND_REF          | –0.3 V to +0.3 V  |

| to DGND, DGND1, DGND2, DGND USB            |                   |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages; assumes use of a JEDEC 4-layer board.

#### Table 34. Thermal Resistance

| Package Type | Αιθ | Unit |

|--------------|-----|------|

| CSP_BGA      | 35  | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

12073-009

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

|   | 1                      | 2                      | 3                     | 4                          | 5                   | 6                        | 7                         | 8               | 9                   | 10                             | 11                | 12                | 13        | 14                 | 15                               |

|---|------------------------|------------------------|-----------------------|----------------------------|---------------------|--------------------------|---------------------------|-----------------|---------------------|--------------------------------|-------------------|-------------------|-----------|--------------------|----------------------------------|

| A | DNC                    | P2.1/<br>COM1/<br>RESX | P2.3/<br>COM3/<br>DCX | P2.5/S2/<br>ECLOCK-<br>WRX | P1.0/S3/<br>D0/SCL  | P1.2/S5/<br>D2/DIN       | P1.4/S7/<br>D4            | P1.6/S9/<br>D6  | P1.8/S11/<br>D8     | P1.10/<br>S13/D10              | P1.12/<br>S15/D12 | P1.14/<br>S17/D14 | P2.10/S23 | P2.9/S22           | P2.15/S28                        |

| в | V_LCD_23               | P2.0/<br>COM0          | P2.2/<br>COM2/<br>CSX | P2.4/S1/<br>RWX-RDX        | P1.1/S4/<br>D1/DOUT | P1.3/S6/<br>D3           | P1.5/S8/<br>D5            | P1.7/S10/<br>D7 | P1.9/S12/<br>D9     | P1.11/<br>S14/D11              | P1.13/<br>S16/D13 | P1.15/<br>S18/D15 | P2.11/S24 | P2.12/S25          | P2.8/S21                         |

| с | HF_XTAL2               | V_LCD_13               |                       |                            |                     |                          |                           |                 |                     |                                |                   |                   |           | P3.10/S31          | P2.7/S20/<br>TOUTA               |

| D | HF_XTAL1               | VLCDVDD                |                       |                            |                     |                          |                           |                 |                     |                                |                   |                   |           | P2.13/S26          | P2.6/<br>S19/TE                  |

| Е | VUSB                   | VLCD FLY1              |                       |                            |                     |                          |                           |                 |                     |                                |                   |                   |           | P3.11/S32          | P2.14/S27                        |

| F | USB DM                 | VLCD FLY2              |                       |                            |                     | DGND<br>USB              | DGND2/<br>LCD_GND         | P3.8/S29        | P3.9/S30            | P3.3/<br>SPI0_CS               |                   |                   |           | P3.0/<br>SPI0_SCLK | P3.2/<br>SPI0_MOSI               |

| G | USB DP                 | VBUS                   |                       |                            |                     | DGND1                    |                           |                 |                     | P3.4/<br>I2CSCL/<br>SPI1_SCLK  |                   |                   |           | P3.1/<br>SPI0_MISO | P3.6/UTX/<br>TOUTB/<br>SPI1_MOSI |

| н | TMS-<br>SWDIO/<br>P0.8 | TCK-<br>SWCLK/<br>P0.9 |                       |                            |                     | VCCM_<br>DIG             |                           |                 |                     | P3.5/<br>I2CSD/<br>SPI1_MISO   |                   |                   |           | DGND               | VDD_IO                           |

| J | TDO-SWO/<br>P0.6/UTX   | TDI/P0.7/<br>URX       |                       |                            |                     | P3.14/<br>LRCLK          |                           |                 |                     | P3.7/URX/<br>TOUTC/<br>SPI1_CS |                   |                   |           | P0.4/<br>CAPT_E    | P0.1/<br>CAPT_B                  |

| к | DVDD                   | P0.11                  |                       |                            |                     | P3.12/<br>BEEP/<br>BMCLK | P3.13/<br>BEEPX/<br>SDATA | RESETX          | AGND_RX/<br>AGND_TX | AGND_REF                       |                   |                   |           | P0.3/<br>CAPT_D    | P0.0/<br>CAPT_A                  |

| L | P4.0/<br>I2CSCL        | P4.1/<br>I2CSD         |                       |                            |                     |                          |                           |                 |                     |                                |                   |                   |           | P0.5/<br>CAPT_F    | P0.2/<br>CAPT_C                  |

| м | VBACK                  | P0.15/<br>SPIH_CS      |                       |                            |                     |                          |                           |                 |                     |                                |                   |                   |           | TRACE0             | TRACECLK                         |

| N | LF_XTAL2               | BOOT                   |                       |                            |                     |                          |                           |                 |                     |                                |                   |                   |           | TRACE2             | TRACE1                           |

| Ρ | LF_XTAL1               | P0.13/<br>SPIH_MISO    | P0.14/<br>SPIH_MOSI   | VCCM_<br>ANA               | RCAL 1              | AFE 2                    | AFE 4                     | AFE 6           | AFE 8               | VBIAS                          | TIA_I             | AN_A              | AN_B      | AGND<br>CTOUCH     | TRACE3                           |

| R | P4.2/<br>TOUTB         | P0.10/<br>TOUTC        | P0.12/<br>SPIH_SCLK   | AVDD_RX/<br>AVDD_TX        | RCAL 2              | AFE 1                    | AFE 3                     | AFE 5           | AFE 7               | VREF                           | TIA_O             | REF_<br>EXCITE    | AN_C      | AN_D               | TRST                             |

Figure 9. Bump Location (Top View Looking Through Device, Bumps Not to Scale)

#### Table 35. Pin Function Descriptions

| Pin No.   | Mnemonic | <b>I/O</b> <sup>1</sup> | I/O Supply <sup>2</sup> | GPIO<br>Pull-Up/Down <sup>2</sup> | Description                                                                                                                                                                        |

|-----------|----------|-------------------------|-------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power and | Ground   |                         |                         |                                   |                                                                                                                                                                                    |