### 16-bit Microcontroller

**CMOS**

# F<sup>2</sup>MC-16LX MB90330A Series

## MB90333A/F334A/F335A/V330A

#### **■ DESCRIPTION**

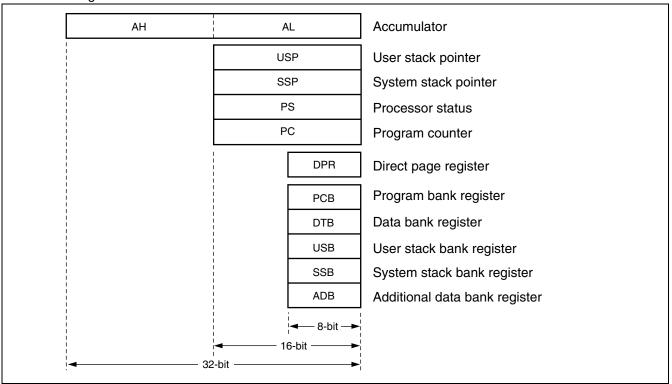

The MB90330A series are 16-bit microcontrollers designed for applications, such as personal computer peripheral devices, that require USB communications. The USB feature supports not only 12-Mbps Function operation but also HOST operation. It is equipped with functions that are suitable for personal computer peripheral devices such as displays and audio devices, and control of mobile devices that support USB communications. While inheriting the AT architecture of the F<sup>2</sup>MC family, the instruction set supports the C language and extended addressing modes and contains enhanced signed multiplication and division instructions as well as a substantial collection of improved bit manipulation instructions. In addition, long word processing is now available by introducing a 32-bit accumulator.

Note: F2MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

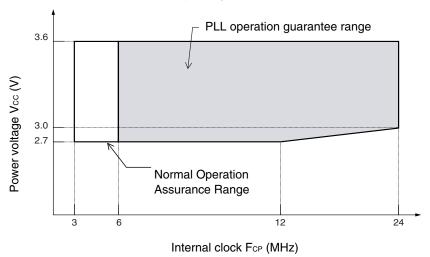

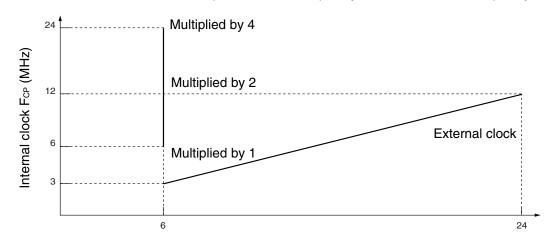

- Clock

- Built-in oscillation circuit and PLL clock frequency multiplication circuit

- Oscillation clock

- The main clock is the oscillation clock divided into 2 (for oscillation 6 MHz : 3 MHz)

- Clock for USB is 48 MHz

- Machine clock frequency of 6 MHz, 12 MHz, or 24 MHz selectable

- Minimum execution time of instruction : 41.7 ns (6 MHz oscillation clock, 4-time multiplied : machine clock 24 MHz and at operating Vcc = 3.3 V).

- The maximum memory space : 16 Mbytes

- 24-bit addressing

(Continued)

For the information for microcontroller supports, see the following web site.

This web site includes the "Customer Design Review Supplement" which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

#### (Continued)

#### Bank addressing

#### • Instruction system

- · Data types : Bit, Byte, Word and Long word

- Addressing mode (23 types)

- Enhanced high-precision computing with 32-bit accumulator

- Enhanced Multiply/Divide instructions with sign and the RETI instruction

#### Instruction system compatible with high-level language (C language) and multi-task

- · Employing system stack pointer

- Instruction set symmetry and barrel shift instructions

#### • Program Patch Function (2 address pointer)

#### • 4-byte instruction queue

#### • Interrupt function

- Priority levels are programmable

- 32 interrupts function

#### Data transfer function

- Extended intelligent I/O service function (El<sup>2</sup>OS): Maximum of 16 channels

- μDMAC : Maximum 16 channels

#### • Low Power Consumption Mode

- Sleep mode (with the CPU operating clock stopped)

- Time-base timer mode (with the oscillator clock and time-base timer operating)

- Stop mode (with the oscillator clock stopped)

- CPU intermittent operation mode (with the CPU operating at fixed intervals of set cycles)

- Watch mode (with 32 kHz oscillator clock and watch timer operating)

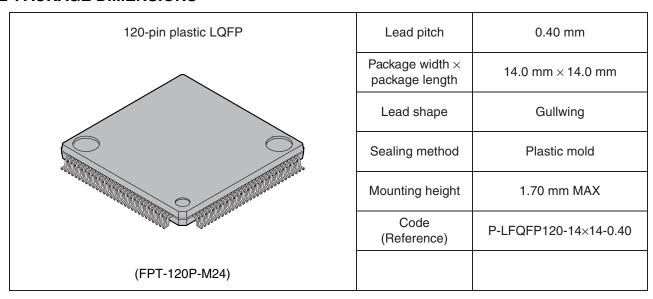

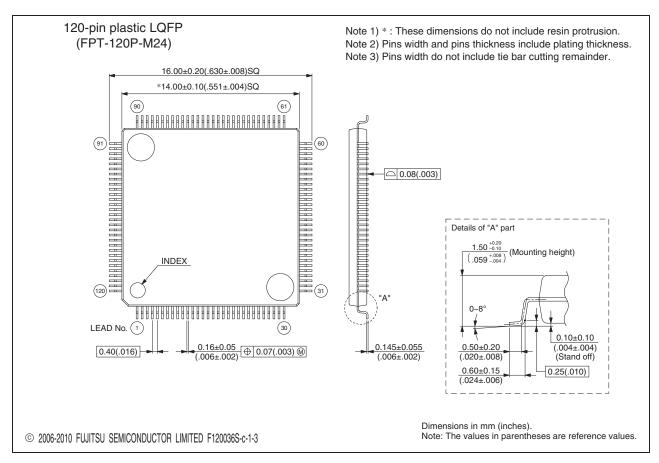

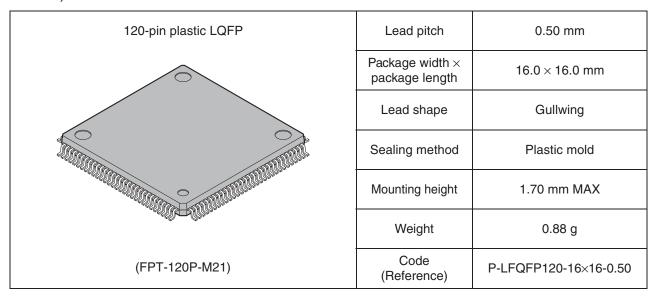

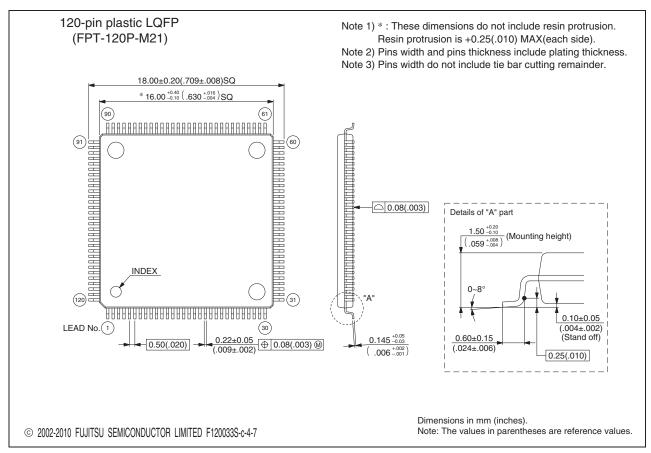

#### Package

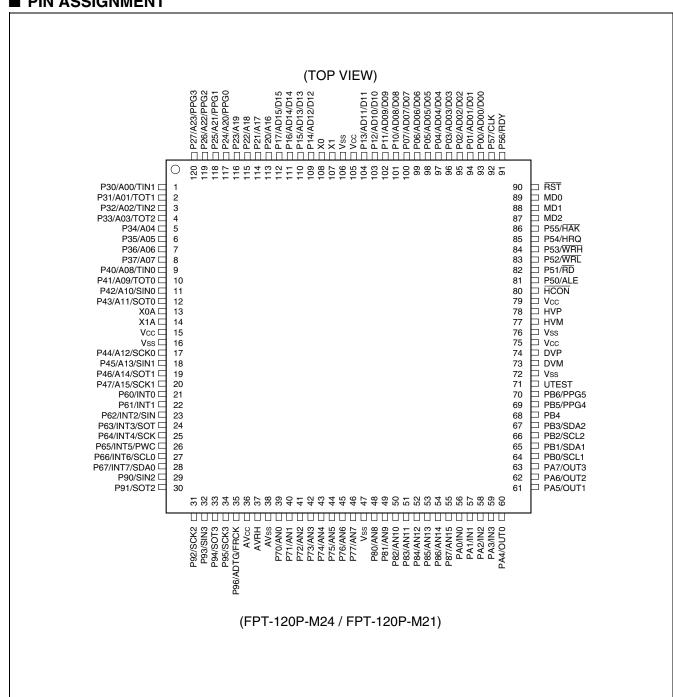

- LQFP-120P (FPT-120P-M24: 0.40 mm pin pitch)

- LQFP-120P (FPT-120P-M21: 0.50 mm pin pitch)

#### • Process : CMOS technology

• Operation guaranteed temperature :  $-40~^{\circ}\text{C}$  to  $+85~^{\circ}\text{C}$  (0  $^{\circ}\text{C}$  to  $+70~^{\circ}\text{C}$  when USB is in use)

#### ■ INTERNAL PERIPHERAL FUNCTION (RESOURCE)

• I/O port : Max 94 ports

Time-base timer: 1 channel

Watchdog timer: 1 channel

Watch timer: 1 channel

• 16-bit reload timer: 3 channels

#### Multi-functional timer

• 16-bit free run timer: 1 channel

• Output compare : 4 channels

An interrupt request can be output when the 16-bit free-run timer value matches the compare register value.

• Input capture : 4 channels

Upon detection of the effective edge of the signal input to the external input pin, the input capture unit sets the input capture data register to the 16-bit free-run timer value to output an interrupt request.

- 8/16-bit PPG timer (8-bit × 6 channels or 16-bit × 3 channels) the period and duty of the output pulse can be set by the program.

- 16-bit PWC timer : 1 channel

Timer function and pulse width measurement function

#### • UART: 4 channels

- Full-duplex double buffer (8-bit length)

- Asynchronous transfer or clock-synchronous serial (Extended I/O serial) transfer can be set.

#### • Extended I/O serial interface : 1 channel

#### • DTP/External interrupt circuit (8 channels)

- Activate the extended intelligent I/O service by external interrupt input

- Interrupt output by external interrupt input

#### • Delay interrupt output module

· Output an interrupt request for task switching

#### • 8/10-bit A/D converter: 16 channels

• 8-bit resolution or 10-bit resolution can be set.

#### • USB: 1 channel

- USB function (correspond to USB Full Speed)

- Full Speed is supported/Endpoint are specifiable up to six.

- Dual port RAM (The FIFO mode is supported).

- Transfer type: Control, Interrupt, Bulk, or Isochronous transfer possible

- USB HOST function

#### • I2C Interface: 3 channels

- Supports Intel SM bus standard and Phillips I<sup>2</sup>C bus standards

- Two-wire data transfer protocol specification

- Master and slave transmission/reception

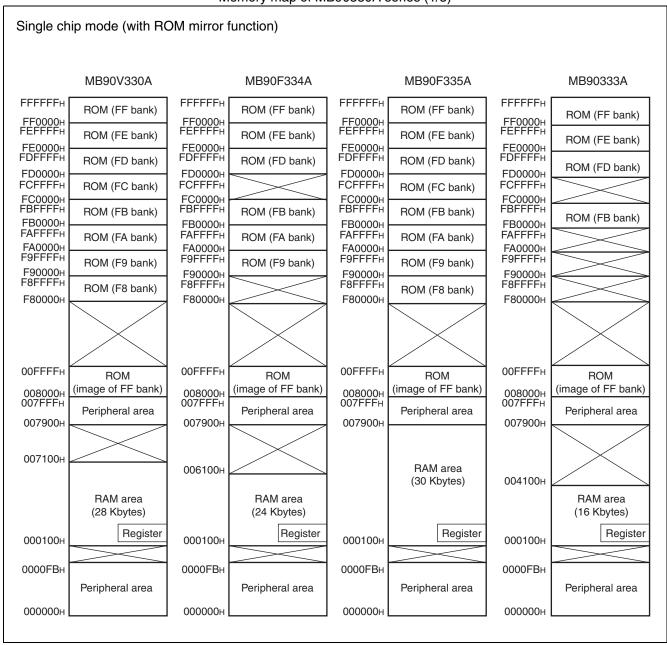

#### **■ PRODUCT LINEUP**

| Part number                      | MB90V330A                                                                                                                                                                                                                                                 | MB90F334A                | MB90F335A                | MB90333A             |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|----------------------|--|

| Туре                             | For evaluation                                                                                                                                                                                                                                            | Built-in Flash<br>memory | Built-in Flash<br>memory | Built-in MASK<br>ROM |  |

| ROM capacity                     | No                                                                                                                                                                                                                                                        | 384 Kbytes               | 512 Kbytes               | 256 Kbytes           |  |

| RAM capacity                     | 28 Kbytes                                                                                                                                                                                                                                                 | 24 Kbytes                | 30 Kbytes                | 16 Kbytes            |  |

| Emulator-specific power supply * | Yes                                                                                                                                                                                                                                                       |                          | _                        |                      |  |

| CPU functions                    | Number of basic instructions  Minimum instruction execution time: 41.7 ns/at oscillation of 6 MHz  (When 4 times are used: Machine of 24 MHz)  Addressing type: 23 types  Program Patch Function: For 2 address pointers  Maximum memory space: 16 Mbytes |                          |                          |                      |  |

| Ports                            | I/O Ports (CMOS) 94                                                                                                                                                                                                                                       | ports                    |                          |                      |  |

| UART                             | Equipped with full-duplex double buffer Clock synchronous or asynchronous operation selectable It can also be used for I/O serial Built-in special baud-rate generator Built-in 4 channels                                                                |                          |                          |                      |  |

| 16-bit reload timer              | 16-bit reload timer op<br>Built-in 3 channels                                                                                                                                                                                                             | eration                  |                          |                      |  |

| Multi-functional timer           | 16-bit free run timer × 1 channel Output compare × 4 channels Input capture × 4 channels 8/16-bit PPG timer (8-bit mode × 6 channels, 16-bit mode × 3 channels) 16-bit PWC timer × 1 channel                                                              |                          |                          |                      |  |

| 8/10-bit A/D converter           | 16 channels (input mu<br>8-bit resolution or 10-<br>Conversion time : 7.1                                                                                                                                                                                 | bit resolution can be    |                          | ck at maximum)       |  |

| DTP/External interrupt           | 8 channels<br>Interrupt factor : "L"→                                                                                                                                                                                                                     | "H" edge/"H"→"L" e       | dge/"L" level/"H" lev    | vel selectable       |  |

| I <sup>2</sup> C                 | 3 channels                                                                                                                                                                                                                                                |                          |                          |                      |  |

| Extended I/O serial interface    | 1 channel                                                                                                                                                                                                                                                 |                          |                          |                      |  |

| USB                              | 1 channel USB function (correspond to USB Full Speed) USB HOST function                                                                                                                                                                                   |                          |                          |                      |  |

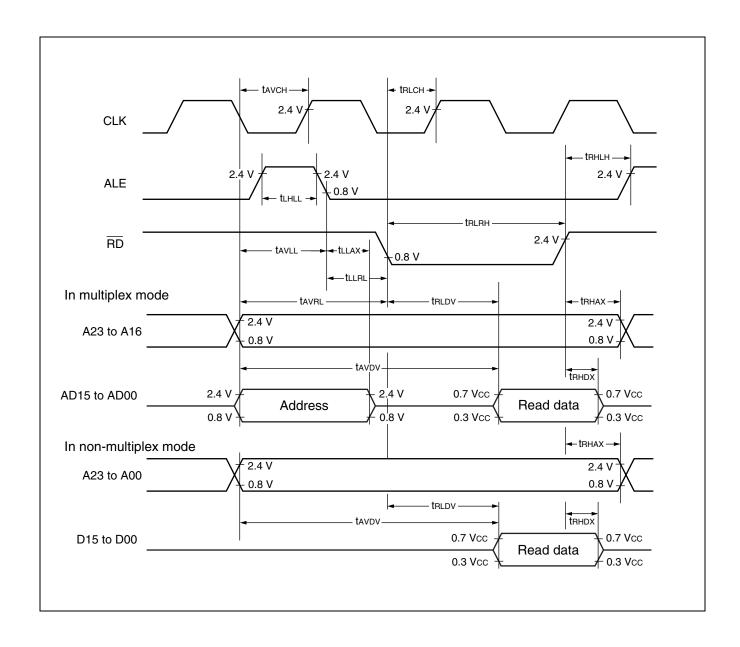

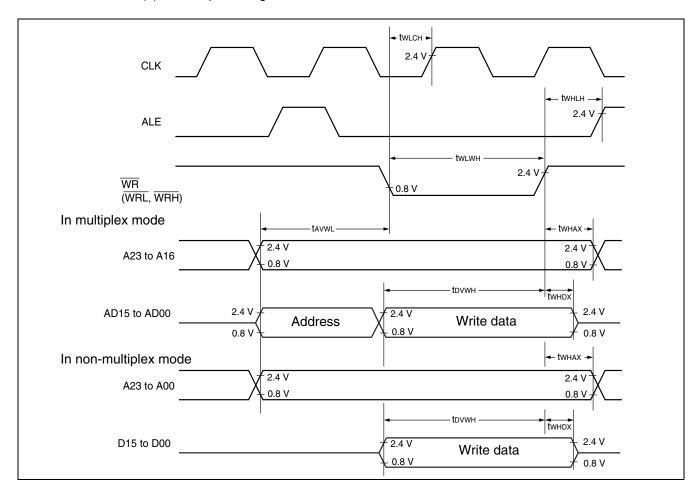

| External bus interface           | For multi-bus/non-mu                                                                                                                                                                                                                                      | lti-bus                  |                          |                      |  |

| Withstand voltage of 5 V         | 16 ports (excluding U                                                                                                                                                                                                                                     | TEST and I/O for I20     | C)                       |                      |  |

| Low Power Consumption Mode       | Sleep mode/Time-base timer mode/Stop mode/CPU intermittent mode/<br>Watch mode                                                                                                                                                                            |                          |                          |                      |  |

| Process                          | CMOS                                                                                                                                                                                                                                                      |                          |                          |                      |  |

| Operating voltage                | $3.3~V\pm0.3~V$ (at maximum machine clock 24 MHz)                                                                                                                                                                                                         |                          |                          |                      |  |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the MB2147-01 or MB2147-20 hardware manual (3.3 Emulator-dedicated Power Supply Switching) about details.

#### ■ PACKAGES AND PRODUCT MODELS

| Package                     | MB90333A | MB90F334A | MB90F335A | MB90V330A |

|-----------------------------|----------|-----------|-----------|-----------|

| FPT-120P-M24 (LQFP-0.40 mm) | 0        | 0         | 0         | ×         |

| FPT-120P-M21 (LQFP-0.50 mm) | 0        | 0         | 0         | ×         |

| PGA-299C-A01 (PGA)          | ×        | ×         | ×         | 0         |

$\bigcirc$  : Yes  $\times$  : No

Note: For detailed information on each package, refer to "■ PACKAGE DIMENSIONS".

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin no.    | Pin name     | I/O<br>Circuit<br>type* | Function                                                                                                                                                                                                       |  |  |

|------------|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

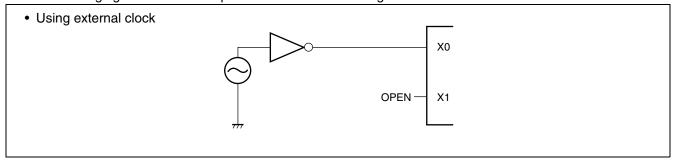

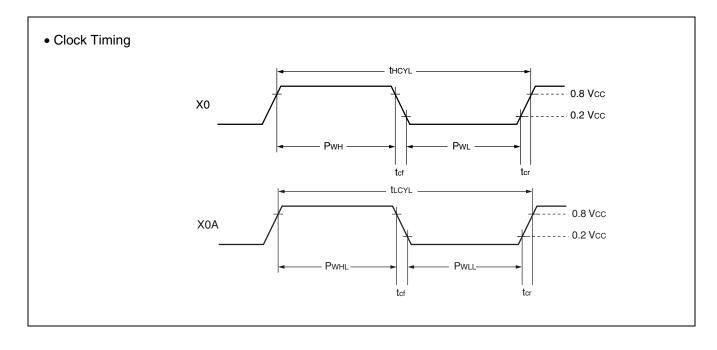

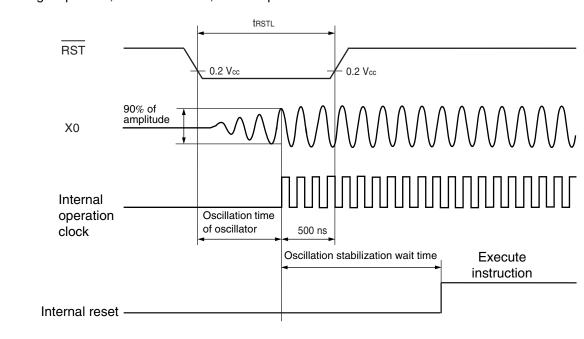

| 108, 107   | X0, X1       | А                       | Terminals to connect the oscillator.  When connecting an external clock, leave the X1 pin side unconnected.                                                                                                    |  |  |

| 13, 14     | X0A, X1A     | Α                       | 32 kHz oscillation terminals.                                                                                                                                                                                  |  |  |

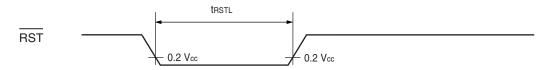

| 90         | RST          | F                       | External reset input pin.                                                                                                                                                                                      |  |  |

|            | P00 to P07   |                         | General purpose input/output port. The ports can be set to be added with a pull-up resistor (RD00 to RD07 = 1) by the pull-up resistor setting register (RDR0). (When the power output is set, it is invalid.) |  |  |

| 93 to 100  | AD00 to AD07 | Н                       | Function as an I/O pin for the low-order external address and data bus in multiplex mode.                                                                                                                      |  |  |

|            | D00 to D07   |                         | Function as an output pin for the low-order external data bus in non-multiplex mode.                                                                                                                           |  |  |

|            | P10 to P13   |                         | General purpose input/output port. The ports can be set to be added with a pull-up resistor (RD10 to RD13 = 1) by the pull-up resistor setting register (RDR1). (When the power output is set, it is invalid.) |  |  |

| 101 to 104 | AD08 to AD11 | Н                       | Function as an I/O pin for the high-order external address and data bus in multiplex mode.                                                                                                                     |  |  |

|            | D08 to D11   |                         | Function as an output pin for the high-order external data bus in non-multiplex mode.                                                                                                                          |  |  |

|            | P14 to P17   |                         | General purpose input/output port. The ports can be set to be added with a pull-up resistor (RD14 to RD17 = 1) by the pull-up resistor setting register (RDR1). (When the power output is set, it is invalid.) |  |  |

| 109 to 112 | AD12 to D15  | Н                       | Function as an I/O pin for the high-order external address and data bus in multiplex mode.                                                                                                                     |  |  |

|            | D12 to D15   |                         | Function as an output pin for the high-order external data bus in non-multiplex mode.                                                                                                                          |  |  |

|            | P20 to P23   |                         | This is a general purpose I/O port. When the bits of external address output control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports.                    |  |  |

| 113 to 116 | A16 to A19   |                         | When the bits of external address output control register (HACR) are set to "0" in multiplex mode, these pins function as address high output pins.                                                            |  |  |

|            | AIOIOAIS     |                         | When the bits of external address output control register (HACR) are set to "0" in non-multiplex mode, these pins function as address high output pins.                                                        |  |  |

| Pin no.    | Pin name     | I/O<br>Circuit<br>type* | Function                                                                                                                                                                                    |

|------------|--------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | P24 to P27   |                         | This is a general purpose I/O port. When the bits of external address output control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports. |

| 117 to 120 |              | D                       | When the bits of external address output control register (HACR) are set to "0" in multiplex mode, these pins function as address high output pins.                                         |

|            | A20 to A23   |                         | When the bits of external address output control register (HACR) are set to "0" in non-multiplex mode, these pins function as address high output pins.                                     |

|            | PPG0 to PPG3 |                         | Function as ch.0 to ch.3 output pins for the 8-bit PPG timer.                                                                                                                               |

|            | P30          |                         | General purpose input/output port.                                                                                                                                                          |

| 1          | A00          | D                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | TIN1         |                         | Function as an event input pin for 16-bit reload timer ch.1.                                                                                                                                |

|            | P31          |                         | General purpose input/output port.                                                                                                                                                          |

| 2          | A01          | D                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | TOT1         |                         | Function as the output pin for 16-bit reload timer ch.1.                                                                                                                                    |

|            | P32          |                         | General purpose input/output port.                                                                                                                                                          |

| 3          | A02          | D                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | TIN2         |                         | Function as an event input pin for 16-bit reload timer ch.2.                                                                                                                                |

|            | P33          |                         | General purpose input/output port.                                                                                                                                                          |

| 4          | A03          | D                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | TOT2         |                         | Function as the output pin for 16-bit reload timer ch.2.                                                                                                                                    |

| 5 to 8     | P34 to P37   | D                       | General purpose input/output port.                                                                                                                                                          |

| 5 10 6     | A04 to A07   | D                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | P40          |                         | General purpose input/output port.                                                                                                                                                          |

| 9          | A08          | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | TIN0         |                         | Function as an event input pin for 16-bit reload timer ch.0.                                                                                                                                |

|            | P41          |                         | General purpose input/output port.                                                                                                                                                          |

| 10         | A09          | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | TOT0         |                         | Function as the output pin for 16-bit reload timer ch.0.                                                                                                                                    |

|            | P42          |                         | General purpose input/output port.                                                                                                                                                          |

| 11         | A10          | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | SIN0         |                         | Function as a data input pin for UART ch.0.                                                                                                                                                 |

|            | P43          |                         | General purpose input/output port.                                                                                                                                                          |

| 12         | A11          | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | SOT0         |                         | Function as a data output pin for UART ch.0.                                                                                                                                                |

|            | P44          |                         | General purpose input/output port.                                                                                                                                                          |

| 17         | A12          | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                 |

|            | SCK0         |                         | Function as a clock I/O pin for UART ch.0.                                                                                                                                                  |

(Continued)

8

| Pin no. | Pin name   | I/O<br>Circuit<br>type* | Function                                                                                                                                                                                              |

|---------|------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | P45        |                         | General purpose input/output port.                                                                                                                                                                    |

| 18      | A13        | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                           |

|         | SIN1       | 1                       | Function as a data input pin for UART ch.1.                                                                                                                                                           |

|         | P46        |                         | General purpose input/output port.                                                                                                                                                                    |

| 19      | A14        | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                           |

|         | SOT1       |                         | Function as a data output pin for UART ch.1.                                                                                                                                                          |

|         | P47        |                         | General purpose input/output port.                                                                                                                                                                    |

| 20      | A15        | G                       | Function as the external address pin in non-multi-bus mode.                                                                                                                                           |

|         | SCK1       | 1                       | Function as a clock I/O pin for UART ch.1.                                                                                                                                                            |

| 0.1     | P50        | ,                       | General purpose input/output port.                                                                                                                                                                    |

| 81      | ALE        | L                       | Function as the address latch enable signal pin in external bus mode.                                                                                                                                 |

| 00      | P51        | ,                       | General purpose input/output port.                                                                                                                                                                    |

| 82      | RD         | L                       | Function as the read strobe output pin in external bus mode.                                                                                                                                          |

|         | P52        |                         | General purpose input/output port.                                                                                                                                                                    |

| 83      | WRL        | L                       | Function as the data write strobe output pin on the lower side in external bus mode. This pin functions as a general-purpose I/O port when the WRE bit in the EPCR register is "0".                   |

|         | P53        | L                       | General purpose input/output port.                                                                                                                                                                    |

| 84      | WRH        |                         | Function as the data write strobe output pin on the higher side in bus width 16-bit external bus mode. This pin functions as a general-purpose I/O port when the WRE bit in the EPCR register is "0". |

|         | P54        |                         | General purpose input/output port.                                                                                                                                                                    |

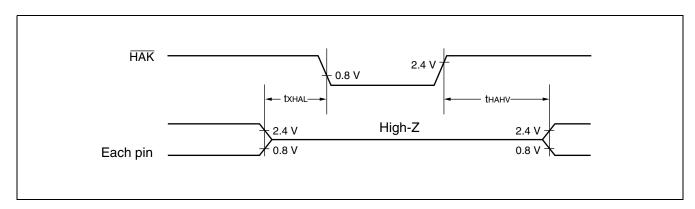

| 85      | HRQ        | L                       | Function as the hold request input pin in external bus mode. This pin functions as a general-purpose I/O port when the HDE bit in the EPCR register is "0".                                           |

|         | P55        |                         | General purpose input/output port.                                                                                                                                                                    |

| 86      | HAK        | L                       | Function as the hold acknowledge output pin in external bus mode. This pin functions as a general-purpose I/O port when the HDE bit in the EPCR register is "0".                                      |

|         | P56        |                         | General purpose input/output port.                                                                                                                                                                    |

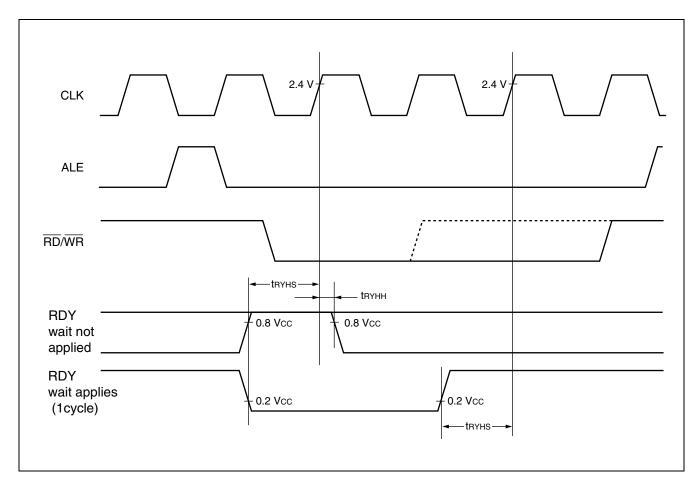

| 91      | RDY        | L                       | Function as the external ready input pin in external bus mode. This pin functions as a general-purpose I/O port when the RYE bit in the EPCR register is "0".                                         |

|         | P57        |                         | General purpose input/output port.                                                                                                                                                                    |

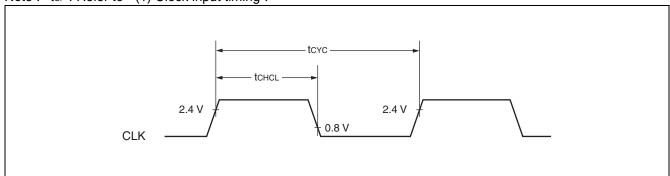

| 92      | CLK        | L                       | Function as the machine cycle clock output pin in external bus mode. This pin functions as a general-purpose I/O port when the CKE bit in the EPCR register is "0".                                   |

| 21, 22  | P60, P61   | С                       | General purpose input/output port. (With stand voltage of 5 V)                                                                                                                                        |

| 21,22   | INT0, INT1 | 0, INT1                 | Function as external interrupt ch.0 and ch.1 input pins.                                                                                                                                              |

| Pin no.  | Pin name    | I/O<br>Circuit<br>type* |                                                                                                                                                |  |

|----------|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | P62         |                         | General purpose input/output ports. (Withstand voltage of 5 V)                                                                                 |  |

| 23       | INT2        | С                       | Function as an external interrupt ch.2 input pin.                                                                                              |  |

|          | SIN         |                         | Extended I/O serial interface data input pin.                                                                                                  |  |

|          | P63         |                         | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |

| 24       | INT3        | С                       | Function as an external interrupt ch.3 input pin.                                                                                              |  |

|          | SOT         |                         | Extended I/O serial interface data output pin.                                                                                                 |  |

|          | P64         |                         | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |

| 25       | INT4        | С                       | Function as an external interrupt ch.4 input pin.                                                                                              |  |

|          | SCK         |                         | Extended I/O serial interface clock input/output pin.                                                                                          |  |

|          | P65         |                         | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |

| 26       | INT5        | С                       | Function as an external interrupt ch.5 input pin.                                                                                              |  |

|          | PWC         |                         | Function as the PWC input pin.                                                                                                                 |  |

|          | P66         |                         | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |

| 27       | INT6        | С                       | Function as an external interrupt ch.6 input pin.                                                                                              |  |

| 21       | SCL0        |                         | Function as the ch.0 clock I/O pin for the I <sup>2</sup> C interface. Set port output to High-Z during I <sup>2</sup> C interface operations. |  |

|          | P67         | С                       | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |

| 28       | INT7        |                         | Function as an external interrupt ch.7 input pin.                                                                                              |  |

| 20       | SDA0        |                         | Function as the ch.0 data I/O pin for the I <sup>2</sup> C interface. Set port output to High-Z during I <sup>2</sup> C interface operations.  |  |

| 39 to 46 | P70 to P77  | ı                       | General purpose input/output port.                                                                                                             |  |

| 39 10 40 | AN0 to AN7  |                         | Function as input pins for analog ch.0 to ch.7.                                                                                                |  |

| 48 to 55 | P80 to P87  | ı                       | General purpose input/output port.                                                                                                             |  |

| 46 10 55 | AN8 to AN15 | '                       | Function as input pins for analog ch.8 to ch.15.                                                                                               |  |

| 29       | P90         | D                       | General purpose input/output port.                                                                                                             |  |

| 29       | SIN2        | D                       | Function as a data input pin for UART ch.2.                                                                                                    |  |

| 30       | P91         | D                       | General purpose input/output port.                                                                                                             |  |

| 30       | SOT2        |                         | Function as a data output pin for UART ch.2.                                                                                                   |  |

| 31       | P92         | D                       | General purpose input/output port.                                                                                                             |  |

| 31       | SCK2        |                         | Function as a clock I/O pin for UART ch.2.                                                                                                     |  |

| 32       | P93         | D                       | General purpose input/output port.                                                                                                             |  |

| 52       | SIN3        |                         | Function as a data input pin for UART ch.3.                                                                                                    |  |

| 33       | P94         | D                       | General purpose input/output port.                                                                                                             |  |

| 33       | SOT3        |                         | Function as a data output pin for UART ch.3.                                                                                                   |  |

| 34       | P95         | D                       | General purpose input/output port.                                                                                                             |  |

| 04       | SCK3        |                         | Function as a clock I/O pin for UART ch.3.                                                                                                     |  |

|          | P96         |                         | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |

| 35       | ADTG        | С                       | Function as the external trigger input pin when the A/D converter is being used.                                                               |  |

|          | FRCK        |                         | Function as the external clock input pin when the free-run timer is being used.                                                                |  |

| (Continue                 | Continued)            |                                                                                      |                                                                                                                                                |  |  |  |  |

|---------------------------|-----------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin no.                   | Pin name              | I/O<br>Circuit<br>type*                                                              | Function                                                                                                                                       |  |  |  |  |

| FO to FO                  | PA0 to PA3            | •                                                                                    | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 56 to 59                  | o 59   IN0 to IN3   C |                                                                                      | Function as the input capture ch.0 to ch.3 trigger inputs.                                                                                     |  |  |  |  |

| CO += CO                  | PA4 to PA7 Gen        |                                                                                      | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 60 to 63                  | OUT0 to OUT3          | C                                                                                    | Function as the output compare ch.0 to ch.3 event output pins.                                                                                 |  |  |  |  |

|                           | PB0                   |                                                                                      | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 64                        | SCL1                  | С                                                                                    | Function as the ch.1 clock I/O pin for the I <sup>2</sup> C interface. Set port output to High-Z during I <sup>2</sup> C interface operations. |  |  |  |  |

|                           | PB1                   |                                                                                      | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 65                        | SDA1                  | С                                                                                    | Function as the ch.1 data I/O pin for the I <sup>2</sup> C interface. Set port output to High-Z during I <sup>2</sup> C interface operations.  |  |  |  |  |

|                           | PB2                   |                                                                                      | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 66                        | SCL2                  | C Function as the ch 2 clock I/O nin for the I <sup>2</sup> C interface. Set nort of |                                                                                                                                                |  |  |  |  |

|                           |                       |                                                                                      | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 67 SDA2                   |                       | С                                                                                    | Function as the ch.2 data I/O pin for the I <sup>2</sup> C interface. Set port output to High-Z during I <sup>2</sup> C interface operations.  |  |  |  |  |

| 68                        | PB4                   | С                                                                                    | General purpose input/output port. (Withstand voltage of 5 V)                                                                                  |  |  |  |  |

| 60.70                     | PB5, PB6              | D                                                                                    | General purpose input/output port.                                                                                                             |  |  |  |  |

| 69, 70                    | PPG4, PPG5            | D                                                                                    | Function as ch.4 and ch.5 output pins for the 8-bit PPG timer.                                                                                 |  |  |  |  |

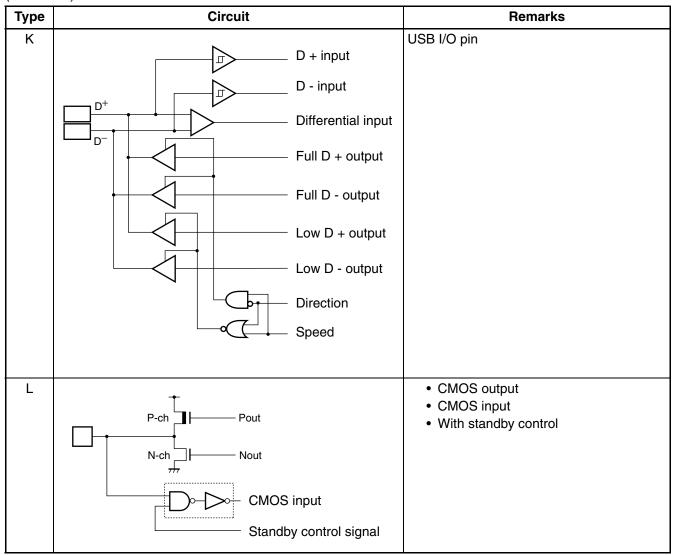

| 71                        | UTEST                 | С                                                                                    | USB test pin. Connect this to a pull-down resistor during normal usage.                                                                        |  |  |  |  |

| 73                        | DVM                   | K                                                                                    | USB function D- pin.                                                                                                                           |  |  |  |  |

| 74                        | DVP                   | K                                                                                    | USB function D+ pin.                                                                                                                           |  |  |  |  |

| 77                        | HVM                   | K                                                                                    | USB HOST D- pin.                                                                                                                               |  |  |  |  |

| 78                        | HVP                   | K                                                                                    | USB HOST D+ pin.                                                                                                                               |  |  |  |  |

| 80                        | HCON                  | E                                                                                    | External pull-up resistor connect pin.                                                                                                         |  |  |  |  |

| 36                        | AVcc                  |                                                                                      | A/D converter power supply pin.                                                                                                                |  |  |  |  |

| 37                        | AVRH                  | J                                                                                    | A/D converter external reference power supply pin.                                                                                             |  |  |  |  |

| 38                        | AVss                  | _                                                                                    | A/D converter power supply pin.                                                                                                                |  |  |  |  |

| 87 to 89                  | MD2 to MD0            | В                                                                                    | Operation mode select input pin.                                                                                                               |  |  |  |  |

| 15, 75,<br>79, 105        | Vcc                   | _                                                                                    | Power supply pin.                                                                                                                              |  |  |  |  |

| 16, 47,<br>72, 76,<br>106 | Vss                   | _                                                                                    | Power supply pin (GND).                                                                                                                        |  |  |  |  |

<sup>\* :</sup> For circuit information, refer to "■ I/O CIRCUIT TYPE".

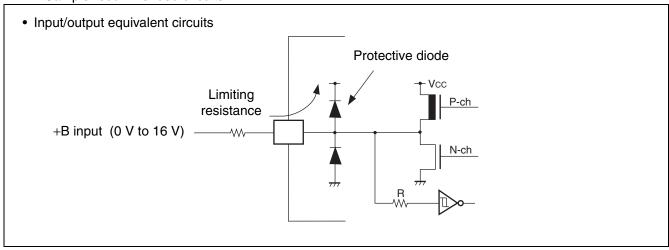

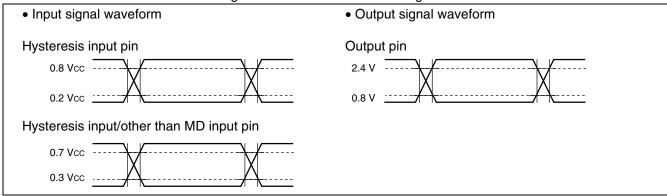

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                          | Remarks                                                                                                                                                                                                                                                               |

|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α    | Clock input  X1A  X0  X0A  Standby control signal                | • High-rate oscillation feedback resistor, approx.1 $M\Omega$ • Low-rate oscillation feedback resistor, approx.10 $M\Omega$ • With standby control                                                                                                                    |

| В    | CMOS hysteresis input                                            | CMOS hysteresis input                                                                                                                                                                                                                                                 |

| С    | N-ch Nout  CMOS hysteresis input  Standby control signal         | CMOS hysteresis input     N-ch open drain output                                                                                                                                                                                                                      |

| D    | P-ch Pout N-ch Nout CMOS hysteresis input Standby control signal | CMOS output CMOS hysteresis input (With input interception function at standby)  Notes: Share one output buffer because both output of I/O port and internal resource are used. Share one input buffer because both input of I/O port and internal resource are used. |

| E    | P-ch Pout  N-ch Nout                                             | CMOS output                                                                                                                                                                                                                                                           |

| F    | CMOS hysteresis input                                            | CMOS hysteresis input with pull-up resistor                                                                                                                                                                                                                           |

| Туре | Circuit                                                                               | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G    | P-ch Pout Open drain control signal  N-ch Nout  CMOS hysteresis input Standby control | CMOS output CMOS hysteresis input (With input interception function at standby) With open drain control signal                                                                                                                                                                                                                                                                                                                                                                |

| Н    | Standby control signal                                                                | CMOS output CMOS input (With input interception function at standby) With input pull-up register control                                                                                                                                                                                                                                                                                                                                                                      |

| I    | P-ch Pout Nout Nout The Nout Standby control signal A/D converter analog input        | CMOS output CMOS hysteresis input (With input interception function at standby) Analog input (The A/D converter analog input is enabled when the corresponding bit in the analog input enable register (ADER) is 1.)  Notes: Because the output of the I/O port and the output of internal resources are used combinedly, one output buffer is shared. Because the input of the I/O port and the input of internal resources are used combinedly, one input buffer is shared. |

| J    | AVRH input  A/D converter analog input enable signal                                  | A/D converter (AVRH) voltage input pin                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### **■ HANDLING DEVICES**

#### 1. Preventing latch-up and turning on power supply

Latch-up may occur on CMOS IC under the following conditions:

- If a voltage higher than Vcc or lower than Vss is applied to input and output pins.

- A voltage higher than the rated voltage is applied between Vcc pin and Vss pin.

- If the AVcc power supply is turned on before the Vcc voltage.

Ensure that you apply a voltage to the analog power supply at the same time as Vcc or after you turn on the digital power supply (when you perform power-off, turn off the analog power supply first or at the same time as Vcc and the digital power supply).

If latch-up occurs, the supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Use meticulous care not to let any voltage exceed the maximum rating.

#### 2. Treatment of unused pins

Leaving unused input pins unconnected can cause abnormal operation or latch-up, leading to permanent damage.

Unused input pins should always be pulled up or down through resistance of at least 2  $k\Omega$ . Any unused input/output pins may be set to output mode and left open, or set to input mode and treated the same as unused input pins. If there is unused output pin, make it to open.

#### 3. Treatment of power supply pins on models with A/D converters

Even when the A/D converters are not in use, be sure to make the necessary connections AVcc = AVRH = Vcc, and AVss = Vss.

#### 4. About the attention when the external clock is used

Even when using an external clock signal, an oscillation stabilization delay is applied after a power-on reset or when recovering from sub clock or stop mode. When suing an external clock, 25 MHz should be the upper frequency limit.

The following figure shows a sample use of external clock signals.

#### 5. Treatment of power supply pins (Vcc/Vss)

In products with multiple  $V_{\rm CC}$  or  $V_{\rm SS}$  pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect the pins to external power supply and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating. Moreover, connect the current supply source with the  $V_{\rm CC}$  and  $V_{\rm SS}$  pins of this device at the low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F between Vcc pin and Vss pin near this device.

#### 6. About Crystal oscillator circuit

Noise near the X0/X1 pins and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1 pins and X0A/X1A pins, the crystal oscillator (or the ceramic oscillator) and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended to design the PC board artwork with the X0/X1 pins and X0A/X1A pins surrounded by ground plane because stable operation can be expected with such a layout.

Please ask the crystal maker to evaluate the oscillational characteristics of the crystal and this device.

#### 7. Caution on Operations during PLL Clock Mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, Fujitsu will not guarantee results of operations if such failure occurs.

#### 8. Stabilization of supply voltage

A sudden change in the supply voltage may cause the device to malfunction even within the  $V_{\rm CC}$  supply voltage operating range. For stabilization reference, the supply voltage should be stabilized so that  $V_{\rm CC}$  ripple variations (peak-to-peak value) at commercial frequencies (50 Hz/60 Hz) fall below 10% of the standard  $V_{\rm CC}$  supply voltage and the transient regulation does not exceed 0.1 V/ms at temporary changes such as power supply switching.

#### 9. When the dual-supply is used as a single-supply device

If you are using only a single-system of the MB90330A series that come in the dual-system product, use it with  $X0A = V_{SS}$ : X1A = OPEN.

#### 10. Writing to flash memory

For serial writing to flash memory, always make sure that the operating voltage  $V_{CC}$  is between 3.13 V and 3.6 V. For normal writing to flash memory, always make sure that the operating voltage  $V_{CC}$  is between 3.0 V and 3.6 V.

#### 11. Serial communication

There is a possibility to receive wrong data due to noise or other causes on the serial communication. Therefore, design a printed circuit board so as to avoid noise.

Consider receiving of wrong data when designing the system. For example, apply a checksum to detect an error. If an error is detected, retransmit the data.

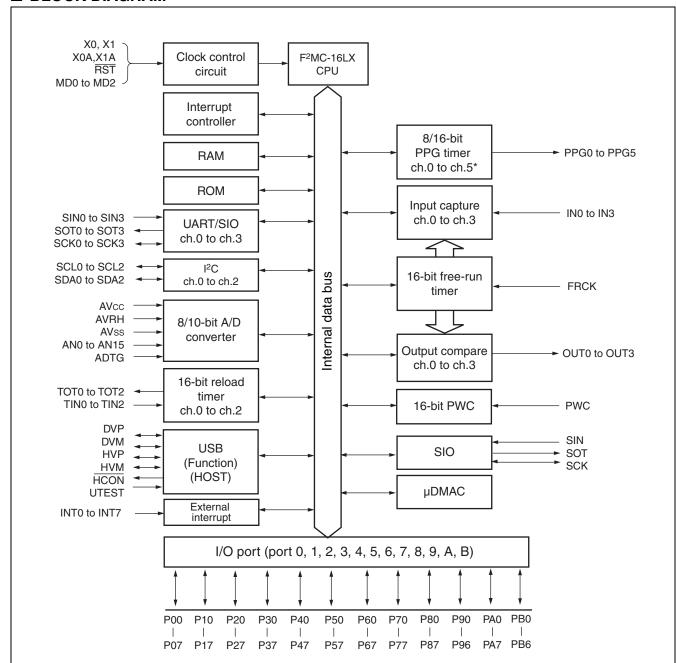

#### **■ BLOCK DIAGRAM**

\*: Channel for use in 8-bit mode. 3 channels (ch.1, ch.3, ch.5) are used in 16-bit mode.

Note: I/O ports share pins with peripheral function (resources).

For details, refer to "■ PIN ASSIGNMENT" and "■ PIN DESCRIPTION".

Note also that pins used for peripheral function (resources) cannot serve as I/O ports.

#### ■ MEMORY MAP

Memory map of MB90330A series (1/3)

#### Memory map of MB90330A series (2/3)

Internal ROM external bus mode (with ROM mirror function) MB90F335A MB90V330A MB90F334A MB90333A FFFFFFH FFFFFFH **FFFFFF**H **FFFFFF**H ROM (FF bank) ROM (FF bank) ROM (FF bank) ROM (FF bank) FF0000H FEFFFFH FF0000H FEFFFFH FF0000н FF0000H FEFFFFH FEFFFFH ROM (FE bank) ROM (FE bank) ROM (FE bank) ROM (FE bank) FE0000H FDFFFFH FE0000H FDFFFFH FE0000H FDFFFFH FE0000H FDFFFFH ROM (FD bank) ROM (FD bank) ROM (FD bank) ROM (FD bank) FD0000H FCFFFFH FD0000H FCFFFFH FD0000H FCFFFFH FD0000H FCFFFFH ROM (FC bank) ROM (FC bank) FC0000H FC0000н FC0000н FC0000н **FBFFFF**H **FBFFFF**H **FBFFFF**H ROM (FB bank) ROM (FB bank) ROM (FB bank) ROM (FB bank) FB0000н FB0000н FB0000н FВ0000н **FAFFFF**H **FAFFFF**H **FAFFFF**<sub>H</sub> **FAFFFF**H ROM (FA bank) ROM (FA bank) ROM (FA bank) FA0000H FA0000H FA0000H FA0000H F9FFFFH F9FFFFH F9FFFH F9FFFH ROM (F9 bank) ROM (F9 bank) ROM (F9 bank) External area F90000н F90000н F90000н F90000н F8FFFFH F8FFFFH ROM (F8 bank) External area ROM (F8 bank) F80000H F80000н F80000H F80000H External area External area External area External area 00FFFFн 00FFFFн 00FFFFн 00FFFFн **ROM ROM ROM** ROM (image of FF bank) (image of FF bank) (image of FF bank) (image of FF bank) 008000н 007FFFн 008000н 007FFFн 008000н 007FFFн 008000н 007FFFн Peripheral area Peripheral area Peripheral area Peripheral area 007900н 007900н 007900н 007900н External area External area 007100н External area RAM area 006100н 004100H (30 Kbytes) RAM area RAM area RAM area (28 Kbytes) (24 Kbytes) (16 Kbytes) Register Register Register Register 000100н 000100н 000100н 000100н 0000 ГВн 0000FВн 0000FВн 0000FВн Peripheral area Peripheral area Peripheral area Peripheral area 000000н 000000н 000000н 000000н

<sup>\*1:</sup> In the area of F80000н to F8FFFFн and FC0000н to FCFFFFн at MB90F334A, a value of "1" is read at read operating.

<sup>\*2:</sup> In the area of FA0000н to FAFFFFн and FC0000н to FCFFFFн at MB90333A, a value of "1" is read at read operating.

#### Memory map of MB90330A series (3/3) External ROM external bus mode MB90V330A MB90F335A MB90333A MB90F334A **FFFFFF**H **FFFFFF**H **FFFFFF**H **FFFFFF**H External area External area External area External area 008000н 008000н 008000н 008000н 007FFFн 07FFFн 007FFFH 007FFFн Peripheral area Peripheral area Peripheral area Peripheral area 007900н 007900н 007900н 007900н External area External area External area 007100н 006100н RAM area 004100H (30 Kbytes) RAM area RAM area RAM area (28 Kbytes) (24 Kbytes) (16 Kbytes) Register Register Register Register 000100H 000100н 000100н 000100н 0000FВн 0000FВн 0000FВн 0000 ГВн Peripheral area Peripheral area Peripheral area Peripheral area

Notes: • When the ROM mirror function register has been set, the mirror image data at higher addresses ("FF8000H to FFFFFH") of bank FF is visible from the higher addresses ("008000H to 00FFFFH") of bank 00.

• The ROM mirror function is effective for using the C compiler small model.

000000н

• The lower 16-bit addresses of bank FF are equivalent to those of bank 00. Since the ROM area in bank FF exceeds 48 Kbytes, however, the mirror image of all the data in the ROM area cannot be reproduced in bank 00.

000000н

000000н

- When the C compiler small model is used, the data table mirror image can be shown at "008000H to 00FFFFH" by storing the data table at "FF8000H to FFFFFFH". Therefore, data tables in the ROM area can be referred without declaring the far addressing with the pointer.

- MB90F335A has the larger size of RAM area than MB90V330A, so that the emulation memory area needs to be set in the tools for a larger size of emulation area than 007100H. For details of setting, please refer to "Notes on Debug Environment Setting for MB90330A Series" by clicking "Application note" at the following URL. http://edevice.fujitsu.com/micom/en-support/

- 3 cycles are required to access to the emulation memory area (007100<sub>H</sub> to 0078FF<sub>H</sub>), which is 1 cycle more than to the mounted RAM area.

000000H

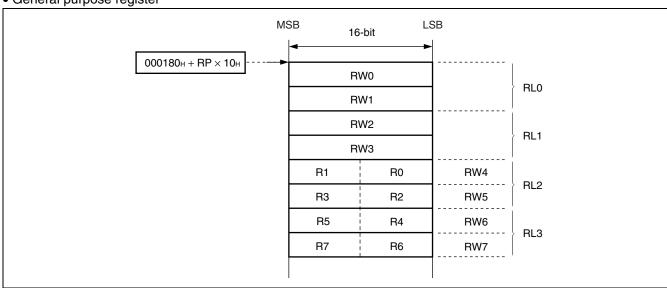

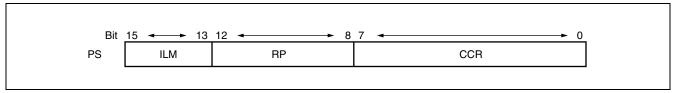

#### ■ F<sup>2</sup>MC-16LX CPU PROGRAMMING MODEL

#### • Dedicated register

#### • General purpose register

#### • Processor status

### ■ I/O MAP

| 000001н PI<br>000002н PI | DR0<br>DR1<br>DR2<br>DR3 | Port 0 Data Register Port 1 Data Register | R/W | Port 0                      | 20000000                     |

|--------------------------|--------------------------|-------------------------------------------|-----|-----------------------------|------------------------------|

| 000002н РІ               | DR2                      | Port 1 Data Register                      |     | 1 511 0                     | XXXXXXXXB                    |

|                          |                          |                                           | R/W | Port 1                      | XXXXXXXXB                    |

| 000003н Рі               | UB3                      | Port 2 Data Register                      | R/W | Port 2                      | XXXXXXXXB                    |

|                          | סווט                     | Port 3 Data Register                      | R/W | Port 3                      | XXXXXXXXB                    |

| 000004н РІ               | DR4                      | Port 4 Data Register                      | R/W | Port 4                      | XXXXXXXXB                    |

| 000005н РІ               | DR5                      | Port 5 Data Register                      | R/W | Port 5                      | XXXXXXXXB                    |

| 000006н РІ               | DR6                      | Port 6 Data Register                      | R/W | Port 6                      | XXXXXXXXB                    |

| 000007н РІ               | DR7                      | Port 7 Data Register                      | R/W | Port 7                      | XXXXXXXXB                    |

| 000008н РІ               | DR8                      | Port 8 Data Register                      | R/W | Port 8                      | XXXXXXXXB                    |

| 000009н РІ               | DR9                      | Port 9 Data Register                      | R/W | Port 9                      | - XXXXXXXB                   |

| 00000Ан РІ               | DRA                      | Port A Data Register                      | R/W | Port A                      | XXXXXXXXB                    |

| 00000Вн                  |                          | Prohibite                                 | ed  |                             |                              |

| 00000Сн РІ               | DRB                      | Port B Data Register                      | R/W | Port B                      | - XXXXXXXB                   |

| 00000Dн DI               | DRB                      | Port B Direction Register                 | R/W | Port B                      | - 0 0 0 0 0 0 0в             |

| 00000Ен                  |                          | Prohibite                                 | - d |                             |                              |

| 00000Fн                  |                          | PIOIIDIE                                  | au  |                             |                              |

| 000010н D                | DR0                      | Port 0 Direction Register                 | R/W | Port 0                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000011н D                | DR1                      | Port 1 Direction Register                 | R/W | Port 1                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000012н D                | DR2                      | Port 2 Direction Register                 | R/W | Port 2                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000013н D                | DR3                      | Port 3 Direction Register                 | R/W | Port 3                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000014н D                | DR4                      | Port 4 Direction Register                 | R/W | Port 4                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000015н D                | DR5                      | Port 5 Direction Register                 | R/W | Port 5                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000016н D                | DR6                      | Port 6 Direction Register                 | R/W | Port 6                      | 0 0 0 0 0 0 0 0в             |

| 000017н D                | DR7                      | Port 7 Direction Register                 | R/W | Port 7                      | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000018н D                | DR8                      | Port 8 Direction Register                 | R/W | Port 8                      | 0 0 0 0 0 0 0 0в             |

| 000019н 🛮 🔘              | DR9                      | Port 9 Direction Register                 | R/W | Port 9                      | - 0 0 0 0 0 0 0 <sub>B</sub> |

| 00001Aн DI               | DRA                      | Port A Direction Register                 | R/W | Port A                      | 0 0 0 0 0 0 0 0в             |

| 00001Вн О                | DR4                      | Port 4 Output Pin Register                | R/W | Port 4 (open drain control) | 0 0 0 0 0 0 0 0в             |

| 00001Cн R                | DR0                      | Port 0 Pull-up Resistance Register        | R/W | Port 0 (PULL-UP)            | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 00001Dн R                | DR1                      | Port 1 Pull-up Resistance Register        | R/W | Port 1 (PULL-UP)            | 0 0 0 0 0 0 0 0в             |

| 00001Ен А                | DER0                     | Analog Input Enable Register 0            | R/W | Port 7, 8, A/D              | 11111111                     |

| 00001Fн AD               | DER1                     | Analog Input Enable Register 1            | R/W | Port 7, 8, A/D              | 11111111                     |

| 000020н SI               | MR0                      | Serial Mode Register 0                    | R/W |                             | 0 0 1 0 0 0 0 0в             |

| 000021н Sc               | CR0                      | Serial Control Register 0                 | R/W |                             | 0 0 0 0 0 1 0 Ов             |

| 000022: SI               | DR0                      | Serial Input Data Register 0              | R   | UART0                       | VVVVVV                       |

| 000022H SC               | DR0                      | Serial Output Data Register 0             | W   |                             | XXXXXXX                      |

| 000023н S                | SR0                      | Serial Status Register 0                  | R/W |                             | 0 0 0 0 1 0 0 0в             |

| 000024н UT               | RLR0                     | UART Prescaler Reload Register 0          | R/W | Communication               | 0 0 0 0 0 0 0 0в             |

| 000025н UT               | CR0                      | UART Prescaler Control Register 0         | R/W | Prescaler (UART0)           | 0 0 0 0 - 0 0 0в             |

| Address       | Register abbreviation | Register                                          | Read/<br>Write | Resource name             | Initial Value                |

|---------------|-----------------------|---------------------------------------------------|----------------|---------------------------|------------------------------|

| 000026н       | SMR1                  | Serial Mode Register 1                            | R/W            |                           | 00100000в                    |

| 000027н       | SCR1                  | Serial Control Register 1                         | R/W            |                           | 00000100в                    |

| 000028н       | SIDR1                 | Serial Input Data Register 1                      | R              | UART1                     | XXXXXXXX                     |

| 000020H       | SODR1                 | Serial Output Data Register 1                     | W              | ]                         | XXXXXXXX                     |

| 000029н       | SSR1                  | Serial Status Register 1                          | R/W            |                           | 0 0 0 0 1 0 0 0 <sub>B</sub> |

| 00002Ан       | UTRLR1                | UART Prescaler Reload Register 1                  | R/W            | Communication             | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 00002Вн       | UTCR1                 | UART Prescaler Control Register 1                 | R/W            | Prescaler (UART1)         | 0 0 0 0 - 0 0 0 <sub>B</sub> |

| 00002Сн       | SMR2                  | Serial Mode Register 2                            | R/W            |                           | 0 0 1 0 0 0 0 0в             |

| 00002Dн       | SCR2                  | Serial Control Register 2                         | R/W            |                           | 0 0 0 0 0 1 0 Ов             |

| 00002Ен       | SIDR2                 | Serial Input Data Register 2                      | R              | UART2                     | XXXXXXXX                     |

| 00002EH       | SODR2                 | Serial Output Data Register 2                     | W              | 1                         | AAAAAAAB                     |

| 00002Fн       | SSR2                  | Serial Status Register 2                          | R/W            |                           | 00001000в                    |

| 000030н       | UTRLR2                | UART Prescaler Reload Register 2                  | R/W            | Communication             | 00000000                     |

| 000031н       | UTCR2                 | UART Prescaler Control Register 2                 | R/W            | Prescaler (UART2)         | 0000-000в                    |

| 000032н       | SMR3                  | Serial Mode Register 3                            | R/W            |                           | 00100000в                    |

| 000033н       | SCR3                  | Serial Control Register 3                         | R/W            | UART3                     | 00000100в                    |

| 000004        | SIDR3                 | Serial Input Data Register 3                      | R              |                           | 20000000                     |

| 000034н       | SODR3                 | Serial Output Data Register 3                     | W              | 1                         | XXXXXXX                      |

| 000035н       | SSR3                  | Serial Status Register 3                          | R/W            | 1                         | 00001000в                    |

| 000036н       | UTRLR3                | UART Prescaler Reload Register 3                  | R/W            | Communication             | 0000000                      |

| 000037н       | UTCR3                 | UART Prescaler Control Register 3                 | R/W            | Prescaler (UART3)         | 0000-000в                    |

| 000038н       |                       | -                                                 |                |                           |                              |