## **Absolute Maximum Ratings**

| PWR to PGND                       | 0.3V to +18V                   |

|-----------------------------------|--------------------------------|

| PVIN to PGND                      | 0.3V to +18V                   |

| LX to PGND                        | $-0.3V$ to $(V_{PVIN} + 0.3V)$ |

| LXSNS to SGND                     | 2V to +14V                     |

| INSNS to SGND                     | 0.3V to +14V                   |

| OUTP, OUTN, DCRP, DCRN to SGND.   | 0.3V to +5.5V                  |

| 3P3 to SGND                       | / to the minimum of +4V        |

|                                   | or (V <sub>GDRV</sub> + 0.3V)  |

| GDRV to SGND                      | / to the minimum of +6V        |

|                                   | or (V <sub>PWR</sub> + 0.3V)   |

| LBI to PGND                       |                                |

| LBO to PGND(V <sub>GDRV</sub> - 0 | 0.3V) to $(V_{GDRV} + 0.3V)$   |

| BST to LX                         | 0.3V to +6V                    |

| BST to PGND                       | 0.3V to +24V                   |

| BST to GDRV                       | 0.3V to +24V                   |

|                                   |                                |

| 1P8 to DGND                                           | 0.3V to +2.2V  |

|-------------------------------------------------------|----------------|

| CIO, SET, PG, ADDR0, ADDR1, SYNC, TEM                 | MPX,           |

| SALRT to DGND                                         | 0.3V to +4V    |

| EN, SCL, SDA to DGND                                  | 0.3V to +4V    |

| PGND to SGND                                          | 0.3V to +0.3V  |

| DGND to SGND                                          | 0.3V to +0.3V  |

| Electrostatic Discharge (ESD) Rating                  |                |

| Human Body Model (HBM)                                | ±2500V         |

| Junction Temperature                                  | +125°C         |

| Operating Temperature Range                           | 40°C to +85°C  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | 1              |

| TQFN (derate 37mW/°C above +70°C)                     | 2963mW         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

## **Package Thermal Characteristics (Note 1)**

**TQFN**

Junction-to-Ambient Thermal Resistance (θ,JA) ......27°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>)......1.7°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(All settings = factory default,  $V_{PWR} = V_{PVIN} = V_{INSNS} = 12V$ ,  $V_{SGND} = V_{DGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 600$ kHz. Specifications are for  $T_A = T_J = -40$ °C to +85°C, typical values are at  $T_A = T_J = +25$ °C. See the <u>Typical Operating Circuit</u>, unless otherwise noted.) (Note 2)

| PARAMETER                           | SYMBOL                 | CONDITIONS                                                                       | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------|------------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| INPUT SUPPLY                        |                        |                                                                                  | ·    |      |      |       |

| Input Voltage Range                 | V <sub>PWR</sub>       |                                                                                  | 4.5  |      | 14   | V     |

| Input Supply Current                |                        | BabyBuck bias supply, driver not switching                                       |      | 10   |      | - mA  |

|                                     | I <sub>PWR</sub>       | Linear mode bias supply, driver not switching                                    |      | 24   | 50   | IIIA  |

| Input Overvoltage-Lockout Threshold | V <sub>OVLO(PWR)</sub> | Input rising                                                                     | 14.3 | 15.2 | 16.0 | V     |

| Input Undervoltage-Lockout          | V                      | Rising edge                                                                      | 3.8  | 4.1  | 4.4  | 4.4 V |

| Threshold                           | V <sub>UVLO(PWR)</sub> | Hysteresis                                                                       |      | 0.24 |      | \ \ \ |

| BIAS REGULATORS                     |                        |                                                                                  |      |      |      |       |

| 3P3 Output Voltage                  | V <sub>3P3</sub>       | I <sub>LOAD(3P3)</sub> = 0mA                                                     |      | 3.3  |      | V     |

| 1P8 Output Voltage                  | V <sub>1P8</sub>       | I <sub>LOAD(1P8)</sub> = 0mA                                                     |      | 1.80 |      | V     |

| STARTUP/SHUTDOWN TIMIN              | G                      |                                                                                  |      |      |      |       |

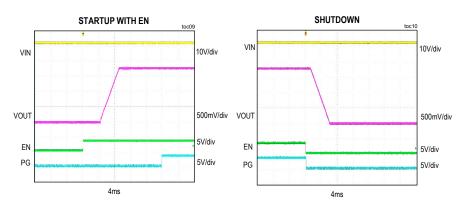

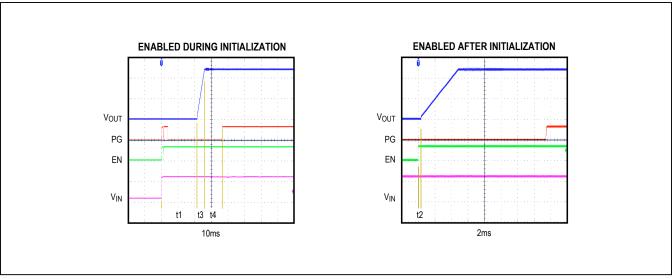

| Firmware Initialization             | t <sub>1</sub>         | From V <sub>IN</sub> > V <sub>UVLO(PWR)</sub> , until ready to enable (Figure 2) |      | 25   |      | ms    |

## **Electrical Characteristics (continued)**

(All settings = factory default,  $V_{PWR} = V_{PVIN} = V_{INSNS} = 12V$ ,  $V_{SGND} = V_{DGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 600kHz$ . Specifications are for  $T_A = T_J = -40$ °C to +85°C, typical values are at  $T_A = T_J = +25$ °C. See the <u>Typical Operating Circuit</u>, unless otherwise noted.) (Note 2)

| PARAMETER                                  | SYMBOL            | CONDITIONS                                                                                  | MIN   | TYP | MAX     | UNITS                 |

|--------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|-------|-----|---------|-----------------------|

| Minimum Programmable toN_DELAY             | t <sub>2</sub>    | (Figure 2, Note 10)                                                                         | 1     |     |         | ms                    |

| Minimum Programmable<br>Turn-On Rise Time  | t <sub>3</sub>    | (Figure 2, Note 10)                                                                         | 1     |     |         | ms                    |

| Adaptive Tuning Time                       | t <sub>4</sub>    | From V <sub>OUT</sub> = V <sub>OUT</sub> command to assertion of power good (PG) (Figure 2) |       | 12  |         | ms                    |

| OUTPUT VOLTAGE                             |                   |                                                                                             |       |     |         |                       |

| Programmable Output Voltage Range          | V <sub>OUT</sub>  | Measured from OUTP to OUTN (Notes 4 and 10)                                                 | 0.5   |     | 5.25    | V                     |

| LX Bias Current                            | I <sub>LX</sub>   | Not switching, current out of device pin                                                    |       | 200 |         | μA                    |

| Allowable Duty-Cycle Range                 |                   | (Note 10)                                                                                   | 5     |     | 95      | %                     |

| Regulation Set-Point                       |                   | $V_{OUT} > 0.8V, -40^{\circ}C \le T_{A} \le +85^{\circ}C$                                   | -1.26 |     | +1.26   | ٥,                    |

| Accuracy (Note 3)                          |                   | V <sub>OUT</sub> ≤ 0.8V, -40°C ≤ T <sub>A</sub> ≤ +85°C                                     | -1.95 |     | +1.95   | %                     |

| V 0 5: 0 1                                 | I <sub>OUTP</sub> | Current flowing into OUTP                                                                   |       | 50  |         | μA                    |

| V <sub>OUT</sub> Sense Bias Current        | I <sub>OUTN</sub> | Current flowing out of OUTN                                                                 |       | 35  |         | μA                    |

|                                            | I <sub>DCRP</sub> | Current flowing into DCR,                                                                   |       | 120 |         | nA                    |

| DCR Sense Bias Current                     | I <sub>DCRN</sub> | V <sub>DCRP</sub> - V <sub>DCRN</sub> = 150mV                                               |       | 4   |         | μA                    |

| PWM CLOCK (Note 3)                         |                   |                                                                                             |       |     | -       |                       |

| Switching-Frequency Range                  | f <sub>SW</sub>   | Note 10                                                                                     | 300   |     | 1000    | kHz                   |

| Switching-Frequency Set-<br>Point Accuracy |                   |                                                                                             | -5    |     | +5      | %                     |

| External Clock to SYNC<br>Frequency Range  | f <sub>SYNC</sub> |                                                                                             | 300   |     | 1000    | kHz                   |

| Minimum Allowable SYNC Duty Cycle          |                   |                                                                                             |       | 40  |         | %                     |

| Maximum Allowable SYNC Duty Cycle          |                   |                                                                                             |       | 60  |         | %                     |

| PROTECTION (Note 3)                        |                   |                                                                                             |       |     |         |                       |

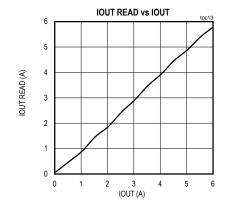

| Overcurrent Fault-Threshold Accuracy       |                   | T <sub>A</sub> = +25°C, exclusive of sensor error                                           |       | ±3  |         | %                     |

| Output Overvoltage-Fault<br>Threshold      |                   | Output rising                                                                               |       | 115 |         | %<br>V <sub>OUT</sub> |

| Output Undervoltage-Fault<br>Threshold     |                   | Output falling                                                                              |       | 85  |         | %<br>V <sub>OUT</sub> |

| Thermal-Shutdown Threshold Accuracy        |                   |                                                                                             |       | ±20 |         | °C                    |

| Thermal-Shutdown Hysteresis                |                   |                                                                                             |       | 20  |         | °C                    |

| Power-Good Threshold                       |                   | V <sub>OUT</sub> rising                                                                     |       | 90  |         | %                     |

| r ower-good Tillesiloid                    |                   | V <sub>OUT</sub> falling                                                                    |       | 85  | <u></u> | V <sub>OUT</sub>      |

## **Electrical Characteristics (continued)**

(All settings = factory default,  $V_{PWR} = V_{PVIN} = V_{INSNS} = 12V$ ,  $V_{SGND} = V_{DGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 600$ kHz. Specifications are for  $T_A = T_J = -40$ °C to +85°C, typical values are at  $T_A = T_J = +25$ °C. See the <u>Typical Operating Circuit</u>, unless otherwise noted.) (Note 2)

| PARAMETER                                        | SYMBOL          | CONDITIONS                                                                           | MIN TYP                   | MAX       | UNITS |

|--------------------------------------------------|-----------------|--------------------------------------------------------------------------------------|---------------------------|-----------|-------|

| STARTUP/SHUTDOWN TIMINO                          | }               |                                                                                      |                           |           |       |

| Firmware Initialization                          | t <sub>1</sub>  | From V <sub>IN</sub> > V <sub>UVLO(PWR)</sub> , until ready to enable (Figure 2)     | 25                        |           | ms    |

| Programmable TON_DELAY,                          |                 | Minimum delay (Figure 2)                                                             | 1                         |           |       |

| TOFF_DELAY Range                                 | t <sub>2</sub>  | Maximum delay (Figure 2)                                                             | 145                       |           | - ms  |

| TON_DELAY, TOFF DELAY Resolution                 |                 | Delay timing step size                                                               | 0.6                       |           | ms    |

| TON_DELAY, TOFF DELAY Command Accuracy (Note 10) |                 | Command value sent vs. read back                                                     |                           | ±0.3      | ms    |

| TON_DELAY, TOFF DELAY Timing Accuracy            |                 | Command read-back value vs. actual delay time                                        | ±0.8                      |           | ms    |

| Programmable TON RISE,                           |                 | Minimum (Figure 2)                                                                   | 1                         |           |       |

| TOFF_FALL Range                                  | t <sub>3</sub>  | Maximum (Figure 2)                                                                   | 255 x<br>t <sub>RR</sub>  |           | ms    |

| TON_RISE, TOFF_FALL Resolution                   | t <sub>RR</sub> | Ramp timing step size (varies with VOUT_<br>COMMAND)                                 | 0.4 -<br>1.0              |           | ms    |

| TON_RISE, TOFF_FALL Command Accuracy (Note 10)   |                 | Command value sent vs. read back                                                     |                           | ±0.5      | ms    |

| TON_RISE, TOFF_FALL Timing Accuracy              |                 | Command read back value vs. actual ramp duration                                     | ±10                       |           | μs    |

| Adaptive Tuning Time                             | t <sub>4</sub>  | From end of soft-start ramp to PG assertion (varies with FREQUENCY_SWITCH (Figure 2) | 12                        |           | ms    |

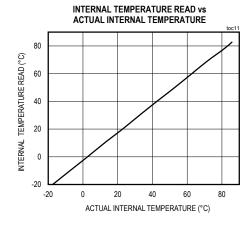

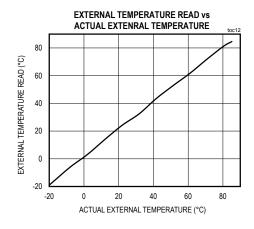

| Temperature-Measurement                          |                 | External                                                                             | ±5                        |           | °C    |

| Accuracy                                         |                 | Internal                                                                             | ±5                        |           |       |

| DIGITAL I/O Power-Good Logic-High                |                 | Open-drain output mode, open-drain                                                   |                           |           |       |

| Leakage Current                                  |                 | connected to 5.5V, $V_{3P3} = 3.3V$                                                  |                           | 10        | μA    |

| Output Logic-High                                |                 | CMOS mode, I <sub>SOURCE</sub> = 4mA                                                 | V <sub>3P3</sub> -<br>0.4 | $V_{3P3}$ | V     |

| Output Logic-Low                                 |                 | I <sub>SINK</sub> = 4mA                                                              |                           | 0.4       | V     |

| Input Bias Current                               |                 |                                                                                      | -1                        | +1        | μA    |

| Rise/Fall Slew Rate                              |                 | C <sub>LOAD</sub> = 15pF                                                             | 2                         |           | ns    |

| EN, SYNC Input-Logic Low<br>Voltage              |                 | Input voltage falling                                                                |                           | 0.8       | V     |

| EN, SYNC Input-Logic High Voltage                |                 | Input voltage rising                                                                 | 2                         |           | V     |

## **Electrical Characteristics (continued)**

(All settings = factory default,  $V_{PWR} = V_{PVIN} = V_{INSNS} = 12V$ ,  $V_{SGND} = V_{DGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 600kHz$ . Specifications are for  $T_A = T_J = -40$ °C to +85°C, typical values are at  $T_A = T_J = +25$ °C. See the <u>Typical Operating Circuit</u>, unless otherwise noted.) (Note 2)

| PARAMETER                                            | SYMBOL              | CONDITIONS                                                                             | MIN | TYP  | MAX  | UNITS |

|------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------|-----|------|------|-------|

| EN, SYNC Input Leakage                               |                     |                                                                                        | -10 |      | +10  | μA    |

| Current                                              |                     |                                                                                        |     |      | . 10 | μ/.   |

| SMBus (Note 3)                                       |                     |                                                                                        |     |      |      |       |

| SDA, SCL Input Logic-Low<br>Voltage                  |                     | Input voltage falling                                                                  |     |      | 0.8  | V     |

| SDA, SCL Input Logic-High<br>Voltage                 |                     | Input voltage rising                                                                   | 2   |      |      | V     |

| SDA, SCL, SALRT Logic-High<br>Leakage Current        |                     | V <sub>SCL</sub> , V <sub>SDA</sub> = 0V, and V <sub>SALRT</sub> tested at 0V and 3.3V |     |      | 10   | μA    |

| SDA, SCL, SALRT Logic-Low<br>Output Voltage          |                     | I <sub>SINK</sub> = 4mA                                                                |     |      | 0.4  | V     |

| PMBus Operating Frequency                            | f <sub>SMB</sub>    |                                                                                        |     | 400  |      | kHz   |

| Bus Free Time<br>(STOP - START)                      | t <sub>BUF</sub>    |                                                                                        | 1.3 |      |      | μs    |

| START Condition Hold Time from SCL                   | t <sub>HD:STA</sub> |                                                                                        | 0.6 |      |      | μs    |

| START Condition Setup Time from SCL                  | t <sub>SU:STA</sub> |                                                                                        | 0.6 |      |      | μs    |

| STOP Condition Setup Time from SCL                   | t <sub>SU:STO</sub> |                                                                                        | 0.6 |      |      | μs    |

| SDA Hold Time from SCL                               | t <sub>HD:DAT</sub> |                                                                                        | 300 |      | ,    | ns    |

| SDA Setup Time from SCL                              | t <sub>SU:DAT</sub> |                                                                                        | 100 |      |      | ns    |

| SCL Low Period                                       | tLOW                |                                                                                        | 1.3 |      |      | μs    |

| SCL High Period                                      | tHIGH               |                                                                                        | 0.6 |      |      | μs    |

| THERMAL PROTECTION                                   |                     |                                                                                        | '   |      |      |       |

| Gate-Driver Thermal-<br>Shutdown Threshold           | T <sub>SHDN</sub>   | Hysteresis = +20°C                                                                     |     | 150  |      | °C    |

| INTEGRATED SWITCHING MO                              | <b>DSFETs</b>       |                                                                                        |     |      |      |       |

| High-Side nMOS On-<br>Resistance                     | RON <sub>H</sub>    |                                                                                        |     | 40   | 60   | mΩ    |

| Low-Side nMOS On-<br>Resistance                      | RONL                |                                                                                        |     | 20   | 30   | mΩ    |

| Maximum Allowable High-<br>Side nMOS Average Current |                     | V <sub>OUT</sub> = 1.8V                                                                |     |      | 4.3  | А     |

| Maximum Allowable Low-Side nMOS Average Current      |                     | V <sub>OUT</sub> = 1.8V                                                                |     |      | 6.0  | А     |

|                                                      |                     | GDRV falling                                                                           | 3.6 | 3.85 | 4.1  | .,    |

| V <sub>GDRV</sub> Undervoltage Lockout               |                     | GDRV rising                                                                            | 3.7 | 3.94 | 4.2  | V     |

| V <sub>GDRV</sub> Output                             | V <sub>GDRV</sub>   | I <sub>LOAD</sub> = 1mA to 100mA,<br>V <sub>IN</sub> = 6V to 14V                       | 4.5 | 5.0  | 5.5  | V     |

### **Electrical Characteristics (continued)**

(All settings = factory default,  $V_{PWR} = V_{PVIN} = V_{INSNS} = 12V$ ,  $V_{SGND} = V_{DGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 600$ kHz. Specifications are for  $T_A = T_J = -40$ °C to +85°C, typical values are at  $T_A = T_J = +25$ °C. See the <u>Typical Operating Circuit</u>, unless

| PARAMETER                | SYMBOL             | CONDITIONS                                                | MIN  | TYP  | MAX             | UNITS   |

|--------------------------|--------------------|-----------------------------------------------------------|------|------|-----------------|---------|

| BabyBuck REGULATOR       |                    |                                                           |      |      |                 |         |

| BabyBuck Oscillator      |                    |                                                           | 1    | 2    | 3.4             | MHz     |

| Frequency                |                    |                                                           | '    |      | J. <del>T</del> | IVII IZ |

| nMOS On-Resistance       |                    |                                                           |      | 4.5  | 9.5             | Ω       |

| nMOS On-Resistance       |                    |                                                           |      | 2.0  | 4.0             | Ω       |

| Current-Sense Resistance | R <sub>CSP</sub>   | LBI to GDRV resistor                                      | 0.65 | 1.1  | 1.6             | Ω       |

| Current Limit            | I <sub>LIM</sub>   |                                                           |      | 491  | 900             | mA      |

| Dropout Voltage          | V <sub>DO</sub>    | I <sub>LOAD</sub> = 100mA, V <sub>IN</sub> = 4.9V         |      | 256  |                 | mV      |

| Foldback Current Limit   | I <sub>LIMFB</sub> | V <sub>GDRV</sub> = 0V                                    |      | 20   |                 | mA      |

| Full Current Limit       | I <sub>LIMF</sub>  | V <sub>GDRV</sub> = 4V                                    |      | 182  |                 | mA      |

| BOOTSTRAP CIRCUIT        |                    |                                                           |      |      |                 |         |

| BST Charging Switch      |                    | V <sub>GDRV</sub> = 5V, LX = 0V (pulldown state),         |      | 1.61 |                 | Ω       |

| R <sub>DS(ON)</sub>      |                    | I <sub>BST</sub> = 100mA                                  |      | 1.01 |                 | 32      |

| BST to LX Supply Current |                    | $V_{GDRV}$ = 0V, LX = 0V (pulldown state), $V_{BST}$ = 5V |      | 250  |                 | μA      |

- Note 2: Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Maximum and minimum limits over temperature are guaranteed through correlation using statistical quality control (SQC) methods. Typical values are expressed as factory-default values also for configurable specifications within a range.

- Note 3: Design guaranteed by bench characterization. Limits are not production tested.

- Note 4: The settable output voltage range is 0.6V to 5.0V. This range expands to 0.5V to 5.25V when the voltage-margining function is enabled.

- Note 5: Can go to 0% or 100% during a transient.

- Note 6: Once the device locks onto an external synchronizing clock, the tolerance on the capture range is ±10%.

- Note 7: See the Voltage Tracking section.

- Note 8: Excluding tracking mode.

- Note 9: Voltage-regulation accuracy is power-stage dependent; adherence to all data sheet design recommendations is required to achieve specified accuracy.

- Note 10: Customer-programmable parameters.

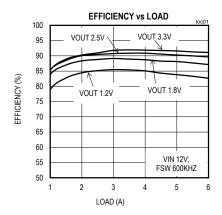

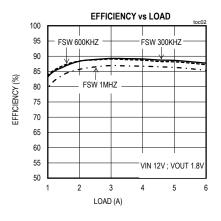

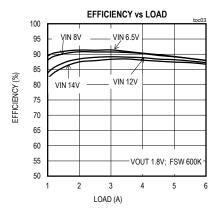

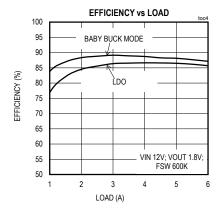

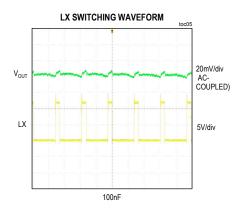

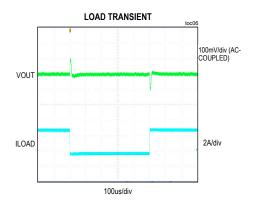

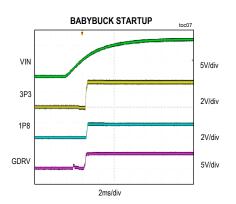

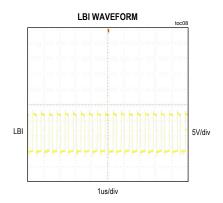

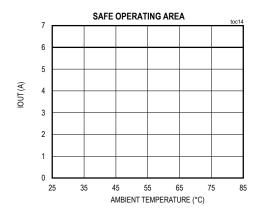

## **Typical Operating Characteristics**

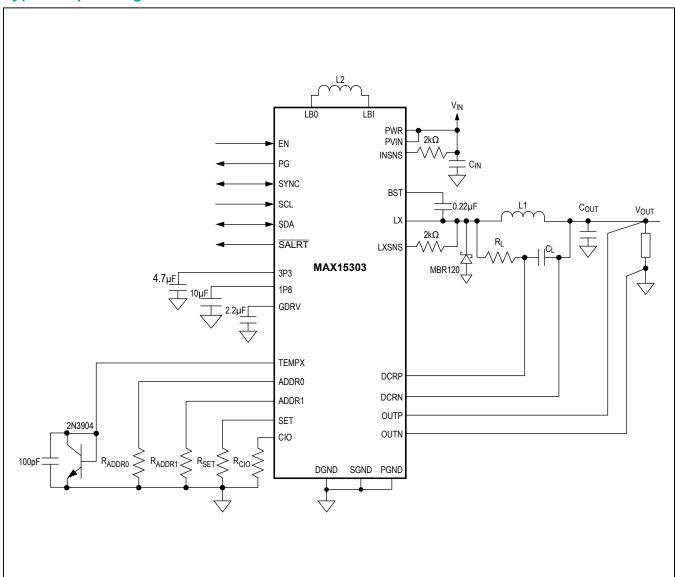

$(T_A = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.2V, f_{SW} = 600kHz, unless otherwise noted. See the$ *Typical Operating Circuit*and Application 1 in Table 8).

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.2V, f_{SW} = 600kHz, unless otherwise noted. See the$ *Typical Operating Circuit*and Application 1 in Table 8).

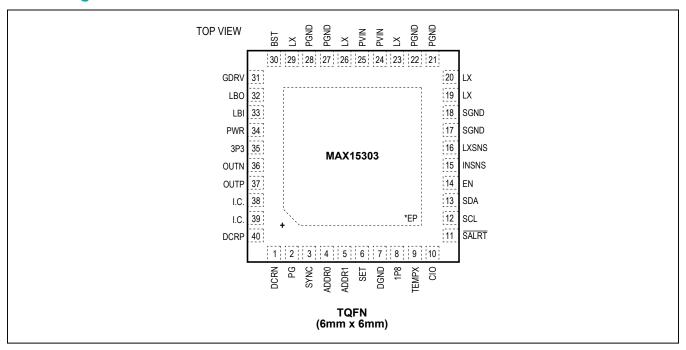

## **Pin Configuration**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

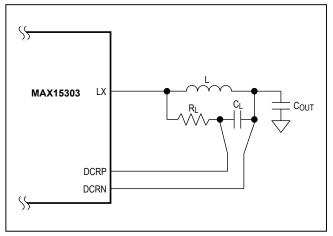

| 1   | DCRN  | Output Current Differential-Sense Negative Input. Connect to the inductor or current-sense element negative side.                                                                                                                          |

| 2   | PG    | Open-Drain Power-Good Indicator. PG asserts high when soft-start is complete, the voltage has reached regulation, and after a successful InTune calibration is completed.                                                                  |

| 3   | SYNC  | External Switching-Frequency Synchronization Input. Connect a resistor between SYNC and SGND to set the switching frequency of the DC-DC converter (see Table 3). The device can also synchronize with an external clock applied at SYNC.  |

| 4   | ADDR0 | SMBus Address-Select Input 0. Used with ADDR1 to assign a unique SMBus address to the device.                                                                                                                                              |

| 5   | ADDR1 | SMBus Address-Select Input 1. Used with ADDR0 to assign a unique SMBus address to the device and set the current limit for the device.                                                                                                     |

| 6   | SET   | Output-Voltage Set Input. Connect a resistor between SET and SGND to set the output voltage. Shorting this pin to ground selects tracking mode (see Table 1).                                                                              |

| 7   | DGND  | Digital Ground. Connect to the exposed pad (EP).                                                                                                                                                                                           |

| 8   | 1P8   | Internal 1.8V Regulator Output. 1P8 is the supply rail for the internal digital circuitry. Bypass 1P8 pin to DGND with a 10µF ceramic capacitor. This pin cannot be used to power any circuitry external to the device.                    |

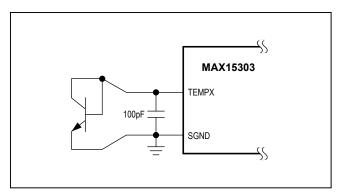

| 9   | TEMPX | Connection for the External Temperature Sensor. Connect an npn transistor junction from TEMPX to SGND to measure the temperature at any point on the PCB. Place a 100pF ceramic capacitor in parallel with the temperature-sense junction. |

| 10  | CIO   | Configurable Input/Output Pin. This is a voltage-tracking input when SET is connected to SGND to select tracking mode. CIO must be grounded when not in tracking mode.                                                                     |

# **Pin Description (continued)**

| PIN                   | NAME         | FUNCTION                                                                                                                                                                                                                                            |

|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                    | SALRT        | SMBus Alert. Interrupt to the SMBus master. Open-drain output that pulls low when SMBus interaction is required.                                                                                                                                    |

| 12                    | SCL          | SMBus Clock Input                                                                                                                                                                                                                                   |

| 13                    | SDA          | SMBus Data Input/Output                                                                                                                                                                                                                             |

| 14                    | EN           | Enable Input. Do not leave unconnected. By default, driving EN high enables output regulation, and driving EN low disables output regulation.                                                                                                       |

| 15                    | INSNS        | Power-Train Input Rail Sense. Monitors the input supply of the DC-DC converter. Connect a series $2k\Omega$ resistor between input rail and INSNS pin.                                                                                              |

| 16                    | LXSNS        | Switching-Node Sense Input. Connect a series $2k\Omega$ resistor between the switching node and the LXSNS pin.                                                                                                                                      |

| 17, 18                | SGND         | Analog Ground. Connect to the exposed pad (EP).                                                                                                                                                                                                     |

| 19, 20, 23,<br>26, 29 | LX           | Switching Node. Connect directly to the high side of the output inductor. Connect a Schottky diode between LX and PGND.                                                                                                                             |

| 21, 22, 27,<br>28     | PGND         | Power Ground. Connect to SGND and DGND using short wide PCB traces.                                                                                                                                                                                 |

| 24, 25                | PVIN         | Power-Supply Input for the Power Stage. Connect to a 4.5V to 14V supply. Must be connected to the same voltage as PWR.                                                                                                                              |

| 30                    | BST          | Bootstrap Capacitor Connection. Connect a 0.22µF ceramic capacitor between BST and the switching node.                                                                                                                                              |

| 31                    | GDRV         | Gate-Driver Supply. Bypass GDRV to PGND with a 2.2µF ceramic capacitor.                                                                                                                                                                             |

| 32                    | LBO          | BabyBuck Switching-Node 2. See the BabyBuck Gate-Driver Regulator section for configurations.                                                                                                                                                       |

| 33                    | LBI          | BabyBuck Switching-Node 1. See the BabyBuck Gate-Driver Regulator section for configurations.                                                                                                                                                       |

| 34                    | PWR          | Power Supply Input for the Bias Circuitry. Connect to a 4.5V to 14V supply. Must be connected to the same voltage as PVIN.                                                                                                                          |

| 35                    | 3P3          | Internal 3.3V Regulator Output. 3P3 is the supply rail for the internal analog circuitry. Bypass 3P3 to SGND with a 4.7µF ceramic capacitor. This pin cannot be used to power any circuitry external to the device.                                 |

| 36                    | OUTN         | Output-Voltage Differential-Sense Negative Input. Connect to ground at the load.                                                                                                                                                                    |

| 37                    | OUTP         | Output-Voltage Differential-Sense Positive Input. Connect to the output voltage at the load.                                                                                                                                                        |

| 38, 39                | I.C.         | Internally Connected. Connect these pins to the exposed pad (EP).                                                                                                                                                                                   |

| 40                    | DCRP         | Output-Current Differential-Sense Positive Input. Connect to the inductor or current-sense element positive side.                                                                                                                                   |

| _                     | EP<br>(SGND) | Exposed Pad and Analog Ground. The EP serves two purposes: it is both the analog ground of the device and a conduit for heat transfer. Connect to large ground plane to maximize thermal performance. See the <i>PCB Layout Guidelines</i> section. |

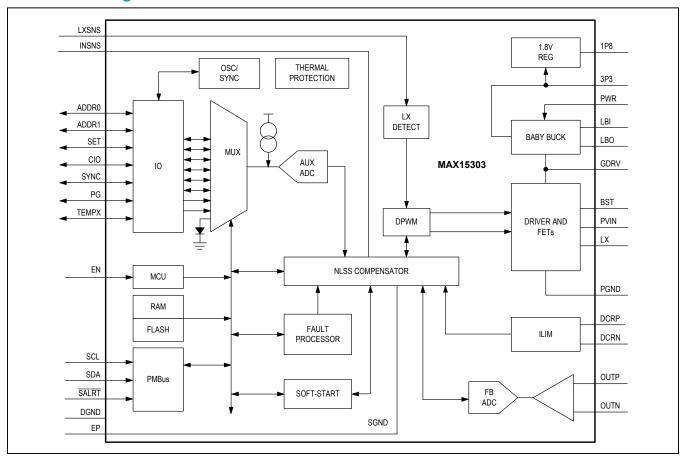

## **Functional Diagram**

### **Detailed Description**

The MAX15303 is an innovative, PMBus-compliant, mixed-signal power-management IC with a built-in high-performance digital PWM controller for POL applications. The device is based on Maxim's InTune automatically compensated digital PWM control loop. The device has optimal partitioning of the digital power management and the digital power-conversion domains to minimize startup times and reduce bias current. The device supports over 80 standard and manufacturer-specific PMBus commands.

The device uses adaptive compensation techniques to handle a broad range of timing, voltage, current, temperature, and external component parameter variations. Efficiency-optimization techniques further enhance the performance of the device, including internal MOSFETs, with internally optimized gate drive, and the switch-mode BabyBuck bias regulators for biasing the internal circuit blocks and the MOSFET gate drive.

The device's BabyBuck is an integrated power converter used to self-bias the digital, analog, and driver blocks from a single input supply (V<sub>PWR</sub>). The device relies on mixed-signal design techniques to control the power system efficiently and precisely. It does not require any software to configure or initialize the device. In addition, many operating features can be monitored and configured through the SMBus interface using standard PMBus commands, resulting in ease of design and flexibility.

The control loop is separated from the housekeeping, power-monitoring, and fault-management blocks. Control-loop parameters are stored in an on-chip nonvolatile flash memory. An internal microcontroller enables monitoring operating conditions using the SMBus interface. The digital pulse-width modulator (DPWM) control loop is implemented using dedicated state machines, so there is no DSP or MCU in the control loop. This partition allows the chip architecture to minimize power consumption while optimizing performance.

The <u>Functional Diagram</u> shows the controller implementation using a digital state-space compensator (model predictive) controller, a microcontroller unit (MCU), a DPWM, a PLL-based master timing generator, and a PMBus serial communication port.

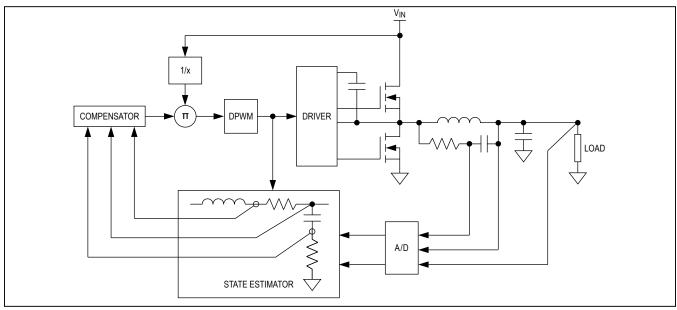

#### State-Space Controller and DPWM

The device uses a digital DPWM control scheme to regulate the output voltage. Traditional PWM regulators (both analog and digital) use classical control methods for DC-DC converters, based on linear models of a discrete time nature and root locus, Bode and Nyquist plots. These linear time-invariant approximations work well for small signals. However, when large transients cause duty-cycle saturation, the performance of the closed loop can be degraded (larger overshoots) and the output transients are "slower" (large settling times). Tighter regulation performance during these disturbances is becoming a requirement. The device addresses the issue by using model-predictive-based feedback design to compensate the DPWM.

The device automatically constructs a state-space model (state estimator) of the control plant (Figure 1). The internal model gives access to state-control variables that are otherwise unavailable. The state-control variables are used to set the proper control values. For a given input-to-output step-down ratio and PWM switching frequency, the device sets the compensation coefficients for that application. Upon output enable, or in response to a

PMBus command, the device performs the InTune calibration. During this calibration several power-train parameter values are measured and the extracted parameters are used to create the internal model to optimize the bandwidth and transient response of the converter.

The state-space compensator block generates the duty-cycle command for the DPWM block. The DPWM block generates the required PWM outputs for the driver.

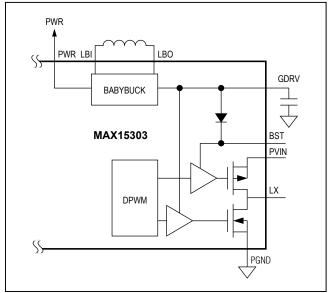

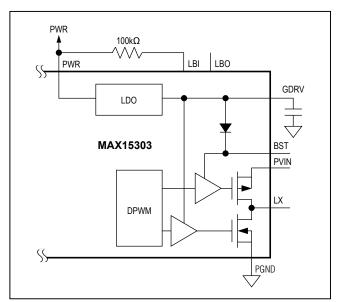

#### **BabyBuck Gate-Driver Regulator**

The device contains an internal bias supply that generates both the gate-drive voltage supply and the internal digital supply to power the controller. This BabyBuck gives the user two options to allow optimal configuration the device for their specific system requirements, BabyBuck mode and LDO mode.

In BabyBuck mode, the internal regulator is configured as a two-output switching regulator that uses a small (1008 size), low-cost inductor. The switching supply efficiently converts the higher input voltage to the lower bias supply and gate-drive voltages. BabyBuck mode is typically used with higher input voltages (> 7V) to improve overall system efficiency. BabyBuck mode cannot be used with input voltages lower than 6.5V. To configure the device in BabyBuck mode, connect PWR to the input voltage (PVIN) and connect the recommended inductor between LBI and LBO.

Figure 1. State-Space Controller Concept

In LDO mode, the device reconfigures BabyBuck to linearly regulate the input voltage down to the gate drive and bias voltages. LDO mode is typically used with lower input voltages (5V to 9V) or when the user wants to eliminate the BabyBuck inductor; however, it can also be used at higher input voltages as well. To configure the device in LDO mode, connect PWR to the input voltage (PVIN) and connect a  $100 \mathrm{k}\Omega$  resistor between PWR and LBI. Leave LBO unconnected.

#### **Temperature Sense**

The device provides both an internal and external temperature measurement. Both the internal and external temperatures are reported to the user through the PMBus commands READ TEMPERATURE 1 and READ\_TEMPERATURE\_2, respectively. The internal temperature is measured directly at the device silicon junction. The external temperature is measured through the TEMPX pin using the base-emitter junction of a standard 2N3904 transistor. This technique is widely employed because it requires no calibration of the sensor. Any PN junction can be used as a temperature sensor. The 2N3904, 2N2222 transistors and integrated thermal diodes found in microprocessors, FPGAs, and ASICs are commonly used temperature sensors. Connect a 100pF filter capacitor, as shown in Figure 7, to ensure accurate temperature measurements.

When the 2N3904 is connected to the TEMPX pin, the device uses the external temperature information for temperature-fault and current-measurement temperature compensation (tempco). If the external temperature measurement is not used or measures out of range, the device uses the internal temperature for temperature compensation and thermal-fault protection. Disable the external temperature measurement by connecting TEMPX to ground.

The device temperature fault thresholds are programmed through the PMBus interface. The default value for the thermal-shutdown threshold is +115°C. The default overtemperature response is to shut down and restart when the fault is no longer present. Note that a rising temperature faults when it crosses the OT\_FAULT\_LIMIT and clears when it falls below the OT\_WARN\_LIMIT. The OT\_WARN\_LIMIT should always be set below the OT\_FAULT\_LIMIT. The device shuts down and pulls PG low when it acts on a temperature fault.

#### **Regulation and Monitoring Functions**

The device improves the reliability of the system it powers with multiple circuits that protect the regulator and the load from unexpected system faults. The device continuously monitors the input voltage, output voltage and current, and internal/external temperatures. The device can be configured to provide alerts for specific conditions of the monitored parameters. The thresholds and responses for these parameters have factory-default values, but can also be configured through the PMBus interface. The status of the power supply can be queried any time by a PMBus master.

#### **Regulator Parameters**

Key operating parameters in the device, such as output voltage, switching frequency, and current-sense resistance, can be configured using resistors. This provides flexibility for the user while ensuring that the device has a well-defined "out-of-the-box" operational state. The pin configurations are only sampled when power is first applied (the device ignores changes to resistor settings after power-up). From this initial operating state, the user can change the parameters using PMBus commands. These changes can be stored in nonvolatile memory, allowing the device to subsequently power up into the customers specifically stored configuration state. However, it is recommended that the pin-strap or resistor settings always be applied with values chosen to provide a safe initial behavior prior to PMBus configuration.

Pin-strap settings are programmed by connecting a resistor from the appropriate device pins to SGND. The device reads the resistance at startup and sets command parameters per the tables in the following sections. Note that the external parts count can be reduced in some cases by unconnecting or grounding the configuration pins.

#### **Output-Voltage Selection**

The SET pin is used to establish the initial output voltage and can be pin strapped high or low, or connected to SGND through a resistor, to select the output voltage, as shown in <a href="Table 1">Table 1</a>. Note that the SET pin is read once at power-up and cannot be used to change the output voltage after that time. Note that shorting SET to ground puts the device into track mode. See the track mode paragraph for more information. The device considers open circuit on SET to be a fault condition so it sets the output voltage to 0V to protect the load.

If the desired output voltage is not included in <u>Table 1</u>, use a resistor to set the initial approximate output voltage, and then send VOUT\_COMMAND to set the exact desired output voltage.

The output voltage can be set to any voltage between 0.5V and 5.25V, including margining, provided the input voltage to the DC-DC converter ( $V_{PWR}$ ) is higher than the output voltage by an amount that conforms to the maximum duty-cycle specification.

The device's output voltage can be dynamically changed during operation through several PMBus commands. The output voltage can be decreased during operation without limit. The output voltage can be increased to 20% above the upper end of the allowable voltage determined by the RDIV setting. The RDIV setting is determined by the programmed output voltage when the output is enabled. Table 5 shows the voltage ranges that set each RDIV setting. As an example, if the output voltage is pin strapped to 1.2V, the RDIV is set to 0.65572 at startup. The output voltage can be increased to 15% above the upper end of the 0.65572 RDIV range, or 1.723V. The output voltage can be programmed higher than 1.723V, but the actual power-supply output may be clamped to a lower voltage.

#### **Setting Switching Frequency**

The switching frequency can be adjusted from 300kHz to 1MHz with an external resistor from SYNC to SGND per Table 3, or by sending the PMBus FREQUENCY SWITCH command. Note that the SYNC pin is read once at powerup and cannot be used to change the switching frequency after that time. The device considers open circuit on SYNC to be a fault condition so it sets the switching frequency to 575kHz in an attempt to pick a switching frequency typical of most applications. 575kHz is not a normal pin-strappable frequency, so if the user reads back a switching frequency of 575kHz, they know the SYNC resistor is open circuited. The switching frequency can be changed on the fly for frequencies between 300kHz to 475kHz and for frequencies between 476kHz to 1000kHz. The switching frequency during operation must stay either above or below 475kHz and should never cross this frequency. Doing so may result in unexpected operation. The user can cross the 475kHz switching boundary by disabling the device, changing the switching frequency, and then reenabling the device.

As a guideline, lower frequencies can be used to improve efficiency, while higher frequencies can be selected to reduce the physical size and value of the external filter inductor and capacitors.

Table 1. Output-Voltage Setting Using Pin-Resistor Setting

| R <sub>SET</sub> (kΩ) | OUTPUT VOLTAGE (V) |

|-----------------------|--------------------|

| 0 to 4.3              | Track mode         |

| 5 to 5.2              | 0.6                |

| 6.1 to 6.3            | 0.7                |

| 7 to 7.3              | 0.75               |

| 8.1 to 8.4            | 0.8                |

| 9.4 to 9.7            | 0.85               |

| 10.8 to 11.2          | 0.9                |

| 12.5 to 12.9          | 0.95               |

| 14.5 to 14.9          | 1                  |

| 17.6 to 18            | 1.05               |

| 21.2 to 21.8          | 1.1                |

| 25.8 to 26.4          | 1.2                |

| 31.2 to 32            | 1.5                |

| 37.9 to 38.7          | 1.8                |

| 43.7 to 44.7          | 2.5                |

| 50.5 to 51.7          | 3.3                |

| 58.4 to 59.6          | 5                  |

| 67.4 to Open          | 0                  |

#### **External Synchronization**

The device can be synchronized with an external clock to eliminate beat noise on the input- and output-voltage lines or to minimize input-voltage ripple. Synchronization is achieved by connecting a clock source to the SYNC pin. The incoming clock signal must be in the 300kHz to 1MHz range and must be stable (see the SYNC Frequency Drift Tolerance specification in the Electrical Characteristics table). The device synchronizes to the rising edge of the clock after the device is enabled. In the event of a loss of the external clock signal during normal operation after successful synchronization with the external clock, the device automatically switches at the frequency programmed into the PMBus command's FREQUENCY SWITCH variable. If an external clock is present at power-on when the device is trying to read the SYNC pin-strap resistance, the device cannot detect the synchronization frequency and does not write the proper frequency into FREQUENCY SWITCH. However, if the clock is still present at enable. the device reads the proper frequency and overwrites FREQUENCY SWITCH with the actual clock frequency.

**Table 2. Interleave Settings**

| SMBus ADDRESS | PHASE DELAY (°) |

|---------------|-----------------|

| xxxx000b      | 0               |

| xxxx001b      | 60              |

| xxxx010b      | 120             |

| xxxx011b      | 180             |

| xxxx100b      | 240             |

| xxxx101b      | 300             |

| xxxx110b      | 90              |

| xxxx111b      | 270             |

If a clock is not present at power-on, the device reads the pin-strap resistor value and writes the frequency into FREQUENCY SWITCH per Table 3. If an external clock is applied to SYNC after power-on but before enable, the device overwrites FREQUENCY SWITCH with the external clock frequency when the device is enabled. If an external clock is not applied prior to the device being enabled, the device keeps the originally programmed FREQUENCY SWITCH value. Applying a clock to SYNC after the device is enables causes the IC to synchronize to the clock, however, the FREQUENCY SWITCH value is not updated. For proper synchronization, the external clock can be applied prior to applying power to the device, but must be applied prior to enabling the device. The external clock frequency should not be changed after the device is enabled.

The device supports interleaving with an external SYNC input. The default phase delay is pin strappable and is determined by the 7-bit SMBus address, as shown in <a href="Table 2">Table 2</a>. The phase delay can also be changed by sending the PMBus INTERLEAVE command while the output is disabled. The phase delay should not be changed during operation. The programmed phase delay is between the rising edge of the SYNC clock signal and the center of the device's PWM pulse. The center of the PWM pulse is used for a reference point because the device's PWM pulse is dual-edge modulated.

#### **SMBus Address Selection**

The ADDR0 and ADDR1 pins are used in combination to set the SMBus address, as listed in <u>Table 4a</u>. Note that the SMBus specification recommends against using the shaded addresses. The PMBus address cannot be changed after startup. Note that SMBus address also sets the default phase delay for interleaving with an external

Table 3. Switching Frequency Resistor Settings (SYNC)

| R <sub>SYNC</sub> (kΩ) | SWITCHING FREQUENCY (kHz) |

|------------------------|---------------------------|

| 0 to 4.3               | 575                       |

| 5 to 5.2               | 300                       |

| 6.1 to 6.3             | 350                       |

| 7 to 7.3               | 400                       |

| 8.1 to 8.4             | 450                       |

| 9.4 to 9.7             | 500                       |

| 10.8 to 11.2           | 550                       |

| 12.5 to 12.9           | 600                       |

| 14.5 to 14.9           | 650                       |

| 17.6 to 18             | 700                       |

| 21.2 to 21.8           | 750                       |

| 25.8 to 26.4           | 800                       |

| 31.2 to 32             | 850                       |

| 37.9 to 38.7           | 900                       |

| 43.7 to 44.7           | 950                       |

| 50.5 to 51.7           | 1000                      |

| 58.4 to Open           | 575                       |

synchronization clock. The ADDR1 resistor also sets the default IOUT CAL GAIN.

#### **IOUT\_CAL\_GAIN Selection**

The device allows the user to set a default pinstrapped IOUT CAL GAIN at startup. IOUT CAL GAIN is the resistance of the current-sense element, which can be either the power inductor's DCR or a discrete current-sense resistor. The device's actual overcurrent trip point is a function of IOUT\_CAL\_GAIN, the currentsense element's actual resistance, and the value of the IOUT\_OC\_FAULT\_LIMIT. See the output-overcurrent protection paragraph for more information on setting the overcurrent trip point. Setting IOUT CAL GAIN is accomplished by pin strapping, connecting a resistor from ADDR1 to SGND, as listed in Table 4b. The user can achieve a more accurate value of IOUT CAL GAIN by setting this parameter through the PMBus. Note that ADDR1 is used to set both the PMBus address and IOUT CAL GAIN. The user should first determine the desired PMBus address and then choose the appropriate ADDR1 resistor per Table 4a and Table 4b.

Table 4a. SMBus Address Set by ADDR0, ADDR1 Resistor Connections

| DCR                     |                |                | R <sub>ADDR1</sub> (kΩ) |                |                |

|-------------------------|----------------|----------------|-------------------------|----------------|----------------|

| 4mΩ →                   | 0 to 4.3       | 5 to 5.2       | 6.1 to 6.3              | 7 to 7.3       | 8.1 to 8.4     |

| 8mΩ →                   | 9.4 to 9.7     | 10.8 to 11.2   | 12.5 to 12.9            | 14.5 to 14.9   | 17.6 to 18     |

| 12mΩ →                  | 21.2 to 21.8   | 25.8 to 26.4   | 31.2 to 32              | 37.9 to 38.7   | 43.7 to 44.7   |

| 16mΩ →                  | 50.5 to 51.7   | 58.4 to 59.6   | 67.4 to 68.8            | 85.7 to 87.5   | 113.8 to 116.2 |

| 20mΩ →                  | 138.6 to 141.4 | 167.3 to 170.7 | 202.9 to 207.1          | 234.6 to 239.4 | 271.2 to Open  |

| R <sub>ADDR0</sub> (kΩ) |                | SME            | Bus 7-BIT DEVICE AD     | DRESS          |                |

| 0 to 4.3                | 0x0A           | 0x22           | 0x3A                    | 0x52           | 0x6A           |

| 5 to 5.2                | 0x0B           | 0x23           | 0x3B                    | 0x53           | 0x6B           |

| 6.1 to 6.3              | 0x0C           | 0x24           | 0x3C                    | 0x54           | 0x6C           |

| 7 to 7.3                | 0x0D           | 0x25           | 0x3D                    | 0x55           | 0x6D           |

| 8.1 to 8.4              | 0x0E           | 0x26           | 0x3E                    | 0x56           | 0x6E           |

| 9.4 to 9.7              | 0x0F           | 0x27           | 0x3F                    | 0x57           | 0x6F           |

| 10.8 to 11.2            | 0x10           | 0x28           | 0x40                    | 0x58           | 0x70           |

| 12.5 to 12.9            | 0x11           | 0x29           | 0x41                    | 0x59           | 0x71           |

| 14.5 to 14.9            | 0x12           | 0x2A           | 0x42                    | 0x5A           | 0x72           |

| 17.6 to 18              | 0x13           | 0x2B           | 0x43                    | 0x5B           | 0x73           |

| 21.2 to 21.8            | 0x14           | 0x2C           | 0x44                    | 0x5C           | 0x74           |

| 25.8 to 26.4            | 0x15           | 0x2D           | 0x45                    | 0x5D           | 0x75           |

| 31.2 to 32              | 0x16           | 0x2E           | 0x46                    | 0x5E           | 0x76           |

| 37.9 to 38.7            | 0x17           | 0x2F           | 0x47                    | 0x5F           | 0x77           |

| 43.7 to 44.7            | 0x18           | 0x30           | 0x48                    | 0x60           | 0x78           |

| 50.5 to 51.7            | 0x19           | 0x31           | 0x49                    | 0x61           | 0x79           |

| 58.4 to 59.6            | 0x1A           | 0x32           | 0x4A                    | 0x62           | 0x7A           |

| 67.4 to 68.8            | 0x1B           | 0x33           | 0x4B                    | 0x63           | 0x7B           |

| 85.7 to 87.5            | 0x1C           | 0x34           | 0x4C                    | 0x64           | 0x7C           |

| 113.8 to 116.2          | 0x1D           | 0x35           | 0x4D                    | 0x65           | 0x7D           |

| 138.6 to 141.4          | 0x1E           | 0x36           | 0x4E                    | 0x66           | 0x7E           |

| 167.3 to 170.7          | 0x1F           | 0x37           | 0x4F                    | 0x67           | 0x7F           |

| 202.9 to 207.1          | 0x20           | 0x38           | 0x50                    | 0x68           | 0x7F           |

| 234.6 to Open           | 0x21           | 0x39           | 0x51                    | 0x69           | 0x7F           |

**Note:** The SMBus specification recommends against using the shaded addresses.

## Table 4b. IOUT\_CAL\_GAIN Set by ADDR1 Resistor Connection

| R <sub>ADDR1</sub> (kΩ) | IOUT_CAL_GAIN (mΩ) |

|-------------------------|--------------------|

| 0 to 8.4                | 4                  |

| 9.4 to 18               | 8                  |

| 21.2 to 44.7            | 12                 |

| 50.5 to 116.2           | 16                 |

| 138.6 to Open           | 20                 |

Figure 2. Startup Timing Diagrams

### **Internal Bias Regulators**

The device analog circuitry is powered by an internal 3.3V regulator (3P3). The device also has an internal bias regulator to generate a 1.8V rail (1P8) to power internal digital circuitry. Bypass the 3P3 pin to SGND with a 4.7 $\mu$ F ceramic (X5R or better) capacitor. Bypass 1P8 to DGND with a 10 $\mu$ F ceramic (X5R or better) capacitor. These internal regulators are not designed to power external circuitry.

#### Input-Voltage Feed Forward

The device uses input-voltage feed-forward techniques to provide excellent line regulation. Connect the INSNS pin to the power-train input voltage through a  $2k\Omega$  series resistor for input-voltage feed-forward and telemetry. The voltage at INSNS is sampled every  $4\mu$ s.

The device does not enable DC-DC conversion if the voltage at INSNS is below the PMBus VIN\_UV\_FAULT\_LIMIT threshold (default 4V) or below the VIN\_ON, VIN\_OFF limits (default 6V rising and 5.5V falling, respectively.) The user can read back the measured input-voltage value using the PMBus READ\_VIN command.

#### **Output On/Off Control**

The device features both a hardware-enable input (EN pin) and a PMBus-enable function. The factory default for the enable functions is that the device can be enabled by either an assertion of the hardware EN pin to a logic-high level or by issuing a PMBus-enable command. The enable functionality can be changed using the PMBus

ON\_OFF\_CONFIG command (see the PMBus specification for details).

#### **Device Initialization**

The device includes power-on-reset circuits that monitor the internal bias supplies and the external supply voltage. When all supplies are above their UVLO thresholds, the following self-test sequence occurs:

- 1) Run self-test and CRC check on the memory.

- Read resistor settings and set command values and program working memory accordingly.

- Confirm absence of any faults that would prevent turn-on.

- 4) Begin wait for a valid output-enable condition (hardware or PMBus command).

The power-up and initialization process takes approximately 25ms, depending on the specific combination of pin-strap resistor values to be read. The device does not enable output regulation until initialization is complete.

### **Output-Voltage Sequencing**

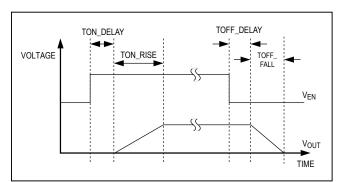

In a system with multiple MAX15303 devices or other PMBus-controlled ICs, output-voltage sequencing can be achieved by configuring each power supply with different turn-on/turn-off delays and output rise/fall times. All power supplies are then commanded to turn on (or off) simultaneously using a combined EN signal, or by using the PMBus Group Command Protocol.

The device supports soft-start and soft-stop functionality as shown in Figure 3. The PMBus TON\_RISE and TOFF\_FALL commands determine the soft-start and soft-stop ramp times. The TON\_DELAY command sets the time from a valid enable condition to the beginning of the output-voltage ramp. Similarly, the TOFF\_DELAY command sets the time between loss of valid enable condition and the beginning of the output ramp-down to 0V. The default setting for TON\_DELAY is the minimum value of 1ms and the default setting for the TON\_RISE is 5ms.

The output-voltage slew rates for turn-on and turn-off are given by VOUT\_COMMAND/TON\_RISE and VOUT\_COMMAND/TOFF\_FALL, respectively. It is recommended to set TON\_RISE and TOFF\_FALL to at least 1ms to prevent excessive inrush currents due to high dV/dt. The output-voltage ramp-up rises monotonically above 300mV regardless of input voltage, output voltage, or prebias voltage on the output. Note that the device initiates the InTune calibration process after the soft-start ramp-up is complete.

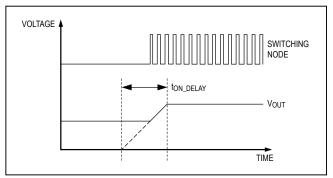

### Startup with Prebias

The device supports soft-start into a prebias output-voltage condition. A prebias condition occurs when there is already a voltage at the output of the power supply before it has been enabled. This can be caused by precharged output capacitors, or a parasitic ESD diode in the load IC that pulls the output up to another system-supply rail. When EN is asserted, the device checks the output for the presence of prebias voltage. If the prebias voltage is less than 200mV, startup is performed normally assuming no prebias. If the prebias is greater than 200mV but below the target set point for the output, the device ramps up the output voltage from the prebias voltage to the regulation set point, as shown in Figure 4. If the prebias is above the VOUT\_OV\_FAULT\_LIMIT value, the device does not attempt soft-start.

Figure 3. Turn-On/-Off Delays and Soft-Start/-Stop Times

If prebias was detected at the time of enable, the device saves the prebias voltage level in a register and terminates the output-voltage ramp-down at the prebias voltage when disabled. This register is not user accessable.

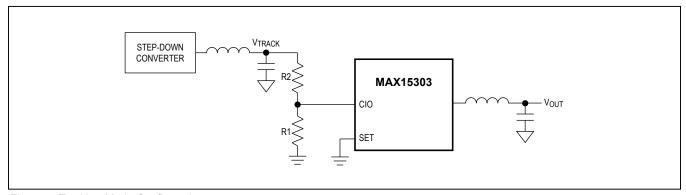

#### **Voltage Tracking**

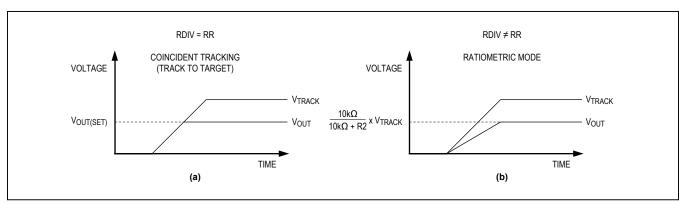

The device supports voltage tracking of the output from a reference input. To select the tracking mode, connect the SET pin to SGND. The device's output tracks the V<sub>TRACK</sub> voltage with a preset ratio governed by an internal feedback divider (RDIV) and an external resistive voltage-divider (R1, R2), which is placed from the supply being tracked to SGND (Figure 5). The center tap of the external divider should be connected to the CIO input.

In tracking mode, V<sub>OUT</sub> is regulated to the lower of:

$$V_{OUT} = \frac{V_{TRACK}}{RDIV} \times \frac{R1}{R1 + R2}$$

or the output set-point voltage (VOUT(SET)), as determined by the VOUT COMMAND. As seen in the above equation, if the resistor-divider ratio RR = R1/(R1 + R2) is chosen such that it is equal to the operational RDIV, the output voltage follows the tracking voltage coincidentally (Figure 6a). For all other cases, the VOLIT follows a ratiometric tracking (Figure 6b) depending on the ratio of RR and RDIV. The IC automatically selects RDIV based on the output set-point voltage as shown in <u>Table 5</u>. For example, if V<sub>OUT(SET)</sub> is set to 1.6V by the VOUT COMMAND, RDIV is set to 0.54247. Note that the default RDIV value in track mode is 0.20272, which corresponds to a 5V output-voltage setting. For reliable voltage tracking, it is recommended that once the device is powered up, the VOUT\_COMMAND should not be changed so as to cause a change to the operational RDIV (Table 5). If such a change in VOUT COMMAND is required, the user should save the new V<sub>OUT(SET)</sub> in the

Figure 4. Startup into a Prebiased Output

device memory (using STORE\_USER\_ALL\_COMMAND) and recycle the input power to set a new RDIV operational value. For simplicity, fix R1 at  $10k\Omega$  and use the following equation to determine R2:

$$R2 = 10k \times \left(\frac{V_{TRACK}}{R_{DIV} \times V_{OUT}} - 1\right)$$

For the best voltage regulation, RR should be set such that the final  $V_{OUT}$  tracking target voltage is slightly higher than the output set-point voltage determined by VOUT\_COMMAND (5V default). The output-voltage ramp tracks the  $V_{TRACK}$  input, as shown in Figure 6, until reaching the VOUT\_COMMAND value. If the application requires continuous ratiometric tracking, VOUT\_COMMAND should be set higher than the desired  $V_{OUT}$  tracking target or left at the 5.0V default value. In this case, there is a small regulation inaccuracy due to the tolerance of the external resistors.

#### **Output-Voltage Margining**

The device supports voltage margining, which can be used to test the end equipment's design margin associated with

power-supply variation. The margin set-point commands (VOUT\_MARGIN\_HIGH and VOUT\_MARGIN\_LOW) are set to ±5% of VOUT\_COMMAND by default, but can be changed through the PMBus interface. Output-voltage margining is controlled by the OPERATION command.

Table 5. Required Divider Ratio (RDIV) as a Function of  $V_{OUT}$

| VOUT_COMMAND (V) | RDIV    |

|------------------|---------|

| < 0.55           | 0.99547 |

| 0.55 to < 0.95   | 0.88222 |

| 0.95 to < 1.15   | 0.76897 |

| 1.15 to < 1.502  | 0.65572 |

| 1.502 to < 1.815 | 0.54247 |

| 1.815 to < 2.295 | 0.42922 |

| 2.295 to < 3.117 | 0.31597 |

| 3.117 to < 5.5   | 0.20272 |

Figure 5. Tracking Mode Configuration

Figure 6. Tracking

#### **Output Voltage Ranges and Fault Limits**

The device features output undervoltage and overvoltage protection. The PMBus VOUT\_OV\_FAULT\_LIMIT is set to 115% of VOUT\_COMMAND by default, and VOUT\_UV\_FAULT\_LIMIT is set to 85%. These thresholds can be changed through PMBus and set anywhere between 0V and the lower of either the ADC full-scale value or VOUT\_MAX (VOUT\_MAX is 110% of VOUT\_COMMAND by default.

The device continuously monitors the output voltage. If the voltage exceeds the protection limits, the device follows the actions prescribed by the VOUT\_OV\_FAULT\_RESPONSE or VOUT\_UV\_FAULT\_RESPONSE commands as appropriate. By default, an overvoltage fault results in an immediate shutdown with no retry attempts, whereas an undervoltage fault is ignored. The fault response commands can be changed at any time, but changes to the fault-response commands only take effect when the output is disabled.

#### **Output-Overcurrent Protection**

The MAX15303 monitors the voltage across the output inductor resistance (or other resistive sense element) to provide output-current monitoring and overload protection. The voltage signal at the current-sense element is divided by the IOUT\_CAL\_GAIN value to yield output current in amps. The value of IOUT\_CAL\_GAIN is initially set by the ADDR1 resistance, according to Table 4b, and should be set as close as possible to the inductor DCR (or the resistive sense element's resistance). More accurate output-current measurement can be achieved by calibrating the IOUT\_CAL\_GAIN value. For more information on calibrating IOUT\_CAL\_GAIN, refer to Maxim Application Note #AN5601: Current Calibration Procedure for InTune Digital Power.

The overcurrent-fault threshold is set by the IOUT\_OC\_FAULT\_LIMIT command; the default value is 8A. The default fault response to an overcurrent condition is to turn off both internal MOSFETs, wait 700ms, and then restart the regulator. This process repeats indefinitely until the fault condition no longer persists. This fault-response behavior can be changed using the PMBus IOUT\_OC\_FAULT\_RESPONSE command.

#### **Fault Handling**

The device monitors input voltage, output voltage, output current, and both internal and external temperatures. The fault thresholds and responses are factory-set, but can be changed using PMBus commands. Fault detection can be

individually enabled or disabled for the parameters through the PMBus. The default limits are as indicated in <u>Table 6</u>. The response to a fault condition can be changed through the PMBus. Refer to Maxim Application Note #AN5816 MAX15303 *PMBus Command Set User's Guide* for more information on setting fault thresholds and fault responses.

### **Nonvolatile PMBus Memory**

The device includes three nonvolatilie memory banks to store PMBus configuration values. The first is the MAXIM store, which contains a read-only copy of all default command settings. The next is the read/write-accessible DEFAULT store, which is intended to contain an equipment manufacturer's preferred or suggested settings. Third is the read/write-accessible USER store, which is intended to store the end user's preferred settings.

When the device is enabled, a combination of the pinconfigurable command values and the contents of the USER store are loaded into working memory. Any command values that have been edited and stored to the USER memory take precedence over their corresponding pin-configured values.

Equipment manufacturers should ensure that the DEFAULT and USER stores are saved with duplicate copies of the manufacturer's preferred or suggested command values. In this manner, an end user can restore the DEFAULT memory and save to the USER store any time they wish to return the device to the manufacturer's original configuration.

Special security commands and features are included so that a manufacturer user can store and lock the regulator's configuration on a command-by-command basis. Contact Maxim for application notes describing these security features.

**Table 6. Fault Conditions**

| FAULT<br>CONDITION            | DEFAULT<br>THRESHOLD   | RANGE           |

|-------------------------------|------------------------|-----------------|

| V <sub>IN</sub> Overvoltage   | 14V                    | 0 to 14.7V      |

| V <sub>IN</sub> Undervoltage  | 4.2V                   | 0 to 14.7V      |

| V <sub>OUT</sub> Overvoltage  | VOUT_COMMAND<br>x 115% | 0 to 5.5V       |

| V <sub>OUT</sub> Undervoltage | VOUT_COMMAND<br>x 85%  | 0 to 5.5V       |

| I <sub>OUT</sub> Overcurrent  | 8A                     | 0 to 8.97A      |

| Overtemperature               | 115°C                  | -40°C to +150°C |

#### **Temperature Sensing**

The device supports remote temperature sensing in addition to sensing its own internal temperature. The device uses a  $\Delta V_{BE}$  measurement internally and at the TEMPX input to compute temperature. This technique is widely employed because it requires no calibration of the sensor. Any PN junction can be used as a temperature sensor. The 2N3904, 2N2222 transistors and integrated thermal diodes found in microprocessors, FPGAs, and ASICs are commonly used temperature sensors. Connect a 100pF filter capacitor, as shown in Figure 7, to ensure accurate temperature measurements.

The device temperature and thermal-fault thresholds are programmed through the PMBus interface. The default value for the thermal-shutdown threshold is +115°C. The device shuts down and PG pulls low when it crosses the temperature-fault threshold.

#### Power Good (PG)

PG is an open-drain power-good output used to indicate when the device is ready to provide regulated output voltage to the load. During startup and during a fault condition, PG is held low. PG is asserted high after the output has ramped to a voltage above the POWER\_GOOD\_ON threshold and a successful InTune calibration has completed. If the output regulation voltage falls below the POWER\_GOOD\_OFF threshold, PG is deasserted.

Figure 7. Temperature Sensing with a 2N3904 npn Transistor

#### **PMBus Digital Interface**

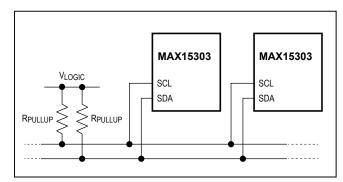

The MAX15303 is a PMBus-compatible device that includes many of the standard PMBus commands. A PMBus 1.2-compliant device uses the System Management Bus (SMBus) version 2.0 for transport protocol and responds to the SMBus slave address. In this data sheet, the term SMBus is used to refer to the electrical characteristics of the PMBus communication using the SMBus physical layer. The term PMBus is used to refer to the PMBus command protocol.

The device employs six standard SMBus protocols (Write Byte, Read Byte, Write Word, Read Word, Write Block, and Read Block) to program output voltage and warning/faults thresholds, read monitored data, and provide access to all manufacturer-specific commands.

The device also supports the group command. The group command is used to send commands to more than one PMBus device. It is not required that all the devices receive the same command. However, no more than one command can be sent to any one device in one group command packet. The group command must not be used with commands that require the receiving device to respond with data, such as the STATUS\_BYTE command. When the device receives a command through this protocol, it begins execution immediately of the received command after detecting the STOP condition.

When the data word is transmitted, the lower order byte is sent first and the higher order byte is sent last. Within any byte, the most significant bit (MSB) is sent first and the least significant bit (LSB) is sent last. Contact the factory for detailed PMBus command support.

#### **Supported PMBus Commands**

The device supports the standard PMBus commands given in <u>Table 7</u>. Refer to Maxim Application Note AN5816: *MAX15303 PMBus Command Set User's Guide* for the device's PMBus command details.

A single pair of pullup resistors (one each for SCL and SDA) is required for each shared bus, as shown in <u>Figure 8</u>. Consult the SMBus 2.0 specifications as well as the guaranteed drive capability of SDA in the

**Table 7. PMBus Command Summary**

| COMMAND<br>CODE | COMMAND NAME           | SMBus<br>TRANSFER<br>TYPE | # OF<br>DATA<br>BYTES | MIN | MAX  | DEFAULT VALUE              | UNITS |