### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Supply Voltage (V+ to GND)              | 6V            |

|-----------------------------------------|---------------|

| Input Voltage                           | 6V            |

| Input Current                           |               |

| Output Short-Circuit Duration (Note 2). | Indefinite    |

| Operating Temperature Range (Note 3)    |               |

| LTC6702C                                | 40°C to 85°C  |

| LTC6702I                                | 40°C to 85°C  |

| LTC6702H                                | 40°C to 125°C |

| Specified Temperature Range (Note 4) |               |

|--------------------------------------|---------------|

| LTC6702C                             | 0°C to 70°C   |

| LTC6702I                             | 40°C to 85°C  |

| LTC6702H                             | 40°C to 125°C |

| Junction Temperature                 | 150°C         |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |               |

| TSOT Packages                        | 300°C         |

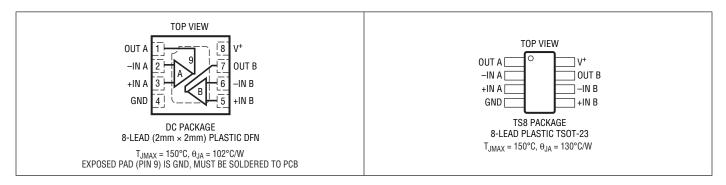

### PIN CONFIGURATION

### **ORDER INFORMATION**

#### **Lead Free Finish**

|                      |                   |               |                                | SPECIFIED         |

|----------------------|-------------------|---------------|--------------------------------|-------------------|

| TAPE AND REEL (MINI) | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION            | TEMPERATURE RANGE |

| LTC6702CDC#TRMPBF    | LTC6702CDC#TRPBF  | LCZJ          | 8-Lead (2mm × 2mm) Plastic DFN | 0°C to 70°C       |

| LTC6702IDC#TRMPBF    | LTC6702IDC#TRPBF  | LCZJ          | 8-Lead (2mm × 2mm) Plastic DFN | -40°C to 85°C     |

| LTC6702HDC#TRMPBF    | LTC6702HDC#TRPBF  | LCZJ          | 8-Lead (2mm × 2mm) Plastic DFN | -40°C to 125°C    |

| LTC6702CTS8#TRMPBF   | LTC6702CTS8#TRPBF | LTCZK         | 8-Lead Plastic TSOT-23         | 0°C to 70°C       |

| LTC6702ITS8#TRMPBF   | LTC6702ITS8#TRPBF | LTCZK         | 8-Lead Plastic TSOT-23         | -40°C to 85°C     |

| LTC6702HTS8#TRMPBF   | LTC6702HTS8#TRPBF | LTCZK         | 8-Lead Plastic TSOT-23         | -40°C to 125°C    |

TRM = 500 pieces. \*Temperature grades are identified by a label on the shipping container.

Consult LTC Marketing for parts specified with wider operating temperature ranges.

Consult LTC Marketing for information on lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

LINEAR

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full specified temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V^+ = 3V$ , $V_{CM} = 1.5V$ , $C_{OUT} = 20pF$ , unless otherwise noted.

| SYMBOL                   | PARAMETER                      | CONDITIONS                                                                             |   | MIN               | TYP   | MAX                   | UNITS          |

|--------------------------|--------------------------------|----------------------------------------------------------------------------------------|---|-------------------|-------|-----------------------|----------------|

| V <sup>+</sup>           | Supply Voltage                 | Guaranteed by PSRR                                                                     | • | 1.7               |       | 5.5                   | V              |

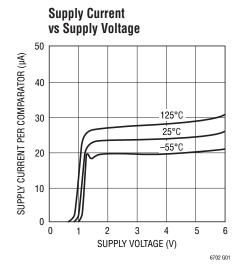

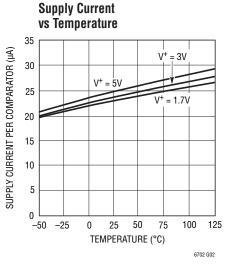

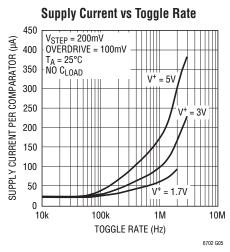

| l+                       | Supply Current per Comparator  | V <sup>+</sup> = 3V                                                                    | • |                   | 24    | 30<br>40              | μA<br>μA       |

|                          |                                | V <sup>+</sup> = 5V                                                                    | • |                   | 25    | 32<br>42              | μA<br>μA       |

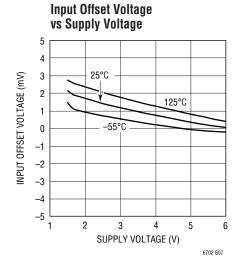

| V <sub>OS</sub>          | Input Offset Voltage           | (Note 5)<br>LTC6702C/LTC6702I<br>LTC6702H                                              | • |                   | 1     | 3.5<br>5<br>6         | mV<br>mV<br>mV |

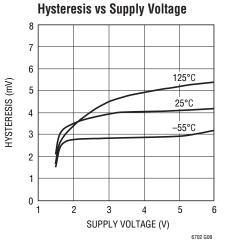

| V <sub>HYST</sub>        | Input Hysteresis Voltage       | (Note 5)<br>LTC6702C/LTC6702I<br>LTC6702H                                              | • | 2.5<br>1.6<br>1.6 | 4.3   | 6.2<br>7.2<br>8.2     | mV<br>mV<br>mV |

| $\Delta V_{OS}/\Delta T$ | Input Offset Voltage Drift     | (Note 5)                                                                               | • |                   | 6     |                       | μV/°C          |

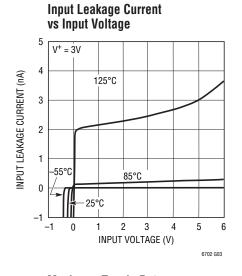

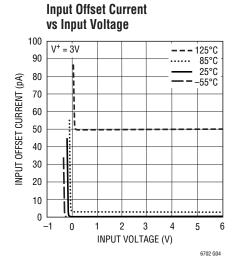

| I <sub>IN</sub>          | Input Leakage Current          | LTC6702C/LTC6702I<br>LTC6702H                                                          | • |                   | 0.001 | 1<br>10               | nA<br>nA<br>nA |

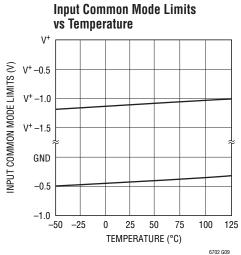

| CMRR                     | Common Mode Rejection Ratio    | $V_{CM} = -0.1V \text{ to } V_{DD} - 1.2V$                                             | • | 58<br>56          | 70    |                       | dB<br>dB       |

|                          | Input Voltage Range            | Guaranteed by CMRR                                                                     | • | -0.1              |       | V <sub>DD</sub> – 1.2 | V              |

| PSRR                     | Power Supply Rejection Ratio   | $V^+ = 1.7V$ to 5.5V, $V_{CM} = 0.5V$                                                  | • | 56<br>54          | 65    |                       | dB<br>dB       |

| $V_{0L}$                 | Output Swing Low               | Overdrive = 20mV (Note 6)<br>I <sub>SINK</sub> = 100µA<br>I <sub>SINK</sub> = 15mA     | • |                   |       | 10<br>250             | mV<br>mV<br>mV |

| V <sub>OH</sub>          | Output Swing High              | Overdrive = 20mV (Note 6)<br>I <sub>SOURCE</sub> = 100µA<br>I <sub>SOURCE</sub> = 15mA | • |                   |       | 10<br>350             | mV<br>mV<br>mV |

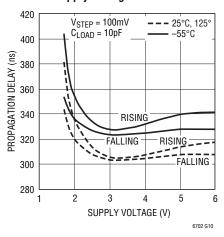

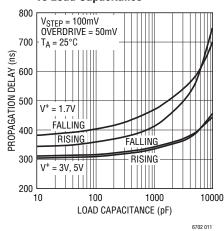

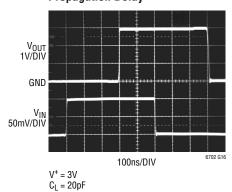

| t <sub>PD</sub>          | Propagation Delay              | (Note 7)                                                                               | • |                   | 320   | 450<br>500            | ns<br>ns       |

| $\Delta t_{PD}$          | Differential Propagation Delay | Between Channels                                                                       |   |                   | 4     |                       | ns             |

| t <sub>SKEW</sub>        | Propagation Delay Skew         | Between t <sub>PDLH</sub> /t <sub>PDHL</sub>                                           |   |                   | 4     |                       | ns             |

| t <sub>r</sub>           | Output Rise Time               |                                                                                        |   |                   | 11    |                       | ns             |

| tf                       | Output Fall Time               |                                                                                        |   |                   | 15    |                       | ns             |

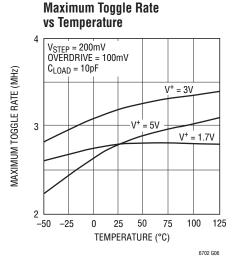

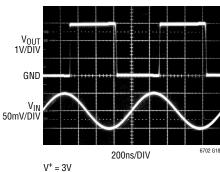

| f <sub>MAX</sub>         | Maximum Toggle Frequency       |                                                                                        |   |                   | 3.2   |                       | MHz            |

| I <sub>SC</sub>          | Short-Circuit Current          | V + = 5V                                                                               |   |                   | ±250  |                       | mA             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** A heat sink may be required to keep the junction temperature below absolute maximum. This depends on the power supply voltage and how many comparators are shorted. The  $\theta_{JA}$  specified for the DC and TS packages is with minimal PCB heat spreading metal. Using expanded metal area on all layers of a board reduces this value.

**Note 3:** The LTC6702C and LTC6702I are guaranteed functional over the temperature range of  $-40^{\circ}$ C to 85°C. The LTC6702H is guaranteed functional over the operating temperature range of  $-40^{\circ}$ C to 125°C.

**Note 4:** The LTC6702C is guaranteed to meet specified performance from 0°C to 70°C. The LTC6702C is designed, characterized and expected to

meet specified performance from  $-40^{\circ}$ C to 85°C but is not tested or QA sampled at these temperatures. The LTC6702I is guaranteed to meet specified performance from  $-40^{\circ}$ C to 85°C. The LTC6702H is guaranteed to meet specified performance from  $-40^{\circ}$ C to 125°C.

**Note 5:** The LTC6702 comparators include internal hysteresis. The offset voltage is defined as the average of the input voltages (trip points) required to change the output in each direction minus  $V_{CM}$ , while the hysteresis voltage is the difference of these trip points.

**Note 6:** Output voltage swings are measured between the output and power supply rails.

**Note 7:** Propagation delay is for 200mV steps, and 50mV of overdrive. Overdrive is measured relative to the positive and negative trip points.

6702fa

### TYPICAL PERFORMANCE CHARACTERISTICS

6702fa

### TYPICAL PERFORMANCE CHARACTERISTICS

#### **Propagation Delay** vs Supply Voltage

#### **Propagation Delay** vs Load Capacitance

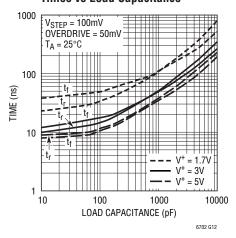

#### **Output Rise and Fall** Times vs Load Capacitance

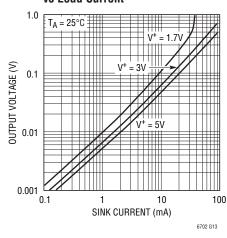

#### **Output Low Voltage** vs Load Current

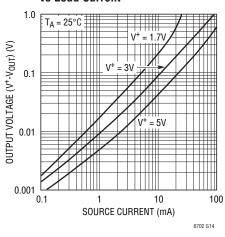

#### **Output High Voltage** vs Load Current

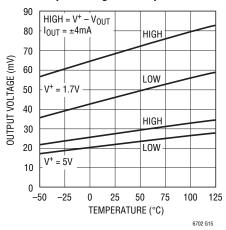

#### **Output Voltage vs Temperature**

#### **Propagation Delay**

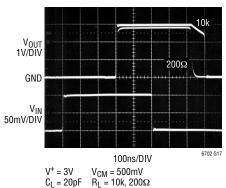

**Propagation Delay with Load**

**1MHz Sinusoid Response**

$C_1 = 20pF$

V<sub>CM</sub> = 500mV

$V_{CM} = 500 \text{mV}$

### LTC6702

### PIN FUNCTIONS

OUT A (Pin 1): Output of Comparator A.

-IN A (Pin 2): Inverting Input of Comparator A.

+IN A (Pin 3): Noninverting Input of Comparator A.

GND (Pin 4): Ground.

+IN B (Pin 5): Noninverting Input of Comparator B.

-IN B (Pin 6): Inverting Input of Comparator B.

**OUT B (Pin 7):** Output of Comparator B.

V+ (Pin 8): Positive Supply Voltage

**Exposed Pad (Pin 9, DC Package Only):** Ground. The

Exposed Pad must be soldered to PCB.

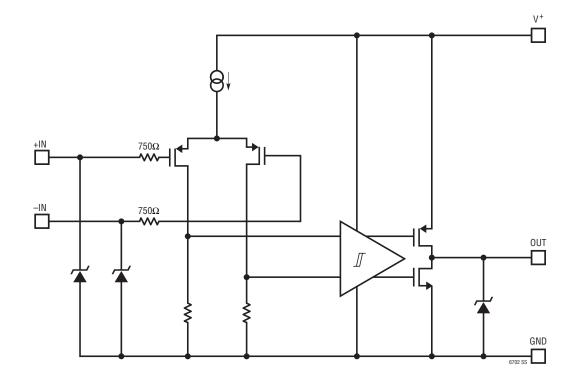

### SIMPLIFIED SCHEMATIC

### APPLICATIONS INFORMATION

The LTC6702 device is a fast (500ns delay), low power, low voltage (1.7V to 5.5V supply) general purpose dual comparator. It provides rail-to-rail outputs able to interface to TTL/CMOS, draws low supply currents (30µA/comparator), and has internal hysteresis (approximately 4mV).

#### **Hysteresis**

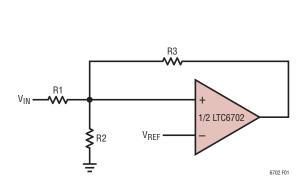

Each comparator has built-in hysteresis to simplify designs, to insure stable operation in the presence of noise at the inputs, and to reject supply rail noise. The reference voltage applied to the input is not the exact switching threshold value due to the built-in hysteresis. Actual output switching typically occurs within  $\pm 2.2$ mV of the reference voltage, plus or minus the input offset voltage. External positive feedback circuitry can be employed to increase effective hysteresis if desired, as shown in Figure 1. This circuitry will provide an apparent effect on both the rising and falling input thresholds (the actual internal trip points remain unaffected). If an inverting configuration with hysteresis is needed, simply swap the  $V_{IN}$  and  $V_{REF}$  connections.

#### **Unused Inputs**

Any unused inputs should be connected in a way that fixes the output logic state high or low. One easy way to do this is to tie +IN to  $V^+$  and -IN to GND.

#### **Input Protection**

External input protection circuitry is only needed if currents would otherwise exceed the absolute maximum rating. Inputs driven further negative than 100mV below ground will not cause damage provided the current is limited to 10mA. ESD protection diodes are provided to prevent damage during handling.

#### **Comparator Input**

The allowable input voltage ranges from 100mV below GND to within 1.2V of the positive supply. The input may be forced below ground without causing an improper output, though some additional input current will begin to flow from the ESD input protection diode. The inputs can reach up to 6V independent of the V+ supply voltage without causing additional input current or damage to the part. As long as one input is within the allowable input voltage range, the LTC6702 will continue to function normally.

#### **Comparator Output**

The comparator output is a push-pull CMOS stage guaranteed to swing to within 350mV of V<sup>+</sup> and 250mV of ground, over temperature when sourcing or sinking 15mA. No external pull-up/down resistor is required. To

Additional Hystersis =

$$\frac{R1}{R3} \cdot V^+$$

Trip Voltages:

$V_{IN(L \to H)} = V_{REF} \cdot R1 \cdot \left(\frac{1}{R1} + \frac{1}{R2} + \frac{1}{R3}\right)$

$V_{IN(H \to L)} = V_{REF} \cdot R1 \cdot \left(\frac{1}{R1} + \frac{1}{R2} + \frac{1}{R3}\right) - \left(\frac{R1}{R3}\right) \cdot V^+$

Example: Additional Hysteresis = 50mV, V<sup>+</sup> = 5V R1=10k R2=249k R3=1M FOR  $V_{REF} = 0.5V : V_{IN} (L \rightarrow H) = 0.525V V_{IN} (H \rightarrow L) = 0.475V$

$$V_{IN}(H \rightarrow L) = 0.475$$

Figure 1. Additional Hysteresis Circuit for Noninverting Configuration

### APPLICATIONS INFORMATION

maintain micropower operation, the output stage uses a break-before-make circuit. The break interval of this circuit turns off both the pull-up and pull-down devices for tens of nanoseconds before activating the appropriate output transistor (depends on the output transition direction). Any load connected to the output will charge or discharge internal capacitance during this interval. This can create a soft corner during output transitions and also decrease the propagation delay. The Typical Performance Characteristics section shows this behavior under three load conditions: unloaded, 10k to ground and  $200\Omega$  to ground. Loads to V+ have a similar affect when the output is transitioning from low to high.

### **Power Supplies**

The comparator circuitry operates from a single 1.7V to 5.5V. A  $0.1\mu\text{F}$  minimum bypass capacitor is required between the V<sup>+</sup> pin and GND. When the output is sinking

at least 1mA, a 1 $\mu$ F bypass capacitor is recommended. Pulsing the V<sup>+</sup> supply to the comparators on and off may engage the ESD protection circuitry at the V<sup>+</sup> pin. If this occurs, current is pulled from the V<sup>+</sup> pin through the output stage. Using the recommended supply bypass capacitors with some series resistance in the V<sup>+</sup> supply line will help to prevent this action in pulsed supply applications.

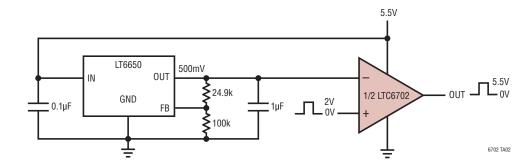

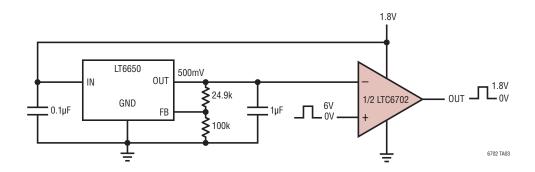

#### **Level Translators**

The level translators in the Typical Applications section show an adjustable high-precision voltage reference enabling the user to vary the threshold voltage. Simply adjusting the ratio of the two resistors changes the threshold voltage according to the following equation:

$$V_{THR} = 0.4 \left( 1 + \frac{R_F}{R_G} \right)$$

### TYPICAL APPLICATIONS

#### Low to High Level Translator

### TYPICAL APPLICATIONS

#### **High to Low Level Translator**

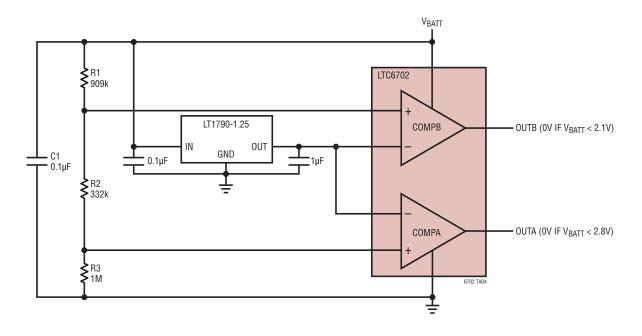

#### **Micropower Battery Monitor with Fast Response**

### PACKAGE DESCRIPTION

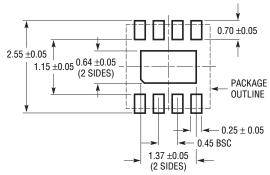

#### DC Package 8-Lead Plastic DFN (2mm × 2mm)

(Reference LTC DWG # 05-08-1719 Rev A)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- 1. DRAWING IS NOT A JEDEC PACKAGE OUTLINE

2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- A. DIMENSIONS ARE IN MILLIMITIESS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH, MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED

SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

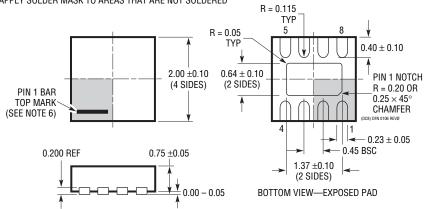

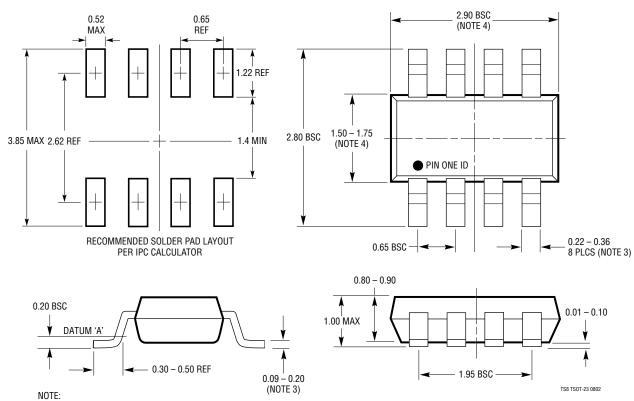

### PACKAGE DESCRIPTION

#### TS8 Package 8-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1637)

- 1. DIMENSIONS ARE IN MILLIMETERS

2. DRAWING NOT TO SCALE

- 3. DIMENSIONS ARE INCLUSIVE OF PLATING

- 4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

- 5. MOLD FLASH SHALL NOT EXCEED 0.254mm

- 6. JEDEC PACKAGE REFERENCE IS MO-193

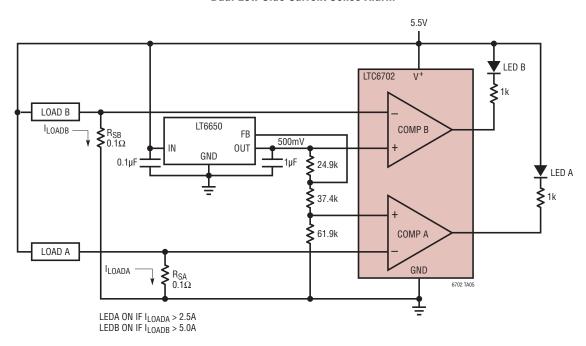

### TYPICAL APPLICATION

#### **Dual Low Side Current Sense Alarm**

## **RELATED PARTS**

| PART NUMBER                    | DESCRIPTION                                        | COMMENTS                                                                   |

|--------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|

| LTC1441/LTC1442                | Dual Ultralow Power Comparators with Reference     | 1.182V ±1% Reference, 8µs Propagation Delay, 5.7µA                         |

| LTC1541/LTC1542                | Micropower Amplifier with Comparator and Reference | 1.2V ±0.8% Reference, Amplifier Stable with 1000pF Load                    |

| LTC1842/LTC1843                | Dual Ultralow Power Comparators with Reference     | 1.182V ±1% Reference, 4µs, 3.5µA, Open-Drain Out                           |

| LT6660                         | Tiny Micropower Precision Series References        | 0.2% Reference, 20ppm/°C Drift, 20mA Output, 2mm × 2mm DFN Package         |

| LT6700-1/LT6700-2/<br>LT6700-3 | Dual Comparators with 400mV Reference              | 1.4V to 18V Operating Range, 18µs Propagation Delay, SOT-23 Package        |

| LT6703-2/LT6703-3              | Tiny Single Comparator with 400mV Reference        | 1.4V to 18V Operating Range, 18µs Propagation Delay, 2mm × 2mm DFN Package |