### **Ordering Information**

|         | Package Option                                                 |

|---------|----------------------------------------------------------------|

| Device  | 48-Lead LQFP 7.00x7.00mm body 1.60mm height (max) 0.50mm pitch |

| HV20822 | HV20822FG-G                                                    |

<sup>-</sup>G indicates package is RoHS compliant ('Green')

|                                                  | <u> </u>                                     |

|--------------------------------------------------|----------------------------------------------|

| Parameter                                        | Value                                        |

| V <sub>DD</sub> Logic power supply voltage       | -0.5V to +15V                                |

| V <sub>PP</sub> - V <sub>NN</sub> Supply voltage | +225V                                        |

| V <sub>PP</sub> Positive high voltage supply     | -0.5V to V <sub>NN</sub> +225V               |

| V <sub>NN</sub> Negative high voltage supply     | +0.5V to -225V                               |

| Logic input voltages                             | -0.5V to V <sub>DD</sub> +0.3V               |

| V <sub>SIG</sub> Analog signal range             | $V_{_{\mathrm{NN}}}$ to $V_{_{\mathrm{PP}}}$ |

| Peak analog signal current/channel               | 3.0A                                         |

| Storage temperature                              | -65°C to +150°C                              |

| Power dissipation                                | 1.0W                                         |

|                                                  |                                              |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

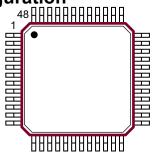

**Pin Configuration**

48-Lead LQFP (FG)

(top view)

#### **Product Marking**

Top Marking

YYWW

HV20822FG

LLLLLLLL

**Bottom Marking**

CCCCCCC

YY = Year Sealed WW = Week Sealed

L = Lot Number

C = Country of Origin\*

A = Assembler ID\*

\_\_\_\_ = "Green" Packaging

\*May be part of top marking

Package may or may not include the following marks: Si or **\$48-Lead LQFP (FG)**

### **Recommended Operating Conditions**

| Sym             | Parameter                                       | Value                                        |

|-----------------|-------------------------------------------------|----------------------------------------------|

| V <sub>PP</sub> | Positive high voltage supply <sup>1</sup>       | +50V to +110V                                |

| V <sub>NN</sub> | Negative high voltage supply <sup>1</sup>       | -10V to V <sub>PP</sub> -220V                |

| V <sub>DD</sub> | Logic power supply voltage <sup>1</sup>         | +4.75V to +12.6V                             |

| V <sub>IH</sub> | High-level input voltage                        | $V_{DD}$ -1.0V to $V_{DD}$                   |

| V <sub>IL</sub> | Low-level input voltage                         | 0V to 1.0V                                   |

| $V_{SIG}$       | Analog signal voltage peak-to-peak <sup>2</sup> | V <sub>NN</sub> +10V to V <sub>PP</sub> -10V |

| T <sub>A</sub>  | Operating free air-temperature                  | 0°C to 70°C                                  |

#### Notes:

- 1. Power up/down sequence is arbitrary except GND must be powered-up first and powered-down last.

- 2.  $V_{SIG}$  must be  $V_{NN} \le V_{SIG} \le V_{PP}$  or floating during power up/down transition.

#### DC Electrical Characteristics (Over recommended operating conditions unless otherwise noted)

|                   | B                                          |     | C    | +25°C |     | +70°C |     |      |       |                                                                             |

|-------------------|--------------------------------------------|-----|------|-------|-----|-------|-----|------|-------|-----------------------------------------------------------------------------|

| Sym               | Parameter                                  | min | max  | min   | typ | max   | min | max  | Units | Conditions                                                                  |

|                   |                                            | -   | 30   | -     | 26  | 32    | -   | 40   |       | $V_{SIG} = 0V, I_{SIG} = 5.0 \text{mA}, V_{PP} = 50V, V_{NN} = -170V$       |

| R <sub>ons</sub>  | Small signal switch                        | -   | 25   | -     | 22  | 27    | -   | 35   | Ω     | $V_{SIG} = 0V, I_{SIG} = 200 \text{mA},$<br>$V_{PP} = 50V, V_{NN} = -170V$  |

| OnS               | on-resistance                              | -   | 25   | -     | 22  | 27    | -   | 30   | 32    | $V_{SIG} = 0V, I_{SIG} = 5.0 \text{mA},$<br>$V_{PP} = 110V, V_{NN} = -110V$ |

|                   |                                            | -   | 20   | -     | 18  | 22    | -   | 25   |       | $V_{SIG} = 0V, I_{SIG} = 200 \text{mA},$<br>$V_{PP} = 110V, V_{NN} = -110V$ |

| ΔR <sub>OnS</sub> | Small signal switch on-resistance matching | -   | 20   | -     | 5.0 | 20    | -   | 20   | %     | $V_{SIG} = 0V, I_{SIG} = 5.0 \text{mA},$<br>$V_{PP} = 110V, V_{NN} = -110V$ |

| R <sub>OnL</sub>  | Large signal switch on-resistance          | -   | -    | -     | 15  | -     | -   | -    | Ω     | V <sub>SIG</sub> = 0V, I <sub>SIG</sub> = 1.0mA                             |

| I <sub>SOL</sub>  | Switch-off leakage per switch              | -   | 5.0  | -     | 1.0 | 10    | -   | 15   | μA    | $V_{SIG} = V_{PP} - 10V$ and $V_{NN} + 10V$                                 |

|                   | DC offset switch-off                       | 300 | _    | _     | 100 | 300   | -   | 300  | mV    | R <sub>L</sub> = 100KΩ                                                      |

| -                 | DC offset switch-on                        | 500 | -    | -     | 100 | 500   | -   | 500  | IIIV  | $R_L = 100 K\Omega$                                                         |

| I <sub>PPQ</sub>  | Pos. HV supply current                     | -   | -    | -     | 10  | 50    | -   | -    |       | All SWs off                                                                 |

| I <sub>NNQ</sub>  | Neg. HV supply current                     | -   | -    | _     | -10 | -50   | -   | _    | μA    | All SVVS OII                                                                |

| I <sub>PPQ</sub>  | Pos. HV supply current                     | -   | -    |       | 10  | 50    | -   | -    | μΑ    | All SWs on 1 = 5.0mA                                                        |

| I <sub>NNQ</sub>  | Neg. HV supply current                     | -   | -    | -     | -10 | -50   | -   | -    |       | All SWs on, I <sub>sw</sub> = 5.0mA                                         |

| -                 | Switch output peak current                 | -   | 3.0  | -     | 3.0 | 2.0   | -   | 2.0  | Α     | V <sub>SIG</sub> duty cycle ≤ 0.1%                                          |

| f <sub>sw</sub>   | Output switch frequency                    | -   | -    | -     | -   | 50    | -   |      | KHz   | Duty cycle = 50%                                                            |

| l <sub>PP</sub>   | I <sub>PP</sub> supply current             | -   | 8.1  | -     | -   | 8.8   | -   | 10   |       | V <sub>PP</sub> = 50V, V <sub>NN</sub> = -170V, all SWs                     |

| I <sub>NN</sub>   | I <sub>NN</sub> supply current             | -   | -8.1 | -     | -   | -8.8  | -   | -10  | mA    | turning on and off at 50KHz                                                 |

| l <sub>PP</sub>   | I <sub>PP</sub> supply current             | -   | 5.0  | -     | -   | 6.3   | -   | 6.9  | IIIA  | V <sub>PP</sub> = 110V, V <sub>NN</sub> = -110V, all SWs                    |

| I <sub>NN</sub>   | I <sub>NN</sub> supply current             | -   | -5.0 | -     | -   | -6.3  | -   | -6.9 |       | turning on and off at 50KHz                                                 |

| I <sub>DDQ</sub>  | Logic supply quiescent current             | -   | 10   | -     | -   | 10    | -   | 10   | μA    | All logic states are at DC                                                  |

| I <sub>DD</sub>   | Logic supply average current               | -   | 2.0  | -     | -   | 2.0   | -   | 2.0  | mA    | $D_{IN}1 = D_{IN}2 = 3.0MHz, \overline{LE} = high$                          |

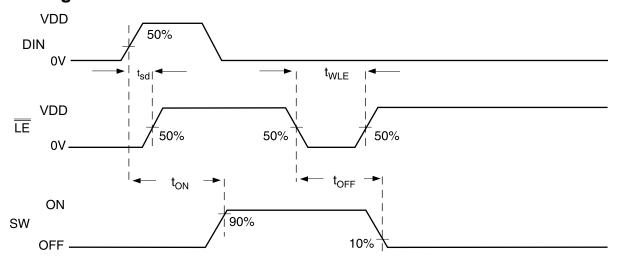

## AC Electrical Characteristics (Over recommended operating conditions unless otherwise noted)

| Sym                   | Parameter                           | 0°C |     | +25°C |     | +70°C |     | Unito | Conditions |            |

|-----------------------|-------------------------------------|-----|-----|-------|-----|-------|-----|-------|------------|------------|

|                       |                                     | min | max | min   | typ | max   | min | max   | Units      | Conditions |

| t <sub>SIG(Off)</sub> | Time to turn off V <sub>SIG</sub> * | 0   | -   | 0     | -   | -     | 0   | -     | ns         |            |

| t <sub>WLE</sub>      | Time width of LE                    | 150 | -   | 150   | _   | -     | 150 | _     | ns         |            |

| t <sub>wdin</sub>     | Time width of D <sub>IN</sub>       | 150 | -   | 150   | -   | -     | 150 | -     | ns         |            |

| t <sub>sD</sub>       | Set up time before LE rises         | 150 | -   | 150   | -   | -     | 150 | -     | ns         |            |

<sup>\*</sup> Time required for analog signal to turn off before output switch turns off.

### AC Electrical Characteristics (cont.)

| Cress               | Baramatar                     | <b>0</b> <sup>c</sup> | C   | +25°C |      | +70°C |     | Units | Canditions |                                                |

|---------------------|-------------------------------|-----------------------|-----|-------|------|-------|-----|-------|------------|------------------------------------------------|

| Sym                 | Parameter                     | min                   | max | min   | typ  | max   | min | max   | Units      | Conditions                                     |

| t <sub>On</sub>     | Turn-on time                  | -                     | 5.0 | -     | -    | 5.0   | -   | 5.0   | μs         | $V_{SIG} = V_{PP} - 10V, R_{LOAD} = 10K\Omega$ |

| t <sub>Off</sub>    | Turn-off time                 | -                     | 5.0 | -     | -    | 5.0   | -   | 5.0   | μs         | $V_{SIG} = V_{PP} - 10V, R_{LOAD} = 10K\Omega$ |

| V                   | Off isolation                 | -30                   | -   | -30   | -33  | -     | -30 | -     | dB         | f = 5.0MHz, 1.0KΩ/15pF Load                    |

| K <sub>o</sub>      | On isolation                  | -45                   | -   | -45   | -50  | -     | -45 | -     | dB         | $f = 7.5MHz, R_{LOAD} = 50\Omega$              |

| K <sub>CR</sub>     | Switch crosstalk              | -45                   | -   | -45   | -    | -     | -45 | -     | dB         | $f = 5.0MHz$ , $R_{LOAD} = 50\Omega$           |

| $C_{GS(Off)}$       | Off-capacitance switch to GND | 5.0                   | 17  | 5.0   | 12   | 17    | 5.0 | 17    | pF         | V <sub>SIG</sub> = 0V, 1.0MHz                  |

| C <sub>GS(On)</sub> | On-capacitance switch to GND  | 25                    | 50  | 25    | 38   | 50    | 25  | 50    | pF         | V <sub>SIG</sub> = 0V, 1.0MHz                  |

| +V <sub>SPK</sub>   | Output voltage enike          | -                     | -   | -     | 4.0  | -     | -   | -     | V          |                                                |

| -V <sub>SPK</sub>   | Output voltage spike          | _                     | -   | -     | -4.0 | -     | -   | -     | V          |                                                |

## **Logic Truth Table**

| D <sub>IN</sub> 2 | D <sub>IN</sub> 1 | LE | SW0 to SW7          | SW8 to SW15 |  |  |  |  |

|-------------------|-------------------|----|---------------------|-------------|--|--|--|--|

| L                 | L                 | L  | Off                 | Off         |  |  |  |  |

| L                 | Н                 | L  | On                  | Off         |  |  |  |  |

| Н                 | L                 | L  | Off                 | On          |  |  |  |  |

| Н                 | Н                 | L  | On                  | On          |  |  |  |  |

| X                 | X                 | Н  | Hold Previous State |             |  |  |  |  |

## **Logic Timing Waveform**

#### **Test Circuits**

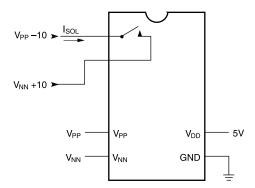

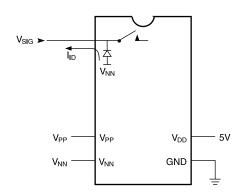

Switch OFF Leakage

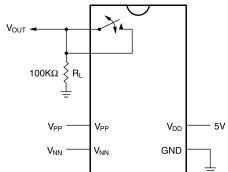

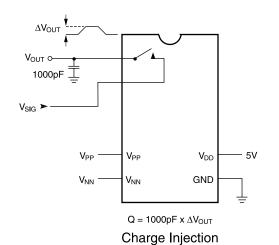

DC Offset ON/OFF

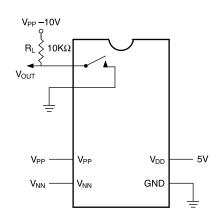

$T_{ON}/T_{OFF}$  Test Circuit

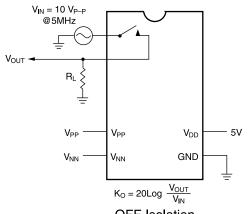

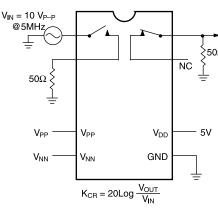

**OFF** Isolation

Isolation Diode Current

Crosstalk

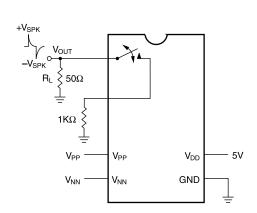

Output Voltage Spike

# **Pin Description**

| Pin # | Function          |

|-------|-------------------|

| 1     | VNN               |

| 2     | N/C               |

| 3     | VPP               |

| 4     | N/C               |

| 5     | D <sub>IN</sub> 1 |

| 6     | ĪĒ                |

| 7     | D <sub>IN</sub> 2 |

| 8     | N/C               |

| 9     | N/C               |

| 10    | VDD               |

| 11    | GND               |

| 12    | N/C               |

| 13    | N/C               |

| 14    | SW15              |

| 15    | SW15              |

| 16    | SW14              |

| 17    | SW14              |

| 18    | SW13              |

| 19    | SW13              |

| 20    | SW12              |

| 21    | SW12              |

| 22    | SW11              |

| 23    | SW11              |

| 24    | N/C               |

| Pin# | Function |

|------|----------|

| 25   | SW10     |

| 26   | SW10     |

| 27   | SW9      |

| 28   | SW9      |

| 29   | SW8      |

| 30   | SW8      |

| 31   | SW7      |

| 32   | SW7      |

| 33   | SW6      |

| 34   | SW6      |

| 35   | SW5      |

| 36   | SW5      |

| 37   | SW4      |

| 38   | N/C      |

| 39   | SW4      |

| 40   | N/C      |

| 41   | SW3      |

| 42   | SW3      |

| 43   | SW2      |

| 44   | SW2      |

| 45   | SW1      |

| 46   | SW1      |

| 47   | SW0      |

| 48   | SW0      |

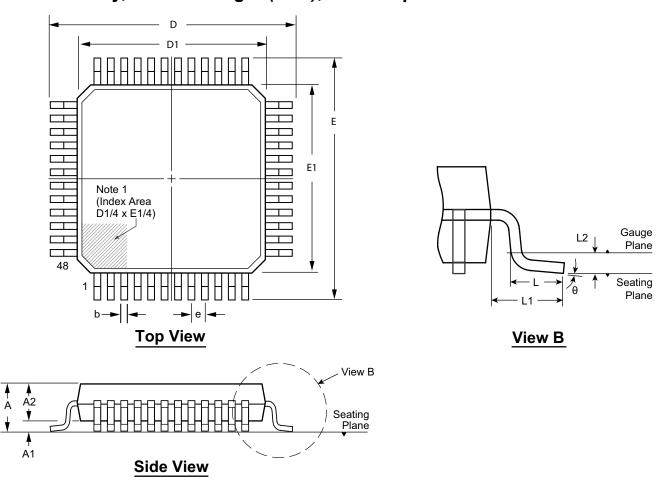

# 48-Lead LQFP Package Outline (FG)

### 7.00x7.00mm body, 1.60mm height (max), 0.50mm pitch

#### Note:

A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo          | ol  | Α     | <b>A</b> 1 | A2   | b    | D     | D1    | E     | E1    | е           | L    | L1          | L2          | θ          |            |

|----------------|-----|-------|------------|------|------|-------|-------|-------|-------|-------------|------|-------------|-------------|------------|------------|

|                | MIN | 1.40* | 0.05       | 1.35 | 0.17 | 8.80* | 6.80* | 8.80* | 6.80* | 0.45        |      |             |             |            | <b>0</b> º |

| Dimension (mm) | NOM | -     | -          | 1.40 | 0.22 | 9.00  | 7.00  | 9.00  | 7.00  | 0.50<br>BSC | 0.60 | 1.00<br>REF | 0.25<br>BSC | 3.5°       |            |

| (11111)        | MAX | 1.60  | 0.15       | 1.45 | 0.27 | 9.20* | 7.20* | 9.20* | 7.20* | 200         | 0.75 |             |             | <b>7</b> ° |            |

JEDEC Registration MS-026, Variation BBC, Issue D, Jan. 2001.

Drawings are not to scale.

Supertex Doc. #: DSPD-48LQFPFG Version, D041309.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http://www.supertex.com.

©2009 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.