## 1. Pinout and Schematic

### 1.1 Pinout Configuration

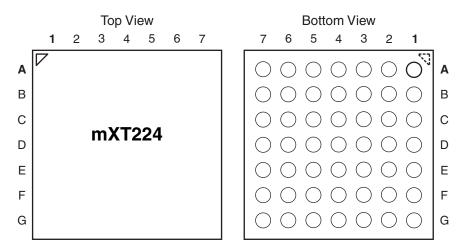

### 1.1.1 49-ball UFBGA/VFBGA

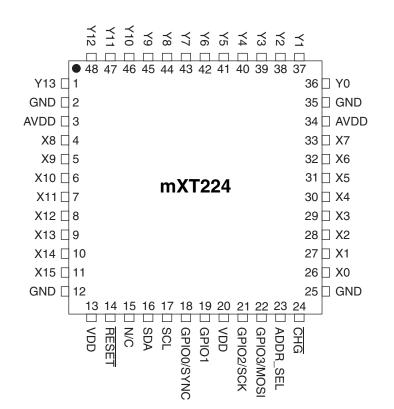

1.1.2 48-pin QFN

mXT224

### 1.2 Pinout Descriptions

### 1.2.1 49-ball UFBGA/VFBGA

Table 1-1.Pin Listing

| Ball | Name  | Туре | Comments                                                                | If Unused, Connect To            |

|------|-------|------|-------------------------------------------------------------------------|----------------------------------|

| A1   | AVDD  | Р    | Analog power                                                            | -                                |

| A2   | Y12   | I/O  | Y line connection or X line in extended mode                            | Leave open                       |

| A3   | Y10   | I/O  | Y line connection or X line in extended mode                            | Leave open                       |

| A4   | Y8    | I    | Y line connection                                                       | Leave open                       |

| A5   | Y6    | I    | Y line connection                                                       | Leave open                       |

| A6   | Y4    | I    | Y line connection                                                       | Leave open                       |

| A7   | Y2    | I    | Y line connection                                                       | Leave open                       |

| B1   | X8    | 0    | X matrix drive line                                                     | Leave open                       |

| B2   | GND   | Р    | Ground                                                                  | -                                |

| B3   | Y11   | I/O  | Y line connection or X line in extended mode                            | Leave open                       |

| B4   | Y9    | I    | Y line connection                                                       | Leave open                       |

| B5   | Y5    | I    | Y line connection                                                       | Leave open                       |

| B6   | Y1    | I    | Y line connection                                                       | Leave open                       |

| B7   | Y0    | I    | Y line connection                                                       | Leave open                       |

| C1   | X10   | 0    | X matrix drive line                                                     | Leave open                       |

| C2   | X9    | 0    | X matrix drive line                                                     | Leave open                       |

| C3   | Y13   | I/O  | Y line connection or X line in extended mode                            | Leave open                       |

| C4   | Y7    | I    | Y line connection                                                       | Leave open                       |

| C5   | Y3    | I    | Y line connection                                                       | Leave open                       |

| C6   | GND   | Р    | Ground                                                                  | -                                |

| C7   | AVDD  | Р    | Analog power                                                            | -                                |

| D1   | X12   | 0    | X matrix drive line                                                     | Leave open                       |

| D2   | X13   | 0    | X matrix drive line                                                     | Leave open                       |

| D3   | X11   | 0    | X matrix drive line                                                     | Leave open                       |

| D4   | GND   | Р    | Ground                                                                  | _                                |

| D5   | X7    | 0    | X matrix drive line                                                     | Leave open                       |

| D6   | X5    | 0    | X matrix drive line                                                     | Leave open                       |

| D7   | X6    | 0    | X matrix drive line                                                     | Leave open                       |

| E1   | X14   | 0    | X matrix drive line                                                     | Leave open                       |

| E2   | X15   | 0    | X matrix drive line                                                     | Leave open                       |

| E3   | RESET | I    | Reset low; has internal 30 k $\Omega$ to 60 k $\Omega$ pull-up resistor | Vdd                              |

| E4   | GPIO1 | I/O  | General purpose I/O                                                     | Input: GND<br>Output: leave open |

#### Pin Listing (Continued) Table 1-1.

| Ball | Name           | Туре | Comments                                        | If Unused, Connect To            |

|------|----------------|------|-------------------------------------------------|----------------------------------|

| E5   | X1             | 0    | X matrix drive line                             | Leave open                       |

| E6   | Х3             | 0    | X matrix drive line                             | Leave open                       |

| E7   | X4             | 0    | X matrix drive line                             | Leave open                       |

| F1   | VDD            | Р    | Digital power                                   | -                                |

| F2   | GND            | Р    | Ground                                          | _                                |

| F3   | SCL            | OD   | Serial Interface Clock                          | _                                |

| F4   | GPIO3/<br>MOSI | I/O  | General purpose I/O /<br>Debug data             | Input: GND<br>Output: leave open |

| F5   | GND            | Р    | Ground                                          | _                                |

| F6   | CHG            | OD   | State change interrupt                          | -                                |

| F7   | X2             | 0    | X matrix drive line                             | Leave open                       |

| G1   | N/C            | _    | No connection                                   | Leave open                       |

| G2   | SDA            | OD   | Serial Interface Data                           | -                                |

| G3   | GPIO0/<br>SYNC | I/O  | General purpose I/O<br>External synchronization | Input: GND<br>Output: leave open |

| G4   | GPIO2/<br>SCK  | I/O  | General purpose I/O /<br>Debug clock            | Input: GND<br>Output: leave open |

| G5   | VDD            | Р    | Digital power                                   | -                                |

| G6   | ADDR_SEL       | I    | I <sup>2</sup> C-compatible address select      | _                                |

| G7   | X0             | 0    | X matrix drive line                             | Leave open                       |

L

Input only Output only, push-pull 0

Ground or power Ρ

I/O

Input and output Open drain output OD

### 1.2.2 48-pin QFN

| Table 1-2.Pin Listing |

|-----------------------|

|-----------------------|

| Pin | Name           | Туре | Comments                                                                | If Unused, Connect To            |

|-----|----------------|------|-------------------------------------------------------------------------|----------------------------------|

| 1   | Y13            | I/O  | Y line connection or X line in extended mode                            | Leave open                       |

| 2   | GND            | Р    | Ground                                                                  | -                                |

| 3   | AVDD           | Р    | Analog power                                                            | -                                |

| 4   | X8             | 0    | X matrix drive line                                                     | Leave open                       |

| 5   | X9             | 0    | X matrix drive line                                                     | Leave open                       |

| 6   | X10            | 0    | X matrix drive line                                                     | Leave open                       |

| 7   | X11            | 0    | X matrix drive line                                                     | Leave open                       |

| 8   | X12            | 0    | X matrix drive line                                                     | Leave open                       |

| 9   | X13            | 0    | X matrix drive line                                                     | Leave open                       |

| 10  | X14            | 0    | X matrix drive line                                                     | Leave open                       |

| 11  | X15            | 0    | X matrix drive line                                                     | Leave open                       |

| 12  | GND            | Р    | Ground                                                                  | -                                |

| 13  | VDD            | Р    | Digital power                                                           | -                                |

| 14  | RESET          | I    | Reset low; has internal 30 k $\Omega$ to 60 k $\Omega$ pull-up resistor | Vdd                              |

| 15  | N/C            | _    | No connection                                                           | Leave open                       |

| 16  | SDA            | OD   | Serial Interface Data                                                   | -                                |

| 17  | SCL            | OD   | Serial Interface Clock                                                  | _                                |

| 18  | GPIO0/<br>SYNC | I/O  | General purpose I/O<br>External synchronization                         | Input: GND<br>Output: leave open |

| 19  | GPIO1          | I/O  | General purpose I/O                                                     | Input: GND<br>Output: leave open |

| 20  | VDD            | Р    | Digital power                                                           | -                                |

| 21  | GPIO2/<br>SCK  | I/O  | General purpose I/O /<br>Debug clock                                    | Input: GND<br>Output: leave open |

| 22  | GPIO3/<br>MOSI | I/O  | General purpose I/O /<br>Debug data                                     | Input: GND<br>Output: leave open |

| 23  | ADDR_SEL       | I    | I <sup>2</sup> C-compatible address select                              | -                                |

| 24  | CHG            | OD   | State change interrupt                                                  | -                                |

| 25  | GND            | Р    | Ground                                                                  | -                                |

| 26  | X0             | 0    | X matrix drive line                                                     | Leave open                       |

| 27  | X1             | 0    | X matrix drive line                                                     | Leave open                       |

| 28  | X2             | 0    | X matrix drive line                                                     | Leave open                       |

| 29  | Х3             | 0    | X matrix drive line                                                     | Leave open                       |

| 30  | X4             | 0    | X matrix drive line                                                     | Leave open                       |

| 31  | X5             | 0    | X matrix drive line                                                     | Leave open                       |

| 32  | X6             | 0    | X matrix drive line                                                     | Leave open                       |

| Pin | Name | Туре | Comments                                     | If Unused, Connect To |

|-----|------|------|----------------------------------------------|-----------------------|

| 33  | X7   | 0    | X matrix drive line                          | Leave open            |

| 34  | AVDD | Р    | Analog power                                 | -                     |

| 35  | GND  | Р    | Ground                                       | _                     |

| 36  | Y0   | I    | Y line connection                            | Leave open            |

| 37  | Y1   | I    | Y line connection                            | Leave open            |

| 38  | Y2   | I    | Y line connection                            | Leave open            |

| 39  | Y3   | I    | Y line connection                            | Leave open            |

| 40  | Y4   | I    | Y line connection                            | Leave open            |

| 41  | Y5   | I    | Y line connection                            | Leave open            |

| 42  | Y6   | I    | Y line connection                            | Leave open            |

| 43  | Y7   | I    | Y line connection                            | Leave open            |

| 44  | Y8   | I    | Y line connection                            | Leave open            |

| 45  | Y9   | I    | Y line connection                            | Leave open            |

| 46  | Y10  | I/O  | Y line connection or X line in extended mode | Leave open            |

| 47  | Y11  | I/O  | Y line connection or X line in extended mode | Leave open            |

| 48  | Y12  | I/O  | Y line connection or X line in extended mode | Leave open            |

I

I/O Input and output

Input only Output only, push-pull Ground or power 0

OD Open drain output

Ρ

6

**mXT224**

### 1.3 Schematic

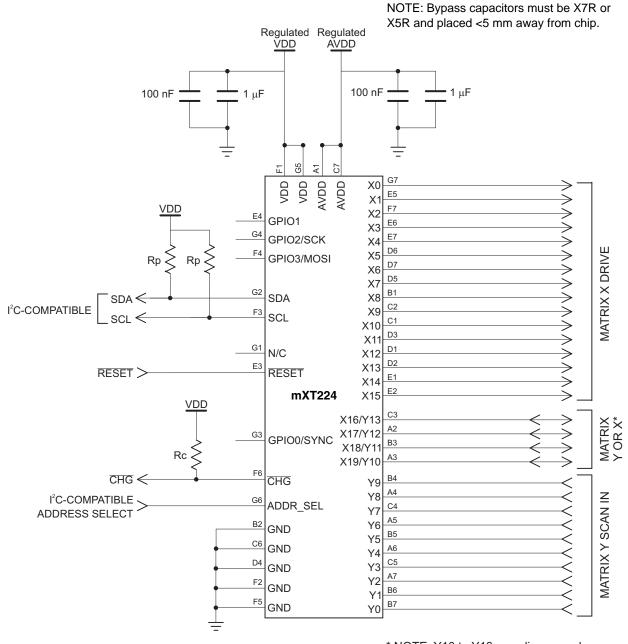

### 1.3.1 49-ball UFBGA/VFBGA

\* NOTE: Y10 to Y13 scan lines may be used as additional X drive lines in extended mode (a  $100\Omega$  resistor must be added to each additional line).

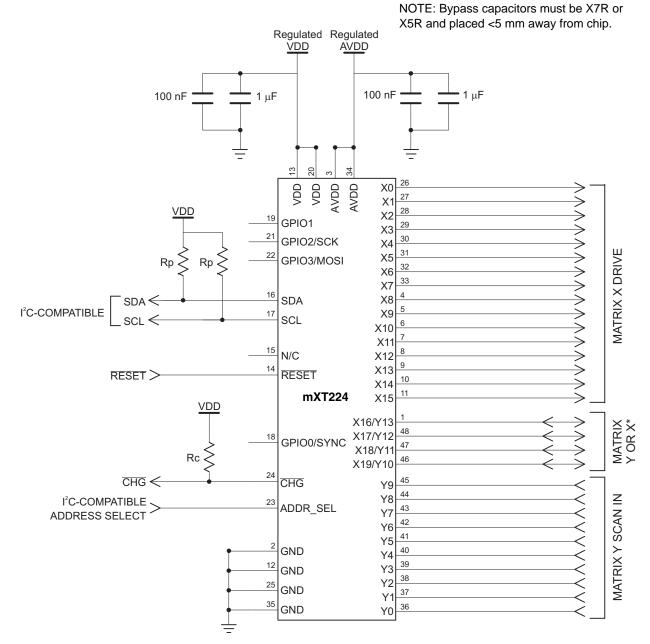

### 1.3.2 48-pin QFN

\* NOTE: Y10 to Y13 scan lines may be used as additional X drive lines in extended mode (a  $100\Omega$  resistor must be added to each additional line).

### 2. Overview of the mXT224

### 2.1 Introduction

The mXT224 uses a unique charge-transfer acquisition engine to implement the QMatrix<sup>T</sup> capacitive sensing method patented by Atmel<sup>®</sup>. This allows the measurement of up to 224 mutual capacitance nodes in under 1 ms. Coupled with a state-of-the-art XMEGA<sup>T</sup> CPU, the entire touchscreen sensing solution can measure, classify and track a single finger touch every 4 ms if required.

The acquisition engine uses an optimal measurement approach to ensure almost complete immunity from parasitic capacitance on the receiver inputs (Y lines). The engine includes sufficient dynamic range to cope with touchscreen mutual capacitances spanning 0.5 pF to 5 pF. This allows great flexibility for use with Atmel's proprietary ITO pattern designs. One and two layer ITO sensors are possible using glass or PET substrates.

The main AVR<sup>®</sup> XMEGA CPU has two powerful, yet low power, microsequencer coprocessors under its control. These combine to allow the signal acquisition, preprocessing, postprocessing and housekeeping to be partitioned in an efficient and flexible way. This gives ample scope for sensing algorithms, touch tracking or advanced shape-based filtering. An in-circuit reflash can be performed over the chip's hardware-driven two-wire interface (I<sup>2</sup>C-compatible).

The mXT224 represents a step improvement over competing technologies. It provides a near optimal mix of low power, small size and low part count with unrivalled true multitouch performance.

# **Revision History**

| Revision Number              | History                               |

|------------------------------|---------------------------------------|

| Revision AS – September 2009 | Initial release for chip revision 1.4 |

| Revision BS – October 2009   | QFN package details added             |

| Revision CS – November 2009  | Updated for chip revision 1.5         |

Notes

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

#### Atmel Asia

Unit 01-05 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369

#### Touch Technology Division

1 Mitchell Point Ensign Way Hamble Southampton Hampshire SO31 4RF United Kingdom Tel: (44) 23-8056-5600 Fax: (44) 23-8045-3939

#### Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Product Contact**

Web Site www.atmel.com Technical Support touch@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTIC-ULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMA-TION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAM-AGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2009 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup>, Adjacent Key Suppression<sup>®</sup> and others are registered trademarks, maXTouch<sup>™</sup>, AKS<sup>™</sup>, QMatrix<sup>™</sup>, XMEGA<sup>™</sup> and others are trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be registered trademarks or trademarks of others.