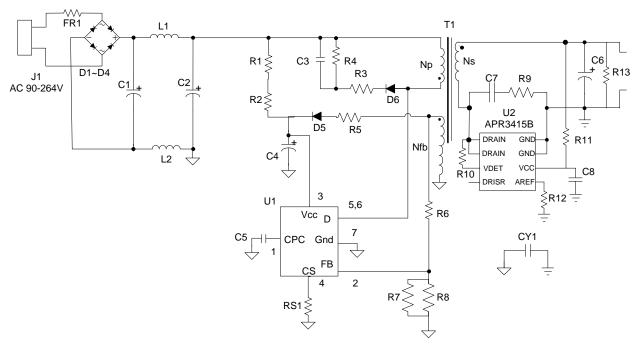

# **Typical Applications Circuit**

Figure 1 Typical Application Circuit of AP3983R

### **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                                                                                                                                                       |  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | CPC      | A capacitor about 50nF should be connected to this pin. The voltage of CPC pin is linear to load of the system and it is used for the functions of cable voltage drop compensation and audio noise suppression |  |

| 2          | FB       | The CV and CC regulation are realized based on the voltage sampling of this pin                                                                                                                                |  |

| 3          | vcc      | The VCC pin supplies the power for the IC. In order to get the correct operation of the IC, a capacitor should be placed as close as possible to the VCC pin                                                   |  |

| 4          | CS       | The CS is the current sense pin of the IC. The IC will turn off the power MOSFET according to the voltage on the CS pin                                                                                        |  |

| 5, 6       | Drain    | High Voltage of MOSFET                                                                                                                                                                                         |  |

| 7          | GND      | The ground of the switcher                                                                                                                                                                                     |  |

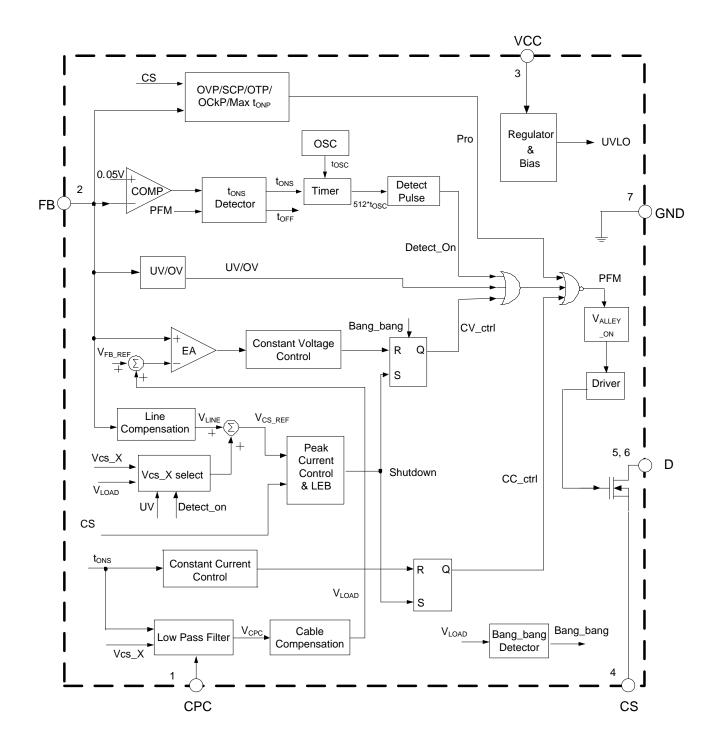

# **Functional Block Diagram**

### **Absolute Maximum Ratings** (Note 4)

| Symbol                             | Parameter                                         | Rating             | Unit |

|------------------------------------|---------------------------------------------------|--------------------|------|

| Vcc                                | Supply Voltage                                    | -0.3 to 35         | V    |

| V <sub>CS</sub> , V <sub>CPC</sub> | Voltage on CS, CPC Pin                            | -0.3 to 7          | V    |

| $V_{FB}$                           | FB Input Voltage                                  | -0.4 to 10         | V    |

| Isource                            | Source Current from OUT Pin                       | Internally Limited | А    |

| TJ                                 | Operating Junction Temperature                    | -40 to +150        | °C   |

| T <sub>STG</sub>                   | Storage Temperature                               | -65 to +150        | °C   |

| BV <sub>DSS</sub>                  | Drain Voltage (T <sub>J</sub> = +25°C)            | 700                | V    |

| I <sub>D</sub>                     | Drain Continuous Current (T <sub>J</sub> = +25°C) | 4                  | А    |

| T <sub>LEAD</sub>                  | Lead Temperature (Soldering, 10 sec)              | +300               | °C   |

| $\theta_{JA}$                      | Thermal Resistance (Junction to Ambient)          | 200                | °C/W |

| LCD                                | ESD (Human Body Model)                            | 2,000              | V    |

| ESD                                | ESD (Charged Device Model)                        | 200                | V    |

Note:

### Electrical Characteristics (@V<sub>CC</sub>=15V, T<sub>A</sub>=+25°C, unless otherwise specified.)

| Symbol                | Parameter                                          | Condition                                              | Min  | Тур  | Max  | Unit |  |  |

|-----------------------|----------------------------------------------------|--------------------------------------------------------|------|------|------|------|--|--|

| STARTUP AND           | STARTUP AND UVLO SECTION                           |                                                        |      |      |      |      |  |  |

| V <sub>TH_ST</sub>    | Startup Threshold                                  | _                                                      | 13   | 15.5 | 18   | V    |  |  |

| V <sub>OPR(MIN)</sub> | Minimal Operating Voltage                          | _                                                      | 6    | 6.8  | 7.6  | V    |  |  |

| STANDBY CUF           | STANDBY CURRENT SECTION                            |                                                        |      |      |      |      |  |  |

| I <sub>ST</sub>       | Startup Current                                    | V <sub>CC</sub> =V <sub>TH_ST</sub> -1V before startup | 0.01 | 0.2  | 0.6  | μΑ   |  |  |

| I <sub>CC_OPR</sub>   | Operating Current                                  | Static current @ no load                               | 300  | 450  | 600  |      |  |  |

| OPERATING F           | OPERATING FREQUENCY SECTION (LL MODE TO FULL LOAD) |                                                        |      |      |      |      |  |  |

| f <sub>S(MAX)</sub>   | Maximum Operating Frequency                        | I <sub>O(MAX)</sub> (Note 5)                           | -    | -    | 80   | kHz  |  |  |

| t <sub>SAMPLE_H</sub> | Comple Time                                        | 37% to 100% I <sub>O(MAX)</sub>                        | 3.8  | 4.2  | 4.6  | μs   |  |  |

| tsample_L             | - Sample Time                                      | 0% to 37% I <sub>O(MAX)</sub> (Note 6)                 | 2.15 | 2.4  | 2.65 | μs   |  |  |

| OPERATING F           | OPERATING FREQUENCY SECTION (LL MODE)              |                                                        |      |      |      |      |  |  |

| V <sub>CPC(EN)</sub>  | CPC Pin Voltage to Enter LL Mode                   | _                                                      | 18   | 20   | 22   | mV   |  |  |

| V <sub>CPC(EX)</sub>  | CPC Pin Voltage to Exit LL Mode                    | _                                                      | 36   | 40   | 44   | mV   |  |  |

| t <sub>OFF(EN)</sub>  | Off Time to Enter LL Mode                          | From the end of tons                                   | 230  | 256  | 282  | μs   |  |  |

| t <sub>OFF(EX)</sub>  | Off Time to Exit LL Mode                           | From the end of tons                                   | 230  | 256  | 282  | μs   |  |  |

<sup>4.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

# **Electrical Characteristics** (continued) ( $@V_{CC} = 15V$ , $T_A = +25$ °C, unless otherwise specified.)

| Symbol                            | Parameter                                    | Condition                            | Min  | Тур  | Max  | Unit |  |

|-----------------------------------|----------------------------------------------|--------------------------------------|------|------|------|------|--|

| FREQUENCY J                       | JITTER                                       |                                      | •    |      |      |      |  |

| ΔV <sub>CS</sub> /V <sub>CS</sub> | V <sub>CS</sub> Modulation                   | 0.50/ 1- 4000/ 1                     | 4.5  | 5    | 5.5  | %    |  |

| f <sub>MOD</sub>                  | V <sub>CS</sub> Modulation Frequency         | 6.5% to 100% I <sub>O(MAX)</sub>     | 3.6  | 4    | 4.4  | kHz  |  |

| CURRENT SEN                       | NSE SECTION                                  |                                      | •    |      |      |      |  |

| Vcs_H                             | Peak Current Sense Threshold                 | 37% to 100% I <sub>O(MAX)</sub>      | 828  | 900  | 972  | mV   |  |

| V <sub>CS_L</sub>                 | Voltage                                      | 0% to 37% I <sub>O(MAX)</sub>        | 460  | 500  | 540  | mV   |  |

| R <sub>LINE</sub>                 | Built-in Line Compensation Resistor          | (Note 7)                             | 245  | 260  | 275  | Ω    |  |

| t <sub>LEB</sub>                  | Leading Edge Blanking                        | (Note 6)                             | 400  | 500  | 600  | ns   |  |

| CONSTANT VO                       | DLTAGE SECTION                               |                                      | •    | •    | •    | •    |  |

| $V_{FB}$                          | Feedback Threshold Voltage                   | Closed loop test of V <sub>OUT</sub> | 3.95 | 4.01 | 4.07 | V    |  |

| R <sub>FB</sub>                   | FB Pin Input Resistance                      | V <sub>FB</sub> = 4V                 | 560  | 700  | 840  | kΩ   |  |

| VCABLE/VOUT                       | Cable Compensation Ratio                     | V <sub>FB</sub> @FULLLOAD-VFB)/VFB   | 7    | 8    | 9    | %    |  |

| CONSTANT CU                       | JRRENT SECTION                               |                                      |      |      |      |      |  |

| t <sub>ONS</sub> /t <sub>SW</sub> | Secondary Winding Conduction Duty            | V <sub>FB</sub> = 4V                 | 0.47 | 0.5  | 0.53 | _    |  |

| VALLEY-ON SI                      | ECTION                                       |                                      |      |      |      |      |  |

| t <sub>VAL-ON</sub>               | Valid Off Time of Valley-on                  | From the end of t <sub>ONS</sub>     | 14.4 | 16   | 17.6 | μs   |  |

| DYNAMIC SEC                       |                                              |                                      |      |      |      |      |  |

| V <sub>TRIGGER</sub>              | Trigger Voltage for Dynamic Function         | _                                    | 74   | 83   | 92   | mV   |  |

| t <sub>DELAY</sub>                | Delay Time for Dynamic Function              | From the end of tons                 | 115  | 128  | 141  | μs   |  |

| V <sub>UV_H</sub>                 | Undervoltage of FB Pin for V <sub>CS_H</sub> | _                                    | 3.82 | 3.89 | 3.96 | V    |  |

| POWER MOSF                        | ET SECTION                                   |                                      |      |      |      |      |  |

| $BV_DSS$                          | Drain-Source Breakdown Voltage               | -                                    | 700  | _    | -    | V    |  |

| R <sub>DS(ON)</sub>               | On State Resistor                            | -                                    | -    | _    | 1.4  | Ω    |  |

| PROTECTION                        | PROTECTION FUNCTION SECTION                  |                                      |      |      |      |      |  |

| V <sub>FB(OVP)</sub>              | Overvoltage Protection at FB Pin             | -                                    | 7.1  | 7.5  | 7.9  | V    |  |

| V <sub>CC(OVP)</sub>              | Overvoltage Protection at VCC Pin            | -                                    | 28   | 30   | 32   | V    |  |

| tonp(max)                         | Maximum Turn-on Time                         | -                                    | 13   | 19   | 25   | μs   |  |

| V <sub>FB(SCP)</sub>              | Short Circuit Protection                     | V <sub>FB</sub> @ Hiccup             | 2.45 | 2.6  | 2.75 | V    |  |

| t <sub>SCP</sub>                  | Maximum Time Under V <sub>FB(SCP)</sub>      | _                                    | 115  | 128  | 141  | ms   |  |

| T <sub>OTP</sub>                  | Shutdown Temperature                         | _                                    | +144 | +160 | +176 | °C   |  |

| T <sub>HYS</sub>                  | Temperature Hysteresis                       | _                                    | +36  | +40  | +44  | °C   |  |

Notes: 5. The output constant-current design value, generally set to 110% to 120% of full load. 6. Guaranteed by design. 7. Line compensation voltage on CS reference:  $\Delta V_{CS\_REF} = 0.438 \times \frac{R_{LINE}}{R_{FB1} + R_{LINE}} \times V_{AUX}$ .

### **Performance Characteristics**

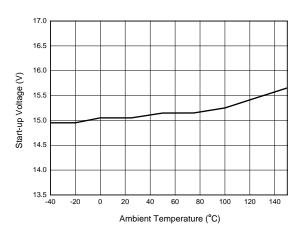

### Start-up Voltage vs. Ambient Temperature

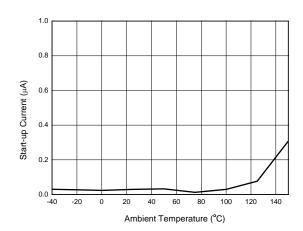

### Start-up Current vs. Ambient Temperature

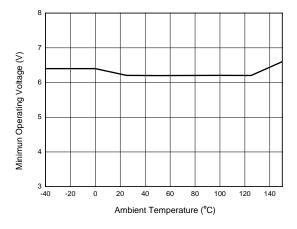

### Minimal Operating Voltage vs. Ambient Temperature

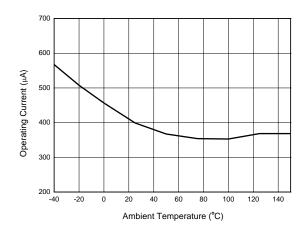

### **Operating Current vs. Ambient Temperature**

### **Performance Characteristics (Cont.)**

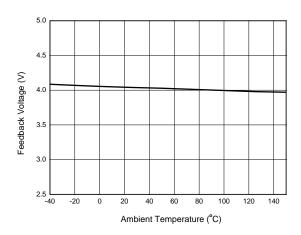

### Feedback Voltage vs. Ambient Temperature

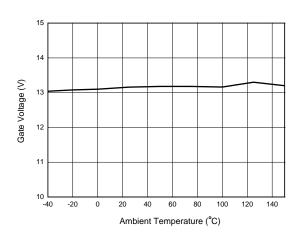

### **Gate Voltage vs. Ambient Temperature**

### **Operation Principle Description**

Figure 1 is the typical application circuit of the AP3983R, which is a conventional flyback converter with a 3-winding transformer--primary winding ( $N_P$ ), secondary winding ( $N_S$ ) and auxiliary winding ( $N_{AUX}$ ). The auxiliary winding is used for providing  $V_{CC}$  supply voltage for IC and sensing the output voltage feedback signal to FB pin.

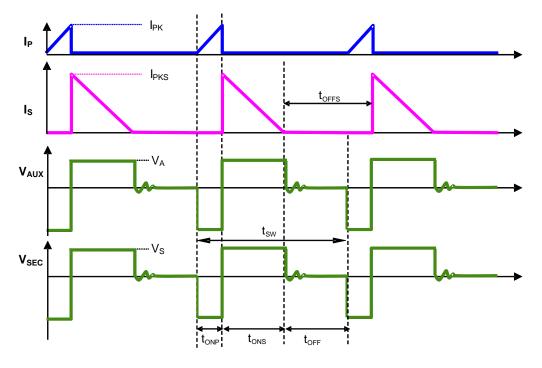

Figure 2 The Operation Waveform of Flyback PSR System

Figure 2 shows the typical waveforms which demonstrate the basic operating principle of the AP3983R application. And the parameters are defined as the following.

Ip---The primary side current

Is --- The secondary side current

IPK---Peak value of primary side current

IPKS---Peak value of secondary side current

Vsec---The transient voltage at secondary winding

Vs---The stable voltage at secondary winding when rectification diode is in conducting status, which equals the sum of output voltage VouT and the forward voltage drop of diode

V<sub>AUX</sub>---The transient voltage at auxiliary winding

V<sub>A</sub>--- The stable voltage at auxiliary winding when rectification diode is in conducting status, which equals the sum of voltage VCC and the forward voltage drop of auxiliary diode

tsw --- The period of switching frequency

tonp --- The conduction time when primary side switch is "ON"

tons --- The conduction time when secondary side diode is "ON"

toff --- The dead time when neither primary side switch nor secondary side diode is "ON"

toffs --- The time when secondary side diode is "OFF"

For primary-side regulation, the primary current ip(t) is sensed by a current sense resistor R<sub>CS</sub> (as shown in Figure 1). The current rises up linearly at a rate of:

$$\frac{dip(t)}{dt} = \frac{\mathbf{V}_{\text{IN}}(t)}{L_{M}} \tag{1}$$

As illustrated in Figure 2, when the current ip(t) rises up to I<sub>PK</sub>, the switch Q1 turns off. The constant peak current is given by:

$$I_{PK} = \frac{V_{CS}}{R_{CS}} \tag{2}$$

The energy stored in the magnetizing inductance  $L_{\text{M}}$  each cycle is therefore:

$$E_G = \frac{1}{2} \times L_M \cdot I_{PK}^2 \tag{3}$$

So the power transferring from the input to the output is given by:

$$P = \frac{1}{2} \times L_M \times I_{PK}^2 \times f_{SW} \tag{4}$$

Where, the f<sub>SW</sub> is the switching frequency. When the peak current I<sub>PK</sub> is constant, the output power depends on the switching frequency f<sub>SW</sub>.

#### **Constant Voltage Operation**

As to constant-voltage (CV) operation mode, the AP3983R detects the auxiliary winding voltage at FB pin to regulate the output voltage. The auxiliary winding voltage is coupled with secondary side winding voltage, so the auxiliary winding voltage at D1 conduction time is:

$$V_{AUX} = \frac{N_{AUX}}{N_S} \times (V_O + V_D) \tag{5}$$

Where V<sub>D</sub> is the diode forward voltage drop.

Downloaded from **Arrow.com**.

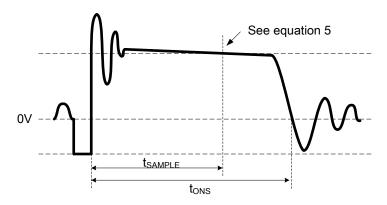

Figure 3 Auxiliary Voltage Waveform

The voltage detection point is at a constant delay time of the D1 on-time. The constant delay time is changed with the different primary peak current. The CV loop control function of the AP3983R then generates a D1 off-time to regulate the output voltage.

#### **Constant Current Operation**

The AP3983R can work in constant-current (CC) mode. Figure 2 shows the secondary current waveforms.

In CC operation mode, the CC control loop of the AP3983R will keep a fixed proportion between D1 on-time tons and D1 off-time toff-time toff-time

$$\frac{t_{ONS}}{t_{OFFS}} = \frac{4}{4} \tag{6}$$

The relationship between the output constant-current and secondary peak current lpks is given by:

$$I_{O(MAX)} = \frac{1}{2} \times I_{PKS} \times \frac{t_{ONS}}{t_{ONS} + t_{OFFS}}$$

(7)

As to tight coupled primary and secondary winding, the secondary peak current is:

$$I_{PKS} = \frac{N_P}{N_S} \times I_{PK} \tag{8}$$

Thus the output constant-current is given by:

$$I_{O(MAX)} = \frac{1}{2} \times \frac{N_P}{N_S} \times I_{PK} \times \frac{t_{ONS}}{t_{ONS} + t_{OFFS}} = \frac{2}{8} \times \frac{N_P}{N_S} \times I_{PK}$$

(9)

Therefore, the AP3983R can realize CC mode operation by constant primary peak current and fixed diode conduction duty cycle.

#### **Multiple Segment Constant Peak Current**

As to the original PFM PSR system, the switching frequency decreases with output current decreasing, which will encounter audible noise issue since switching frequency decreases to audio frequency range, about less than 20kHz.

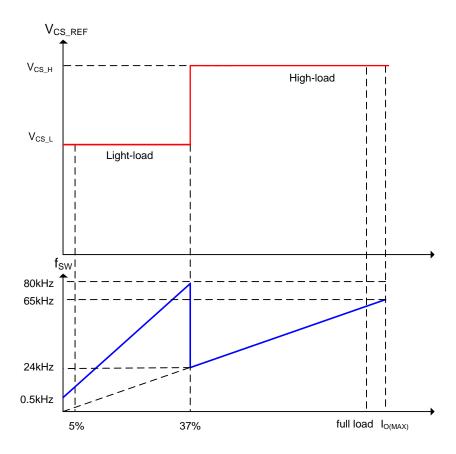

In order to avoid audible noise issue, the AP3983R uses 2-segment constant primary peak current control method. At constant voltage mode, the current sense threshold voltage is of multiple segments with different loading, as shown in Figure 4, which are V<sub>CS\_H</sub> for high load, V<sub>CS\_L</sub> for light load and LL Mode. At constant current mode, the current sense threshold voltage is always V<sub>CS\_H</sub>.

Downloaded from **Arrow.com**.

Figure 4 Multiple Segment Peak Current at CV Mode

It can be seen from Figure 4, with multiple segment peak current control, the AP3983R power system can keep switching frequency above 24kHz at whole heavy load and most of light load to guarantee the audible noise-free performance.

#### Constant Voltage Operation in LL Mode and Dynamic Response

In primary side regulation of the AP3983R application, APR3415 must be used at secondary side as the output voltage regulator, low standby power and excellent dynamic response can be achieved. When the output voltage detected by APR3415 is lower than its trigger voltage, APR3415 outputs periodical signals which will be coupled to auxiliary side. When the AP3983R detects the signal which is valid that the signal voltage is higher than V<sub>TRIGGER</sub> and to<sub>FF</sub> is longer than t<sub>DELAY</sub>, the AP3983R will begin an operating pulse, then primary switch immediately turns on to provide one energy pulse to output terminal and primary V<sub>CC</sub>.

By fast response and cooperation, the APR3415 and AP3983R can maintain a constant output voltage with very low operating frequency in LL mode and also can effectively improve dynamic performance for primary side regulation power systems.

The conditions of entering LL mode---V<sub>CPC</sub><20mV and t<sub>OFF</sub>>256µs.

The condition of exiting LL mode---V<sub>CPC</sub> ≥40mV or t<sub>OFF</sub><256µs.

The critical point of the LL mode is generally about 5%  $I_{O(MAX)}$ .

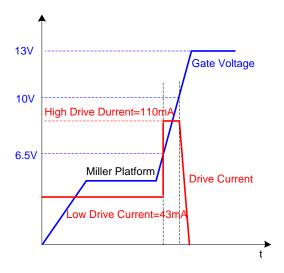

### 3-Segment Drive Current for Radiative EMI Suppression

When the power switch is turned on, a turn-on spike will occur, that worsens the radiative EMI. It is an effective way to decrease drive current before gate voltage gets to miller platform. The AP3983R uses 3-segment drive current for radiative EMI suppression, as shown in Figure 5. When gate voltage gets to 6V, the AP3983R drive current switches from low current (43mA) to high current (110mA). When the gate voltage gets to 10V, the drive current will decrease gradually to 0mA until the gate voltage goes up to the clamp voltage (13V).

Figure 5 Drive Current and Gate Voltage

#### Leading Edge Blanking (LEB) Time

When the power switch is turned on, a turn-on spike will occur on the sense resistor. To avoid false turn off switch, a leading-edge blanking is built in. During this blanking time, the current sense comparator is disabled and the external power switch cannot be turned off.

#### Adjustable Line Compensation and Fixed Cable Compensation

The AP3983R power system can adjust line compensation by changing the upper resistor at FB pin. The line compensation capability is increased by decreasing the resistance of the upper FB resistor.

Cable compensation is fixed in the AP3983R.

#### Valley Turn-On

When the off time (t<sub>OFF</sub>) is lower than 16µs, the AP3983R power system can work with valley turn-on. It can reduce MOSFET switching-on power losses which is resulted from the equivalent output capacitance. At the same time, because of valley turn-on, the switching frequency has the random jitter feature, which will be beneficial for conductive EMI performance. And valley turn-on can also reduce the power switch turn-on spike current and then result in the better radiative EMI performance.

### **Frequency Jitter**

Even though the valley turn-on function can lead the random frequency jitter feature, an active frequency jitter function is added to the AP3983R to ensure the frequency jitter performance in the whole loading condition. By adjusting the  $V_{CS\_REF}$  with deviation of 5.0% every 256 $\mu$ s cycle, the active frequency jitter can be realized.

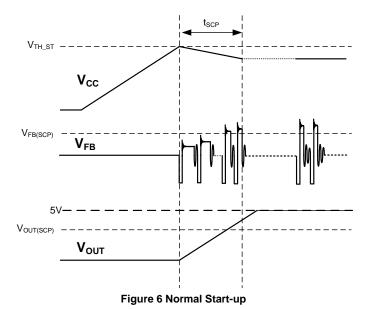

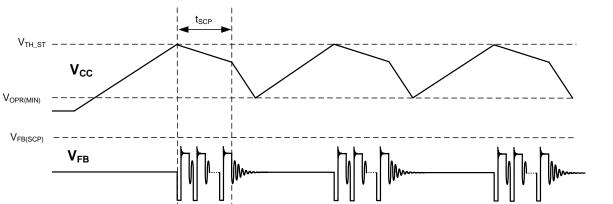

#### **Short Circuit Protection (SCP)**

Short Circuit Protection (SCP) detection principle is similar to the normal output voltage feedback detection by sensing FB pin voltage. When the detected FB pin voltage is below  $V_{FB(SCP)}$  for a duration of about 128ms, the SCP is triggered. Then the AP3983R enters hiccup mode that the IC immediately shuts down and then restarts, so that the  $V_{CC}$  voltage changes between  $V_{TH\_ST}$  and UVLO threshold until  $V_{FB(SCP)}$  condition is removed.

As to the normal system startup, the time duration of FB pin voltage below  $V_{FB(SCP)}$  should be less than  $t_{SCP}$  to avoid entering SCP mode. However, for the output short condition or the output voltage below a certain level, the SCP mode will be triggered.

Figure 6 is the AP3983R normal start-up waveform that the voltage of FB pin is above  $V_{FB(SCP)}$  during  $t_{SCP}$  after  $V_{CC}$  gets to the  $V_{TH\_ST}$ , which doesn't enter the SCP mode. As shown in Figure 7,  $V_{OUT}$  is short and the voltage of FB pin is lower than  $V_{FB(SCP)}$  during  $t_{SCP}$ , the AP3983R triggers the SCP and enter the hiccup mode.

Figure 7 Short Circuit Protection (SCP) and Hiccup Mode

### OVP

The AP3983R includes output overvoltage protection (OVP). If the voltage at FB pin exceeds  $V_{FB(OVP)}$ , the AP3983R immediately shuts down and keeps the internal circuitry enabled to discharge the  $V_{CC}$  capacitor to the UVLO turn-off threshold. After that, the device returns to the start state and a start-up sequence ensues.

#### ОТР

If the junction temperature reaches the threshold of  $+160^{\circ}$ C, the AP3983R shuts down immediately. Before V<sub>CC</sub> voltage decreases to UVLO, if the junction temperature decreases to  $+120^{\circ}$ C, the AP3983R can recover to normal operation. If not, the power system enters restart Hiccup mode until the junction temperature decreases below  $+120^{\circ}$ C.

V<sub>out</sub>

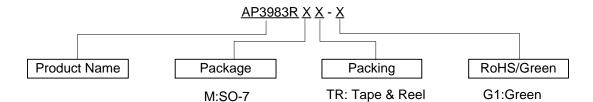

# Ordering Information

| Product | Package | Temperature<br>Range | Cable<br>Compensation<br>Voltage | Part Number   | Marking ID | Packing           |

|---------|---------|----------------------|----------------------------------|---------------|------------|-------------------|

| AP3983R | SO-7    | -40 to +85°C         | 8%                               | AP3983RMTR-G1 | 3983RM-G1  | 4,000/Tape & Reel |

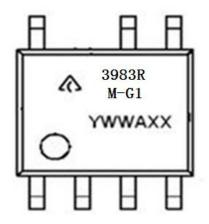

# **Marking Information**

First and Second Lines: Logo and Marking ID

Third Line: Date Code

Y: Year.

WW: Work Week of Molding A: Assembly House Code

XX: 7th and 8th Digits of Batch No

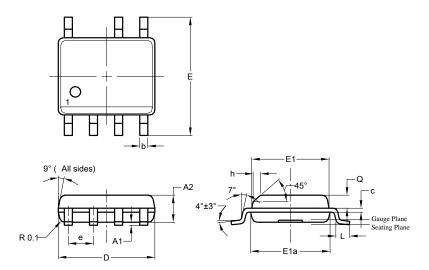

### Package Outline Dimensions (All dimensions in mm. (inch).)

Please see http://www.diodes.com/package-outlines.html for the latest version.

SO-7

| SO-7                 |      |      |      |  |  |

|----------------------|------|------|------|--|--|

| Dim                  | Min  | Max  | Тур  |  |  |

| A2                   | 1.40 | 1.50 | 1.45 |  |  |

| <b>A</b> 1           | 0.10 | 0.20 | 0.15 |  |  |

| b                    | 0.30 | 0.50 | 0.40 |  |  |

| С                    | 0.15 | 0.25 | 0.20 |  |  |

| D                    | 4.85 | 4.95 | 4.90 |  |  |

| Е                    | 5.90 | 6.10 | 6.00 |  |  |

| E1                   | 3.80 | 3.90 | 3.85 |  |  |

| E1a                  | 3.85 | 3.95 | 3.90 |  |  |

| e                    | -    | -    | 1.27 |  |  |

| h                    | -    | -    | 0.35 |  |  |

| ٦                    | 0.62 | 0.82 | 0.72 |  |  |

| Q                    | 0.60 | 0.70 | 0.65 |  |  |

| All Dimensions in mm |      |      |      |  |  |

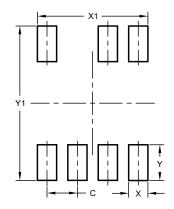

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

SO-7

| Dimensions | Value<br>(in mm) |  |  |

|------------|------------------|--|--|

| С          | 1.270            |  |  |

| Х          | 0.802            |  |  |

| X1         | 4.612            |  |  |

| Y          | 1.505            |  |  |

| V1         | 6 500            |  |  |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com