2

# TABLE OF CONTENTS

| <u>Section</u>                         | <u>Page</u> |

|----------------------------------------|-------------|

| . Product Overview                     | 4           |

| 2. Electrical Specifications           | 4           |

| 3. Typical AM/FM Application Schematic | 15          |

| Bill of Materials                      | 16          |

| 5. Pin Descriptions: Si473x-GM         | 17          |

| 6. Ordering Guide                      | 18          |

| '. Package Outline: Si473x QFN         | 19          |

| B. PCB Land Pattern: Si473x QFN        | 20          |

| Additional Reference Resources         | 22          |

| Contact Information                    | 24          |

#### 1. Product Overview

The Si473x receivers are the industry's first fully-integrated multiband radio receiver ICs from antenna input to audio output. They require minimal external components with no factory alignment. The Si473x receivers reduce the receiver footprint by >90% versus traditional AM/FM solutions. The Si473x also offer best-in-class performance with the most features. The high integration and complete system production test simplifies design-in, increases system quality, and improves manufacturability.

The Si473x receivers include advanced seek algorithms, adjustable soft mute, auto-calibrated digital tuning, and FM stereo processing. In addition, the Si473x ICs provide a programmable reference clock and an I2C-compatible 2-wire control interface.

The Si4731/35/37/39 incorporates a digital processor for the European Radio Data System (RDS) and the North American Radio Broadcast Data System (RBDS), including all required symbol decoding, block synchronization, error detection, and error correction functions. Using these features, the Si4731/35/37/39 enables broadcast data such as station identification and song name to be displayed to the end user.

## 2. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                                | Symbol              | Test Condition | Min | Тур | Max | Unit |

|------------------------------------------|---------------------|----------------|-----|-----|-----|------|

| Supply Voltage                           | V <sub>DD</sub>     |                | 2.7 | _   | 5.5 | V    |

| Interface Supply Voltage                 | V <sub>IO</sub>     |                | 1.5 | _   | 3.6 | V    |

| Power Supply Powerup Rise Time           | V <sub>DDRISE</sub> |                | 10  | _   | _   | μs   |

| Interface Power Supply Powerup Rise Time | V <sub>IORISE</sub> |                | 10  | _   | _   | μs   |

| Ambient Temperature                      | T <sub>A</sub>      |                | -20 | 25  | 85  | °C   |

**Note:** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at V<sub>DD</sub> = 3.3 V and 25 °C unless otherwise stated. Parameters are tested in production unless otherwise stated.

Table 2. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                   | Symbol           | Value                           | Unit            |

|-----------------------------|------------------|---------------------------------|-----------------|

| Supply Voltage              | V <sub>DD</sub>  | -0.5 to 5.8                     | V               |

| Interface Supply Voltage    | V <sub>IO</sub>  | -0.5 to 3.9                     | V               |

| Input Current <sup>3</sup>  | I <sub>IN</sub>  | 10                              | mA              |

| Input Voltage <sup>3</sup>  | V <sub>IN</sub>  | -0.3 to (V <sub>IO</sub> + 0.3) | V               |

| Operating Temperature       | T <sub>OP</sub>  | -40 to 95                       | °C              |

| Storage Temperature         | T <sub>STG</sub> | -55 to 150                      | °C              |

| RF Input Level <sup>4</sup> |                  | 0.4                             | V <sub>PK</sub> |

#### Notes:

- 1. Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure beyond recommended operating conditions for extended periods may affect device reliability.

- 2. The Si473x devices are high-performance RF integrated circuits with certain pins having an ESD rating of < 2 kV HBM. Handling and assembly of these devices should only be done at ESD-protected workstations.

- 3. For input pins SCLK, SEN, SDIO, RST, RCLK, DCLK, DFS, GPO1, GPO2, and GPO3.

- 4. At RF input pins, FMI and AMI.

**Table 3. DC Characteristics**

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C)

| Parameter                              | Symbol            | Test Condition                                      | Min                   | Тур  | Max                   | Unit |

|----------------------------------------|-------------------|-----------------------------------------------------|-----------------------|------|-----------------------|------|

| FM Mode                                | •                 |                                                     | •                     |      |                       |      |

| Supply Current                         | I <sub>FM</sub>   |                                                     | _                     | 19.2 | 22                    | mA   |

| Supply Current <sup>1</sup>            | I <sub>FM</sub>   | Low SNR level                                       | _                     | 19.8 | 23                    | mA   |

| RDS Supply Current <sup>2</sup>        | I <sub>FM</sub>   |                                                     | _                     | 19.9 | 23                    | mA   |

| WB Mode (Si4736/37/38/39 on            | y)                |                                                     |                       |      |                       |      |

| Supply Current                         | I <sub>FM</sub>   |                                                     | _                     | 19.2 | 22                    | mA   |

| Supply Current <sup>1</sup>            | I <sub>FM</sub>   | Low SNR level                                       | _                     | 19.8 | 23                    | mA   |

| AM Mode (Si4730/31/34/35/36/           | 37 only)          |                                                     |                       |      |                       |      |

| Supply Current                         | I <sub>AM</sub>   |                                                     | _                     | 17.3 | 20.5                  | mA   |

| Supplies and Interface                 | •                 |                                                     |                       |      |                       |      |

| Interface Supply Current               | I <sub>IO</sub>   |                                                     | _                     | 320  | 600                   | μΑ   |

| V <sub>DD</sub> Powerdown Current      | I <sub>DDPD</sub> |                                                     | _                     | 10   | 20                    | μΑ   |

| V <sub>IO</sub> Powerdown Current      | I <sub>IOPD</sub> | SCLK, RCLK inactive                                 | _                     | 1    | 10                    | μA   |

| High Level Input Voltage <sup>3</sup>  | V <sub>IH</sub>   |                                                     | 0.7 x V <sub>IO</sub> | _    | V <sub>IO</sub> + 0.3 | V    |

| Low Level Input Voltage <sup>3</sup>   | V <sub>IL</sub>   |                                                     | -0.3                  | _    | 0.3 x V <sub>IO</sub> | V    |

| High Level Input Current <sup>3</sup>  | I <sub>IH</sub>   | $V_{IN} = V_{IO} = 3.6 \text{ V}$                   | -10                   | _    | 10                    | μΑ   |

| Low Level Input Current <sup>3</sup>   | I <sub>IL</sub>   | $V_{IN} = 0 \text{ V},$<br>$V_{IO} = 3.6 \text{ V}$ | -10                   | _    | 10                    | μΑ   |

| High Level Output Voltage <sup>4</sup> | V <sub>OH</sub>   | I <sub>OUT</sub> = 500 μA                           | 0.8 x V <sub>IO</sub> | _    | _                     | V    |

| Low Level Output Voltage <sup>4</sup>  | V <sub>OL</sub>   | I <sub>OUT</sub> = -500 μA                          | _                     | _    | 0.2 x V <sub>IO</sub> | V    |

#### Notes:

- 1. LNA is automatically switched to higher current mode for optimum sensitivity in weak signal conditions.

- 2. Specifications are guaranteed by characterization.

- 3. For input pins SCLK, SEN, SDIO, RST, RCLK, DCLK, and DFS.

- 4. For output pins SDIO, DOUT, GPO1, GPO2, and GPO3.

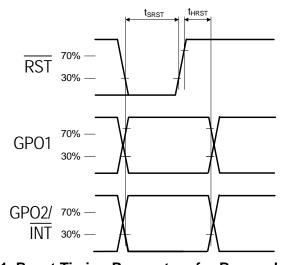

## Table 4. Reset Timing Characteristics 1,2

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                                         | Symbol            | Min | Тур | Max | Unit |

|---------------------------------------------------|-------------------|-----|-----|-----|------|

| RST Pulse Width and GPO1, GPO2/INT Setup to RST↑3 | t <sub>SRST</sub> | 100 | _   | _   | μs   |

| GPO1, GPO2/INT Hold from RST↑                     | t <sub>HRST</sub> | 30  | -   | -   | ns   |

#### **Important Notes:**

- 1. When selecting 2-wire mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

- 2. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of RST, and stays high until after the first start condition.

- 3. If GPO1 and GPO2 are actively driven by the user, then minimum  $t_{SRST}$  is only 30 ns. If GPO1 or GPO2 is hi-Z, then minimum  $t_{SRST}$  is 100  $\mu$ s to provide time for on-chip 1 M $\Omega$  devices (active while  $\overline{RST}$  is low) to pull GPO1 high and GPO2 low.

Figure 1. Reset Timing Parameters for Busmode Select

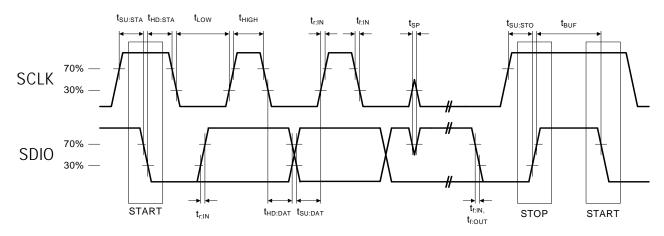

Table 5. 2-Wire Control Interface Characteristics 1,2,3

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C)

| Parameter                                | Symbol                                 | Test Condition | Min                         | Тур | Max | Unit |

|------------------------------------------|----------------------------------------|----------------|-----------------------------|-----|-----|------|

| SCLK Frequency                           | f <sub>SCL</sub>                       |                | 0                           | _   | 400 | kHz  |

| SCLK Low Time                            | t <sub>LOW</sub>                       |                | 1.3                         | _   | _   | μs   |

| SCLK High Time                           | t <sub>HIGH</sub>                      |                | 0.6                         | _   | _   | μs   |

| SCLK Input to SDIO ↓ Setup<br>(START)    | t <sub>SU:STA</sub>                    |                | 0.6                         | _   | _   | μs   |

| SCLK Input to SDIO ↓ Hold (START)        | t <sub>HD:STA</sub>                    |                | 0.6                         | _   | _   | μs   |

| SDIO Input to SCLK ↑ Setup               | t <sub>SU:DAT</sub>                    |                | 100                         | _   | _   | ns   |

| SDIO Input to SCLK ↓ Hold <sup>4,5</sup> | t <sub>HD:DAT</sub>                    |                | 0                           | _   | 900 | ns   |

| SCLK input to SDIO ↑ Setup<br>(STOP)     | t <sub>SU:STO</sub>                    |                | 0.6                         | _   | _   | μs   |

| STOP to START Time                       | t <sub>BUF</sub>                       |                | 1.3                         | _   | _   | μs   |

| SDIO Output Fall Time                    | t <sub>f:OUT</sub>                     |                | 20 + 0.1 C <sub>b</sub> 1pF | _   | 250 | ns   |

| SDIO Input, SCLK Rise/Fall Time          | t <sub>f:IN</sub><br>t <sub>r:IN</sub> |                | $20 + 0.1 \frac{C_b}{1pF}$  | _   | 300 | ns   |

| SCLK, SDIO Capacitive Loading            | C <sub>b</sub>                         |                | _                           | _   | 50  | pF   |

| Input Filter Pulse Suppression           | t <sub>SP</sub>                        |                | _                           |     | 50  | ns   |

#### Notes:

- 1. When  $V_{IO} = 0$  V, SCLK and SDIO are low impedance.

- 2. When selecting 2-wire mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

- 3. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of RST, and stays high until after the first start condition.

- The Si473x delays SDIO by a minimum of 300 ns from the V<sub>IH</sub> threshold of SCLK to comply with the minimum t<sub>HD:DAT</sub> specification.

- 5. The maximum  $t_{\text{HD:DAT}}$  has only to be met when  $f_{\text{SCL}} = 400$  kHz. At frequencies below 400 KHz,  $t_{\text{HD:DAT}}$  may be violated as long as all other timing parameters are met.

Figure 2. 2-Wire Control Interface Read and Write Timing Parameters

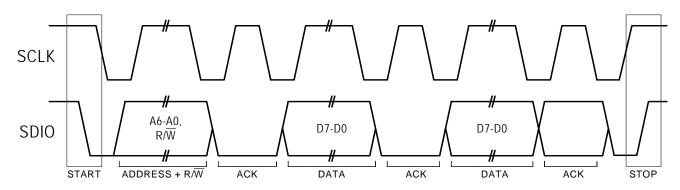

Figure 3. 2-Wire Control Interface Read and Write Timing Diagram

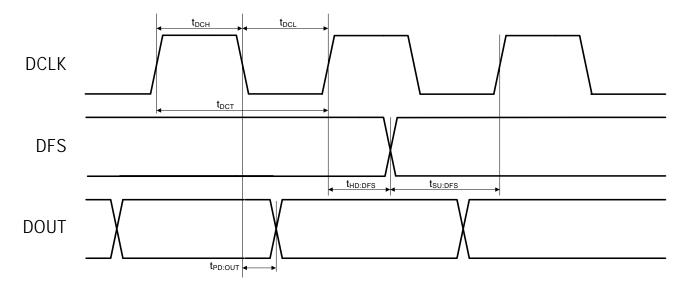

### **Table 6. Digital Audio Interface Characteristics**

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                                     | Symbol               | Test Condition | Min | Тур | Max  | Unit |

|-----------------------------------------------|----------------------|----------------|-----|-----|------|------|

| DCLK Cycle Time                               | t <sub>DCT</sub>     |                | 26  | _   | 1000 | ns   |

| DCLK Pulse Width High                         | t <sub>DCH</sub>     |                | 10  | _   |      | ns   |

| DCLK Pulse Width Low                          | t <sub>DCL</sub>     |                | 10  | _   |      | ns   |

| DFS Set-up Time to DCLK Rising Edge           | t <sub>SU:DFS</sub>  |                | 5   | _   |      | ns   |

| DFS Hold Time from DCLK Rising Edge           | t <sub>HD:DFS</sub>  |                | 5   | _   |      | ns   |

| DOUT Propagation Delay from DCLK Falling Edge | t <sub>PD:DOUT</sub> |                | 0   | _   | 12   | ns   |

Figure 4. Digital Audio Interface Timing Parameters, I<sup>2</sup>S Mode

Table 7. FM Receiver Characteristics 1,2

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C)

| Parameter                                               | Symbol          | Test Condition                            | Min | Тур | Max | Unit     |

|---------------------------------------------------------|-----------------|-------------------------------------------|-----|-----|-----|----------|

| Input Frequency                                         | f <sub>RF</sub> |                                           | 76  | _   | 108 | MHz      |

| Sensitivity with Headphone<br>Network <sup>3,4,5</sup>  |                 | (S+N)/N = 26  dB                          | _   | 2.2 | 3.5 | μV EMF   |

| Sensitivity with 50 $\Omega$ Network <sup>3,4,5,6</sup> |                 | (S+N)/N = 26 dB                           | _   | 1.1 | _   | μV EMF   |

| RDS Sensitivity <sup>6</sup>                            |                 | $\Delta f = 2 \text{ kHz},$ RDS BLER < 5% | _   | 15  | _   | μV EMF   |

| LNA Input Resistance <sup>6,7</sup>                     |                 |                                           | 3   | 4   | 5   | kΩ       |

| LNA Input Capacitance <sup>6,7</sup>                    |                 |                                           | 4   | 5   | 6   | pF       |

| Input IP3 <sup>6,8</sup>                                |                 |                                           | 100 | 105 | _   | dBµV EMF |

| AM Suppression <sup>3,4,6,7</sup>                       |                 | m = 0.3                                   | 40  | 50  | _   | dB       |

| Adjacent Channel Selectivity                            |                 | ±200 kHz                                  | 35  | 50  | _   | dB       |

| Alternate Channel Selectivity                           |                 | ±400 kHz                                  | 60  | 70  | _   | dB       |

| Spurious Response Rejection <sup>6</sup>                |                 | In-band                                   | 35  | _   | _   | dB       |

| Audio Output Voltage <sup>3,4,7</sup>                   |                 |                                           | 72  | 80  | 90  | $mV_RMS$ |

| Audio Output L/R Imbalance <sup>3,7,9</sup>             |                 |                                           | _   | _   | 1   | dB       |

| Audio Frequency Response Low <sup>6</sup>               |                 | −3 dB                                     | _   | _   | 30  | Hz       |

| Audio Frequency Response High <sup>6</sup>              |                 | −3 dB                                     | 15  | _   | _   | kHz      |

| Audio Stereo Separation <sup>7,9</sup>                  |                 |                                           | 25  | _   | _   | dB       |

| Audio Mono S/N <sup>3,4,5,7,10</sup>                    |                 |                                           | 55  | 63  | _   | dB       |

| Audio Stereo S/N <sup>4,5,7,10,11</sup>                 |                 |                                           | _   | 58  | _   | dB       |

| Audio THD <sup>3,7,9</sup>                              |                 |                                           | _   | 0.1 | 0.5 | %        |

| De-emphasis Time Constant <sup>6</sup>                  |                 | FM_DEEMPHASIS = 2                         | 70  | 75  | 80  | μs       |

|                                                         |                 | FM_DEEMPHASIS = 1                         | 45  | 50  | 54  | μs       |

| Audio Output Load Resistance <sup>6,10</sup>            | $R_L$           | Single-ended                              | 10  | _   | _   | kΩ       |

| Audio Output Load Capacitance <sup>6,10</sup>           | C <sub>L</sub>  | Single-ended                              | _   | _   | 50  | pF       |

- 1. Additional testing information is available in "AN388: Si470x/1x/2x/3x/4x Evaluation Test Board Procedure." Volume = maximum for all tests. Tested at RF = 98.1 MHz.

- 2. To ensure proper operation and receiver performance, follow the guidelines in "AN383: Si47xx Antenna, Schematic, Layout and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 3.  $F_{MOD} = 1 \text{ kHz}$ , 75  $\mu$ s de-emphasis, MONO = enabled, and L = R unless noted otherwise.

- **4.**  $\Delta f = 22.5 \text{ kHz}.$

- **5.**  $B_{AF} = 300 \text{ Hz to } 15 \text{ kHz}, \text{ A-weighted}.$

- **6.** Guaranteed by characterization.

- **7.**  $V_{EMF} = 1 \text{ mV}.$

- **8.**  $|f_2 f_1| > 2$  MHz,  $f_0 = 2 \times f_1 f_2$ . AGC is disabled. **9.**  $\Delta f = 75$  kHz.

- 10. At  $L_{OUT}$  and  $R_{OUT}$  pins.

- **11.** Analog audio output mode.

- 12. At temperature (25°C).

11

## Table 7. FM Receiver Characteristics<sup>1,2</sup> (Continued)

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                   | Symbol | Test Condition                               | Min | Тур | Max | Unit       |

|-----------------------------|--------|----------------------------------------------|-----|-----|-----|------------|

| Seek/Tune Time <sup>6</sup> |        | RCLK tolerance<br>= 100 ppm                  | _   | _   | 80  | ms/channel |

| Powerup Time <sup>6</sup>   |        | From powerdown                               | _   | _   | 110 | ms         |

| RSSI Offset <sup>12</sup>   |        | Input levels of 8 and<br>60 dBµV at RF Input | -3  | _   | 3   | dB         |

#### Notes:

- 1. Additional testing information is available in "AN388: Si470x/1x/2x/3x/4x Evaluation Test Board Procedure." Volume = maximum for all tests. Tested at RF = 98.1 MHz.

- **2.** To ensure proper operation and receiver performance, follow the guidelines in "AN383: Si47xx Antenna, Schematic, Layout and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 3.  $F_{MOD}$  = 1 kHz, 75  $\mu$ s de-emphasis, MONO = enabled, and L = R unless noted otherwise.

- **4.**  $\Delta f = 22.5 \text{ kHz}.$

- **5.**  $B_{AF} = 300 \text{ Hz}$  to 15 kHz, A-weighted.

- **6.** Guaranteed by characterization.

- **7.**  $V_{EMF} = 1 \text{ mV}.$

- **8.**  $|f_2 f_1| > 2$  MHz,  $f_0 = 2 \times f_1 f_2$ . AGC is disabled.

- **9.**  $\Delta f = 75 \text{ kHz}.$

- **10.** At  $L_{OUT}$  and  $R_{OUT}$  pins.

- 11. Analog audio output mode.

- 12. At temperature (25°C).

### Table 8. AM/SW/LW Receiver Characteristics<sup>1</sup>

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V, TA = –20 to 85 °C)

| Parameter                                    | Symbol   | Test Condition                                         | Min | Тур  | Max   | Unit                 |

|----------------------------------------------|----------|--------------------------------------------------------|-----|------|-------|----------------------|

|                                              |          | Long Wave (LW)                                         | 153 | _    | 279   | kHz                  |

| Input Frequency                              | $f_{RF}$ | Medium Wave (AM)                                       | 520 | _    | 1710  | kHz                  |

|                                              |          | Short Wave (SW)                                        | 2.3 | _    | 21.85 | MHz                  |

| Sensitivity <sup>2,3,4,5,6</sup>             |          | (S+N)/N = 26 dB                                        | _   | 25   | 35    | μV EMF               |

| Large Signal Voltage Handling <sup>5,7</sup> |          | THD < 8%                                               | _   | 300  | _     | $mV_RMS$             |

| Power Supply Rejection Ratio                 |          | $\Delta V_{DD} = 100 \text{ mV}_{RMS}, 100 \text{ Hz}$ | _   | 40   | _     | dB                   |

| Audio Output Voltage <sup>2,8</sup>          |          |                                                        | 54  | 60   | 67    | ${\sf mV}_{\sf RMS}$ |

| Audio S/N <sup>2,3,4,6,8</sup>               |          |                                                        | 50  | 56   | _     | dB                   |

| Audio THD <sup>2,4,8</sup>                   |          |                                                        | _   | 0.1  | 0.5   | %                    |

| Antonna Industance                           |          | Long Wave (LW)                                         | _   | 2800 | _     |                      |

| Antenna Inductance                           |          | Medium Wave (AM)                                       | 180 | _    | 450   | μH                   |

| Powerup Time                                 |          | From powerdown                                         | _   |      | 110   | ms                   |

#### Notes:

- 1. To ensure proper operation and receiver performance, follow the guidelines in "AN383: Si47xx Antenna, Schematic, Layout and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 2. FMOD = 1 kHz, 30% modulation, A-weighted, 2 kHz channel filter.

- 3.  $B_{AF} = 300 \text{ Hz to } 15 \text{ kHz}, \text{ A-weighted}.$

- **4.**  $f_{RF} = 1000 \text{ kHz}$ ,  $\Delta f = 10 \text{ kHz}$ .

- **5.** Guaranteed by characterization.

- 6. Analog audio output mode.

- 7. See "AN388: Si470X/1X/2X/3X/4X Evaluation Board Test Procedure" for evaluation method.

- **8.**  $V_{IN} = 5 \text{ mVrms}.$

- 9. Stray capacitance on antenna and board must be < 10 pF to achieve full tuning range at higher inductance levels.

### Table 9. WB Receiver Characteristics<sup>1</sup>

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ VIO} = 1.5 \text{ to } 3.6 \text{V}, \text{ T}_{A} = 25 \text{ °C})$

| Parameter                                  | Symbol         | Test Condition | Min   | Тур | Max    | Unit   |

|--------------------------------------------|----------------|----------------|-------|-----|--------|--------|

| Input Frequency                            | f <sub>R</sub> |                | 162.4 | _   | 162.55 | MHz    |

| Sensitivity <sup>2,3</sup>                 |                | SINAD = 12 dB  | _     | 0.9 | _      | μV EMF |

| Adjacent Channel Selectivity               |                | ±25 kHz        | _     | 52  | _      | dB     |

| Audio S/N <sup>2,3,4,5</sup>               |                | Mono           | _     | 45  | _      | dB     |

| Audio Frequency Response Low <sup>6</sup>  |                | −3 dB          | _     | _   | 300    | Hz     |

| Audio Frequency Response High <sup>6</sup> |                | −3 dB          | 3     | _   | _      | kHz    |

#### Notes:

- 1. To ensure proper operation and receiver performance, follow the guidelines in "AN383: Si47xx Antenna, Schematic, Layout and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- **2.**  $F_{MOD} = 1 \text{ kHz}.$

- 3.  $\Delta f = 3 \text{ kHz}.$

- **4.**  $V_{EMF} = 1 \text{ mV}.$

- 5. A-weighted.

- 6. Guaranteed by characterization

#### **Table 10. Reference Clock and Crystal Characteristics**

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                                | Symbol | Test Condition    | Min    | Тур    | Max    | Unit |  |  |  |  |

|------------------------------------------|--------|-------------------|--------|--------|--------|------|--|--|--|--|

| Reference Clock                          |        |                   |        |        |        |      |  |  |  |  |

| RCLK Supported Frequencies <sup>1</sup>  |        |                   | 31.130 | 32.768 | 40,000 | kHz  |  |  |  |  |

| RCLK Frequency Tolerance <sup>2</sup>    |        |                   | -100   | _      | 100    | ppm  |  |  |  |  |

| REFCLK_PRESCALE                          |        |                   | 1      | _      | 4095   |      |  |  |  |  |

| REFCLK                                   |        |                   | 31.130 | 32.768 | 34.406 | kHz  |  |  |  |  |

|                                          | С      | rystal Oscillator |        |        |        |      |  |  |  |  |

| Crystal Oscillator Frequency             |        |                   | _      | 32.768 | _      | kHz  |  |  |  |  |

| Crystal Frequency Tolerance <sup>2</sup> |        |                   | -50    | _      | 50     | ppm  |  |  |  |  |

| Board Capacitance                        |        |                   | _      | _      | 3.5    | pF   |  |  |  |  |

#### Notes:

- 1. The Si473x divides the RCLK input by REFCLK\_PRESCALE to obtain REFCLK. There are some RCLK frequencies between 31.130 kHz and 40 MHz that are not supported. See "AN332: Si47xx Programming Guide," Table 6 for more details.

- 2. A frequency tolerance of ±50 ppm is required for FM seek/tune using 50 kHz channel spacing, SW seek/tune, and WB tune.

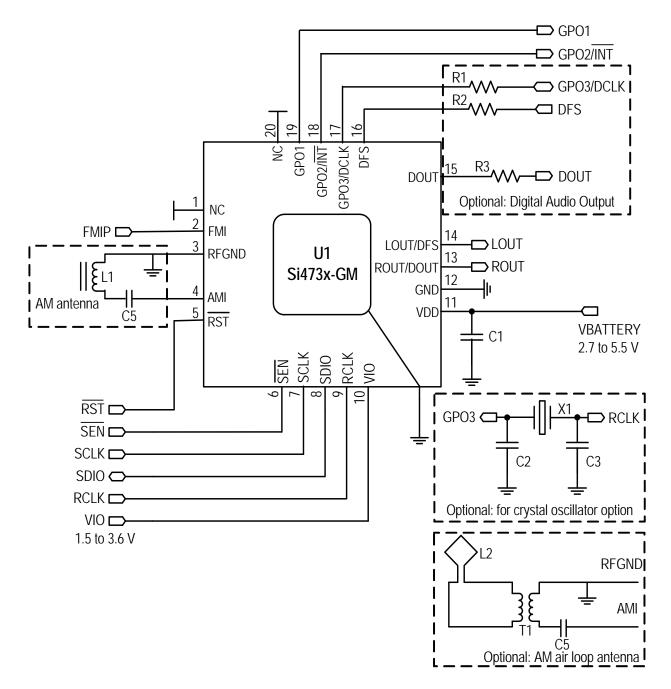

## 3. Typical AM/FM Application Schematic

#### Notes:

- 1. Place C1 close to V<sub>DD</sub> pin.

- 2. All grounds connect directly to GND plane on PCB.

- 3. Pins 1 and 20 are no connects, leave floating.

- **4.** To ensure proper operation and receiver performance, follow the guidelines in "AN383: Si47xx Antenna, Schematic, Layout and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 5. Pin 2 connects to the FM antenna interface and pin 4 connects to the AM antenna interface.

- 6. RFGND should be locally isolated from GND.

- 7. Place Si473x as close as possible to antenna jack and keep the FMI and AMI traces as short as possible.

## Si473x-B20

## 4. Bill of Materials

| Component(s) | Value/Description                                                                  | Supplier             |  |  |

|--------------|------------------------------------------------------------------------------------|----------------------|--|--|

| C1           | Supply bypass capacitor, 22 nF, ±20%, Z5U/X7R                                      | Murata               |  |  |

| C5           | Coupling capacitor, 0.47 µF, ±20%, Z5U/X7R                                         | Murata               |  |  |

| L1           | Ferrite loop stick, 180–450 µH                                                     | Jiaxin               |  |  |

| U1           | Si473x AM/FM Radio Tuner                                                           | Silicon Laboratories |  |  |

|              | Optional Components                                                                |                      |  |  |

| T1           | Transformer, 1–5 turns ratio                                                       | Jiaxin, UMEC         |  |  |

| L2           | Air loop antenna, 10–20 μH                                                         | Various              |  |  |

| C2, C3       | Crystal load capacitors, 22 pF, ±5%, COG (Optional: for crystal oscillator option) | Venkel               |  |  |

| X1           | 32.768 kHz crystal (Optional: for crystal oscillator option)                       | Epson                |  |  |

| R1           | Resistor, 2 kΩ (Optional: for digital audio)                                       | Venkel               |  |  |

| R2           | Resistor, 2 kΩ (Optional: for digital audio)                                       | Venkel               |  |  |

| R3           | Resistor, 600 $\Omega$ (Optional: for digital audio)                               | Venkel               |  |  |

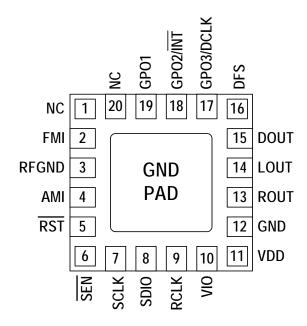

## 5. Pin Descriptions: Si473x-GM

| Pin Number(s) | Name      | Description                                                                                                |  |

|---------------|-----------|------------------------------------------------------------------------------------------------------------|--|

| 1, 20         | NC        | No connect. Leave floating.                                                                                |  |

| 2             | FMI       | FM/WB/SW RF inputs. FMI should be connected to the antenna trace.                                          |  |

| 3             | RFGND     | RF ground. Connect to ground plane on PCB.                                                                 |  |

| 4             | AMI       | AM/SW/LW RF input. AMI should be connected to the AM antenna.                                              |  |

| 5             | RST       | Device reset (active low) input.                                                                           |  |

| 6             | SEN       | Serial enable input (active low).                                                                          |  |

| 7             | SCLK      | Serial clock input.                                                                                        |  |

| 8             | SDIO      | Serial data input/output.                                                                                  |  |

| 9             | RCLK      | External reference oscillator input.                                                                       |  |

| 10            | $V_{IO}$  | I/O supply voltage.                                                                                        |  |

| 11            | $V_{DD}$  | Supply voltage. May be connected directly to battery.                                                      |  |

| 12, GND PAD   | GND       | Ground. Connect to ground plane on PCB.                                                                    |  |

| 13            | ROUT      | Right audio line output in analog output mode.                                                             |  |

| 14            | LOUT      | Left audio line output in analog output mode.                                                              |  |

| 15            | DOUT      | Digital output data in digital output mode.                                                                |  |

| 16            | DFS       | Digital frame synchronization input in digital output mode.                                                |  |

| 17            | GPO3/DCLK | General purpose output, crystal oscillator, or digital bit synchronous clock input in digital output mode. |  |

| 18            | GPO2/INT  | General purpose output or interrupt pin.                                                                   |  |

| 19            | GPO1      | General purpose output.                                                                                    |  |

## 6. Ordering Guide

| Part Number*  | Description                                        | Package<br>Type | Operating<br>Temperature |

|---------------|----------------------------------------------------|-----------------|--------------------------|

| Si4730-B20-GM | AM/FM Broadcast Radio Receiver                     | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4731-B20-GM | AM/FM Broadcast Radio Receiver with RDS/RBDS       | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4734-B20-GM | AM/FM/SW/LW Broadcast Radio Receiver               | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4735-B20-GM | AM/FM/SW/LW Broadcast Radio Receiver with RDS/RBDS | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4736-B20-GM | AM/FM/WB Broadcast Radio Receiver                  | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4737-B20-GM | AM/FM/WB Broadcast Radio Receiver with RDS/RBDS    | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4738-B20-GM | FM/WB Broadcast Radio Receiver                     | QFN<br>Pb-free  | −20 to 85 °C             |

| Si4739-B20-GM | FM/WB Broadcast Radio Receiver with RDS/RBDS       | QFN<br>Pb-free  | −20 to 85 °C             |

\*Note: Add an "(R)" at the end of the device part number to denote tape and reel option; 2500 quantity per reel.

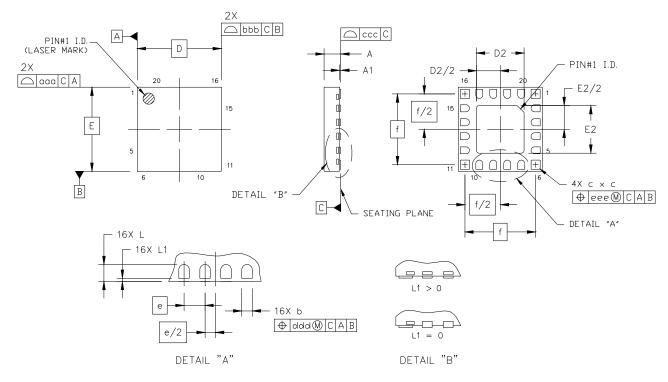

## 7. Package Outline: Si473x QFN

Figure 5 illustrates the package details for the Si473x. Table 11 lists the values for the dimensions shown in the illustration.

Figure 5. 20-Pin Quad Flat No-Lead (QFN)

**Table 11. Package Dimensions**

| Symbol | Millimeters |      |      |

|--------|-------------|------|------|

|        | Min         | Nom  | Max  |

| Α      | 0.50        | 0.55 | 0.60 |

| A1     | 0.00        | 0.02 | 0.05 |

| b      | 0.20        | 0.25 | 0.30 |

| С      | 0.27        | 0.32 | 0.37 |

| D      | 3.00 BSC    |      |      |

| D2     | 1.65        | 1.70 | 1.75 |

| е      | 0.50 BSC    |      |      |

| Е      | 3.00 BSC    |      |      |

| E2     | 1.65        | 1.70 | 1.75 |

|          | Millimeters |                       |  |

|----------|-------------|-----------------------|--|

| Min      | Nom         | Max                   |  |

| 2.53 BSC |             |                       |  |

| 0.35     | 0.40        | 0.45                  |  |

| 0.00     | _           | 0.10                  |  |

| _        | _           | 0.05                  |  |

| _        | _           | 0.05                  |  |

| _        | _           | 0.08                  |  |

| _        | _           | 0.10                  |  |

| _        | _           | 0.10                  |  |

|          | 0.35        | 2.53 BSC<br>0.35 0.40 |  |

#### Notes:

- 1. All dimensions are shown in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

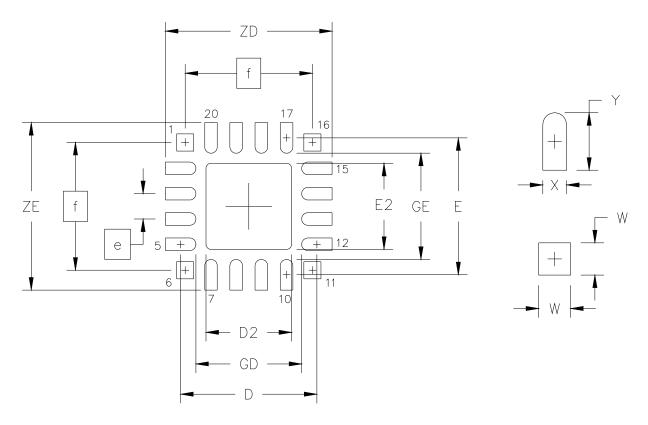

## 8. PCB Land Pattern: Si473x QFN

Figure 6 illustrates the PCB land pattern details for the Si473x family. Table 12 lists the values for the dimensions shown in the illustration.

Figure 6. PCB Land Pattern

**Table 12. PCB Land Pattern Dimensions**

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Max  |  |

| D      | 2.71 REF    |      |  |

| D2     | 1.60        | 1.80 |  |

| е      | 0.50 BSC    |      |  |

| Е      | 2.71 REF    |      |  |

| E2     | 1.60        | 1.80 |  |

| f      | 2.53 BSC    |      |  |

| GD     | 2.10        |      |  |

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Max  |  |

| GE     | 2.10        | _    |  |

| W      | _           | 0.34 |  |

| Х      | _           | 0.28 |  |

| Y      | 0.61 REF    |      |  |

| ZE     | _           | 3.31 |  |

| ZD     | _           | 3.31 |  |

#### Notes: General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### Notes: Stencil Design

- 1. A stainless steel, laser-cut, and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- 4. A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### **Notes: Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

21

## Si473x-B20

## 9. Additional Reference Resources

Contact your local sales representatives for more information or to obtain copies of the following references:

- EN55020 Compliance Test Certificate

- AN332: Si47xx Programming Guide

- AN383: Si47xx Antenna, Schematic, Layout, and Design Layout Guidelines

- AN388: Si470x/1x/2x/3x/4x Evaluation Board Test Procedure

Notes:

## Si473x-B20

### **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669

Toll Free: 1+(877) 444-3032 Email: FMinfo@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.