TABLE 2: SILICON ISSUE SUMMARY

| Module            | Feature               | Item   | Issue Summary                                                                            |    | cted<br>ions <sup>(1)</sup> |

|-------------------|-----------------------|--------|------------------------------------------------------------------------------------------|----|-----------------------------|

|                   |                       | Number |                                                                                          | А3 | A4                          |

| Oscillator        | Two-Speed<br>Start-up | 1.     | Feature is not functional.                                                               | Х  | Х                           |

| Resets            | _                     | 2.     | POR flag also set on BOR and External Reset.                                             | Х  | Х                           |

| Enhanced<br>PMP   | _                     | 3.     | Write incompatibility with certain slave devices.                                        | Х  | Х                           |

| A/D Converter     | _                     | 4.     | Module continues to draw current when disabled.                                          | Х  | Х                           |

| Interrupts        | INTx                  | 5.     | External interrupts missed when writing to INTCON2                                       | Х  | Χ                           |

| Output<br>Compare | Cascaded<br>Mode      | 6.     | Some modes unavailable in Cascaded mode.                                                 | Х  | Х                           |

| USB               | Host Mode             | 7.     | Low speed devices, when connected to a hub, will not work.                               | X  | Х                           |

| USB               | Device and Host Modes | 8.     | ACTVIF wake-up behavior differs from previous documentation.                             | Х  | Х                           |

| USB               | OTG Mode              | 9.     | VBUS comparators may trip at values outside of the required range for USB OTG operation. | Х  | Х                           |

| USB               | Device<br>Mode        | 10.    | EPSTALL bit behavior differs from previous documentation.                                | Х  | Х                           |

**Note 1:** Only those issues indicated in the last column apply to the current silicon revision.

#### Silicon Errata Issues

Note:

This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (A4).

#### 1. Module: Oscillator (Two-Speed Start-up)

Two-Speed Start-up is not functional. Leaving the IESO Configuration bit in its default state (Two-Speed Start-up enabled) may result in unpredictable operation.

#### Work around

None. Always program the IESO Configuration bit to disable the feature (CW2<15>=0).

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 2. Module: Resets

On Brown-out Resets and External (Master Clear) Resets, the POR bit may also become set. This may cause Brown-out and External Reset conditions to be indistinguishable from a Power-on Reset.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Х  | Χ  |  |  |  |

#### 3. Module: Enhanced PMP

The module is not write-compatible with slave devices that require data to be present before the Write strobe is asserted. The module has no configuration provision to output data before asserting the Write strobe.

Since most slave devices require valid input data to be present before the Write strobe is deasserted, the significance of this issue is thought to be limited.

#### Work around

None.

#### **Affected Silicon Revisions**

| A3 | i | A4 |  |  |  |

|----|---|----|--|--|--|

| Х  |   | Χ  |  |  |  |

#### 4. Module: A/D Converter

Once the A/D module is enabled (AD1CON1<15> = 1), it may continue to draw extra current even if the module later is disabled (AD1CON1<15> = 0).

#### Work around

In addition to disabling the module through the ADON bit, set the corresponding PMD bit, ADC1MD (PMD1<0>), to power it down completely.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 5. Module: Interrupts (INTx)

Writing to the INTCON2 register may cause an external interrupt event (inputs on INT0 through INT4) to be missed. This only happens when the interrupt event and the write event occur during the same clock cycle.

#### Work around

If this cannot be avoided, write the data intended for INTCON2 to any other register in the interrupt block of the SFR (addresses, 0080h to 00E0h); then write the data to INTCON2.

Be certain to write the data to a register not being actively used by the application, or to any of the interrupt flag registers, in order to avoid spurious interrupts. For example, if the interrupts controlled by IEC5 are not being used in the application, the code sequence would be:

IEC5 = 0x1E; INTCON2 = 0x1E; IEC5 = 0;

It is the user's responsibility to determine an appropriate register for the particular application.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

# 6. Module: Output Compare (Cascaded Mode)

When 32-bit Cascaded mode is enabled (OCxCON2<8> = 1), these modes are unavailable:

- Single-Shot operations when OCM (OCxCON1<2:0> = 110 or 111 and OCTRIG (OCxCON2<7>) = 1 and TRIGMODE (OCxCON1<3>) = 1.

- Synchronous modes when the SYNCSEL bits (OCxCON2<4:0>)! = 00000 and OCTRIG (OCxCON2<7>) = 0.

#### Work around

None.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Χ  | Х  |  |  |  |

#### 7. Module: USB

While operating in Host mode and attached to a low-speed device through a full-speed USB hub, the host may persistently drive the bus to an SE0 state (both D+/D- as '0') which would be interpreted as a bus Reset condition by the hub; or the host may persistently drive the bus to a J state, which would make the hub detach condition undetectable by the host.

#### Work around

Connect low-speed devices directly to the host USB port and not through a USB hub.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Х  | Х  |  |  |  |

#### 8. Module: USB (Device and Host Modes)

In previous literature for this module, the ACTVIF interrupt flag (U1OTGIR<4>) is described as being asserted, based on state changes detected on D+, D- or VBUS, when the microcontroller is in Sleep mode. In actual implementation, state changes on the RF3/USBID pin also cause the ACTVIF flag to be asserted.

As a result, logic input level changes on RF3/USBID may cause ACTVIF to be asserted, even in non-OTG applications that do not use the USBID function. This may cause the microcontroller to wake up unexpectedly.

#### Work around

<u>For On-The-Go (OTG) based applications:</u> No work around is needed.

For non-OTG Device, Host or dual-role applications: If ACTVIF is used as a wake-up source, it is recommended that the application be designed so that RF3/USBID does not see any changes while the microcontroller is in a power-saving mode.

If RF3/USBID is not needed in the application, it is recommended to configure it as a digital output.

If the RF3/USBID pin is configured as a digital input, ensure that the signal provider does not change the pin state while ACTVIF is enabled as a wake-up source. If the pin is used as a general purpose input, which can change while in the USB Suspend state, check the IDIF flag (U1OTGIR<7>) after waking up from an ACTVIF event to determine if the wake-up event was caused by a state change on RF3/USBID.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Х  | Х  |  |  |  |

#### 9. Module: USB (OTG Mode)

When using the on-chip VBUS comparators, the comparators may trip at values outside of the required range for USB OTG operation.

#### Work around

For Device mode operation: Use the SESVDIF interrupt flag and SESVD status bit for detection of VBUS, instead of the VBUSVDIF interrupt and VBUSVD status bit.

For OTG operation: Use the External Comparator mode for proper level detection. This is enabled by setting the UVCMPDIS bit (U1CNFG2<1>).

Note that the External Comparator mode requires the application to include external comparators and logic to generate signals for the VCMPST or VBUSVLD/SESSVLD/SESSEND digital input pins, according to the bus conditions (Table 3). It is the user's responsibility to provide the appropriate circuit design for this application.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Χ  | Χ  |  |  |  |

#### 10. Module: USB (Device Mode)

In previous literature for this module, the EPSTALL bits (U1EPn<1>) are described as being only stall status indicator bits in Device mode. In actual implementation, the EPSTALL bits function as both status and control bits.

If the EPSTALL bit for endpoint 'n' is set (either by the SIE hardware or manually in firmware), both the IN and OUT endpoints, associated with the endpoint, will send STALL packets when the endpoint's UOWN bit (BDnSTAT<15>) is also set.

#### Work around

<u>For Host applications:</u> No work around is needed, as hosts do not send STALL packets.

For Device mode applications: When it is necessary to stop sending STALL packets on an endpoint, clear the endpoint's respective BSTALL (BDnSTAT<10>) and EPSTALL bits. If the application firmware was developed based on one of the examples in the Microchip USB framework, this is already the default behavior of the USB stack firmware (except Version 2.8); no further work around is normally needed.

If a Device mode application was based upon Version 2.8 of the USB framework, and the application uses STALL packets on any of the application endpoints (1-15), it is suggested to update the application to the latest version.

#### **Affected Silicon Revisions**

| А3 | A4 |  |  |  |

|----|----|--|--|--|

| Χ  | Х  |  |  |  |

TABLE 3: EXTERNAL COMPARATOR MODE INPUTS FOR VARIOUS VBUS CONDITIONS

| When UVCMPSI | EL = 0: |                                    |                                  |  |  |  |

|--------------|---------|------------------------------------|----------------------------------|--|--|--|

| VCMPST1      | VCMPST2 |                                    | Bus Condition                    |  |  |  |

| 0            | 0       |                                    | VBUS < VB_SESS_END               |  |  |  |

| 1            | 0       |                                    | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |

| 0            | 1       |                                    | VA_SESS_VLD < VBUS < VA_VBUS_VLD |  |  |  |

| 1            | 1       | VBUS > VVBUS_VLD                   |                                  |  |  |  |

| When UVCMPSI | EL = 1: |                                    |                                  |  |  |  |

| VBUSVLD      | SESSVLD | SESSEND                            | Bus Condition                    |  |  |  |

| 0            | 0       | 1                                  | VBUS < VB_SESS_END               |  |  |  |

| 0            | 0       | 0 VB_SESS_END < VBUS < VA_SESS_VLD |                                  |  |  |  |

| 0            | 1       | 0 VA_SESS_VLD < VBUS < VA_VBUS_VLD |                                  |  |  |  |

| 1            | 1       | 0                                  | VBUS > VVBUS_VLD                 |  |  |  |

#### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS39969**B**):

**Note:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

#### Module: Guidelines for Getting Started with 16-Bit Microcontrollers

Section 2.4 Voltage Regulator Pins (ENVREG/DIS-VREG and VCAP/VDDCORE) has been replaced with a new and more detailed section. The entire text follows:

# 2.4 Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)

The on-chip voltage regulator enable pin must always be connected directly to a supply voltage.

Refer to **Section 27.2 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

When the regulator is enabled, a low-ESR ( $< 5\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

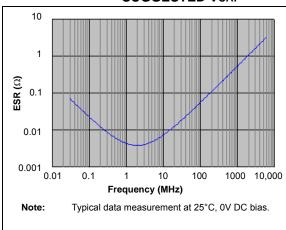

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 30.0 "Electrical Characteristics"** for additional information.

FIGURE 2-3 FREQUENCY vs. ESR

PERFORMANCE FOR

SUGGESTED VCAP

TABLE 2-1 SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |

|-----------|--------------------|------------------------|----------------|---------------|--------------|

| TDK       | C3216X7R1C106K     | 10 μF                  | ±10%           | 16V           | -55 to 125°C |

| TDK       | C3216X5R1C106K     | 10 μF                  | ±10%           | 16V           | -55 to 85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 μF                  | ±10%           | 16V           | -55 to 125°C |

| Panasonic | ECJ-4YB1C106K      | 10 μF                  | ±10%           | 16V           | -55 to 85°C  |

| Murata    | GRM32DR71C106KA01L | 10 μF                  | ±10%           | 16V           | -55 to 125°C |

| Murata    | GRM31CR61C106KC31L | 10 μF                  | ±10%           | 16V           | -55 to 85°C  |

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

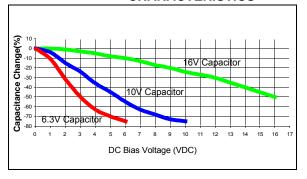

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as  $\pm 10\%$  to  $\pm 20\%$  (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex: ±15% over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of +22%/-82%. Due to the extreme temperature tolerance, a 10µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal voltage regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for 16V, 10V and 6.3V rated capacitors is shown in Figure 2-4.

FIGURE 2-4 DC BIAS VOLTAGE vs.

CAPACITANCE

CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 1.8V VCAP voltage. Suggested capacitors are shown in Table 2-1.

#### 2. Module: Electrical Specifications

The "Absolute Maximum Ratings" listed on page 371 are amended by adding the following specification:

Voltage on VUSB with respect to VSS.....(VDDCORE – 0.3V) to 4.0V

# 3. Module: Electrical Specifications (DC Characteristics)

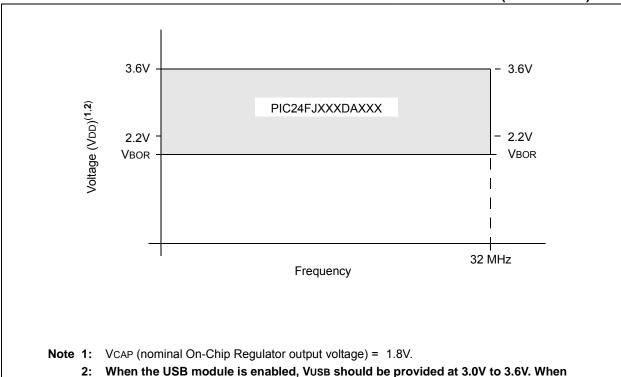

Figure 30-1 ("PIC24FJ256DA210 Family Voltage-Frequency Graph") is amended by adding an additional footnote. The updated figure is shown below (changes in **bold**; bold in original removed for clarity).

FIGURE 30-1: PIC24FJ256DA210 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

2: When the USB module is enabled, VusB should be provided at 3.0V to 3.6V. When the USB module is not enabled, the wider limits shaded in grey apply. The voltage on the VusB pin should be maintained at (VDD – 0.3V) or greater. Optionally, the pin may be left in a high-impedance state when the USB module is not in use, but doing so may result in higher IPD currents than specified.

# 4. Module: Electrical Specifications (DC Characteristics)

Table 30-3 ("DC Characteristics: Temperature and Voltage Specifications") is amended by adding a new specification, VUSB, and an explanatory footnote. The changes are shown below in **bold** (bold text in original removed for clarity).

TABLE 30-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS (PARTIAL REPRESENTATION)

| DC CHARACTERISTICS |                   | , ,                |                                       | ions: 2.0V to 3.6V (unless otherwise stated) $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial |     |       |                                                                                                 |  |  |  |  |

|--------------------|-------------------|--------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No.       | Symbol            | Characteristic     | Min                                   | Typ <sup>(1)</sup>                                                                                                      | Max | Units | Conditions                                                                                      |  |  |  |  |

| Operati            | Operating Voltage |                    |                                       |                                                                                                                         |     |       |                                                                                                 |  |  |  |  |

|                    | Vusb              | USB Supply Voltage | Greater of:<br>3.0 or<br>(VDD – 0.3V) | 3.3                                                                                                                     | 3.6 | V     | USB module enabled                                                                              |  |  |  |  |

|                    |                   |                    | (VDD – 0.3V) <sup>(3)</sup>           | _                                                                                                                       | 3.6 | V     | USB disabled, RG2/RG3<br>unused and externally<br>pulled low or left in<br>high-impedance state |  |  |  |  |

|                    |                   |                    | (VDD – 0.3V)                          | VDD                                                                                                                     | 3.6 | V     | USB disabled, RG2/RG3<br>used as general purpose<br>I/O                                         |  |  |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: This is the limit to which VDD can be lowered without losing RAM data.

- 3: The VUSB pin may also be left in a high-impedance state under these conditions. However, if the voltage floats below (VDD 0.3V), this may result in higher IPD currents than specified.

# APPENDIX A: DOCUMENT REVISION HISTORY

#### Rev A Document (6/2010)

Initial release of this document; issued for revision A3. Includes silicon issues 1 (Oscillator – Two-Speed Start-up), 2 (Resets), 3 (Enhanced PMP), 4 (A/D), 5 (Interrupts – INTx), and 6 (Output Compare – Cascaded Mode).

#### Rev B Document (9/2010)

Revised silicon issue 4 (A/D Converter) to reflect updated definition of issues.

Added data sheet clarification issue 1 (Guidelines For Getting Started with 16-Bit Microcontrollers).

#### Rev C Document (1/2011)

Added silicon issue 7 (USB).

#### Rev D Document (6/2011)

Added silicon revision A4. Adds existing silicon issues 1 through 7 from revision A3 without changes. No new data sheet clarifications added. No issues removed.

#### Rev E Document (9/2011)

Added silicon issues 8 (USB – Device and Host Modes), 9 (USB – OTG Mode) and 10 (USB – Device Mode) to all revisions.

Added data sheet clarification issues 2, 3 and 4 (Electrical Characteristics).

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010-2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-61341-663-1

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2009

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

**Toronto**

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511

Fax: 86-28-8665-7889 China - Chongging

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2401-1200

Fax: 852-2401-1200

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829

Fax: 86-24-2334-2393 China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166

Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

**Philippines - Manila** Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351

Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

08/02/11