# **Table of Contents**

| 1 | Orde  | ring Information                                      |   |       | 3.3.11 FEC                                       | 57      |

|---|-------|-------------------------------------------------------|---|-------|--------------------------------------------------|---------|

| 2 | Pin A | Assignments5                                          |   |       | 3.3.12 USB ULPI                                  | 59      |

|   | 2.1   | 516-TEPBGA Ball Map                                   |   |       | 3.3.13 On-Chip USB PHY                           | 60      |

|   | 2.2   | Pinout Listings6                                      |   |       | 3.3.14 SDHC                                      | 60      |

| 3 | Elect | rical and Thermal Characteristics                     |   |       | 3.3.15 DIU                                       | 62      |

|   | 3.1   | DC Electrical Characteristics                         |   |       | 3.3.16 SPDIF                                     | 65      |

|   |       | 3.1.1 Absolute Maximum Ratings17                      |   |       | 3.3.17 CAN                                       | 65      |

|   |       | 3.1.2 Recommended Operating Conditions                |   |       | 3.3.18 I <sup>2</sup> C                          | 65      |

|   |       | 3.1.3 DC Electrical Specifications                    |   |       | 3.3.19 J1850                                     | 66      |

|   |       | 3.1.4 Electrostatic Discharge                         |   |       | 3.3.20 PSC                                       | 66      |

|   |       | 3.1.5 Power Dissipation                               |   |       | 3.3.21 GPIOs and Timers                          | 73      |

|   |       | 3.1.6 Thermal Characteristics                         |   |       | 3.3.22 Fusebox                                   | 73      |

|   | 3.2   | Oscillator and PLL Electrical Characteristics         |   |       | 3.3.23 IEEE 1149.1 (JTAG)                        | 74      |

|   |       | 3.2.1 System Oscillator Electrical Characteristics 26 |   |       | 3.3.24 VIU                                       | 76      |

|   |       | 3.2.2 RTC Oscillator Electrical Characteristics 26    | 4 | Syste | em Design Information                            | 76      |

|   |       | 3.2.3 System PLL Electrical Characteristics26         |   | 4.1   | Power Up/Down Sequencing                         |         |

|   |       | 3.2.4 e300 Core PLL Electrical Characteristics 27     |   | 4.2   | System and CPU Core AVDD Power Supply Filter     | ing. 76 |

|   | 3.3   | AC Electrical Characteristics28                       |   | 4.3   | Connection Recommendations                       | 77      |

|   |       | 3.3.1 Overview                                        |   | 4.4   | Pull-Up/Pull-Down Resistor Requirements          | 78      |

|   |       | 3.3.2 AC Operating Frequency Data28                   |   |       | 4.4.1 Pull-Down Resistor Requirements for TEST   | Γpin78  |

|   |       | 3.3.3 Resets                                          |   |       | 4.4.2 Pull-Up Requirements for the PCI Control L | _ines78 |

|   |       | 3.3.4 External Interrupts                             |   | 4.5   | JTAG                                             | 78      |

|   |       | 3.3.5 SDRAM (DDR)32                                   |   |       | 4.5.1 TRST                                       | 78      |

|   |       | 3.3.6 PCI34                                           |   |       | 4.5.2 e300 COP/BDM Interface                     | 79      |

|   |       | 3.3.7 LPC                                             | 5 | Pack  | age Information                                  | 82      |

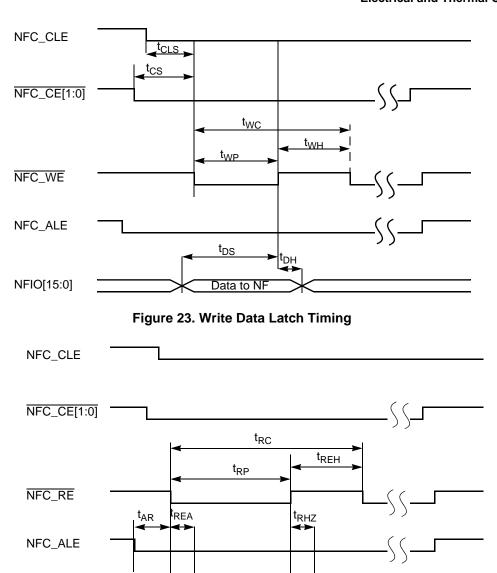

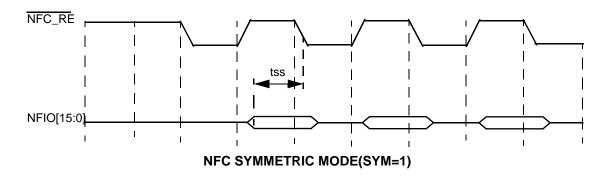

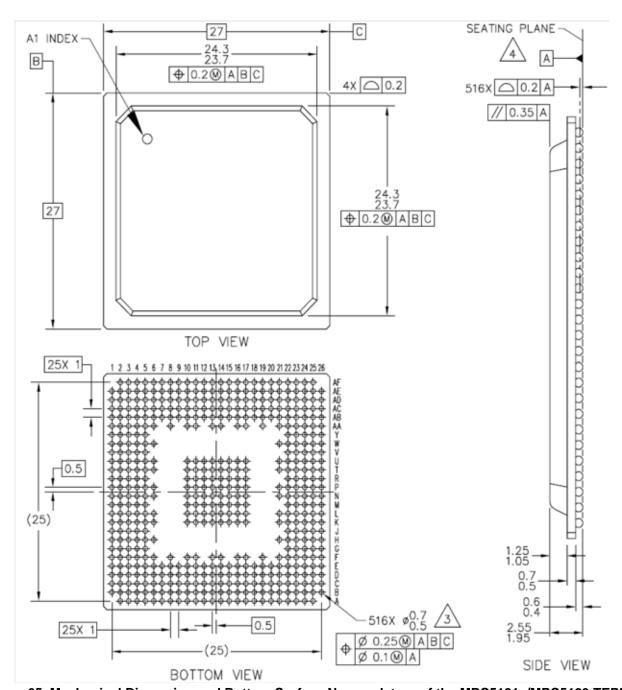

|   |       | 3.3.8 NFC                                             |   | 5.1   | Package Parameters                               | 82      |

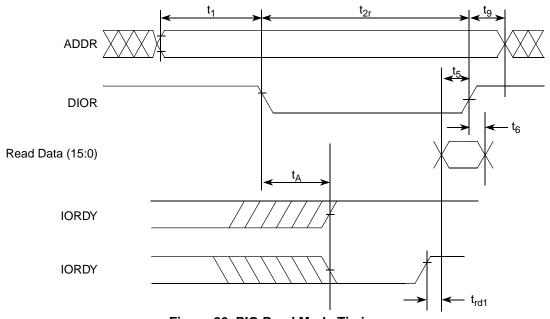

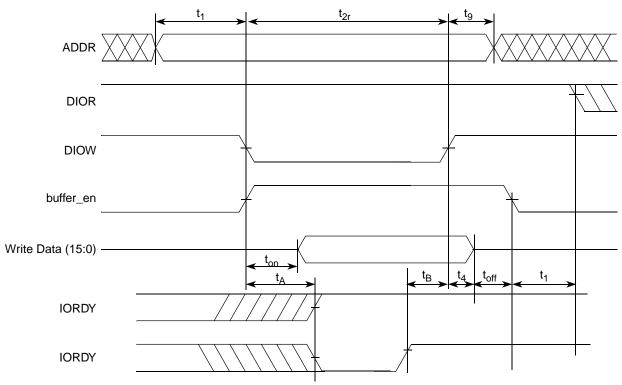

|   |       | 3.3.9 PATA45                                          |   | 5.2   | Mechanical Dimensions                            | 83      |

|   |       | 3.3.10 SATA PHY                                       | 6 | Prod  | uct Documentation                                | 84      |

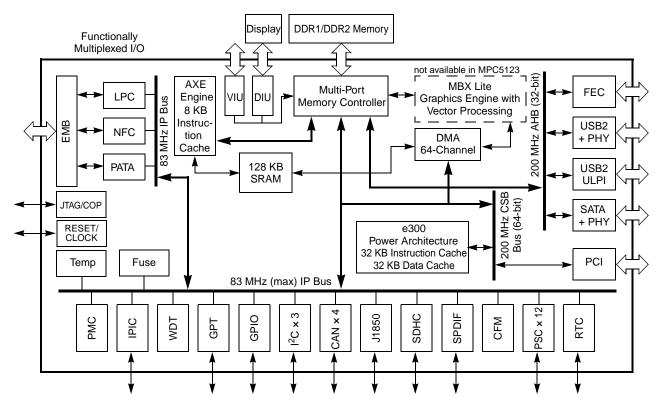

Figure 1 shows a simplified MPC5121e/MPC5123 block diagram.

Figure 1. Simplified MPC5121e/MPC5123 Block Diagram

# 1 Ordering Information

**Table 1. MPC5121e Orderable Part Numbers**

| Freescale Part Number | Speed (MHz) | Temperature<br>(ambient) | Qualification  | Package          | Availability  |

|-----------------------|-------------|--------------------------|----------------|------------------|---------------|

| MPC5121VY400B         | 400         | 0 °C to 70 °C            | Consumer       | RoHS and Pb-free | Tray          |

| MPC5121VY400BR        | 400         | 0 °C to 70 °C            | Consumer       | RoHS and Pb-free | Tape and Reel |

| MPC5121YVY400B        | 400         | –40 °C to 85 °C          | Industrial     | RoHS and Pb-free | Tray          |

| MPC5121YVY400BR       | 400         | –40 °C to 85 °C          | Industrial     | RoHS and Pb-free | Tape and Reel |

| SPC5121YVY400B        | 400         | –40 °C to 85 °C          | Automotive—AEC | RoHS and Pb-free | Tray          |

| SPC5121YVY400BR       | 400         | –40 °C to 85 °C          | Automotive—AEC | RoHS and Pb-free | Tape and Reel |

**Table 2. MPC5123 Orderable Part Numbers**

| Freescale Part Number | Speed (MHz) | Temperature<br>(ambient) | Qualification | Package          | Availability  |

|-----------------------|-------------|--------------------------|---------------|------------------|---------------|

| MPC5123VY400B         | 400         | 0 °C to 70 °C            | Consumer      | RoHS and Pb-free | Tray          |

| MPC5123VY400BR        | 400         | 0 °C to 70 °C            | Consumer      | RoHS and Pb-free | Tape and Reel |

| MPC5123YVY400B        | 400         | –40 °C to 85 °C          | Industrial    | RoHS and Pb-free | Tray          |

MPC5121E/MPC5123 Data Sheet, Rev. 5

# **Ordering Information**

# Table 2. MPC5123 Orderable Part Numbers (continued)

| Freescale Part Number | Speed (MHz) | Temperature<br>(ambient) | Qualification  | Package          | Availability  |

|-----------------------|-------------|--------------------------|----------------|------------------|---------------|

| MPC5123YVY400BR       | 400         | –40 °C to 85 °C          | Industrial     | RoHS and Pb-free | Tape and Reel |

| SPC5123YVY400B        | 400         | –40 °C to 85 °C          | Automotive—AEC | RoHS and Pb-free | Tray          |

| SPC5123YVY400BR       | 400         | –40 °C to 85 °C          | Automotive—AEC | RoHS and Pb-free | Tape and Reel |

MPC5121E/MPC5123 Data Sheet, Rev. 5

Freescale Semiconductor

4

# 2 Pin Assignments

This section details pin assignments.

# 2.1 516-TEPBGA Ball Map

| Ī  | 1                     | 2                     | 3                        | 4                     | 5                      | 6                    | 7          | 8          | 9                   | 10                 | 11           | 12           | 13           | 14                 | 15                 | 16           | 17                  | 18                 | 19            | 20                 | 21                              | 22                    | 23                    | 24            | 25           | 26             |

|----|-----------------------|-----------------------|--------------------------|-----------------------|------------------------|----------------------|------------|------------|---------------------|--------------------|--------------|--------------|--------------|--------------------|--------------------|--------------|---------------------|--------------------|---------------|--------------------|---------------------------------|-----------------------|-----------------------|---------------|--------------|----------------|

| Α  |                       | VSS                   | VSS                      | SATA_<br>RXN          | SATA_<br>RXP           | SATA_<br>RX_VS<br>SA | PSC7_<br>4 | PSC7_      | PSC6_<br>4          | PSC6_<br>2         | PSC6_<br>0   | PSC11<br>_0  | PSC10<br>_2  | PSC2_              | PSC1_              | PSC1_<br>1   | PSC0_<br>1          | CAN1_<br>TX        | GPIO2<br>8    | RTC_X<br>TALO      | USB2_<br>DRVVB<br>US            | USB_D<br>M            | USB_D<br>P            | USB_T<br>PA   | VSS          |                |

| В  | VSS                   | VSS                   | VSS                      | SATA_<br>RX_VS<br>SA  | VSS                    | PSC8_<br>3           | VSS        | PSC7_<br>0 | PSC6_<br>3          | VDD_I<br>O         | PSC11<br>_1  | VSS          | PSC10<br>_1  | PSC2_              | VDD_I<br>O         | PSC0_        | VSS                 | GPIO3              | CAN2_<br>RX   | VSS                | USB2_<br>VBUS_<br>PWR_F<br>AULT | VSS                   | USB_V<br>SSA_B<br>IAS | USB_X<br>TALO | VDD_I<br>O   | VSS            |

| С  | VSS                   | SATA_<br>XTALO        | SATA_<br>XTALI           | VSS                   | SATA_<br>VDDA_<br>1P2  | PSC9_<br>0           | PSC8_      | PSC7_<br>2 | AVDD_<br>FUSE<br>WR | PSC6_<br>1         | PSC11<br>_2  | PSC10<br>_3  | PSC10<br>_0  | PSC2_<br>0         | PSC1_<br>0         | PSC0_        | PSC_<br>MCLK_<br>IN | GPIO3<br>0         | CAN1_<br>RX   | RTC_X<br>TALI      | USB_V<br>DDA                    | USB_V<br>SSA          | VSS                   | USB_X<br>TALI | VSS          | PCI_C<br>LK    |

| D  | SATA_<br>VDDA_<br>1P2 | VSS                   | SATA_<br>PLL_V<br>SSA    | SATA_<br>VDDA_<br>3P3 | SATA_<br>VDDA_<br>VREG | PSC9_                | PSC9_      | PSC8_<br>1 | VDD_I<br>O          | VDD_I<br>O         | PSC11<br>_4  | VSS          | PSC2_<br>4   | PSC1_<br>4         | VDD_I<br>O         | PSC0_<br>0   | VSS                 | HIB_M<br>ODE       | VBAT_<br>RTC  | USB_V<br>DDA       | USB_V<br>BUS                    | USB_V<br>DDA_B<br>IAS | USB_P<br>LL_PW<br>R3  | VSS           | VSS          | PCI_R<br>EQ2   |

| E  | SATA_<br>TXN          | SATA_V<br>DDA_1<br>P2 | SATA_P<br>LL_VDD<br>A1P2 | SATA_R<br>ESREF       | SATA_A<br>NAVIZ        | PSC9_                | PSC9_      | PSC8_      | PSC8_               | PSC7_              | PSC11<br>_3  | PSC10<br>_4  | PSC2_        | PSC1_              | PSC0_              | CAN2_<br>TX  | GPIO2<br>9          | VSS                | USB_U<br>ID   | USB_V<br>SSA       | USB_V<br>SSA                    | USB_R<br>REF          | USB_PL<br>L_GND       | PCI_G<br>NT2  | PCI_G<br>NT0 | PCI_R<br>EQ1   |

| F  | SATA_<br>TXP          | VSS                   | VSS                      | VSS                   | VSS                    | VSS                  |            | VSS        |                     | VSS                | VDD_I<br>O   |              | VDD_I<br>O   | VDD_I<br>O         |                    | VSS          | VSS                 |                    | VDD_I<br>O    |                    | VSS                             | PCI_RS<br>T_OUT       | VDD_I<br>O            | PCI_A<br>D30  | VDD_I<br>O   | PCI_A<br>D28   |

| G  | SATA_<br>TX_VS<br>SA  | NFC_R                 | NFC_<br>WE               | NFC_<br>WP            | VSS                    |                      |            |            |                     |                    |              |              |              |                    |                    |              |                     |                    |               |                    |                                 | PCI_G<br>NT1          | PCI_R<br>EQ0          | PCI_A<br>D29  | PCI_A<br>D26 | PCI_C/<br>BE3  |

| Н  | NFC_R<br>/B           | PATA_<br>DACK         | NFC_C<br>E0              | NFC_A<br>LE           | NFC_C<br>LE            | VSS                  |            |            |                     |                    |              |              |              |                    |                    |              |                     |                    |               |                    | VDD_I<br>O                      | PCI_A<br>D31          | VSS                   | PCI_A<br>D24  | VSS          | PCI_A<br>D21   |

| J  | PATA_I<br>OR          | PATA_I<br>OCHR<br>DY  | PATA_I<br>NTRQ           | PATA_<br>DRQ          | VDD_I<br>O             |                      |            |            |                     |                    |              |              |              |                    |                    |              |                     |                    |               |                    |                                 | PCI_A<br>D27          | PCI_A<br>D25          | PCI_A<br>D23  | PCI_A<br>D20 | PCI_A<br>D18   |

| к  | PATA_<br>CE1          | VDD_I<br>O            | PATA_I<br>SOLAT<br>E     | VDD_I<br>O            | PATA_I<br>OW           | VSS                  |            |            |                     | VDD_C<br>ORE       | VDD_C<br>ORE | VDD_C<br>ORE | VDD_C<br>ORE | VDD_C<br>ORE       | VDD_C<br>ORE       | VDD_C<br>ORE | VDD_C<br>ORE        |                    |               |                    | VSS                             | PCI_ID<br>SEL         | PCI_A<br>D22          | PCI_A<br>D19  | PCI_A<br>D17 | PCI_IR<br>DY   |

| L  | EMB_A<br>D03          | EMB_A<br>D02          | EMB_A<br>D01             | EMB_A<br>D00          | PATA_<br>CE2           | VSS                  |            |            |                     | VDD_C<br>ORE       | VSS          | VSS          | VSS          | VSS                | VSS                | VSS          | VDD_C<br>ORE        |                    |               |                    | VSS                             | PCI_A<br>D16          | VDD_I<br>O            | PCI_C/<br>BE2 | VDD_I<br>O   | PCI_D<br>EVSEL |

| М  | EMB_A<br>D06          | VSS                   | EMB_A<br>D05             | VSS                   | EMB_A<br>D04           |                      |            |            |                     | VDD_C<br>ORE       | VSS          | VSS          | VSS          | VSS                | VSS                | VSS          | VDD_C<br>ORE        |                    |               |                    |                                 | PCI_T<br>RDY          | PCI_F<br>RAME         | PCI_S<br>TOP  | PCI_P<br>ERR | PCI_S<br>ERR   |

| N  | EMB_A<br>D10          | EMB_A<br>D09          | EMB_A<br>D08             | EMB_A<br>D07          | VSS                    | VDD_I<br>O           |            |            |                     | VDD_C<br>ORE       | VSS          | VSS          | VSS          | VSS                | VSS                | VSS          | VDD_C<br>ORE        |                    |               |                    | VDD_I<br>O                      | PCI_P<br>AR           | VSS                   | PCI_C/<br>BE1 | VSS          | PCI_A<br>D15   |

| Р  | EMB_A<br>D15          | EMB_A<br>D14          | EMB_A<br>D11             | EMB_A<br>D13          | EMB_A<br>D12           | VDD_I<br>O           |            |            |                     | VDD_C<br>ORE       | VSS          | VSS          | VSS          | VSS                | VSS                | VSS          | VDD_C<br>ORE        |                    |               |                    | VDD_I<br>O                      | PCI_C/<br>BE0         | PCI_A<br>D09          | PCI_A<br>D13  | PCI_A<br>D14 | PCI_A<br>D12   |

| R  | EMB_A<br>D17          | VDD_I<br>O            | EMB_A<br>D16             | VDD_I<br>O            | EMB_A<br>D19           |                      |            |            |                     | VDD_C<br>ORE       | VSS          | VSS          | VSS          | VSS                | VSS                | VSS          | VDD_C<br>ORE        |                    |               |                    |                                 | PCI_A<br>D03          | PCI_A<br>D06          | PCI_A<br>D10  | PCI_A<br>D11 | PCI_A<br>D08   |

| Т  | EMB_A<br>D22          | EMB_A<br>D18          | EMB_A<br>D20             | EMB_A<br>D21          | EMB_A<br>D23           | VSS                  |            |            |                     | VDD_C<br>ORE       | VSS          | VSS          | VSS          | VSS                | VSS                | VSS          | VDD_C<br>ORE        |                    |               |                    | VSS                             | SYS_PL<br>L_AVDD      | VDD_I<br>O            | PCI_A<br>D05  | VDD_I<br>O   | PCI_A<br>D07   |

| U  | EMB_A<br>D25          | VSS                   | EMB_A<br>D24             | VSS                   | EMB_A<br>D29           | VSS                  |            |            |                     | VDD_C<br>ORE       | VDD_C<br>ORE | VDD_C<br>ORE | VDD_C<br>ORE | VDD_C<br>ORE       | VDD_C<br>ORE       | VDD_C<br>ORE | VDD_C<br>ORE        |                    |               |                    | VSS                             | SYS_PL<br>L_AVSS      | PCI_IN<br>TA          | PCI_A<br>D00  | PCI_A<br>D02 | PCI_A<br>D04   |

| ٧  | D26                   | EMB_A<br>D27          | EMB_A<br>D28             | EMB_A<br>D30          | EMB_A<br>X01           |                      |            |            |                     |                    |              |              |              |                    |                    |              |                     |                    |               |                    |                                 | SRESE<br>T            | VSS                   | SYS_X<br>TALI | VSS          | PCI_A<br>D01   |

| w  | D31                   | EMB_A<br>X00          | EMB_A<br>X02             | LPC_A<br>X03          | LPC_C<br>S0            | VDD_I<br>O           |            |            |                     |                    |              |              |              |                    |                    |              |                     |                    |               |                    | VDD_I<br>O                      | TDO                   | PORE<br>SET           | HRES          | TEST         | SYS_X<br>TALO  |

| Y  | LPC_C<br>\$2          | VDD_I<br>O            | S1                       | VDD_I<br>O            | LPC_O<br>E             |                      |            | VDD        |                     |                    |              |              | VDD          | VDD                |                    |              |                     |                    | CORE          |                    |                                 | J1850_<br>TX          | TDI                   | VSS           | TMS          | _OUT           |

| AA | LPC_R<br>WB           | LPC_A<br>CK           | PSC4_<br>1               | LPC_C<br>LK           | PSC4_<br>3             | VSS                  |            | MEM_I<br>O |                     | VSS                | VSS          |              | MEM_I<br>O   | MEM_I<br>O         |                    | VSS          | VSS                 |                    | _PLL_<br>AVDD |                    | VSS                             | I2C2_S<br>DA          | VDD_I<br>O            | J1850_<br>RX  | VDD_I<br>O   | TRST           |

| Ab | PSC4_<br>0            | VSS                   | PSC4_<br>2               | VSS                   | PSC3_<br>1             | MDQ1                 | MVTT0      | MDQ5       | MDQ1<br>0           | VSS                | MVRE<br>F    | MDQ1<br>9    | MDQ2<br>1    | 7                  | MDQ3<br>1          | MA1          | MA5                 | VDD_<br>MEM_I<br>O | MA14          | MCKE               | SPDIF<br>_TXCL<br>K             | I2C1_S<br>CL          | I2C1_S<br>DA          | vss           | ĪRQ1         | тск            |

| AC | PSC5_<br>0            | PSC4_<br>4            | PSC5_<br>1               | PSC3_<br>2            | VDD_<br>MEM_I<br>O     | MDM0                 | MDQ8       | VSS        | MDQ1<br>4           | VDD_<br>MEM_I<br>O | MDQS<br>2    | VSS          | MDQ2<br>5    | VDD_<br>MEM_I<br>O | MDQ3<br>0          | MBA1         | VSS                 | MA7                | MA11          | VDD_<br>MEM_I<br>O | MODT                            | VSS                   | I2C0_S<br>CL          | SPDIF<br>_RX  | I2C2_S<br>CL | ĪRQ0           |

| AD | PSC5_<br>2            | PSC5_<br>3            | VSS                      | PSC3_<br>3            | MDQS<br>0              | MDQ6                 | MDQ1<br>1  | MDQS<br>1  | VDD_<br>MEM_I<br>O  | MDQ1<br>6          | MDQ1<br>8    | MDQ2<br>0    | MDQ2<br>3    | MDQS<br>3          | MDQ2<br>9          | MBA0         | MA0                 | MA4                | MA9           | MA13               | MWE                             | MCS                   | CORE<br>_PLL_<br>AVSS | SPDIF<br>_TX  | VSS          | I2C0_S<br>DA   |

| ΑE | VDD_I<br>O            | VDD_I<br>O            | PSC5_<br>4               | MDQ2                  | VDD_<br>MEM_I<br>O     | MDQ7                 | VSS        | MDM1       | MDQ1<br>2           | VDD_<br>MEM_I<br>O | MVTT2        | VSS          | MDQ2<br>4    | MVTT3              | VDD_<br>MEM_I<br>O | MDQ2<br>8    | VSS                 | MA2                | MA6           | VDD_<br>MEM_I<br>O | MA12                            | MA15                  | VSS                   | VDD_I<br>O    | VDD_I<br>O   | VSS            |

| AF |                       | VDD_I<br>O            | PSC3_<br>0               | PSC3_<br>4            | MDQ0                   | MDQ3                 | MDQ4       | MDQ9       | MVTT1               | MDQ1<br>3          | MDQ1<br>5    | MDQ1<br>7    | MDM2         | MDQ2<br>2          | MDQ2<br>6          | MDM3         | MCK                 | MCK                | MBA2          | MA3                | MA8                             | MA10                  | MRAS                  | MCAS          | VDD_I<br>O   |                |

Figure 2. Ball Map for the MPC5121e 516 TEPBGA Package MPC5121E/MPC5123 Data Sheet, Rev. 5

# 2.2 Pinout Listings

Table 3 provides the pin-out listing for the MPC5121e/MPC5123.

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 1 of 12)

| Signal | Package Pin Number | Pad Type        | Power Supply           | Notes |

|--------|--------------------|-----------------|------------------------|-------|

|        | DDR Memory         | y Interface (67 | Total)                 |       |

| MDQ0   | AF5                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ1   | AB6                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ2   | AE4                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ3   | AF6                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ4   | AF7                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ5   | AB8                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ6   | AD6                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ7   | AE6                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ8   | AC7                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ9   | AF8                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ10  | AB9                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ11  | AD7                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ12  | AE9                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ13  | AF10               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ14  | AC9                | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ15  | AF11               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ16  | AD10               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ17  | AF12               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ18  | AD11               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ19  | AB12               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ20  | AD12               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ21  | AB13               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ22  | AF14               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ23  | AD13               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ24  | AE13               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ25  | AC13               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ26  | AF15               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ27  | AB14               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ28  | AE16               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ29  | AD15               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

| MDQ30  | AC15               | DDR             | V <sub>DD_MEM_IO</sub> | _     |

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 2 of 12)

| Signal | Package Pin Number | Pad Type | Power Supply           | Notes |

|--------|--------------------|----------|------------------------|-------|

| MDQ31  | AB15               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDM0   | AC6                | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDM1   | AE8                | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDM2   | AF13               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDM3   | AF16               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDQS0  | AD5                | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDQS1  | AD8                | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDQS2  | AC11               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MDQS3  | AD14               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MBA0   | AD16               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MBA1   | AC16               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MBA2   | AF19               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA0    | AD17               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA1    | AB16               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA2    | AE18               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA3    | AF20               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA4    | AD18               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA5    | AB17               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA6    | AE19               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA7    | AC18               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA8    | AF21               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA9    | AD19               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA10   | AF22               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA11   | AC19               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA12   | AE21               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA13   | AD20               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA14   | AB19               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MA15   | AE22               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MWE    | AD21               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MRAS   | AF23               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MCAS   | AF24               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MCS    | AD22               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MCKE   | AB20               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MCK    | AF17               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

| MCK    | AF18               | DDR      | V <sub>DD_MEM_IO</sub> | _     |

MPC5121E/MPC5123 Data Sheet, Rev. 5

# **Pin Assignments**

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 3 of 12)

| Signal   | Package Pin Number | Pad Type         | Power Supply           | Notes |

|----------|--------------------|------------------|------------------------|-------|

| MODT     | AC21               | DDR              | V <sub>DD_MEM_IO</sub> | _     |

|          | LPC Int            | erface (8 Total) |                        |       |

| LPC_CLK  | AA4                | General IO       | $V_{DD\_IO}$           | _     |

| LPC_OE   | Y5                 | General IO       | $V_{DD\_IO}$           | _     |

| LPC_RW   | AA1                | General IO       | $V_{DD\_IO}$           | _     |

| LPC_CS0  | W5                 | General IO       | $V_{DD\_IO}$           | _     |

| LPC_CS1  | Y3                 | General IO       | $V_{DD\_IO}$           | _     |

| LPC_CS2  | Y1                 | General IO       | $V_{DD\_IO}$           | _     |

| LPC_ACK  | AA2                | General IO       | V <sub>DD_IO</sub>     | _     |

| LPC_AX03 | W4                 | General IO       | V <sub>DD_IO</sub>     | _     |

|          | EMB Into           | erface (35 Total | )                      |       |

| EMB_AX02 | W3                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AX01 | V5                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AX00 | W2                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD31 | W1                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD30 | V4                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD29 | U5                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD28 | V3                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD27 | V2                 | General IO       | V <sub>DD_IO</sub>     | _     |

| EMB_AD26 | V1                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD25 | U1                 | General IO       | V <sub>DD_IO</sub>     | _     |

| EMB_AD24 | U3                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD23 | T5                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD22 | T1                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD21 | T4                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD20 | Т3                 | General IO       | $V_{DD\_IO}$           | _     |

| EMB_AD19 | R5                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD18 | T2                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD17 | R1                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD16 | R3                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD15 | P1                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD14 | P2                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD13 | P4                 | General IO       | $V_{\mathrm{DD\_IO}}$  | _     |

| EMB_AD12 | P5                 | General IO       | $V_{DD\_IO}$           | _     |

MPC5121E/MPC5123 Data Sheet, Rev. 5

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 4 of 12)

| Signal       | Package Pin Number | Pad Type          | Power Supply           | Notes           |

|--------------|--------------------|-------------------|------------------------|-----------------|

| EMB_AD11     | P3                 | General IO        | V <sub>DD_IO</sub>     | _               |

| EMB_AD10     | N1                 | General IO        | $V_{DD\_IO}$           | _               |

| EMB_AD09     | N2                 | General IO        | V <sub>DD_IO</sub>     | _               |

| EMB_AD08     | N3                 | General IO        | $V_{\mathrm{DD\_IO}}$  | _               |

| EMB_AD07     | N4                 | General IO        | $V_{DD\_IO}$           | _               |

| EMB_AD06     | M1                 | General IO        | $V_{\mathrm{DD\_IO}}$  | _               |

| EMB_AD05     | M3                 | General IO        | $V_{\mathrm{DD\_IO}}$  | _               |

| EMB_AD04     | M5                 | General IO        | $V_{DD\_IO}$           | _               |

| EMB_AD03     | L1                 | General IO        | V <sub>DD_IO</sub>     | _               |

| EMB_AD02     | L2                 | General IO        | V <sub>DD_IO</sub>     | _               |

| EMB_AD01     | L3                 | General IO        | V <sub>DD_IO</sub>     | _               |

| EMB_AD00     | L4                 | General IO        | V <sub>DD_IO</sub>     | _               |

|              | PATA In            | terface (9 Total) |                        |                 |

| PATA_CE1     | K1                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | ATA name: CS0   |

| PATA_CE2     | L5                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | ATA name: CS1   |

| PATA_ISOLATE | K3                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| PATA_IOR     | J1                 | General IO        | V <sub>DD_IO</sub>     | ATA name: DIOR  |

| PATA_IOW     | K5                 | General IO        | V <sub>DD_IO</sub>     | ATA name: DIOW  |

| PATA_IOCHRDY | J2                 | General IO        | V <sub>DD_IO</sub>     | ATA name: IORDY |

| PATA_INTRQ   | J3                 | General IO        | V <sub>DD_IO</sub>     | _               |

| PATA_DRQ     | J4                 | General IO        | V <sub>DD_IO</sub>     | ATA name: DMARQ |

| PATA_DACK    | H2                 | General IO        | $V_{\mathrm{DD\_IO}}$  | ATA name: DMACK |

|              | NFC Int            | terface (7 Total) |                        |                 |

| NFC_WP       | G4                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| NFC_R/B      | H1                 | General IO        | $V_{DD\_IO}$           | _               |

| NFC_WE       | G3                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| NFC_RE       | G2                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| NFC_ALE      | H4                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| NFC_CLE      | H5                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| NFC_CE0      | H3                 | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

|              | I2C Int            | erface (6 Total)  |                        |                 |

| I2C0_SCL     | AC23               | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| I2C0_SDA     | AD26               | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

| I2C1_SCL     | AB22               | General IO        | $V_{\mathrm{DD_{IO}}}$ | _               |

MPC5121E/MPC5123 Data Sheet, Rev. 5

# **Pin Assignments**

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 5 of 12)

| Signal      | Package Pin Number        | Pad Type          | Power Supply          | Notes |  |  |  |  |  |  |  |

|-------------|---------------------------|-------------------|-----------------------|-------|--|--|--|--|--|--|--|

| I2C1_SDA    | AB23                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| I2C2_SCL    | AC25                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| I2C2_SDA    | AA22                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

|             | IRQ Int                   | erface (2 Total)  |                       |       |  |  |  |  |  |  |  |

| ĪRQ0        | AC26                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| ĪRQ1        | AB25                      | General IO        | V <sub>DD_IO</sub>    | _     |  |  |  |  |  |  |  |

|             | CAN In                    | terface (4 Total) |                       |       |  |  |  |  |  |  |  |

| CAN1_RX     | C19                       | Analog Input      | VBAT_RTC              | _     |  |  |  |  |  |  |  |

| CAN1_TX     | A18                       | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| CAN2_RX     | B19                       | Analog Input      | VBAT_RTC              | _     |  |  |  |  |  |  |  |

| CAN2_TX     | E16                       | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

|             | J1850 Ir                  | nterface (2 Total | )                     |       |  |  |  |  |  |  |  |

| J1850_TX    | Y22                       | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| J1850_RX    | AA24                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

|             | SPDIF Interface (3 Total) |                   |                       |       |  |  |  |  |  |  |  |

| SPDIF_TXCLK | AB21                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| SPDIF_TX    | AD24                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| SPDIF_RX    | AC24                      | General IO        | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

|             | PC                        | I (54 Total)      |                       |       |  |  |  |  |  |  |  |

| PCI_INTA    | U23                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_RST_OUT | F22                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD00    | U24                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD01    | V26                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD02    | U25                       | PCI               | $V_{\mathrm{DD\_IO}}$ | _     |  |  |  |  |  |  |  |

| PCI_AD03    | R22                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD04    | U26                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD05    | T24                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD06    | R23                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD07    | T26                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD08    | R26                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD09    | P23                       | PCI               | V <sub>DD_IO</sub>    | _     |  |  |  |  |  |  |  |

| PCI_AD10    | R24                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

| PCI_AD11    | R25                       | PCI               | V <sub>DD_IO</sub>    | _     |  |  |  |  |  |  |  |

| PCI_AD12    | P26                       | PCI               | $V_{DD\_IO}$          | _     |  |  |  |  |  |  |  |

MPC5121E/MPC5123 Data Sheet, Rev. 5

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 6 of 12)

| Signal     | Package Pin Number | Pad Type | Power Supply          | Notes |

|------------|--------------------|----------|-----------------------|-------|

| PCI_AD13   | P24                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD14   | P25                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD15   | N26                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD16   | L22                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD17   | K25                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD18   | J26                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD19   | K24                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD20   | J25                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD21   | H26                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD22   | K23                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD23   | J24                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD24   | H24                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD25   | J23                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD26   | G25                | PCI      | $V_{DD\_IO}$          | _     |

| PCI_AD27   | J22                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD28   | F26                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_AD29   | G24                | PCI      | $V_{DD\_IO}$          | _     |

| PCI_AD30   | F24                | PCI      | $V_{\mathrm{DD\_IO}}$ | _     |

| PCI_AD31   | H22                | PCI      | $V_{\mathrm{DD\_IO}}$ | _     |

| PCI_C/BE0  | P22                | PCI      | $V_{DD\_IO}$          | _     |

| PCI_C/BE1  | N24                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_C/BE2  | L24                | PCI      | V <sub>DD_IO</sub>    | _     |

| PCI_C/BE3  | G26                | PCI      | $V_{DD\_IO}$          | _     |

| PCI_PAR    | N22                | PCI      | $V_{\mathrm{DD\_IO}}$ | _     |

| PCI_FRAME  | M23                | PCI      | $V_{\mathrm{DD\_IO}}$ | 1     |

| PCI_TRDY   | M22                | PCI      | $V_{DD\_IO}$          | 1     |

| PCI_IRDY   | K26                | PCI      | $V_{\mathrm{DD\_IO}}$ | 1     |

| PCI_STOP   | M24                | PCI      | $V_{\mathrm{DD\_IO}}$ | 1     |

| PCI_DEVSEL | L26                | PCI      | V <sub>DD_IO</sub>    | 1     |

| PCI_IDSEL  | K22                | PCI      | $V_{DD\_IO}$          | _     |

| PCI_SERR   | M26                | PCI      | $V_{DD\_IO}$          | 1     |

| PCI_PERR   | M25                | PCI      | $V_{DD\_IO}$          | 1     |

| PCI_REQ0   | G23                | PCI      | $V_{DD\_IO}$          | 1     |

| PCI_REQ1   | E26                | PCI      | $V_{DD\_IO}$          | 1     |

| PCI_REQ2   | D26                | PCI      | $V_{\mathrm{DD\_IO}}$ | 1     |

MPC5121E/MPC5123 Data Sheet, Rev. 5

# **Pin Assignments**

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 7 of 12)

| Signal      | Package Pin Number | Pad Type         | Power Supply          | Notes |

|-------------|--------------------|------------------|-----------------------|-------|

| PCI_GNT0    | E25                | PCI              | V <sub>DD_IO</sub>    | _     |

| PCI_GNT1    | G22                | PCI              | $V_{DD\_IO}$          | _     |

| PCI_GNT2    | E24                | PCI              | $V_{\mathrm{DD\_IO}}$ | _     |

| PCI_CLK     | C26                | PCI              | $V_{\mathrm{DD\_IO}}$ | _     |

|             | PSC Inte           | erface (61 Total | )                     |       |

| PSC_MCLK_IN | C17                | General IO       | $V_{DD\_IO}$          | _     |

| PSC0_0      | D16                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC0_1      | A17                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC0_2      | E15                | General IO       | $V_{DD\_IO}$          | _     |

| PSC0_3      | C16                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC0_4      | B16                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC1_0      | C15                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC1_1      | A16                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC1_2      | E14                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC1_3      | A15                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC1_4      | D14                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC2_0      | C14                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC2_1      | B14                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC2_2      | E13                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC2_3      | A14                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC2_4      | D13                | General IO       | $V_{DD\_IO}$          | _     |

| PSC3_0      | AF3                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC3_1      | AB5                | General IO       | $V_{DD\_IO}$          | _     |

| PSC3_2      | AC4                | General IO       | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC3_3      | AD4                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC3_4      | AF4                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC4_0      | AB1                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC4_1      | AA3                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC4_2      | AB3                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC4_3      | AA5                | General IO       | $V_{DD\_IO}$          | _     |

| PSC4_4      | AC2                | General IO       | V <sub>DD_IO</sub>    | _     |

| PSC5_0      | AC1                | General IO       | $V_{DD\_IO}$          | _     |

| PSC5_1      | AC3                | General IO       | $V_{DD\_IO}$          | _     |

| PSC5_2      | AD1                | General IO       | V <sub>DD_IO</sub>    | _     |

|             |                    |                  |                       |       |

MPC5121E/MPC5123 Data Sheet, Rev. 5

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 8 of 12)

| Signal  | Package Pin Number | Pad Type     | Power Supply          | Notes |

|---------|--------------------|--------------|-----------------------|-------|

| PSC5_3  | AD2                | General IO   | V <sub>DD_IO</sub>    | _     |

| PSC5_4  | AE3                | General IO   | $V_{DD\_IO}$          | _     |

| PSC6_0  | A11                | General IO   | V <sub>DD_IO</sub>    | _     |

| PSC6_1  | C10                | General IO   | $V_{DD\_IO}$          | _     |

| PSC6_2  | A10                | General IO   | $V_{DD\_IO}$          | _     |

| PSC6_3  | В9                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC6_4  | A9                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC7_0  | B8                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC7_1  | E10                | General IO   | $V_{DD\_IO}$          | _     |

| PSC7_2  | C8                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC7_3  | A8                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC7_4  | A7                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC8_0  | E9                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC8_1  | D8                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC8_2  | C7                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC8_3  | B6                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC8_4  | E8                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC9_0  | C6                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC9_1  | D7                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC9_2  | E7                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC9_3  | D6                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC9_4  | E6                 | General IO   | $V_{DD\_IO}$          | _     |

| PSC10_0 | C13                | General IO   | $V_{DD\_IO}$          | _     |

| PSC10_1 | B13                | General IO   | $V_{DD\_IO}$          | _     |

| PSC10_2 | A13                | General IO   | $V_{DD\_IO}$          | _     |

| PSC10_3 | C12                | General IO   | $V_{DD\_IO}$          | _     |

| PSC10_4 | E12                | General IO   | $V_{DD\_IO}$          | _     |

| PSC11_0 | A12                | General IO   | $V_{\mathrm{DD\_IO}}$ |       |

| PSC11_1 | B11                | General IO   | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC11_2 | C11                | General IO   | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC11_3 | E11                | General IO   | $V_{\mathrm{DD\_IO}}$ | _     |

| PSC11_4 | D11                | General IO   | $V_{\mathrm{DD\_IO}}$ | _     |

|         | JTA                | AG (5 Total) |                       |       |

| TCK     | AB26               | General IO   | $V_{DD\_IO}$          | 2     |

|         |                    |              |                       |       |

MPC5121E/MPC5123 Data Sheet, Rev. 5

# **Pin Assignments**

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 9 of 12)

| Signal    | Package Pin Number   | Pad Type          | Power Supply       | Notes                   |

|-----------|----------------------|-------------------|--------------------|-------------------------|

| TDI       | Y23                  | General IO        | $V_{DD\_IO}$       | 3                       |

| TDO       | W22                  | General IO        | $V_{DD\_IO}$       | _                       |

| TMS       | Y25                  | General IO        | $V_{DD\_IO}$       | 3                       |

| TRST      | AA26                 | General IO        | $V_{DD\_IO}$       | 3                       |

|           | Test / I             | Debug (2 Total)   |                    |                         |

| TEST      | W25                  | General IO        | $V_{DD\_IO}$       | 4, 5                    |

| CKSTP_OUT | Y26                  | General IO        | $V_{DD\_IO}$       | _                       |

|           | System               | Control (3 Total  | )                  |                         |

| HRESET    | W24                  | General IO        | $V_{DD\_IO}$       | 6, 2                    |

| PORESET   | W23                  | General IO        | $V_{DD\_IO}$       | 4, 2                    |

| SRESET    | V22                  | General IO        | V <sub>DD_IO</sub> | 6, 2                    |

|           | System               | Clock (2 Total)   |                    |                         |

| SYS_XTALI | V24                  | Analog Input      | SYS_PLL_AVDD       | Oscillator Input        |

| SYS_XTALO | W26                  | Analog Output     | SYS_PLL_AVDD       | Oscillator Output       |

|           | RT                   | C (3 Total)       |                    |                         |

| RTC_XTALI | C20                  | Analog Input      | VBAT_RTC           | Oscillator Input        |

| RTC_XTALO | A20                  | Analog Output     | VBAT_RTC           | Oscillator Output       |

| HIB_MODE  | D18                  | Analog Output     | VBAT_RTC           | _                       |

|           | GP Inp               | ut Only (4 Total) |                    |                         |

| GPIO28    | A19                  | Analog Input      | VBAT_RTC           | _                       |

| GPIO29    | E17                  | Analog Input      | VBAT_RTC           | _                       |

| GPIO30    | C18                  | Analog Input      | VBAT_RTC           | _                       |

| GPIO31    | B18                  | Analog Input      | VBAT_RTC           | _                       |

|           | DDR Re               | ference Voltage   | •                  |                         |

| MVREF     | AB11                 | Analog Input      | Voltage Reference  | for SSTL input pads     |

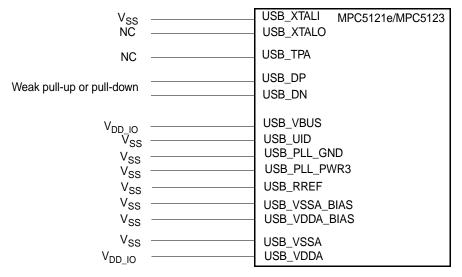

| U         | SB – PHY without Pow | er and Ground     | Supplies (7 Total) |                         |

| USB_XTALI | C24                  | Analog Input      | USB_PLL_PWR3       | Oscillator Input        |

| USB_XTALO | B24                  | Analog Output     | USB_PLL_PWR3       | Oscillator Output       |

| USB_DP    | A23                  | Analog IO         | USB_VDDA           | _                       |

| USB_DM    | A22                  | Analog IO         | USB_VDDA           | _                       |

| USB_TPA   | A24                  | Analog Output     | _                  | USB PHY<br>debug output |

| USB_VBUS  | D21                  | Analog IO         | _                  | _                       |

|           |                      |                   |                    |                         |

MPC5121E/MPC5123 Data Sheet, Rev. 5

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 10 of 12)

| Signal                    | Package Pin Number                                                                                                                                                                                                | Pad Type        | Power Supply       | Notes                 |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|-----------------------|--|--|--|

| USB_UID                   | E19                                                                                                                                                                                                               | Analog Input    | _                  | _                     |  |  |  |

| USB digital IOs (2 Total) |                                                                                                                                                                                                                   |                 |                    |                       |  |  |  |

| USB2_VBUS_PWR_FA<br>ULT   | B21                                                                                                                                                                                                               | General IO      | $V_{DD\_IO}$       | _                     |  |  |  |

| USB2_DRVVBUS              | A21                                                                                                                                                                                                               | General IO      | $V_{DD\_IO}$       | _                     |  |  |  |

| s                         | ATA PHY without Powe                                                                                                                                                                                              | er and Ground S | Supplies (7 Total) |                       |  |  |  |

| SATA_XTALI                | C3                                                                                                                                                                                                                | Analog Input    | SATA_VDDA_3P3      | Oscillator Input      |  |  |  |

| SATA_XTALO                | C2                                                                                                                                                                                                                | Analog Output   | SATA_VDDA_3P3      | Oscillator Output     |  |  |  |

| SATA_ANAVIZ               | E5                                                                                                                                                                                                                | Analog Output   | _                  | SATA PHY debug output |  |  |  |

| SATA_TXN                  | E1                                                                                                                                                                                                                | Analog Output   | SATA_VDDA_1P2      | _                     |  |  |  |

| SATA_TXP                  | F1                                                                                                                                                                                                                | Analog Output   | SATA_VDDA_1P2      | _                     |  |  |  |

| SATA_RXP                  | A5                                                                                                                                                                                                                | Analog Input    | SATA_VDDA_1P2      | _                     |  |  |  |

| SATA_RXN                  | A4                                                                                                                                                                                                                | Analog Input    | SATA_VDDA_1P2      | _                     |  |  |  |

| Powe                      | er and Ground Supplie                                                                                                                                                                                             | s (without SATA | PHY and USB PHY    | )                     |  |  |  |

| V <sub>DD_</sub> CORE     | K10, K11, K12, K13,<br>K14, K15, K16, K17,<br>L10, L17, M10, M17,<br>N10, N17, P10, P17,<br>R10, R17, T10, T17,<br>U10, U11, U12, U13,<br>U14, U15, U16, U17                                                      | Power           | _                  | _                     |  |  |  |

| V <sub>DD_IO</sub>        | B10, B15, B25, D9,<br>D10, D15, F11, F13,<br>F14, F19, F23, F25,<br>H21, J5, K2, K4, L23,<br>L25, N6, N21, P6,<br>P21, R2, R4, T23,<br>T25, W6, W21, Y2,<br>Y4, AA23, AA25, AE1,<br>AE2, AE24, AE25,<br>AF2, AF25 | Power           | _                  | _                     |  |  |  |

| V <sub>DD_MEM_IO</sub>    | AA8, AA13, AA14,<br>AB18, AC5, AC10,<br>AC14, AC20, AD9,<br>AE5, AE10, AE15,<br>AE20                                                                                                                              | Power           | _                  | _                     |  |  |  |

# **Pin Assignments**

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 11 of 12)

| Signal          | Package Pin Number                                                                                                                                                                                                                                                                                                                      | Pad Type        | Power Supply      | Notes                |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|----------------------|

| V <sub>SS</sub> | A2, A3, A25, B1,B2,<br>B3, B5, B7, B12, B17,<br>B20, B22, B26, C1,<br>C4, C23, C25, D2,<br>D12, D17, D24, D25,<br>E18, F2, F3, F4, F5,<br>F6, F8, F10, F16, F17,<br>F21, G5, H6, H23,<br>H25, K6, K21, L6, L11,<br>L12, L13, L14, L15,<br>L16, L21, M2, M4,<br>M11, M12, M13, M14,<br>M15, M16, N5, N11,<br>N12, N13, N14, N15,<br>N16, | Ground          | _                 | _                    |

| V <sub>SS</sub> | N23, N25, P11, P12, P13, P14, P15, P16, R11, R12, R13, R14, R15, R16, T6, T11, T12, T13, T14, T15, T16, T21, U2, U4, U6, U21, V23, V25, Y24, AA6, AA10, AA11, AA16, AA17, AA21, AB2, AB4, AB10, AB24, AC8, AC12, AC17, AC22, AD3, AD25, AE7, AE12, AE17, AE23, AE26                                                                     | Ground          | _                 | _                    |

| SYS_PLL_AVDD    | T22                                                                                                                                                                                                                                                                                                                                     | Analog Power    | _                 | _                    |

| SYS_PLL_AVSS    | U22                                                                                                                                                                                                                                                                                                                                     | Analog Ground   | _                 | _                    |

| CORE_PLL_AVDD   | AA19                                                                                                                                                                                                                                                                                                                                    | Analog Power    | _                 | _                    |

| CORE_PLL_AVSS   | AD23                                                                                                                                                                                                                                                                                                                                    | Analog Ground   | _                 | _                    |

| VBAT_RTC        | D19                                                                                                                                                                                                                                                                                                                                     | Power           | _                 | _                    |

| AVDD_FUSEWR     | C9                                                                                                                                                                                                                                                                                                                                      | Power           | _                 | _                    |

| MVTT0           | AB7                                                                                                                                                                                                                                                                                                                                     | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

| MVTT1           | AF9                                                                                                                                                                                                                                                                                                                                     | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

| MVTT2           | AE11                                                                                                                                                                                                                                                                                                                                    | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

| MVTT3           | AE14                                                                                                                                                                                                                                                                                                                                    | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

|                 | Power and Grou                                                                                                                                                                                                                                                                                                                          | und Supplies (U | SB PHY)           |                      |

| USB_PLL_GND     | E23                                                                                                                                                                                                                                                                                                                                     | Analog Ground   | _                 | _                    |

| USB_PLL_PWR3    | D23                                                                                                                                                                                                                                                                                                                                     | Analog Power    | _                 | _                    |

| USB_RREF        | E22                                                                                                                                                                                                                                                                                                                                     | Analog Power    | _                 | _                    |

| USB_VSSA_BIAS   | B23                                                                                                                                                                                                                                                                                                                                     | Analog Ground   | _                 | _                    |

MPC5121E/MPC5123 Data Sheet, Rev. 5

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 12 of 12)

| Signal           | Package Pin Number | Pad Type        | Power Supply | Notes |

|------------------|--------------------|-----------------|--------------|-------|

| USB_VDDA_BIAS    | D22                | Analog Power    | _            | _     |

| USB_VSSA         | C22, E20, E21      | Analog Ground   | <del>-</del> | _     |

| USB_VDDA         | C21, D20           | Analog Power    | _            | _     |

|                  | Power and Grou     | nd Supplies (SA | ATA PHY)     |       |

| SATA_RESREF      | E4                 | Analog Power    | _            | _     |

| SATA_VDDA_3P3    | D4                 | Analog Power    | <del>-</del> | _     |

| SATA_VDDA_1P2    | C5, D1, E2         | Analog Power —  |              | _     |

| SATA_VDDA_VREG   | D5                 | Analog Power    | _            | _     |

| SATA_PLL_VDDA1P2 | E3                 | Analog Power    | _            | _     |

| SATA_PLL_VSSA    | D3                 | Analog Ground   | _            | _     |

| SATA_RX_VSSA     | A6, B4             | Analog Ground   | _            | _     |

| SATA_TX_VSSA     | G1                 | Analog Ground   | _            | _     |

This pins should have an external pull-up resistor. Follow PCI specification and see System Design Information.

### **NOTE**

This table indicates only the pins with permananently enabled internal pull-up, pull-down, or Schmitt trigger. Most of the digital I/O pins can be configured to enable internal pull-up, pull-down, or Schmitt trigger. See the *MPC5121e Microcontroller Reference Manual*, IO Control chapter.

<sup>&</sup>lt;sup>2</sup> This pin contains an enabled internal Schmitt trigger.

<sup>&</sup>lt;sup>3</sup> These JTAG pins have internal pull-up P-FETs. This pin can not be configured.

<sup>&</sup>lt;sup>4</sup> This pin is an input only. This pin can not be configured.

$<sup>^{5}</sup>$  This test pin must be tied to  $V_{SS}$ .

This pin is an input or open-drain output. This pin can not be configured. There is an internal pull-up resistor implemented.

# 3.1 DC Electrical Characteristics

# 3.1.1 Absolute Maximum Ratings

The tables in this section describe the MPC5121e/MPC5123 DC Electrical characteristics. Table 4 gives the absolute maximum ratings.

Table 4. Absolute Maximum Ratings<sup>1</sup>

| Characteristic                                  | Symbol                                      | Min  | Max                             | Unit | SpecID |

|-------------------------------------------------|---------------------------------------------|------|---------------------------------|------|--------|

| Supply voltage – e300 core and peripheral logic | V <sub>DD_CORE</sub>                        | -0.3 | 1.47                            | V    | D1.1   |

| Supply voltage – I/O buffers                    | V <sub>DD_IO</sub> , V <sub>DD_MEM_IO</sub> | -0.3 | 3.6                             | V    | D1.2   |

| Input reference voltage (DDR/DDR2)              | MVREF                                       | -0.3 | 3.6                             | V    |        |

| Termination Voltage (DDR2)                      | MVTT                                        | -0.3 | 3.6                             | V    |        |

| Supply voltage – System APLL, System Oscillator | SYS_PLL_AVDD                                | -0.3 | 3.6                             | V    | D1.3   |

| Supply voltage – e300 APLL                      | CORE_PLL_AVDD                               | -0.3 | 3.6                             | V    | D1.4   |

| Supply voltage – RTC (Hibernation)              | VBAT_RTC                                    | -0.3 | 3.6                             | V    | D1.5   |

| Supply voltage – FUSE Programming               | AVDD_FUSEWR                                 | -0.3 | 3.6                             | V    | D1.6   |

| Supply voltage – SATA PHY analog                | SATA_VDDA_3P3                               | -0.3 | 3.6                             | V    | D1.8   |

| Supply voltage – SATA PHY voltage regulator     | SATA_VDDA_VREG                              | -0.3 | 2.6                             | V    | D1.9   |

| Supply voltage – SATA PHY Tx/Rx                 | SATA_VDDA_1P2                               | -0.3 | 1.47                            | V    | D1.10  |

| Supply voltage – SATA PHY PLL                   | SATA_PLL_VDDA1P2                            | -0.3 | 1.47                            | V    | D1.11  |

| Supply voltage – USB PHY PLL and OSC            | USB_PLL_PWR3                                | -0.3 | 3.6                             | V    | D1.12  |

| Supply voltage – USB PHY transceiver            | USB_VDDA                                    | -0.3 | 3.6                             | V    | D1.13  |

| Supply voltage – USB PHY bandgap bias           | USB_VDDA_BIAS                               | -0.3 | 3.6                             | V    | D1.14  |

| Input voltage – USB PHY cable                   | USB_VBUS                                    | -0.3 | 3.6                             | V    | D1.15  |

| Input voltage (V <sub>DD_IO</sub> )             | Vin                                         | -0.3 | V <sub>DD_IO</sub><br>+ 0.3     | V    | D1.16  |

| Input voltage (V <sub>DD_MEM_IO</sub> )         | Vin                                         | -0.3 | V <sub>DD_MEM_IO</sub><br>+ 0.3 | V    | D1.17  |

| Input voltage (VBAT_RTC)                        | Vin                                         | -0.3 | VBAT_RTC<br>+ 0.3               | V    | D1.18  |

| Input voltage overshoot                         | Vinos                                       | _    | 1                               | V    | D1.19  |

| Input voltage undershoot                        | Vinus                                       | _    | 1                               | V    | D1.20  |

| Storage temperature range                       | Tstg                                        | -55  | 150                             | οС   | D1.21  |

Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage.

# 3.1.2 Recommended Operating Conditions

Table 5 gives the recommended operating conditions.

Table 5. Recommended Operating Conditions

| Characteristic                                                        | Symbol                                                      | Min <sup>1</sup>                 | Тур                              | Max <sup>1</sup>                 | Unit | SpecID |

|-----------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|------|--------|

| Supply voltage – e300 core and peripheral logic                       | $V_{DD\_CORE}$                                              | 1.33                             | 1.4                              | 1.47                             | V    | D2.1   |

| State Retention voltage – e300 core and peripheral logic <sup>2</sup> |                                                             | 1.08                             | _                                | _                                | V    | D2.2   |

| Supply voltage – standard I/O buffers                                 | $V_{DD\_IO}$                                                | 3.0                              | 3.3                              | 3.6                              | V    | D2.3   |

| Supply voltage – memory I/O buffers (DDR)                             | V <sub>DD_MEM_IO_DDR</sub>                                  | 2.3                              | 2.5                              | 2.7                              | V    | D2.4   |

| Supply voltage – memory I/O buffers (DDR2, LPDDR)                     | V <sub>DD_MEM_IO_DDR2</sub><br>V <sub>DD_MEM_IO_LPDDR</sub> | 1.7                              | 1.8                              | 1.9                              | V    | D2.5   |

| Input Reference Voltage (DDR/DDR2)                                    | MVREF                                                       | 0.49 ×<br>V <sub>DD_MEM_IO</sub> | 0.50 ×<br>V <sub>DD_MEM_IO</sub> | 0.51 x<br>V <sub>DD_MEM_IO</sub> | V    | D2.6   |

| Termination Voltage (DDR2)                                            | MVTT                                                        | MVREF<br>- 0.04                  | MVREF                            | MVREF<br>+ 0.04                  | V    | D2.7   |

| Supply voltage – System APLL, System Oscillator                       | SYS_PLL_AVDD                                                | 3.0                              | 3.3                              | 3.6                              | V    | D2.8   |

| Supply voltage – e300 APLL                                            | CORE_PLL_AVDD                                               | 3.0                              | 3.3                              | 3.6                              | V    | D2.9   |

| Supply voltage – RTC (Hibernation) <sup>3</sup>                       | VBAT_RTC                                                    | 3.0                              | 3.3                              | 3.6                              | V    | D2.10  |

| Supply voltage – FUSE Programming                                     | AVDD_FUSEWR                                                 | 3.3                              |                                  | 3.6                              | V    | D2.11  |

| Supply voltage – SATA PHY analog and OSC                              | SATA_VDDA_3P3                                               | 3.0                              | 3.3                              | 3.6                              | V    | D2.13  |

| Supply voltage – SATA PHY voltage regulator                           | SATA_VDDA_VREG                                              | 1.7                              |                                  | 2.6                              | V    | D2.14  |

| Supply voltage – SATA PHY Tx/Rx                                       | SATA_VDDA_1P2                                               | 1.14                             | 1.2                              | 1.47                             | V    | D2.15  |

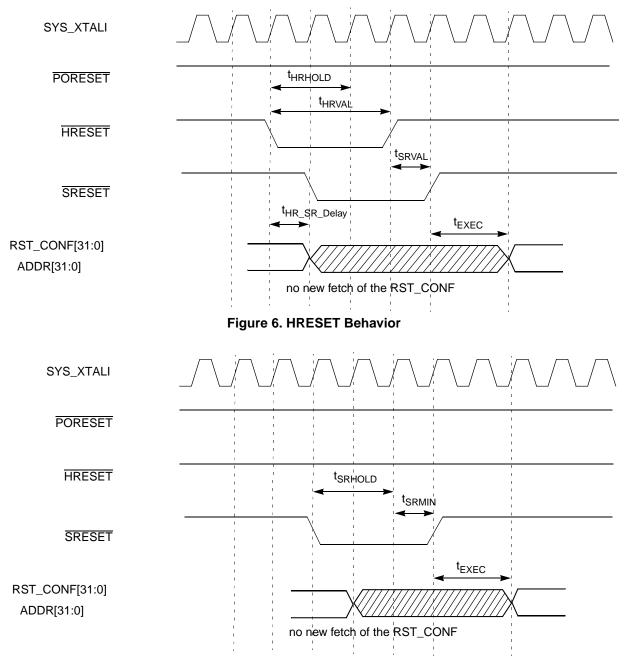

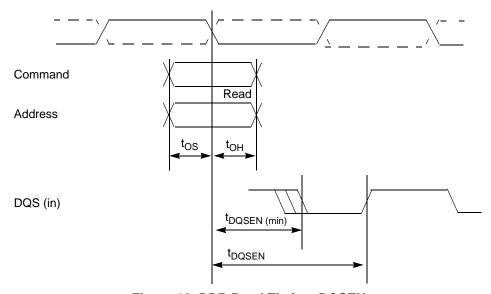

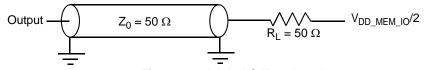

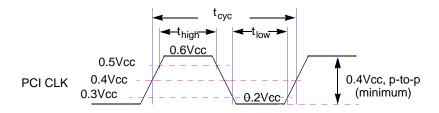

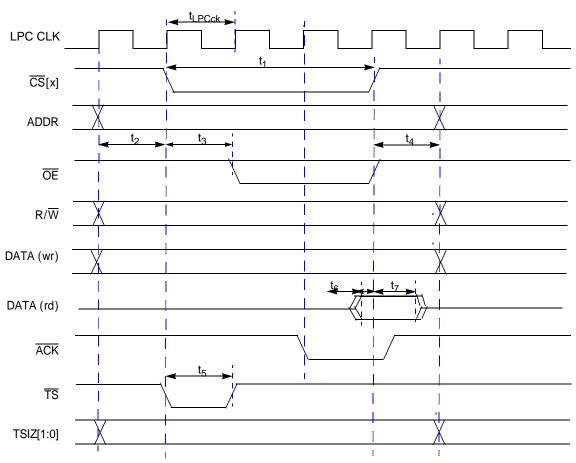

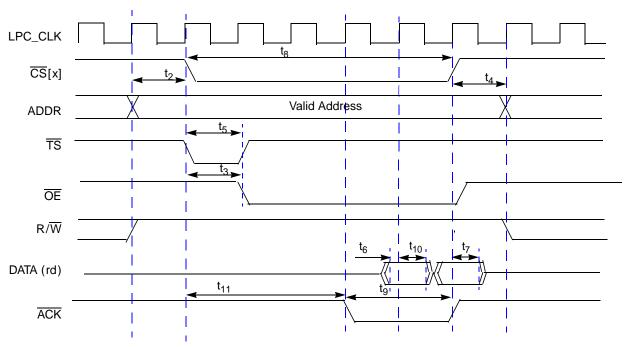

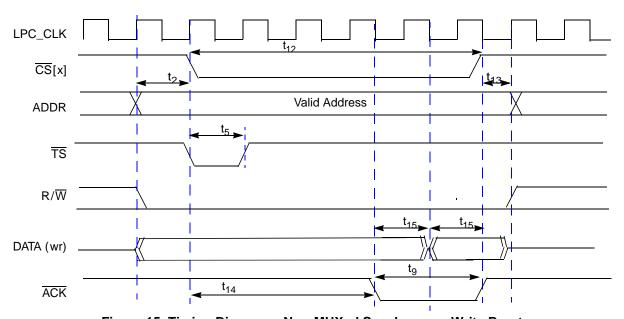

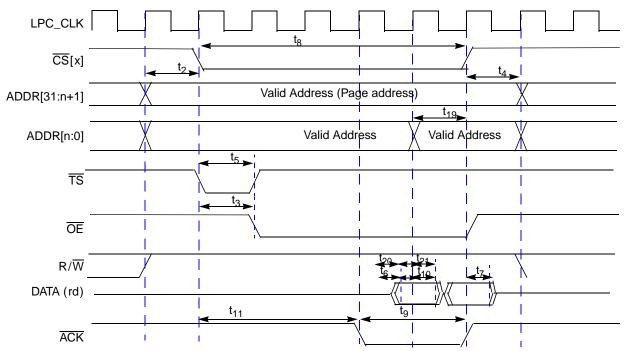

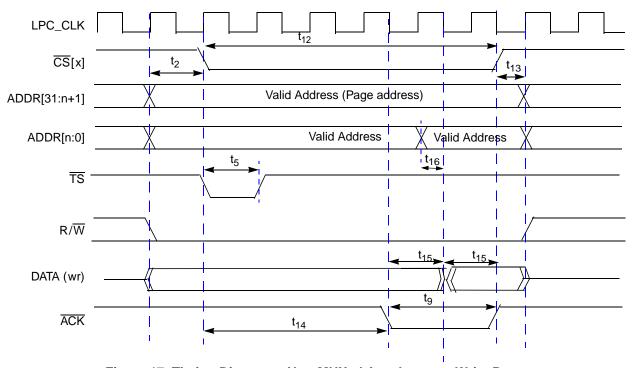

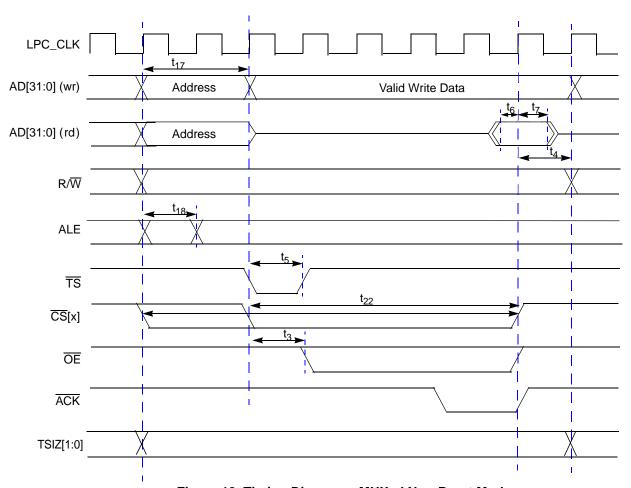

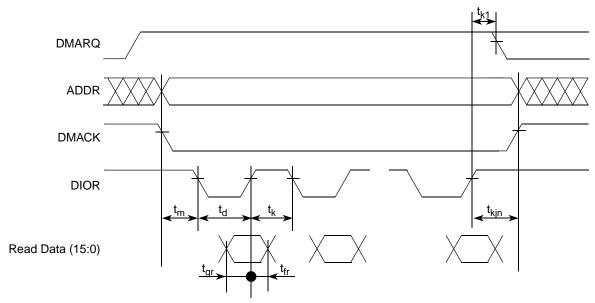

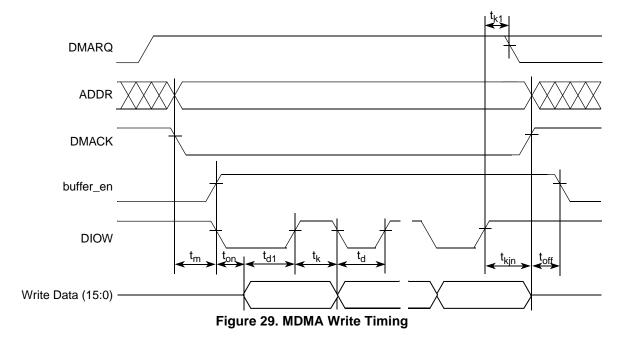

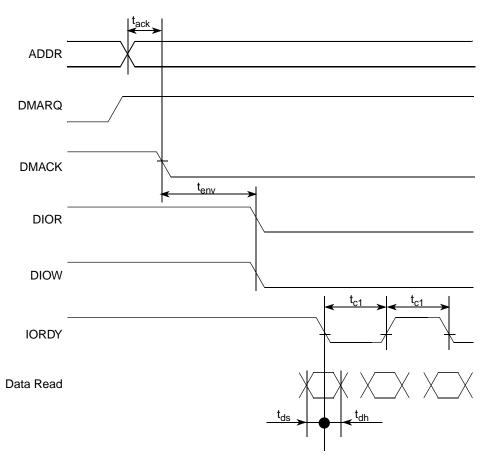

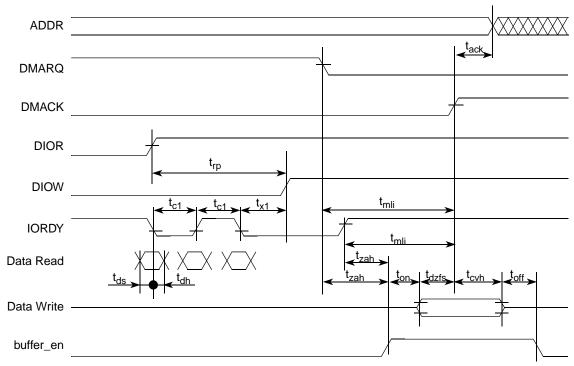

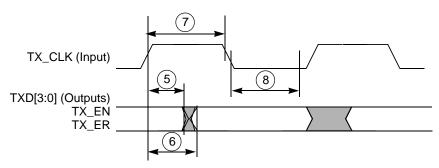

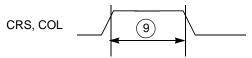

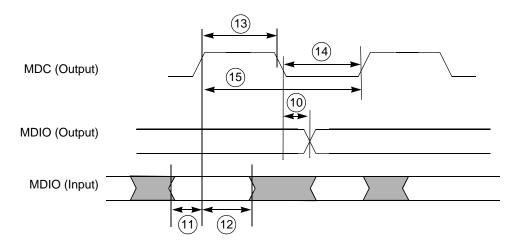

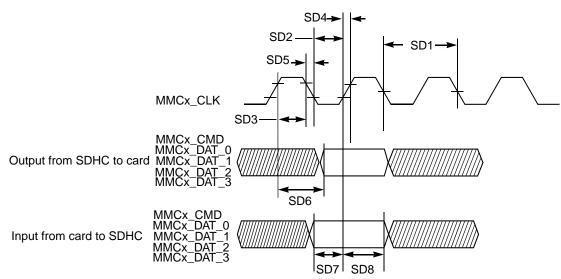

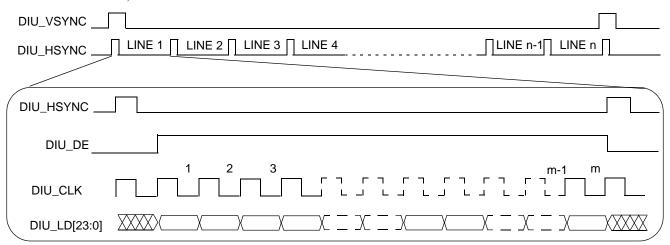

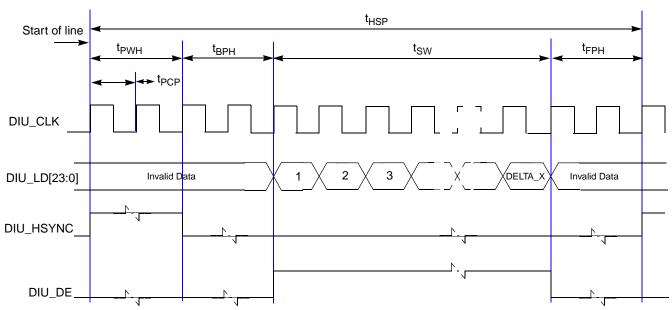

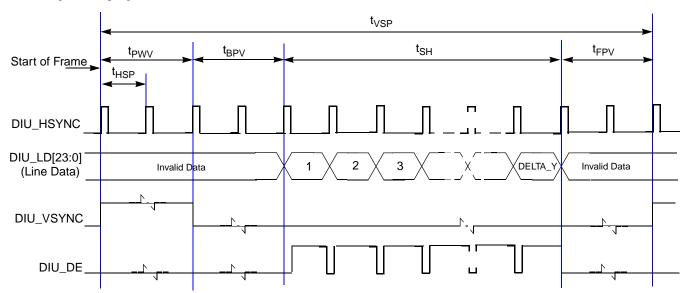

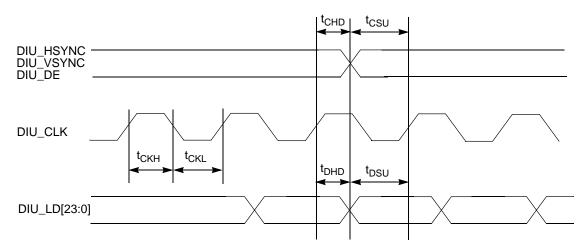

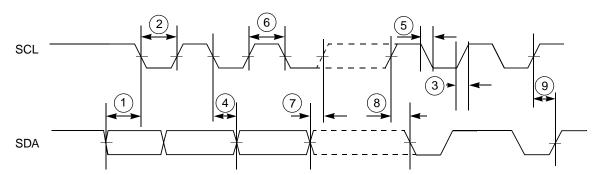

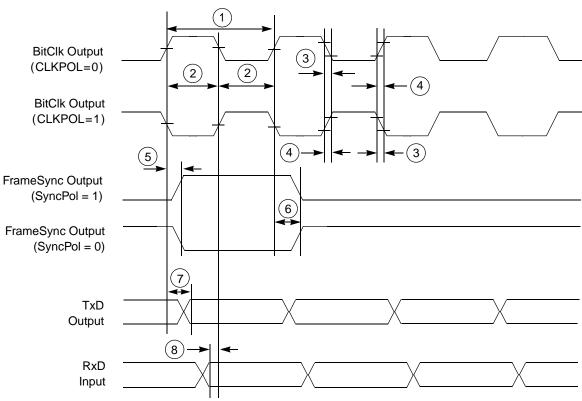

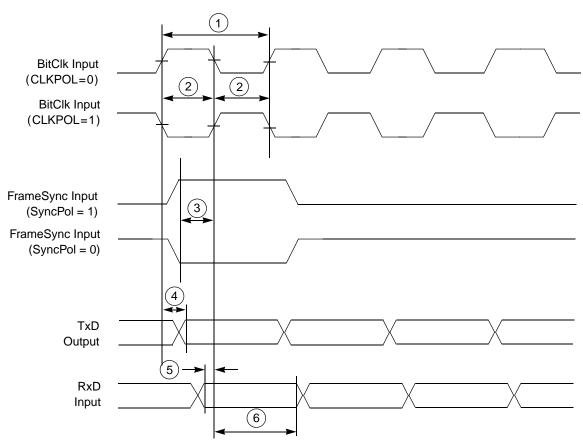

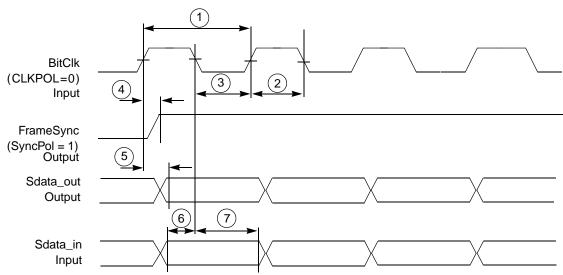

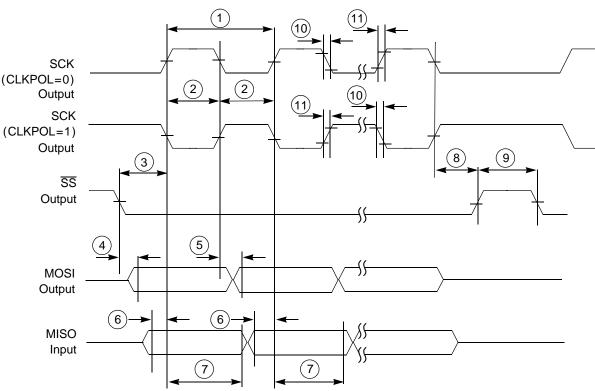

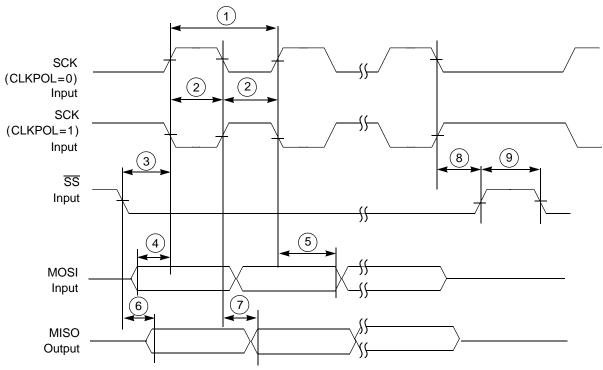

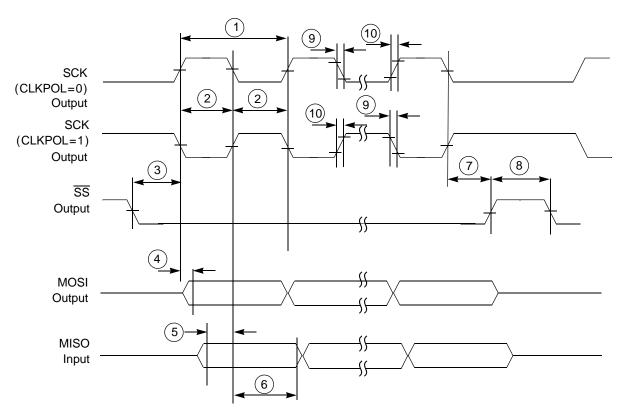

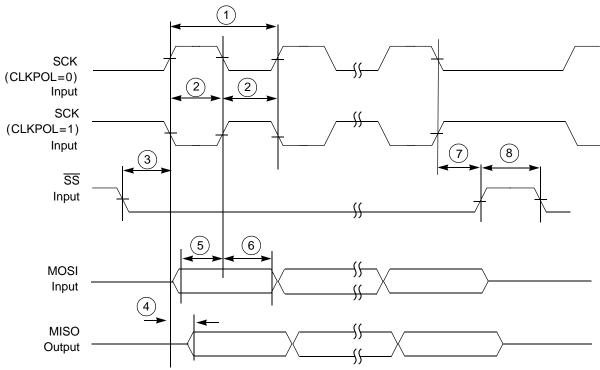

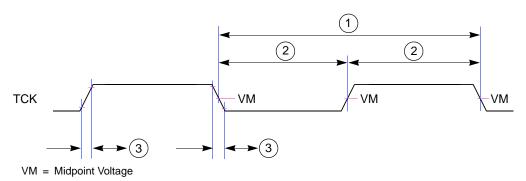

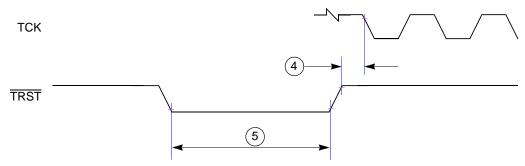

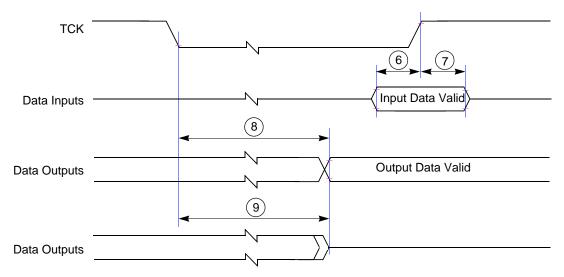

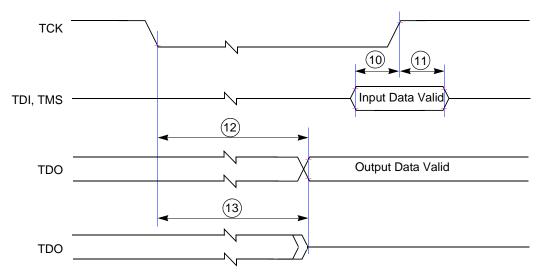

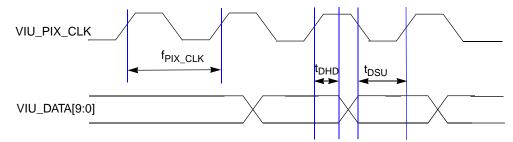

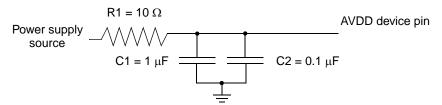

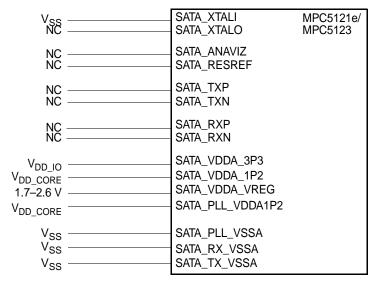

| Supply voltage – SATA PHY PLL                                         | SATA_PLL_VDDA1P2                                            | 1.33                             | 1.4                              | 1.47                             | V    | D2.16  |