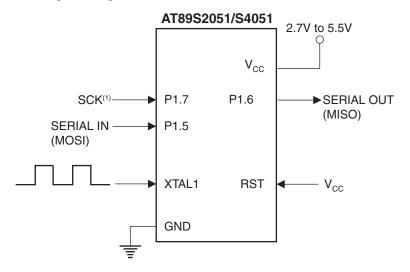

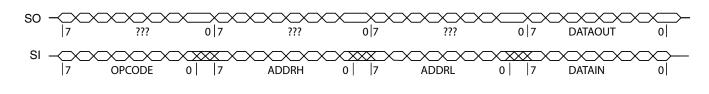

The on-board Flash program memory is accessible through the ISP serial interface. Holding RST active forces the device into a serial programming interface and allows the program memory to be written to or read from, unless one or more lock bits have been activated.

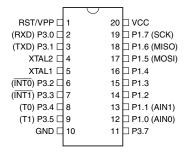

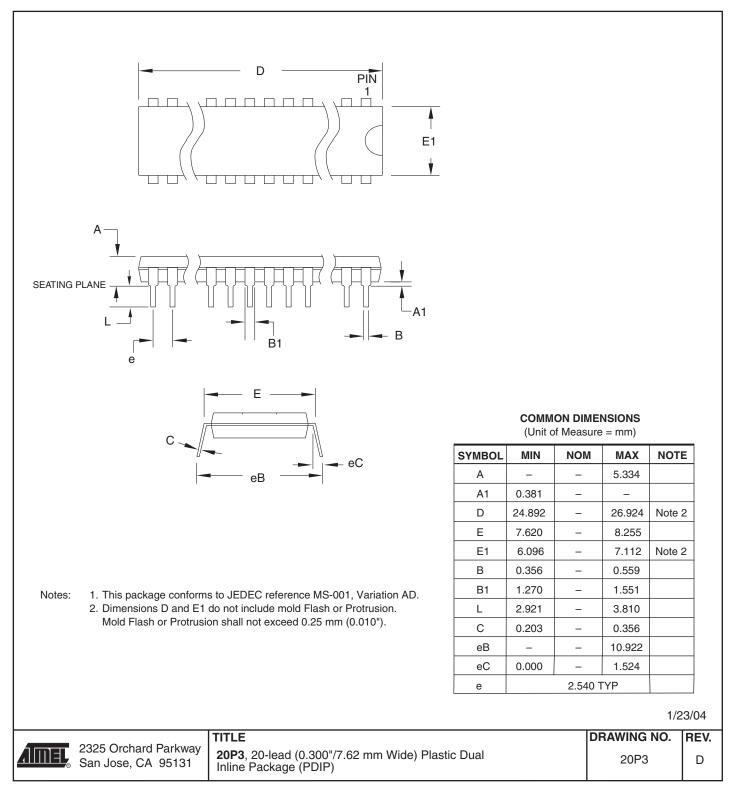

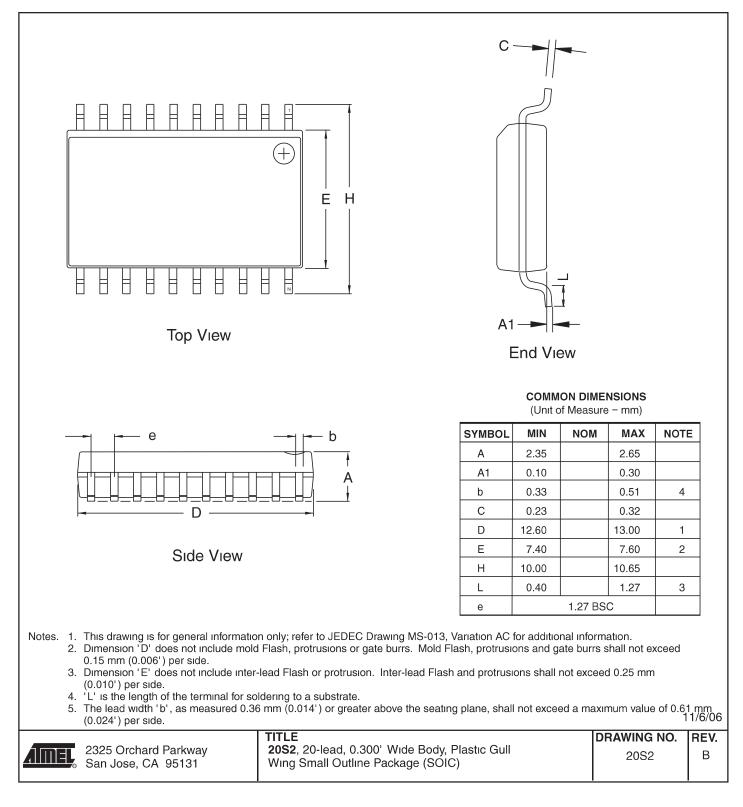

# 2. Pin Configuration

#### 2.1 20-lead PDIP/SOIC

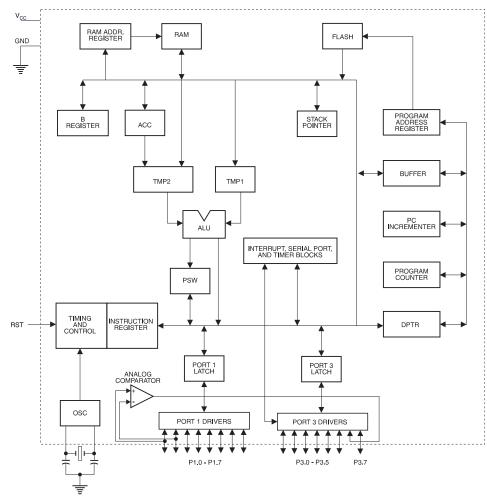

## 3. Block Diagram

AT89S2051/S4051

Downloaded from Arrow.com.

2

# 4. Pin Description

4.1 VCC

Supply voltage.

4.2 GND

Ground.

#### 4.3 Port 1

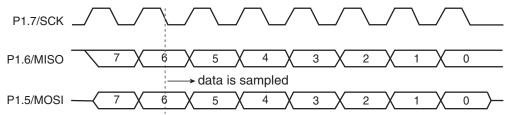

Port 1 is an 8-bit bi-directional I/O port. Port pins P1.2 to P1.7 provide internal pull-ups. P1.0 and P1.1 require external pull-ups. P1.0 and P1.1 also serve as the positive input (AIN0) and the negative input (AIN1), respectively, of the on-chip precision analog comparator. The Port 1 output buffers can sink 20 mA and can drive LED displays directly. When 1s are written to Port 1 pins, they can be used as inputs. When pins P1.2 to P1.7 are used as inputs and are externally pulled low, they will source current ( $I_{IL}$ ) because of the internal pull-ups.

Port 1 also receives code data during Flash programming and verification.

| Port Pin | Alternate Functions                                              |

|----------|------------------------------------------------------------------|

| P1.5     | MOSI (Master data output, slave data input pin for ISP channel)  |

| P1.6     | MISO (Master data input, slave data output pin for ISP channel)  |

| P1.7     | SCK (Master clock output, slave clock input pin for ISP channel) |

#### 4.4 Port 3

Port 3 pins P3.0 to P3.5, P3.7 are seven bi-directional I/O pins with internal pull-ups. P3.6 is hard-wired as an input to the output of the on-chip comparator and is not accessible as a general-purpose I/O pin. The Port 3 output buffers can sink 20 mA. When 1s are written to Port 3 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{IL}$ ) because of the pull-ups.

Port 3 also serves the functions of various special features of the AT89S2051/S4051 as listed below:

| Port Pin | Alternate Functions                     |

|----------|-----------------------------------------|

| P3.0     | RXD (serial input port)                 |

| P3.1     | TXD (serial output port)                |

| P3.2     | INT0 (external interrupt 0)             |

| P3.3     | INT1 (external interrupt 1)             |

| P3.4     | T0 (timer 0 external input)             |

| P3.5     | T1 (timer 1 external input)/ PWM output |

Port 3 also receives some control signals for Flash programming and verification.

| 4.5 | RST   |                                                                                                      |

|-----|-------|------------------------------------------------------------------------------------------------------|

|     |       | Reset input. Holding the RST pin high for two machine cycles while the is running resets the device. |

|     |       | Each machine cycle takes 6 or clock cycles.                                                          |

| 4.6 | XTAL1 | Input to the inverting amplifier and input to the internal clock operating circuit.                  |

| 4.7 | XTAL2 | Output from the inverting amplifier.                                                                 |

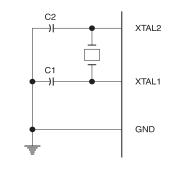

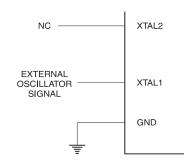

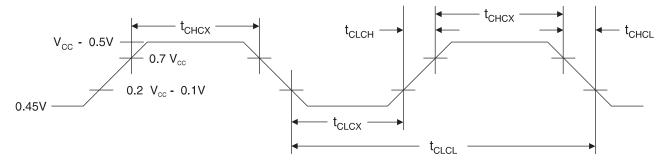

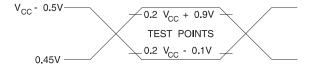

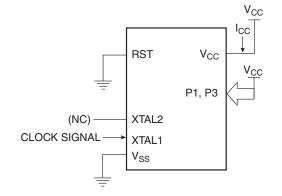

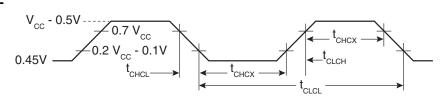

## 5. Characteristics

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip, as shown in Figure 5-1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 5-2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

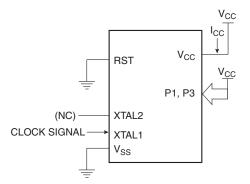

Figure 5-1. Connections

Note: C1, C2 = 5 pF  $\pm$ 5 pF for Crystals = 5 pF  $\pm$ 5 pF for Ceramic Resonators

#### Figure 5-2. External Clock Drive Configuration

# AT89S2051/S4051

4

## 6. X2 Mode Description

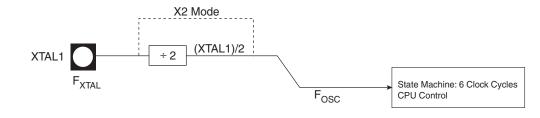

The clock for the entire circuit and peripherals is normally divided by 2 before being used by the CPU core and peripherals. This allows any cyclic ratio (duty cycle) to be accepted on XTAL1 input. In X2 mode this divider is bypassed. Figure 6-1 shows the clock generation block diagram.

Figure 6-1. Clock Generation Block Diagram

## 7. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 7-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future products to invoke new features. In that case, the reset or inactive values of the new bits will always be 0.

|      |                  |                   |                 |                 |                 | i               |                    | •    |

|------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|--------------------|------|

| 0F8H |                  |                   |                 |                 |                 |                 |                    | 0FFH |

| 0F0H | B<br>00000000    |                   |                 |                 |                 |                 |                    | 0F7H |

| 0E8H |                  |                   |                 |                 |                 |                 |                    | 0EFH |

| 0E0H | ACC<br>00000000  |                   |                 |                 |                 |                 |                    | 0E7H |

| 0D8H |                  |                   |                 |                 |                 |                 |                    | 0DFH |

| 0D0H | PSW<br>00000000  |                   |                 |                 |                 |                 |                    | 0D7H |

| 0C8H |                  |                   |                 |                 |                 |                 |                    | 0CFH |

| 0C0H |                  |                   |                 |                 |                 |                 |                    | 0C7H |

| 0B8H | IP<br>X0X00000   | SADEN<br>00000000 |                 |                 |                 |                 |                    | 0BFH |

| 0B0H | P3<br>11111111   |                   |                 |                 |                 |                 | IPH<br>X0X00000    | 0B7H |

| 0A8H | IE<br>00X00000   | SADDR<br>00000000 |                 |                 |                 |                 |                    | 0AFH |

| 0A0H |                  |                   |                 |                 |                 |                 |                    | 0A7H |

| 98H  | SCON<br>00000000 | SBUF<br>XXXXXXXX  |                 |                 |                 |                 |                    | 9FH  |

| 90H  | P1<br>11111111   |                   |                 |                 |                 |                 | ACSR<br>XXX00000   | 97H  |

| 88H  | TCON<br>00000000 | TMOD<br>00000000  | TL0<br>00000000 | TL1<br>00000000 | TH0<br>00000000 | TH1<br>00000000 | CLKREG<br>XXXXXX0X | 8FH  |

| 80H  |                  | SP<br>00000111    | DPL<br>00000000 | DPH<br>00000000 |                 |                 | PCON<br>000X0000   | 87H  |

#### Table 7-1. AT89S2051/S4051 SFR Map and Reset Values

# 8. Restrictions on Certain Instructions

The AT89S2051/S4051 is an economical and cost-effective member of Atmel's family of microcontrollers. It contains 2K/4K bytes of Flash program memory. It is fully compatible with the MCS-51 architecture, and can be programmed using the MCS-51 instruction set. However, there are a few considerations one must keep in mind when utilizing certain instructions to program this device.

All the instructions related to jumping or branching should be restricted such that the destination address falls within the physical program memory space of the device, which is 2K/4K for the AT89S2051/S4051. This should be the responsibility of the software programmer. For example, LJMP 7E0H would be a valid instruction for the AT89S2051 (with 2K of memory), whereas LJMP 900H would not.

## 8.1 Branching Instructions

LCALL, LJMP, ACALL, AJMP, SJMP, JMP @A+DPTR. These unconditional branching instructions will execute correctly as long as the programmer keeps in mind that the destination branching address must fall within the physical boundaries of the program memory size (locations 00H to 7FFH/FFFH for the AT89S2051/S4051). Violating the physical space limits may cause unknown program behavior.

**CJNE** [...], **DJNZ** [...], **JB**, **JNB**, **JC**, **JNC**, **JBC**, **JZ**, **JNZ**. With these conditional branching instructions, the same rule above applies. Again, violating the memory boundaries may cause erratic execution.

For applications involving interrupts, the normal interrupt service routine address locations of the 80C51 family architecture have been preserved.

#### 8.2 MOVX-related Instructions, Data Memory

The AT89S2051/S4051 contains 256 bytes of internal data memory. External DATA memory access is not supported in this device, nor is external PROGRAM memory execution. Therefore, no MOVX [...] instructions should be included in the program.

A typical 80C51 assembler will still assemble instructions, even if they are written in violation of the restrictions mentioned above. It is the responsibility of the user to know the physical features and limitations of the device being used and adjust the instructions used accordingly.

# 9. Program Memory Lock Bits

On the chip are two lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in Table 9-1:

| Program Lock Bits |     |     |                                               |

|-------------------|-----|-----|-----------------------------------------------|

|                   | LB1 | LB2 | Protection Type                               |

| 1                 | U U |     | No program lock features.                     |

| 2                 | Р   | U   | Further programming of the Flash is disabled. |

| 3                 | Р   | Р   | Same as mode 2, also verify is disabled.      |

**Table 9-1.**Lock Bit Protection Modes<sup>(1)</sup>

Note: 1. The Lock Bits can only be erased with the Chip Erase operation.

## 10. Reset

During reset, all I/O Registers are set to their initial values, the port pins are weakly pulled to  $V_{CC}$ , and the program starts execution from the Reset Vector, 0000H. The AT89S2051/S4051 has three sources of reset: power-on reset, brown-out reset, and external reset.

#### 10.1 Power-On Reset

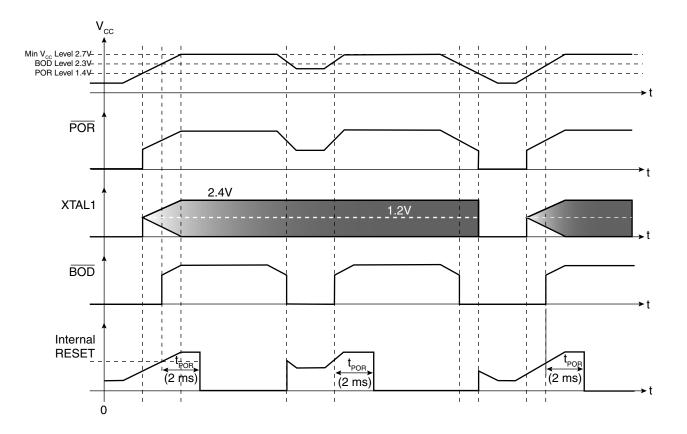

A Power-On Reset (POR) is generated by an on-chip detection circuit. The detection level is nominally 1.4V. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up reset or to detect a supply voltage failure in devices without a brown-out detector. The POR circuit ensures that the device is reset from power-on. When  $V_{CC}$  reaches the Power-on Reset threshold voltage, the Pierce Oscillator is enabled (if the XTAL Oscillator Bypass fuse is OFF). Only after  $V_{CC}$  has also reached the BOD (brown-out detection) level (see Section 10.2 "Brown-out Reset"), the BOD delay counter starts measuring a 2-ms delay after which the Internal Reset is deasserted and the microcontroller starts executing. The built-in 2-ms delay allows the  $V_{CC}$  voltage to reach the minimum 2.7V level before executing, thus guaranteeing the maximum operating clock frequency. The POR signal is activated again, without any delay, when  $V_{CC}$  falls below the POR threshold level. A Power-On Reset (i.e. a cold reset) will set the POF flag in PCON. Refer to Figure 10-1 for details on the POR/BOD behavior.

# AT89S2051/S4051

8

#### 10.2 Brown-out Reset

The AT89S2051/S4051 has an on-chip Brown-out Detection (BOD) circuit for monitoring the  $V_{CC}$  level during operation by comparing it to a fixed trigger level. The trigger level for the BOD is nominally 2.0V. The purpose of the BOD is to ensure that if  $V_{CC}$  fails or dips while executing at speed, the system will gracefully enter reset without the possibility of errors induced by incorrect execution. When  $V_{CC}$  decreases to a value below the trigger level, the Brown-out Reset is immediately activated. When  $V_{CC}$  increases above the trigger level, the BOD delay counter starts the microcontroller after the timeout period has expired in approximately 2 ms.

#### 10.3 External Reset

The RST pin functions as an active-high reset input. The pin must be held high for at least two machine cycles to trigger the internal reset. RST also serves as the In-System Programming (ISP) enable input. ISP mode is enabled when the external reset pin is held high and the ISP Enable fuse is set.

# 11. Clock Register

| EG – Clock Register |

|---------------------|

|                     |

| CLKRE     | EG = 8FH Reset Value = XXXX XX0XB |   |   |   |   |   |       |    |

|-----------|-----------------------------------|---|---|---|---|---|-------|----|

| Not Bit / | Addressable                       |   |   |   |   |   |       |    |

|           | -                                 | _ | _ | _ | - | _ | PWDEX | X2 |

| Bit       | 7                                 | 6 | 5 | 4 | 3 | 2 | 1     | 0  |

| Symbol    | Function                          |   |   |   |   |   |       |    |

| PWDEX | Power-down Exit Mode. When PWDEX = 1, wake up from Power-down is externally controlled. When PWDEX = 0, wake up from Power-down is internally timed.                                                                                                                                                                                                                                                                                                                   |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X2    | When $X2 = 0$ , the frequency (at XTAL1 pin) is internally divided by 2 before it is used as the device system frequency.<br>When $X2 = 1$ , the divide by 2 is no longer used and the XTAL1 frequency becomes the device system frequency. This<br>enables the user to use a 6 MHz crystal instead of a 12 MHz crystal in order to reduce EMI. The X2 bit is initialized on<br>power-up with the value of the X2 user fuse and may be changed at runtime by software. |

## **12. Power Saving Modes**

The AT89S2051/S4051 supports two power-reducing modes: Idle and Power-down. These modes are accessed through the PCON register.

#### 12.1 Idle Mode

Setting the IDL bit in PCON enters idle mode. Idle mode halts the internal CPU clock. The CPU state is preserved in its entirety, including the RAM, stack pointer, program counter, program status word, and accumulator. The Port pins hold the logical states they had at the time that Idle was activated. Idle mode leaves the peripherals running in order to allow them to wake up the CPU when an interrupt is generated. Timer 0, Timer 1, and the UART will continue to function during Idle mode. The analog comparator is disabled during Idle. Any enabled interrupt source or reset may terminate Idle mode. When exiting Idle mode with an interrupt, the interrupt will immediately be serviced, and following RETI, the next instruction to be executed will be the one following the instruction that put the device into Idle.

P1.0 and P1.1 should be set to "0" if no external pull-ups are used, or set to "1" if external pull-ups are used.

#### 12.2 Power-down Mode

Setting the PD bit in PCON enters Power-down mode. Power-down mode stops the and powers down the Flash memory in order to minimize power consumption. Only the power-on circuitry will continue to draw power during Power-down. During Power-down the power supply voltage may be reduced to the RAM keep-alive voltage. The RAM contents will be retained; however, the SFR contents are not guaranteed once  $V_{CC}$  has been reduced. Power-down may be exited by external reset, power-on reset, or certain interrupts.

The user should not attempt to enter (or re-enter) the power-down mode for a minimum of 4 µs until after one of the following conditions has occurred: Start of code execution (after any type of reset), or Exit from power-down mode.

#### 12.3 Interrupt Recovery from Power-down

Two external interrupts may be configured to terminate Power-down mode. External interrupts  $\overline{INT0}$  (P3.2) and  $\overline{INT1}$  (P3.3) may be used to exit Power-down. To wake up by external interrupt  $\overline{INT0}$  or  $\overline{INT1}$ , the interrupt must be enabled and configured for level-sensitive operation.

When terminating Power-down by an interrupt, two different wake up modes are available. When PWDEX in CLKREG.2 is zero, the wake up period is internally timed. At the falling edge on the interrupt pin, Power-down is exited, the is restarted, and an internal timer begins counting. The internal clock will not be allowed to propagate and the CPU will not resume execution until after the timer has counted for nominally 2 ms. After the timeout period the interrupt service routine will begin. To prevent the interrupt from re-triggering, the ISR should disable the interrupt before returning. The interrupt pin should be held low until the device has timed out and begun executing.

When PWDEX = 1 the wakeup period is controlled externally by the interrupt. Again, at the falling edge on the interrupt pin, Power-down is exited and the is restarted. However, the internal clock will not propagate and CPU will not resume execution until the **rising edge** of the interrupt pin. After the rising edge on the pin, the interrupt service routine will begin. The interrupt should be held low long enough for the to stabilize.

#### 12.4 Reset Recovery from Power-down

Wakeup from Power-down through an external reset is similar to the interrupt with PWDEX = 0. At the rising edge of RST, Power-down is exited, the is restarted, and an internal timer begins counting. The internal clock will not be allowed to propagate to the CPU until after the timer has counted for nominally 2 ms. The RST pin must be held high for longer than the timeout period to ensure that the device is reset properly. The device will begin executing once RST is brought low.

It should be noted that when idle is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

P1.0 and P1.1 should be set to "0" if no external pull-ups are used, or set to "1" if external pull-ups are used.

|          | PCON – P      | ower Control      | Register                            |                |                   |                  |                |                  |         |

|----------|---------------|-------------------|-------------------------------------|----------------|-------------------|------------------|----------------|------------------|---------|

| PCON     | = 87H         |                   |                                     |                |                   |                  | Reset Value =  | = 000X 0000B     |         |

| Not Bit  | Addressable   |                   |                                     |                |                   |                  |                |                  | _       |

|          | SMOD1         | SMOD0             | PWMEN                               | POF            | GF1               | GF0              | PD             | IDL              |         |

| Bit      | 7             | 6                 | 5                                   | 4              | 3                 | 2                | 1              | 0                |         |

| Symbol   | Function      |                   |                                     |                |                   |                  |                |                  |         |

| SMOD1    | Double Bauc   | d Rate bit. Dou   | oles the baud ra                    | ate of the UAF | T in modes 1,     | 2, or 3.         |                |                  |         |

| SMOD0    |               |                   | SMOD0 = 0, SC<br>the state of SN    |                | When SMOD         | ) = 1, SCON.7 i  | s FE. Note tha | at FE will be se | t aftei |

| PWMEN    |               |                   | able. When PW<br>The PWM outp       |                |                   | er 1 are configu | red as an 8-bi | t PWM counte     | r with  |

| POF      |               | -                 | to "1" during po<br>e. warm resets) |                | ld reset). It car | n be set or rese | t under softwa | re control and   | is not  |

| GF1, GF0 | General-purp  | pose Flags        |                                     |                |                   |                  |                |                  |         |

| PD       | Power Down    | bit. Setting thi  | s bit activates p                   | ower down op   | peration.         |                  |                |                  |         |

| IDL      | Idle Mode bit | t. Setting this b | it activates idle                   | mode operati   | on                |                  |                |                  |         |

Table 12-1. PCON – Power Control Register

Downloaded from Arrow.com.

## 13. Interrupts

The AT89S2051/S4051 provides 6 interrupt sources: two external interrupts, two timer interrupts, a serial port interrupt, and an analog comparator interrupt. These interrupts and the system reset each have a separate program vector at the start of the program memory space. Each interrupt source can be individually enabled or disabled by setting or clearing a bit in the interrupt enable register IE. The IE register also contains a global disable bit, EA, which disables all interrupts.

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in the interrupt priority registers IP and IPH. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt cannot be interrupted by any other interrupt source. If two requests of different priority levels are pending at the end of an instruction, the request of higher priority level is serviced. If requests of the same priority level are pending at the end of an instruction, an internal polling sequence determines which request is serviced. The polling sequence is based on the vector address; an interrupt with a lower vector address has higher priority than an interrupt with a higher vector address. Note that the polling sequence is only used to resolve pending requests of the same priority level.

The External Interrupts INTO and INT1 can each be either level-activated or transition-activated, depending on bits ITO and IT1 in Register TCON. The flags that actually generate these interrupts are the IEO and IE1 bits in TCON. When the service routine is vectored to, hardware clears the flag that generated an external interrupt only if the interrupt was transition-activated. If the interrupt was level activated, then the external requesting source (rather than the on-chip hardware) controls the request flag.

The Timer 0 and Timer 1 Interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers (except for Timer 0 in Mode 3). When a timer interrupt is generated, the on-chip hardware clears the flag that generated it when the service routine is vectored to.

The Serial Port Interrupt is generated by the logical OR of RI and TI in SCON. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine normally must determine whether RI or TI generated the interrupt, and the bit must be cleared in software.

The CF bit in ACSR generates the Comparator Interrupt. The flag is not cleared by hardware when the service routine is vectored to and must be cleared by software.

Most of the bits that generate interrupts can be set or cleared by software, with the same result as though they had been set or cleared by hardware. That is, interrupts can be generated and pending interrupts can be canceled in software.

| Interrupt            | Source            | Vector Address |

|----------------------|-------------------|----------------|

| System Reset         | RST or POR or BOD | 0000H          |

| External Interrupt 0 | IEO               | 0003H          |

| Timer 0 Overflow     | TF0               | 000BH          |

| External Interrupt 1 | IE1               | 0013H          |

| Timer 1 Overflow     | TF1               | 001BH          |

| Serial Port          | RI or TI          | 0023H          |

| Analog Comparator    | CF                | 0033H          |

# 14. Interrupt Registers

Table 14-1.

IE – Interrupt Enable Register

| IE = .    | A8H                                                                                                                                                            |                                                                       |            |    |     |     | Reset Value = | 00X0 0000B |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------|----|-----|-----|---------------|------------|--|

| Bit Ad    | dressable                                                                                                                                                      |                                                                       |            |    |     |     |               |            |  |

|           | EA                                                                                                                                                             | EC                                                                    | _          | ES | ET1 | EX1 | ET0           | EX0        |  |

| Bit       | 7                                                                                                                                                              | 6                                                                     | 5          | 4  | 3   | 2   | 1             | 0          |  |

| Symbol    | Function                                                                                                                                                       |                                                                       |            |    |     |     |               |            |  |

| EA        | Global enable/disable. All interrupts are disabled when EA = 0. When EA = 1, each interrupt source is enabled/disabled by setting/clearing its own enable bit. |                                                                       |            |    |     |     |               |            |  |

|           |                                                                                                                                                                | eaning its own e                                                      | nable bit. |    |     |     |               |            |  |

| EC        |                                                                                                                                                                | Interrupt Enable                                                      |            |    |     |     |               |            |  |

| EC<br>ES  | Comparator                                                                                                                                                     | •                                                                     |            |    |     |     |               |            |  |

|           | Comparator                                                                                                                                                     | Interrupt Enable                                                      |            |    |     |     |               |            |  |

| ES        | Comparator<br>Serial Port In<br>Timer 1 Inter                                                                                                                  | Interrupt Enable                                                      |            |    |     |     |               |            |  |

| ES<br>ET1 | Comparator<br>Serial Port In<br>Timer 1 Inter                                                                                                                  | Interrupt Enable<br>nterrupt Enable<br>rrupt Enable<br>rrupt 1 Enable |            |    |     |     |               |            |  |

#### Table 14-2. IP – Interrupt Priority Register

| IP = B8 | Reset Value = X0X0 0000B |    |   |    |     |     |     |     |

|---------|--------------------------|----|---|----|-----|-----|-----|-----|

| Bit Add | Iressable                |    |   |    |     |     |     |     |

|         | _                        | PC | - | PS | PT1 | PX1 | PT0 | PX0 |

| Bit     | 7                        | 6  | 5 | 4  | 3   | 2   | 1   | 0   |

| Symbol  | Function                 |    |   |    |     |     |     |     |

| • • • • • • |                                    |  |  |  |  |

|-------------|------------------------------------|--|--|--|--|

| PC          | Comparator Interrupt Priority Low  |  |  |  |  |

| PS          | Serial Port Interrupt Priority Low |  |  |  |  |

| PT1         | Timer 1 Interrupt Priority Low     |  |  |  |  |

| PX1         | External Interrupt 1 Priority Low  |  |  |  |  |

| PT0         | Timer 0 Interrupt Priority Low     |  |  |  |  |

| PX0         | External Interrupt 0 Priority Low  |  |  |  |  |

## Table 14-3. IPH – Interrupt Priority High Register

| IPH = B   | 7H          |     |   | Reset Value = X0X0 0000 |      |      |      |      |

|-----------|-------------|-----|---|-------------------------|------|------|------|------|

| Not Bit A | Addressable |     |   |                         |      |      |      |      |

|           | _           | PCH | - | PSH                     | PT1H | PX1H | PT0H | PX0H |

| Bit       | 7           | 6   | 5 | 4                       | 3    | 2    | 1    | 0    |

| Symbol | Function                            |

|--------|-------------------------------------|

| PCH    | Comparator Interrupt Priority High  |

| PSH    | Serial Port Interrupt Priority High |

| PT1H   | Timer 1 Interrupt Priority High     |

| PX1H   | External Interrupt 1 Priority High  |

| PT0H   | Timer 0 Interrupt Priority High     |

| PX0H   | External Interrupt 0 Priority High  |

## 15. Timer/Counters

The AT89S2051/S4051 have two 16-bit Timer/Counters: Timer 0 and Timer 1. The Timer/Counters are identical to those in the AT89C2051/C4051. For more detailed information on the Timer/Counter operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

## 16. Pulse Width Modulation

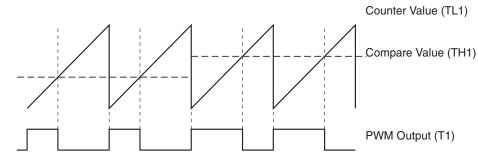

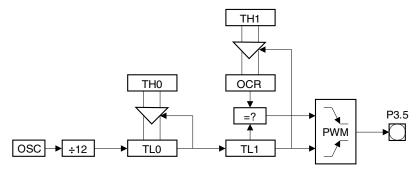

Timer 0 and Timer 1 may be configured as an 8-bit pulse width modulator by setting the PWMEN bit in PCON. The generated waveform is output on the Timer 1 input pin, T1. In PWM mode Timer 0 acts as an 8-bit prescaler to select the PWM timebase. Timer 0 is forced into Mode 2 (8-bit auto-reload) by PWMEN and the value in TH0 will determine the clock division from 0 (FFh) to 256 (00h). Timer 1 acts as the 8-bit PWM counter. TL1 counts once on every overflow from TL0. TH1 stores the 8-bit pulse width value. On the FFh-->00h overflow of TL1, the PWM output is set high. When the count in TL1 matches the value in TH1, the PWM output is set low. Therefore, the output pulse width is proportional to the value in TH1. To prevent glitches, writes to TH1 only take effect on the FFh-->00h overflow of TL1. However, a read from TH1 will read the new value at any time after a write to TH1. See Figure 16-1 for PWM waveform example.

Figure 16-1. Pulse Width Modulation (PWM) Output Waveform

TL0 counts once every machine cycle (1 machine cycle = 12 clocks in X1 mode) and TH0 is the reload value for when TL0 overflows. Every time TL0 overflows TL1 increments by one, with TL0 overflowing after counting 256 minus TH0 machine cycles.

To calculate the pulse width for the PWM output on pin T1, users should use the following formula:

TH1 \* (256 - TH0) \* (1/clock\_freq) \* 12 = Pulse Width

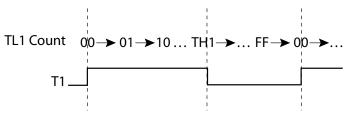

TL1 will always count from 00h to FFh. The output on the Timer 1 (T1) pin will be high from when TL1 equals 00h until TL1 equals TH1 (see Figure 16-3). TH1 does not act as the reload value for TL1 on overflow. Instead, TH1 is used strictly as a compare value (see Figure 16-2).

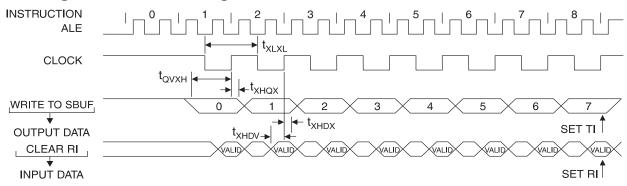

## 17. UART

The UART in the AT89S2051/S4051 operates the same way as the UART in the AT89C2051/C4051. For more detailed information on the UART operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

#### 17.1 Enhanced UART

In addition to all of its usual modes, the UART can perform framing error detection by looking for missing stop bits, and automatic address recognition. The UART also fully supports multiprocessor communication as does the standard 80C51 UART.

When used for framing error detect, the UART looks for missing stop bits in the communication. A missing bit will set the FE bit in the SCON register. The FE bit shares the SCON.7 bit with SM0 and the function of SCON.7 is determined by PCON.6 (SMOD0). If SMOD0 is set then SCON.7 functions as FE. SCON.7 functions as SM0 when SMOD0 is cleared. When used as FE, SCON.7 can only be cleared by software.

#### 17.2 Automatic Address Recognition

Automatic Address Recognition is a feature which allows the UART to recognize certain addresses in the serial bit stream by using hardware to make the comparisons. This feature saves a great deal of software overhead by eliminating the need for the software to examine every serial address which passes by the serial port. This feature is enabled by setting the SM2 bit in SCON. In the 9-bit UART modes, mode 2 and mode 3, the Receive Interrupt flag (RI) will be automatically set when the received byte contains either the "Given" address or the "Broadcast" address. The 9-bit mode requires that the 9th information bit is a 1 to indicate that the received information is an address and not data.

The 8-bit mode is called mode 1. In this mode the RI flag will be set if SM2 is enabled and the information received has a valid stop bit following the 8 address bits and the information is either a Given or Broadcast address.

Mode 0 is the Shift Register mode and SM2 is ignored.

Using the Automatic Address Recognition feature allows a master to selectively communicate with one or more slaves by invoking the given slave address or addresses. All of the slaves may be contacted by using the Broadcast address. Two special Function Registers are used to define the slave's address, SADDR, and the address mask, SADEN. SADEN is used to define which bits in the SADDR are to be used and which bits are "don't care". The SADEN mask can

be logically ANDed with the SADDR to create the "Given" address which the master will use for addressing each of the slaves. Use of the Given address allows multiple slaves to be recognized while excluding others. The following examples will help to show the versatility of this scheme:

| Slave 0 | SADDR = 1100 0000        |             |  |  |  |

|---------|--------------------------|-------------|--|--|--|

|         | SADEN = <u>1111 1101</u> |             |  |  |  |

|         | Given                    | = 1100 00X0 |  |  |  |

| Slave 1 | SADDR = 1100 0000        |             |  |  |  |

|         | SADEN = <u>1111 1110</u> |             |  |  |  |

|         | Given                    | = 1100 000X |  |  |  |

In the previous example SADDR is the same and the SADEN data is used to differentiate between the two slaves. Slave 0 requires a 0 in bit 0 and it ignores bit 1. Slave 1 requires a 0 in bit 1 and bit 0 is ignored. A unique address for slave 0 would be 1100 0010 since slave 1 requires a 0 in bit 1. A unique address for slave 1 would be 1100 0001 since a 1 in bit 0 will exclude slave 0. Both slaves can be selected at the same time by an address which has bit 0 = 0 (for slave 0) and bit 1 = 0 (for slave 1). Thus, both could be addressed with 1100 0000.

In a more complex system the following could be used to select slaves 1 and 2 while excluding slave 0:

| Slave 0 | SADDR = 1100 0000        |               |  |  |  |

|---------|--------------------------|---------------|--|--|--|

|         | SADEN = <u>1111 1001</u> |               |  |  |  |

|         | Given                    | = 1100 0XX0   |  |  |  |

|         |                          |               |  |  |  |

| Slave 1 | SADDR = 111              | 0000 0        |  |  |  |

|         | SADEN = <u>111</u>       | <u>1 1010</u> |  |  |  |

|         | Given                    | = 1110 0X0X   |  |  |  |

|         |                          |               |  |  |  |

| Slave 2 | SADDR = 111              | 0000 0        |  |  |  |

|         | SADEN = <u>111</u>       | <u>1 1100</u> |  |  |  |

|         | Given                    | = 1110 00XX   |  |  |  |

|         |                          |               |  |  |  |

In the above example the differentiation among the 3 slaves is in the lower 3 address bits. Slave 0 requires that bit 0 = 0 and it can be uniquely addressed by 1110 0110. Slave 1 requires that bit 1 = 0 and it can be uniquely addressed by 1110 and 0101. Slave 2 requires that bit 2 = 0 and its unique address is 1110 0011. To select Slaves 0 and 1 and exclude Slave 2, use address 1110 0100, since it is necessary to make bit 2 = 1 to exclude slave 2.

The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zeros in this result are trended as don't cares. In most cases, interpreting the don't cares as ones, the broadcast address will be FF hexadecimal.

Upon reset SADDR (SFR address 0A9H) and SADEN (SFR address 0B9H) are loaded with 0s. This produces a given address of all "don't cares" as well as a Broadcast address of all "don't cares". This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard 80C51-type UART drivers which do not make use of this feature.

## Table 17-1. SCON – Serial Port Control Register

| SCON Ac   | ldress = 98H                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                 |                 |                |                                        | Reset Value                                  | = 0000 0000B  |       |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------|----------------------------------------|----------------------------------------------|---------------|-------|--|

| Bit Addre | ssable                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                 |                 |                |                                        |                                              |               | т.    |  |

|           | SM0/FE                                                                                                                                                                                                                                                                                                                                                                                                        | SM1             | SM2             | REN             | TB8            | RB8                                    | TI                                           | RI            |       |  |

| Bit       | 7                                                                                                                                                                                                                                                                                                                                                                                                             | 6               | 5               | 4               | 3              | 2                                      | 1                                            | 0             |       |  |

| (SN       | $MOD = 0/1)^{(1)}$                                                                                                                                                                                                                                                                                                                                                                                            |                 |                 |                 |                |                                        |                                              |               |       |  |

| Symbol    | Function                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                 |                 |                |                                        |                                              |               |       |  |

| FE        | Framing error bit. This bit is set by the receiver when an invalid stop bit is detected. The FE bit is not cleared by valid frames but should be cleared by software. The SMOD0 bit must be set to enable access to the FE bit. FE will be set regardless of the state of SMOD.                                                                                                                               |                 |                 |                 |                |                                        |                                              |               |       |  |

| SM0       | Serial Port                                                                                                                                                                                                                                                                                                                                                                                                   | Mode Bit 0, (S  | MOD must = 0    | to access bit S | SM0)           |                                        |                                              |               |       |  |

|           | Serial Port                                                                                                                                                                                                                                                                                                                                                                                                   | Mode Bit 1      |                 |                 |                |                                        |                                              |               |       |  |

|           | SM0                                                                                                                                                                                                                                                                                                                                                                                                           | S               | M1              | Mode            | Description    | Baud Rat                               | e <sup>(2)</sup>                             |               |       |  |

|           | 0                                                                                                                                                                                                                                                                                                                                                                                                             |                 | 0               | 0               | shift register | f <sub>osc</sub> /12                   |                                              |               |       |  |

| SM1       | 0                                                                                                                                                                                                                                                                                                                                                                                                             |                 | 1               | 1               | 8-bit UART     | variable                               | e                                            |               |       |  |

|           | 1                                                                                                                                                                                                                                                                                                                                                                                                             |                 | 0               | 2               | 9-bit UART     | f <sub>osc</sub> /64 or f <sub>o</sub> | f <sub>osc</sub> /64 or f <sub>osc</sub> /32 |               |       |  |

|           | 1                                                                                                                                                                                                                                                                                                                                                                                                             |                 | 1               | 3               | 9-bit UART     | variable                               | e                                            |               |       |  |

| SM2       | Enables the Automatic Address Recognition feature in modes 2 or 3. If SM2 = 1 then RI will not be set unless the received 9th data bit (RB8) is 1, indicating an address, and the received byte is a Given or Broadcast Address. In mode 1, if SM2 = 1 then RI will not be activated unless a valid stop bit was received, and the received byte is a Given or Broadcast Address. In Mode 0, SM2 should be 0. |                 |                 |                 |                |                                        |                                              |               |       |  |

| REN       | Enables s                                                                                                                                                                                                                                                                                                                                                                                                     | erial receptio  | n. Set by soft  | ware to enab    | le reception.  | Clear by softw                         | are to disab                                 | le reception. |       |  |

| TB8       | The 9th da                                                                                                                                                                                                                                                                                                                                                                                                    | ata bit that wi | ll be transmitt | ted in modes    | 2 and 3. Set c | or clear by sof                        | tware as des                                 | sired.        |       |  |

| RB8       | In modes 2 and 3, the 9th data bit that was received. In mode 1, if SM2 = 0, RB8 is the stop bit that was received. In mode 0, RB8 is not used.                                                                                                                                                                                                                                                               |                 |                 |                 |                |                                        |                                              |               |       |  |

| TI        |                                                                                                                                                                                                                                                                                                                                                                                                               |                 | -               |                 |                |                                        |                                              | he beginning  | of th |  |

|           | <ul> <li>stop bit in the other modes, in any serial transmission. Must be cleared by software.</li> <li>Receive interrupt flag. Set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bit time in the other modes, in any serial reception (except see SM2). Must be cleared by software.</li> </ul>                                                                          |                 |                 |                 |                |                                        |                                              |               |       |  |

2.  $f_{osc} =$  frequency.

Downloaded from Arrow.com.

## 18. Analog Comparator

A single analog comparator is provided in the AT89S2051/S4051. The comparator operation is such that the output is a logical "1" when the positive input AIN0 (P1.0]) is greater than the negative input AIN1 (P1.1). Otherwise the output is a zero. Setting the CEN bit in ACSR enables the comparator. When the comparator is first enabled, the comparator output and interrupt flag are not guaranteed to be stable for 10 microseconds. The corresponding comparator interrupt should not be enabled during that time, and the comparator interrupt flag must be cleared before the interrupt is enabled in order to prevent an immediate interrupt service.

The comparator may be configured to cause an interrupt under a variety of output value conditions by setting the CM bits in ACSR. The comparator interrupt flag CF in ACSR is set whenever the comparator output matches the condition specified by CM. The flag may be polled by software or may be used to generate an interrupt and must be cleared by software. The analog comparator is always disabled during Idle or Power-down modes.

# 19. Comparator Interrupt with Debouncing

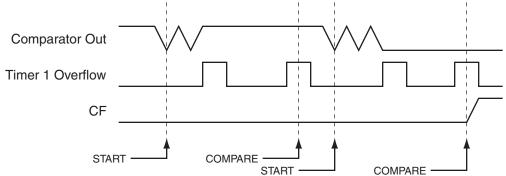

The comparator output is sampled at every State 4 (S4) of every machine cycle. The conditions on the analog inputs may be such that the comparator output will toggle excessively. This is especially true if applying slow moving analog inputs. Three debouncing modes are provided to filter out this noise. In debouncing mode, the comparator uses Timer 1 to modulate its sampling time. When a relevant transition occurs, the comparator waits until two Timer 1 overflows have occurred before resampling the output. If the new sample agrees with the expected value, CF is set. Otherwise, the event is ignored. The filter may be tuned by adjusting the timeout period of Timer 1. Because Timer 1 is free running, the debouncer must wait for two overflows to guarantee that the sampling delay is at least 1 timeout period. Therefore after the initial edge event, the interrupt may occur between 1 and 2 timeout periods later. See Figure 19-1.

Figure 19-1. Example of Negative Edge Comparator Interrupt with Debouncing

# 20. Analog Comparator Register

| ACSR     | = 97H   |                                                                                                                                                                                                                                            |          |                       |              |          |     |     | Reset Value = | XXX0 0000B |   |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|--------------|----------|-----|-----|---------------|------------|---|

| Not Bit  | Address | sable                                                                                                                                                                                                                                      | 9        |                       |              |          |     |     |               |            |   |

|          | _       | -                                                                                                                                                                                                                                          |          | -                     | _            | CF       | CEN | CM2 | CM1           | CM0        | ] |

| Bit      | 7       | ,                                                                                                                                                                                                                                          |          | 6                     | 5            | 4        | 3   | 2   | 1             | 0          |   |

| Symbol   | Funct   | ion                                                                                                                                                                                                                                        |          |                       |              |          |     |     |               |            |   |

| CF       |         | Comparator Interrupt Flag. Set when the comparator output meets the conditions specified by the CM [2:0] bits and CEN is set. The flag must be cleared by software. The interrupt may be enabled/disabled by setting/clearing bit 6 of IE. |          |                       |              |          |     |     |               |            |   |

| CEN      |         | Comparator Enable. Set this bit to enable the comparator. Clearing this bit will force the comparator output low and prevent further events from setting CF.                                                                               |          |                       |              |          |     |     |               |            |   |

|          | Comp    | arato                                                                                                                                                                                                                                      | or Inter | rupt Mode             |              |          |     |     |               |            |   |

|          | 2       | 1                                                                                                                                                                                                                                          | 0        | Interrupt Mode        |              |          |     |     |               |            |   |

|          |         | 0                                                                                                                                                                                                                                          | 0        | Negative (Low) level  |              |          |     |     |               |            |   |

|          | 0       | 0                                                                                                                                                                                                                                          | 1        | Positive edge         |              |          |     |     |               |            |   |

| CM [2:0] | 0       | 1                                                                                                                                                                                                                                          | 0        |                       | ith debounc  | e        |     |     |               |            |   |

|          | 0       | 1                                                                                                                                                                                                                                          | 1        | Positive              | edge with de | bounce   |     |     |               |            |   |

|          | 1       | 0                                                                                                                                                                                                                                          | 0        | Negative edge         |              |          |     |     |               |            |   |

|          | 1       | 0                                                                                                                                                                                                                                          | 1        | Toggle                |              |          |     |     |               |            |   |

|          | 1       | 1                                                                                                                                                                                                                                          | 0        | Negative              | edge with c  | lebounce |     |     |               |            |   |

|          | 1       | 1                                                                                                                                                                                                                                          | 1        | Positive (High) level |              |          |     |     |               |            |   |

Table 20-1.

ACSR – Analog Comparator Control & Status Register

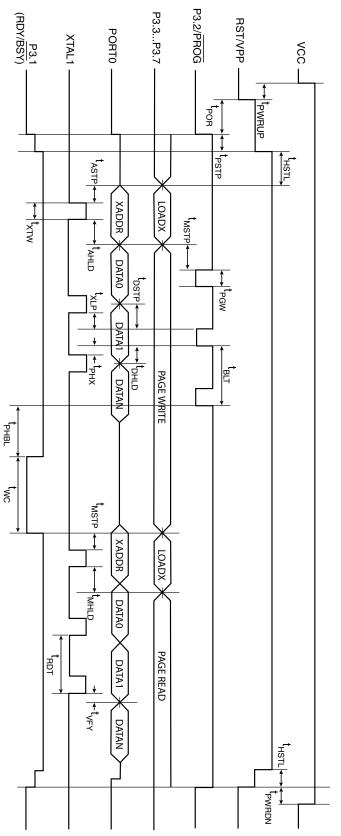

# 21. Parallel Programming Specification

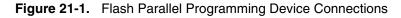

Atmel's AT89S2051/S4051 offers 2K/4K bytes of In-System Programmable Flash code memory. In addition, the device contains a 32-byte User Signature Row and a 32-byte read-only Atmel Signature Row.

| Table 21-1. | Memory Organization |

|-------------|---------------------|

|-------------|---------------------|

| Device #  | Page Size | # Pages | Address Range | Page Range |

|-----------|-----------|---------|---------------|------------|

| AT89S2051 | 32 bytes  | 64      | 0000H - 07FFH | 00H - 3FH  |

| AT89S4051 | 32 bytes  | 128     | 0000H - 0FFFH | 00H - 7FH  |

Sampling of pin P3.1 (RDY/BSY) is optional. In Parallel Mode, P3.1 will be pulled low while the device is busy. However, it requires an external passive pull-up to V<sub>CC</sub>. Also, note that P3.6 does not exist, so TestCode connects to P3.7, P3.5, P3.4, and P3.3.

| Table 21-2. | Parallel Programming Mode Command Summary    |

|-------------|----------------------------------------------|

|             | r aranor r rogramming mode e emmana e annarg |

|                                       |             |        | Test Contro        |        |      | Test S | elects |      | Data I/O         |

|---------------------------------------|-------------|--------|--------------------|--------|------|--------|--------|------|------------------|

|                                       |             | P3.2   |                    | INC    |      |        |        |      |                  |

| Mode                                  |             |        | RST <sup>(1)</sup> |        | P3.3 | P3.4   | P3.5   | P3.7 | P1.7-0           |

| Chip Erase <sup>(5)</sup>             |             | 1.0 µs | 12V                | L      | Н    | L      | L      | L    | XX               |

| Load X-Address <sup>(2)</sup>         |             | Н      | 12V                | 0.1 µs | Н    | L      | Н      | н    | D <sub>IN</sub>  |

| Page Write <sup>(3)(4)(6)</sup>       | Code Memory | 1.0 µs | 12V                | 0.1 µs | L    | Н      | Н      | н    | D <sub>IN</sub>  |

| Page Read <sup>(3)</sup>              | Code Memory | Н      | 12V                | 0.1 µs | L    | L      | Н      | н    | D <sub>OUT</sub> |

| Page Write <sup>(3)(4)(6)(7)</sup>    | Sig. Row    | 1.0 µs | 12V                | 0.1 µs | L    | L      | L      | L    | D <sub>IN</sub>  |

| Page Read <sup>(3)(8)(10)</sup>       | Sig. Row    | Н      | 12V                | 0.1 µs | L    | L      | L      | н    | D <sub>OUT</sub> |

| Write Fuse/Lock Bit <sup>(5)(9)</sup> |             | 1.0 µs | 12V                | L      | Н    | н      | Н      | н    | D <sub>IN</sub>  |

| Read Fuse/Lock Bit <sup>(9)</sup>     |             | Н      | 12V                | L      | Н    | Н      | L      | L    | D <sub>OUT</sub> |

Notes: 1. The internal Y-address counter is reset to 00H on the rising/falling edge of RST.

2. A positive pulse on XTAL1 loads the address data on Port P1 into the X-address (page) register and resets the Y-address.

3. A positive pulse on XTAL1 advances the Y-address counter.

4. A low pulse on P3.2 loads data from Port P1 for the current address. If another P3.2 low pulse does not arrive within 150 μs, programming starts.

- 5. Internally timed for 4 ms.

- 6. Internally timed for 2 ms.

7. 00H must be loaded into the X-address before executing this command.

- 8. Will read User Signature if X-address is 00H, will read Atmel Signature if X-address is 01H.

- 9. Fuse/Lock Bit Definitions:

| Bit 7 | XTAL Osc Bypass      | Enable = 0/Disable = 1  |

|-------|----------------------|-------------------------|

| Bit 6 | User Row Programming | Enable = 0/Disable = 1  |

| Bit 5 | x2 Clock             | Enable = 0/Disable = 1  |

| Bit 4 | Serial Programming   | Enable = 0/Disable = 1  |

| Bit 1 | Lock Bit 2           | Locked = 0/Unlocked = 1 |

| Bit 0 | Lock Bit 1           | Locked = 0/Unlocked = 1 |

|       |                      |                         |

#### 10. Atmel Signature Bytes:

| AT89S2051: | Address | 00H = 1EH |

|------------|---------|-----------|

|            |         | 01H = 23H |

|            |         | 02H = FFH |

| AT89S4051: | Address | 00H = 1EH |

|            |         | 01H = 43H |

|            |         | 02H = FFH |

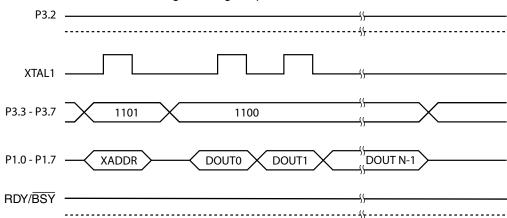

## 22. Power-up Sequence

Execute the following sequence to power-up the device before programming.

- 1. Apply power between VCC and GND pins.

- 2. After  $V_{CC}$  has settled, wait 10  $\mu s$  and bring RST to "H".

- 3. Wait 4 ms for the internal Power-on Reset to timeout.

- 4. Bring P3.2 to "H" and drive P3.7, P3.5, P3.4, and P3.3 to known values, then wait 10  $\mu s.$

- 5. Raise RST/V<sub>PP</sub> to 12V to enable the parallel programming modes.

- 6. After  $V_{PP}$  has settled, wait an additional 10  $\mu$ s before programming.

#### Figure 22-1. Power-up Operation

| V <sub>cc</sub> .   |                    |

|---------------------|--------------------|

| RST/V <sub>PP</sub> |                    |

| P3.2                |                    |

|                     |                    |

| XTAL1 ·             |                    |

| P3.3 - P3.7         | High Z             |

| P1.0 - P1.7         | High Z             |

| RDY/BSY ·           | ······High Z-····· |

## 23. Power-down Sequence

Execute the following sequence to power-down the device after programming.

- 1. Tri-state Port P1.

- 2. Bring RST/V<sub>PP</sub> down from 12V to V<sub>CC</sub> and wait 10  $\mu$ s.

- 3. Bring XTAL and P3.2 to "L" and tri-state P3.7, P3.5, P3.4, and P3.3.

- 4. Bring RST to "L" and wait 10 μs.

- 5. Power off  $V_{CC}$ .

#### Figure 23-1. Power-down Operation

| $V_{cc}$     |        |

|--------------|--------|

| $RST/V_{PP}$ |        |

| P3.2         |        |

| XTAL1        |        |

| P3.3 - P3.7  | High Z |

| P1.0 - P1.7  | High Z |

| RDY/BSY      | High Z |

## 24. Chip Erase

#### Function:

- 1. FFH programmed to every address location.

- 2. FFH programmed to User Signature Row if User Row Fuse bit is enabled.

- 3. Lockbit1 and Lockbit2 programmed to "unlock" state.

#### Usage:

- 1. Apply "0001" TestCode to P3.7, P3.5, P3.4, P3.3.

- 2. Pulse P3.2 low for 1  $\mu$ s.

- 3. Wait 4 ms, monitor P3.1, or poll data.

Note: This and the following waveforms are not to scale.

#### Figure 24-1. Chip Erase Sequence

| P3.2          |        | [ |  |

|---------------|--------|---|--|

| XTAL1         |        |   |  |

| P3.3 - P3.7   | 0001   |   |  |

| P1.0 - P1.7 . | High Z |   |  |

| RDY/BSY       |        |   |  |

## 25. Load X-Address

#### Function:

- Loads the X-Address register with data on Port P1. The loaded address will select the page for subsequent write/read commands. The X-Address is equivalent to bits [11:5] of the full byte address.

- 2. Resets the Y-Address counter to 00H. The Y-Address is equivalent to bits [4:0] of the full byte address and selects a byte within a page.

#### Usage:

- 1. Apply "1101" TestCode to P3.7, P3.5, P3.4, P3.3.

- 2. Drive Port P1 with 8-bit X-address data.

- 3. Pulse XTAL1 high for at least 100 ns. The address is latched on the falling edge of XTAL1.

# Figure 25-1. Load X-Address Sequence P3.2 XTAL1 P3.3 - P3.7 P1.0 - P1.7 High Z RDY/BSY

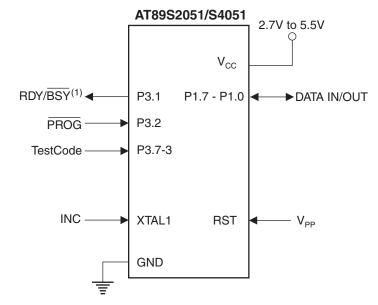

# 26. Page Write 4K Code

#### Function:

- 1. Programs 1 page (1 to 32 bytes) of data into the Code Memory array.

- 2. X-address (page) determined by previous Load-X command.

- 3. Y-address (offset) incremented by positive pulse on XTAL1.

- 4. 1 byte of data is loaded from Port P1 for the current X- and Y-address by a low pulse on P3.2.

#### Usage:

- 1. Execute the Load-X command to set the page address and reset the offset.

- 2. Apply "1110" TestCode to P3.7, P3.5, P3.4, P3.3.

- 3. Drive Port P1 with 8-bit data.

- 4. Pulse P3.2 low for 1 µs to load the data from Port P1.

- 5. For additional bytes (up to 32), pulse XTAL1 high for at least 100 ns to increment the Y-address and repeat steps 3 and 4 within 150  $\mu$ s.

- 6. Wait 2 ms, monitor P3.1, or poll data.

Note: It is possible to skip bytes by pulsing XTAL1 high multiple times before pulsing P3.2 low.

Figure 26-1. Page Write 4K Code Programming Sequence

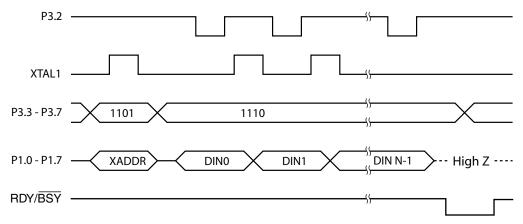

# 27. Read 4K Code

#### Function:

- 1. Read 1 page (1 to 32 bytes) of data from the Code Memory array.

- 2. X-address (page) determined by previous Load-X command.

- 3. Y-address (offset) incremented by positive pulse on XTAL1.

#### Usage:

- 1. Execute the Load-X command to set the page address and reset the offset.

- 2. Apply "1100" TestCode to P3.7, P3.5, P3.4, P3.3.

- 3. Read 8-bit data on Port P1.

- 4. For additional bytes (up to 32), pulse XTAL1 high for at least 100 ns to increment the Y-address and repeat step 3. The address will change on the falling edge of XTAL1.

Figure 27-1. Read 4K Code Programming Sequence

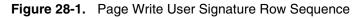

# 28. Page Write User Signature Row

#### Function:

- 1. Programs 1 to 32 bytes of data into the User Signature Row.

- 2. X-address (page) should be 00H from a previous Load-X command.

- 3. Y-address (offset) incremented by positive pulse on XTAL1.

- 4. 1 byte of data is loaded from Port P1 for the current Y-address by a low pulse on P3.2.

- 5. Disabled if User Row Fuse bit is disabled.

#### Usage:

- 1. Execute the Load-X command to set the page to 00H and reset the offset.

- 2. Apply "0000" TestCode to P3.7, P3.5, P3.4, P3.3.

- 3. Drive Port P1 with 8-bit data.

- 4. Pulse P3.2 low for 1  $\mu$ s to load the data from Port P1.

- 5. For additional bytes (up to 32), pulse XTAL1 high for at least 100 ns to increment the Y-address and repeat steps 3 and 4 within 150  $\mu$ s.

- 6. Wait 2 ms, monitor P3.1, or poll data.

Note: It is possible to skip bytes by pulsing XTAL1 high multiple times before pulsing P3.2 low.

| P3.2        |  |

|-------------|--|

| XTAL1       |  |

| P3.3 - P3.7 |  |

| P1.0 - P1.7 |  |

| RDY/BSY     |  |

# <sup>26</sup> AT89S2051/S4051

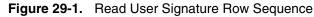

## 29. Read User Signature Row

#### Function:

- 1. Reads 1 to 32 bytes of data from the User Signature Row.

- 2. X-address (page) should be 00H from a previous Load-X command.

- 3. Y-address (offset) incremented by positive pulse on XTAL1.

#### Usage:

- 1. Execute the Load-X command to set the page to 00H and reset the offset.

- 2. Apply "1000" TestCode to P3.7, P3.5, P3.4, P3.3.

- 3. Read 8-bit data on Port P1.

- 4. For additional bytes (up to 32), pulse XTAL1 high for at least 100 ns to increment the Yaddress and repeat step 3. The address will change on the falling edge of XTAL1.

| P3.2        |                  | ,        |

|-------------|------------------|----------|

| XTAL1       |                  | ,        |

| P3.3 - P3.7 | <u>1101</u> 1000 |          |

| P1.0 - P1.7 |                  | DOUT N-1 |

| RDY/BSY     |                  | ,        |

## 30. Read Atmel Signature Row

#### Function:

- 1. Reads 1 to 32 bytes of data from the Atmel Signature Row.

- 2. X-address (page) should be 01H from a previous Load-X command.

- 3. Y-address (offset) incremented by positive pulse on XTAL1.

#### Usage:

- 1. Execute the Load-X command to set the page to 01H and reset the offset.

- 2. Apply "1000" TestCode to P3.7, P3.5, P3.4, P3.3.

- 3. Read 8-bit data on Port P1.

- 4. For additional bytes (up to 32), pulse XTAL1 high for at least 100 ns to increment the Yaddress and repeat step 3. The address will change on the falling edge of XTAL1.

#### Figure 30-1. Read Atmel Signature Row Sequence

## 31. Write Lock Bits/User Fuses

#### Function:

- 1. Program Lock Bits 1 and 2.

- 2. Program user fuses.

#### Usage:

1) Apply "1111" TestCode to P3.7, P3.5, P3.4, P3.3.

- 3. Drive Port P1 with fuse data, bits [7:4] for fuses and bits [1:0] for lock bits.

- 4. Pulse P3.2 low for 1 µs.

- 5. Wait 4 ms, monitor P3.1, or poll data.

#### Figure 31-1. Write Lock Bits/User Fuses

| P3.2        |             |        |

|-------------|-------------|--------|

| XTAL1       |             |        |

| P3.3 - P3.7 | 1111        | _X     |

| P1.0 - P1.7 | High Z DATA | High Z |

| RDY/BSY     |             | 1      |

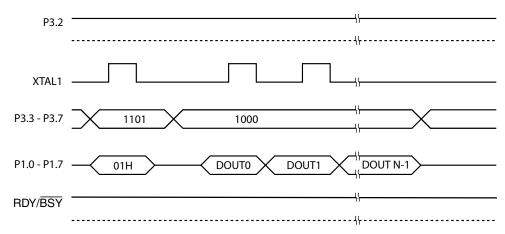

## 32. Read Lock Bits/User Fuses

#### Function:

- 1. Read status of Lock Bits 1 and 2.

- 2. Read status of user fuses.

#### Usage:

- 1. Apply "0011" TestCode to P3.7, P3.5, P3.4, P3.3.

- 2. Read fuse data from Port P1, bits [7:4] for fuses and bits [1:0] for lock bits.

#### Figure 32-1. Read Lock Bits/User Fuses

| P3.2        |               |

|-------------|---------------|

|             |               |

| XTAL1       |               |

| P3.3P3.7    | 0011          |

| P1.0 - P1.7 | High Z High Z |

| RDY/BSY     |               |

Downloaded from Arrow.com.

| Symbol Parameter                                                           |                                    | Min  | Мах    | Units |

|----------------------------------------------------------------------------|------------------------------------|------|--------|-------|

| V <sub>PP</sub> Programming Enable Voltage                                 |                                    | 11.5 | 12.5   | V     |

| I <sub>PP</sub>                                                            | Programming Enable Current         |      | 1.0    | mA    |

| t <sub>PWRUP</sub>                                                         | Power-on to RST High               | 10   |        | μs    |

| t <sub>POR</sub>                                                           | Power-on Reset Time                | 2    |        | ms    |

| t <sub>PSTP</sub>                                                          | PROG Setup to V <sub>PP</sub> High | 10   |        | μs    |

| t <sub>HSTL</sub>                                                          | High Voltage Setting time          | 10   |        | μs    |

| t <sub>MSTP</sub>                                                          | Mode Setup to PROG or XTAL1        | 1    |        | μs    |

| t <sub>MHLD</sub>                                                          | Mode Hold after PROG or XTAL2      | 1    |        | μs    |

| t <sub>xTW</sub>                                                           | XTAL1 High Width                   | 0.5  |        | μs    |

| t <sub>ASTP</sub> Address Setup to XTAL1 High                              |                                    | 0.5  |        | μs    |

| t <sub>AHLD</sub> Address Hold after XTAL1 Low                             |                                    | 0.5  |        | μs    |

| t <sub>PGW</sub> PROG Low Width                                            |                                    | 1    |        | μs    |

| t <sub>DSTP</sub> Data Setup to PROG Low                                   |                                    | 0.5  |        | μs    |

| t <sub>DHLD</sub>                                                          | Data Hold after PROG High          | 0.5  | 0.5 µs |       |

| t <sub>XLP</sub>                                                           | XTAL1 Low to PROG Low              | 0.5  | μs     |       |

| t <sub>PHX</sub>                                                           |                                    |      |        | μs    |

| t <sub>BLT</sub>                                                           | Byte Load Period                   |      | 150    | μs    |

| t <sub>PHBL</sub> PROG High to BUSY Low<br>t <sub>WC</sub> Wire Cycle Time |                                    |      | 256    | μs    |

|                                                                            |                                    |      | 4.5    | ms    |