Edition 2005-11-25

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### Two Port Bridge Fiber to Fast Ethernet Converter

#### Revision History: 2005-11-25, Rev. 1.02

| Previous Ve | Previous Version:                                                                  |  |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Page/Date   | Subjects (major changes since last revision)                                       |  |  |  |  |  |  |

| 2004-05-05  | Rev. 1.0, First release of NINJA C (ADM6992C)                                      |  |  |  |  |  |  |

| 2005-05-20  | Rev. 1.01, Document conversion from Word to FrameMaker (XML)                       |  |  |  |  |  |  |

| 2005-11-25  | Rev. 1.01 changed to Rev. 1.02<br>Minor change. Included Green package information |  |  |  |  |  |  |

|             |                                                                                    |  |  |  |  |  |  |

|             |                                                                                    |  |  |  |  |  |  |

|             |                                                                                    |  |  |  |  |  |  |

|             |                                                                                    |  |  |  |  |  |  |

|             |                                                                                    |  |  |  |  |  |  |

### Trademarks

ABM<sup>®</sup>, ACE<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ASM<sup>®</sup>, ASP<sup>®</sup>, DigiTape<sup>®</sup>, DuSLIC<sup>®</sup>, EPIC<sup>®</sup>, ELIC<sup>®</sup>, FALC<sup>®</sup>, GEMINAX<sup>®</sup>, IDEC<sup>®</sup>, INCA<sup>®</sup>, IOM<sup>®</sup>, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>, ITAC<sup>®</sup>, IWE<sup>®</sup>, IWORX<sup>®</sup>, MUSAC<sup>®</sup>, MuSLIC<sup>®</sup>, OCTAT<sup>®</sup>, OptiPort<sup>®</sup>, POTSWIRE<sup>®</sup>, QUAT<sup>®</sup>, QuadFALC<sup>®</sup>, SCOUT<sup>®</sup>, SICAT<sup>®</sup>, SICOFI<sup>®</sup>, SIDEC<sup>®</sup>, SLICOFI<sup>®</sup>, SMINT<sup>®</sup>, SOCRATES<sup>®</sup>, VINETIC<sup>®</sup>, 10BaseV<sup>®</sup>, 10BaseVX<sup>®</sup> are registered trademarks of Infineon Technologies AG. 10BaseS<sup>™</sup>, EasyPort<sup>™</sup>, VDSLite<sup>™</sup> are trademarks of Infineon Technologies AG. Microsoft<sup>®</sup> is a registered trademark of Microsoft Corporation, Linux<sup>®</sup> of Linus Torvalds, Visio<sup>®</sup> of Visio Corporation, and FrameMaker<sup>®</sup> of Adobe Systems Incorporated.

### **Table of Contents**

# **Table of Contents**

|                                          | Table of Contents                                                                                                                                                                            | . 4                  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                          | List of Figures                                                                                                                                                                              | . 6                  |

|                                          | List of Tables                                                                                                                                                                               | . 7                  |

| <b>1</b><br>1.1<br>1.2<br>1.3            | Product Overview                                                                                                                                                                             | . 8<br>. 8           |

| 1.4                                      | Data Lengths Conventions                                                                                                                                                                     |                      |

| <b>2</b><br>2.1<br>2.2<br>2.3            | NINJA C/CX Interface Description         Pin Diagram         Pin Type and Buffer Type Abbreviations         Pin Descriptions                                                                 | 10<br>11<br>12       |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2 | Function Description         10/100M PHY Block         Auto Negotiation and Speed Configuration         Auto Negotiation         Speed Configuration                                         | 19<br>20<br>20<br>20 |

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3           | Switch Functional Description         Store & Forward Mode         Modified Cut-through Mode         MII cut-through Mode                                                                    | 21<br>22<br>22       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3           | Basic Operations       MAC Address Learning & Filtering         Address Learning       Hash Algorithm                                                                                        | 22<br>22             |

| 3.4.4<br>3.4.5<br>3.4.6<br>3.4.7         | Address Recognition and Packet Forwarding         Address Aging         Back off Algorithm         Inter-Packet Gap (IPG)                                                                    | 23<br>23<br>23       |

| 3.4.8<br>3.4.9<br>3.4.10                 | Illegal Frames         Half Duplex Flow Control         Full Duplex Flow Control                                                                                                             | 23<br>23<br>24       |

| 3.4.11<br>3.4.12<br>3.4.13<br>3.5        | Bandwidth Control       Interrupt         Interrupt       Auto TP MDIX function         Converter Functional Description                                                                     | 24<br>24             |

| 3.5.1<br>3.6<br>3.6.1                    | Fault Propagation         Serial Management Interface (SMI) Register Access         Preamble Suppression                                                                                     | 24<br>25             |

| 3.6.2<br>3.6.3<br>3.7<br>3.7.1           | Preamble Suppression         Read EEPROM Register via SMI Register         Write EEPROM Register via SMI Register         Reset Operation         Write EEPROM Register via EEPROM Interface | 26<br>27<br>27       |

| <b>4</b><br>4.1<br>4.2                   | Registers Description         EEPROM Registers         EEPROM Register Descriptions                                                                                                          | 28<br>28             |

## Ninja C/CX ADM6992C/CX

#### **Table of Contents**

| 4.2.1<br>4.3<br>4.4<br>4.4.1 | EEPROM Register Format                                                           | 55<br>57 |

|------------------------------|----------------------------------------------------------------------------------|----------|

| <b>5</b><br>5.1<br>5.2       | Electrical Specification         DC Characterization         AC Characterization | 75       |

| 6                            | Packaging                                                                        | 78       |

|                              | References                                                                       | 80       |

|                              | Terminology                                                                      | 81       |

#### **List of Figures**

# **List of Figures**

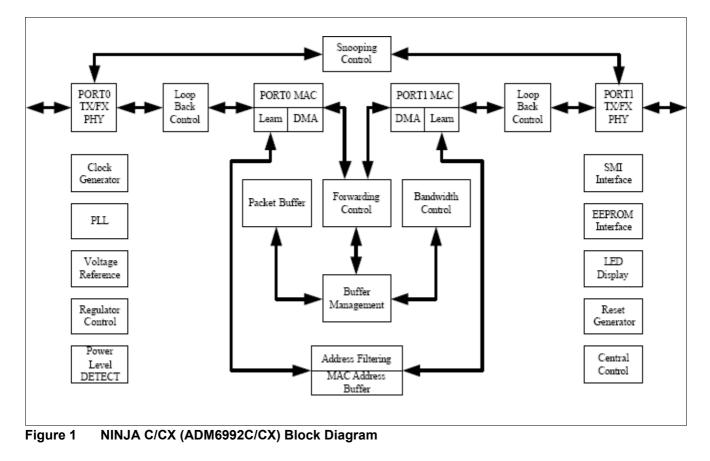

- Figure 1 NINJA C/CX (ADM6992C/CX) Block Diagram 9

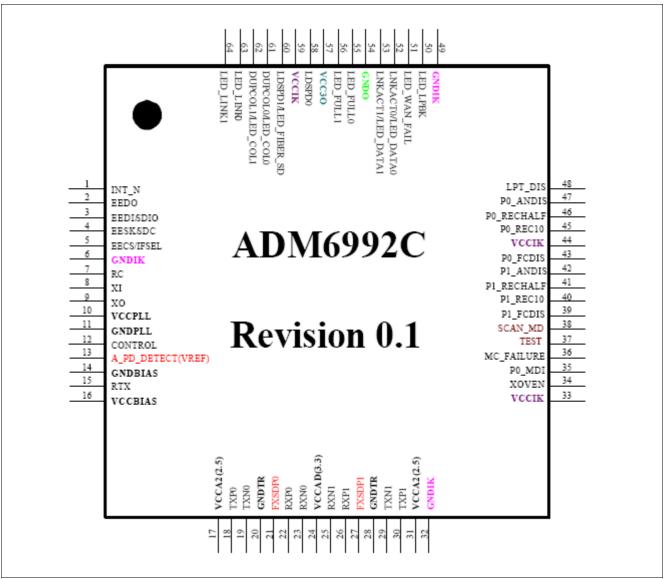

- Figure 2 NINJA C/CX (ADM6992C/CX) 64-Pin Assignment 10

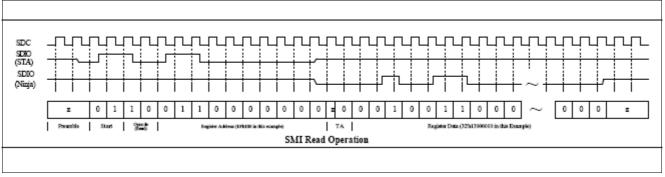

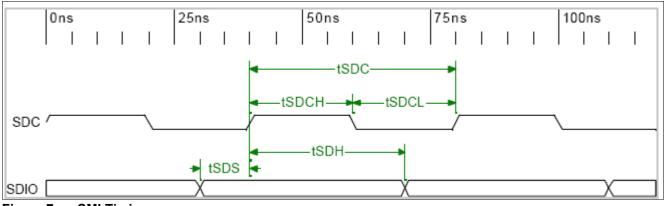

- Figure 3 SMI Read Operation 25

- Figure 4 SMI Write Operation 26

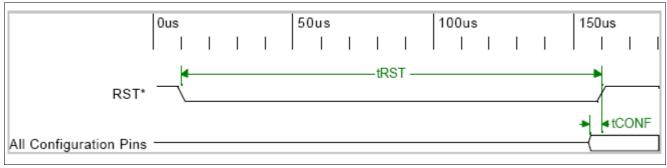

- Figure 5 Power on Reset Timing 76

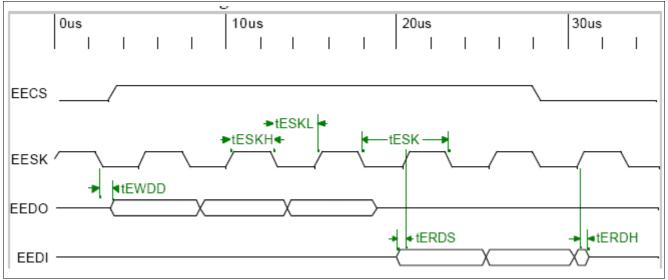

- Figure 6 EEPROM Interface Timing 76

- Figure 7 SMI Timing 77

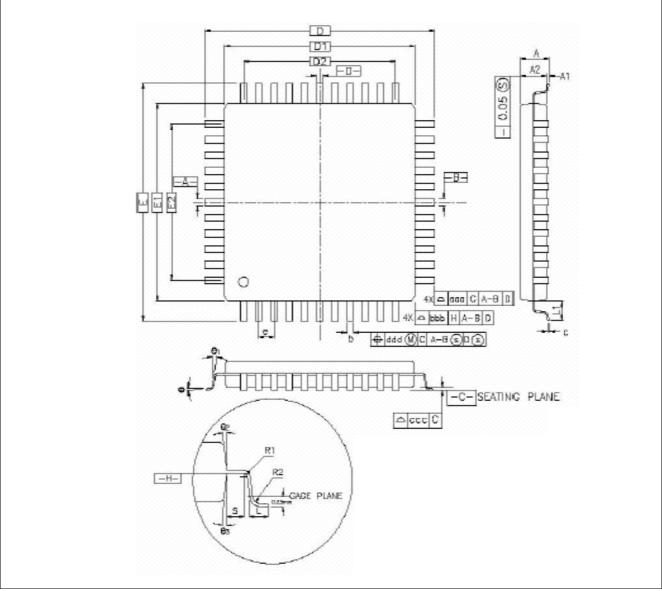

- Figure 8 64 pin LQFP Outside Dimension 78

#### List of Tables

# **List of Tables**

- Table 1Data Lengths Conventions 9

- Table 2Abbreviations for Pin Type 11

- Table 3Abbreviations for Buffer Type 11

- Table 4Port 0/1 Twisted Pair Interface (8 Pins)12

- Table 5LED Interface (12 Pins)12

- Table 6EEPROM Interface (4 Pins)15

- Table 7Configuration Interface (28 Pins)16

- Table 8Ground/Power Interface (27 Pins)17

- Table 9Miscellaneous (14 Pins)17

- Table 10Speed Configuration 21

- Table 11SMI Read/Write Command Format25

- Table 12EEPROM Register Map28

- Table 13

Registers Address SpaceRegisters Address Space 30

- Table 14 Registers Overview 30

- Table 15Register Access Types 31

- Table 16 Registers Clock Domains 32

- Table 17 Other Packet Filter Control Regsiters 43

- Table 18 Other Filter Regsiters 45

- Table 19 Other Tag Port Rule 0 Registers 48

- Table 20 Other Tag Port Rule 1 Regsiters 49

- Table 21 Serial Management Register Map 55

- Table 22 Registers Address Space 57

- Table 23 Registers Overview 57

- Table 24 Register Access Types 58

- Table 25

Registers Clock DomainsRegisters Clock Domains 58

- Table 26 Other Counter Registers 60

- Table 27Electrical Absolute Maximum Rating 75

- Table 28 Recommended Operating Conditions 75

- Table 29 DC Electrical Characteristics for 3.3 V Operation 75

- Table 30 Power on Reset Timing 76

- Table 31 EEPROM Interface Timing 76

- Table 32 SMI Timing 77

- Table 33Dimensions for 64 Pin LQFP Outside Dimension79

#### **Product Overview**

# 1 **Product Overview**

Features and the block diagram.

### 1.1 Overview

The NINJA C/CX (ADM6992C/CX) is a single chip integrating two 10/100 Mbps MDIX TX/FX transceivers with a two-port 10/100M Ethernet L2 switch controller. Features include a converter mode to meet demanding applications, such as Fiber-to-Ethernet media converters. The ADM6992CX is the environmentally friendly "green" package version.

The NINJA C/CX (ADM6992C/CX) supports 16 entries of packet classification and marking or filtering for TCP/UDP port numbering, IP protocol ID and Ethernet Type. These can be configured either using the EEPROM or on-the-fly using a small, low-cost micro controller.

On the media side, the NINJA C/CX (ADM6992C/CX)'s 0 and 1 ports support auto-MDIX 10Base-T/100Base-TX and 100Base-FX as specified by the IEEE 802.3 committee through uses of digital circuitry and high speed A/D.

The NINJA C/CX (ADM6992C/CX) also supports a serial management interface (SMI), which is initialized and configured using a small low-cost micro controller. It also provides the port status for remote agent monitoring and a smart counter for reporting port statistics.

### 1.2 Features

Main features:

- 2-port10/100M switch integrated with a 2-port PHY (10/100TX and 100FX)

- Provides TX<--> FX Converter modes with Link Pass Through (LPT)

- Built-in data buffer 6Kx64bit SRAM

- Up to 1k of Unicast. MAC addresses with a 4-way associative hashing table

- MAC address learning table with aging function

- Supports store & forward frame forwarding, modify cut-through frame forwarding, and fast cut-through frame forwarding.

- Forwarding and filtering at non-blocking full wire speed

- 802.3x flow control for full duplex and back-pressure for half duplex

- Supports Auto-Negotiation

- Supports Auto Cross-Over

- Packet lengths up to 9216 bytes.

- 16 entries of packet classification and marking or filtering for TCP/UDP Port Numbering, IP Protocol ID and Ethernet Type

- Serial Management Interface for low-end CPU

- · Hardware bandwidth control support for both ingress/egress traffic

- Provides port status for remote agent monitoring

- · Provides smart counters for port statistics reporting

- 64 LQFP packaging with 1.8 V/3.3 V power supply

**Product Overview**

### 1.3 Block Diagram

### 1.4 Data Lengths Conventions

### Table 1 Data Lengths Conventions

| qword  | 64 bits |

|--------|---------|

| dword  | 32 bits |

| word   | 16 bits |

| byte   | 8 bits  |

| nibble | 4 bits  |

# 2 NINJA C/CX Interface Description

This chapter describes Pin Diagram, Pin Type and Buffer Type Abbreviations, and Pin Descriptions.

### 2.1 Pin Diagram

Figure 2 NINJA C/CX (ADM6992C/CX) 64-Pin Assignment

# 2.2 Pin Type and Buffer Type Abbreviations

Standardized abbreviations:

#### Table 2Abbreviations for Pin Type

| Abbreviations | Description                                 |

|---------------|---------------------------------------------|

| Ι             | Standard input-only pin. Digital levels.    |

| 0             | Output. Digital levels.                     |

| I/O           | I/O is a bidirectional input/output signal. |

| AI            | Input. Analog levels.                       |

| AO            | Output. Analog levels.                      |

| AI/O          | Input or Output. Analog levels.             |

| PWR           | Power                                       |

| GND           | Ground                                      |

| MCL           | Must be connected to Low (JEDEC Standard)   |

| MCH           | Must be connected to High (JEDEC Standard)  |

| NU            | Not Usable (JEDEC Standard)                 |

| NC            | Not Connected (JEDEC Standard)              |

### Table 3 Abbreviations for Buffer Type

| Abbreviations | Description                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z             | High impedance                                                                                                                                                                                                                                                                     |

| PU1           | Pull up, 10 kΩ                                                                                                                                                                                                                                                                     |

| PD1           | Pull down, 10 kΩ                                                                                                                                                                                                                                                                   |

| PD2           | Pull down, 20 kΩ                                                                                                                                                                                                                                                                   |

| TS            | Tristate capability: The corresponding pin has 3 operational states: Low, high and high-<br>impedance.                                                                                                                                                                             |

| OD            | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. An external pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central resource. |

| OC            | Open Collector                                                                                                                                                                                                                                                                     |

| PP            | Push-Pull. The corresponding pin has 2 operational states: Active-low and active-high (identical to output with no type attribute).                                                                                                                                                |

| OD/PP         | Open-Drain or Push-Pull. The corresponding pin can be configured either as an output with the OD attribute or as an output with the PP attribute.                                                                                                                                  |

| ST            | Schmitt-Trigger characteristics                                                                                                                                                                                                                                                    |

| TTL           | TTL characteristics                                                                                                                                                                                                                                                                |

### 2.3 Pin Descriptions

Interfaces:

- Port 0/1 Twisted Pair Interface, 8 pins

- LED Interface, 12 pins

- EEPROM Interface, 4 pins

- Configuration Interface, 28 pins

- Ground/Power Interface, 27 pins

- Miscellaneous, 14 pins

Note: If not specified, all signals default to digital signals.

| Pin or Ball No. | Name    | Pin<br>Type | Buffer<br>Type | Function              |  |

|-----------------|---------|-------------|----------------|-----------------------|--|

| 18              | TXP 0   | AI/O        | Type           | Twisted Pair Transmit |  |

| 30              | TXP 1   | AI/O        |                | Output Positive.      |  |

| 19              | TXN_0   | AI/O        |                | Twisted Pair Transmit |  |

| 29              | TXN_1   | AI/O        |                | Output Negative.      |  |

| 22              | RXP_0   | AI/O        |                | Twisted Pair Receive  |  |

| 26              | RXP_1   | AI/O        |                | Input Positive.       |  |

| 23              | RXN_0   | AI/O        |                | Twisted Pair Receive  |  |

| 25              | RXN_1   | AI/O        |                | Input Negative.       |  |

| 21              | FXSDP_0 | AI          |                | OMD Signal Detect In  |  |

| 27              | FXSDP_1 | AI          |                |                       |  |

### Table 4 Port 0/1 Twisted Pair Interface (8 Pins)

#### Table 5LED Interface (12 Pins)

| Pin or<br>Ball<br>No. | Name                    | Pin<br>Type | Buffer<br>Type     | Function                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-------------------------|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52                    | LNKACT_0                | I/O         | TTL,<br>PD,<br>8mA | <b>PORT0 Link &amp; Active LED/Link LED.</b><br>If LEDMODE_0 is 1, this pin indicates both link status and RX/TX activity. When link status is LINK_UP, LNKACT_0 will be turned on. While PORT0 is receiving/transmitting data, LNKACT_0 will be off for 100ms and then on for 100ms.<br>If LEDMODE[0] is 0, this pin only indicates RX/TX activity. |

|                       | LED_DATA_0<br>LEDMODE_0 |             |                    | LED mode for LINK/ACT LED of PORT0.                                                                                                                                                                                                                                                                                                                  |

|                       |                         |             |                    | During power on reset, value will be latched by NINJA C/CX (ADM6992C/CX) at the rising edge of RESETL as LEDMODE_0.                                                                                                                                                                                                                                  |

| Pin or<br>Ball<br>No. | Name       | Pin<br>Type | Buffer<br>Type     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53                    | LNKACT_1   | I/O         | TTL,<br>PD,<br>8mA | <b>PORT1 Link &amp; Active LED/Link LED.</b><br>If LEDMODE_2 is 1, this pin indicates both link status and RX/TX activity. When link status is LINK_UP, LNKACT_1 will be turned on. While PORT1 is receiving/transmitting data, LNKACT_1 will be off for 100ms and then on for 100ms.<br>If LEDMODE[2] is 0, this pin only indicates RX/TX activity.                                                                                                                                                                                |

|                       | LED_DATA_1 |             |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       | LEDMODE_1  |             |                    | LED mode for LINK/ACT LED of PORT0 & PORT1.<br>During power on reset, value will be latched by NINJA C/CX<br>(ADM6992C/CX) at the rising edge of RESETL as LEDMODE_1.<br>If LEDMODE_1 is 1, DUPCOL[1:0] will display both duplex<br>condition and collision status.<br>If LEDMODE_1 is 0, only collision status will be displayed.                                                                                                                                                                                                  |

| 61                    | DUPCOL_0   | I/O         | TTL,<br>PD,<br>8mA | <b>PORT0 Duplex/Collision LED</b><br>If LEDMODE_1 is 1, this pin indicates both duplex condition and<br>collision status. When FULL_DUPLEX, this pin will be turned on<br>for PORT0. When HALF_DUPLEX and no collision occurs, this<br>pin will be turned off. When HALF_DUPLEX and a collision<br>occurs, this pin will be off for 100ms and then on for 100ms.<br>If LEDMODE_1 is 0, this pin indicates collision status. When in<br>HALF_DUPLEX and a collision occurs, this pin will be off for<br>100ms and turn on for 100ms. |

|                       | LED_COL_0  |             |                    | Collision LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       | DIS_LEARN  |             |                    | <b>Disable Address Learning.</b><br>During power on reset, value will be latched by NINJA C/CX<br>(ADM6992C/CX) at the rising edge of RESETL as DIS_LEARN.<br>If DIS_LEARN is 1, MAC address learning will be disabled.                                                                                                                                                                                                                                                                                                             |

| 62                    | DUPCOL_1   | I/O         | TTL,<br>PU,<br>8mA | <b>PORT1 Duplex</b><br>If LEDMODE_1 is 1, this pin indicates both duplex condition and<br>collision status. When FULL_DUPLEX, this pin will be turned on<br>for PORT1. When HALF_DUPLEX and no collision occurs, this<br>pin will be turned off. When HALF_DUPLEX and a collision<br>occurs, this pin will be off for 100ms and then on for 100ms. If<br>LEDMODE_1 is 0, this pin indicates collision status. When<br>HALF_DUPLEX and a collision occurs, this pin will be off for<br>100ms and turn on for 100ms.                  |

|                       | LED_COL_1  |             |                    | Collision LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 58                    | LDSPD_0    | I/O         | TTL,<br>PD,<br>8mA | <b>PORT0 Speed LED</b><br>Used to indicate speed status of PORT0. When operating in<br>100Mbps this pin is turned on, and when operating in 10Mbps this<br>pin is off.                                                                                                                                                                                                                                                                                                                                                              |

|                       | FXMODE0    |             |                    | <b>FXMODE0</b><br>During power on reset, value will be latched by NINJA C/CX<br>(ADM6992C/CX) at the rising edge of RESETL as bit 0 of<br>FXMODE.                                                                                                                                                                                                                                                                                                                                                                                   |

### Table 5LED Interface (12 Pins) (cont'd)

| Pin or<br>Ball<br>No. | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin<br>Type                                                                                                                                                                             | Buffer<br>Type                                                                                                            | Function                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60                    | LED_FIBER_SD       PD, 8mA       Used to indicate speed st 100Mbps this pin is turned pin is off.         LED_FIBER_SD       Used to indicate signal st (ADM6992C/CX) is operated to indicate signal st (ADM6992C/CX) is operated to Used to reset, variable of the sector o | Used to indicate speed status of PORT1. When operating in 100Mbps this pin is turned on, and when operating in 10Mbps this                                                              |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         | LED_FIBER_SD.<br>Used to indicate signal status of PORT1 when NINJA C/CX<br>(ADM6992C/CX) is operating in converter mode. |                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LED mode for LINK/ACT LED of PORT1.During power on reset, value will be latched by NINJA C/CX(ADM6992C/CX) at the rising edge of RESETL as LEDMODE2. $0_B$ TBD, ACT $1_B$ TBD, LINK/ACT |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                 |

| 63 LED_LINK_0 I/      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TTL,<br>PU,<br>8mA                                                                                                                                                                      | <b>PORT0 Link LED</b><br>This pin indicates link status. When Port0 link status is LINK_UP, this pin will be turned on.   |                                                                                                                                                                                                                                                                                                                                                                 |

|                       | FXMODE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                         |                                                                                                                           | FXMODE1During power on reset, value will be latched by NINJA C/CX(ADM6992C/CX) at the rising edge of RESETL as bit 1 ofFXMODE.FXMODE [1:0] Interface $00_B$ TBD, Both Port0 & Port1 are TP port $01_B$ TBD, Port0 is TP port and Port1 is FX port $10_B$ TBD, Port0 is TP port and Port1 is FX port (converter mode) $11_B$ TBD, Both Port0 & Port1 are FX port |

| 64                    | LED_LINK_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                                                                     | TTL,<br>PU,<br>8mA                                                                                                        | <b>PORT1 Link LED</b><br>This pin indicates link status. When Port1 link status is LINK_UP, this pin will be turned on.                                                                                                                                                                                                                                         |

|                       | BYPASS_PAUS<br>E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                         |                                                                                                                           | Bypass framewhich destination address is reserved IEEE MAC address.During power on reset, value will be latched by NINJA C/CX(ADM6992C/CX) at the rising edge of RESETL asBYPASS_PAUSE. $0_B$ <b>D</b> , Disable $1_B$ <b>E</b> , Enable                                                                                                                        |

| 55                    | LED_FULL_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                                                                     | TTL,<br>PU,<br>8mA                                                                                                        | <b>PORT0 Full Duplex LED</b><br>This pin indicates current duplex condition of PORT0. When<br>FULL_DUPLEX, this pin will be turned on. When HALF_DUPLEX<br>this pin will be turned off.                                                                                                                                                                         |

|                       | CHIPID_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                         |                                                                                                                           | Chip ID Bit 0.<br>During power on reset, value will be latched by NINJA C/CX<br>(ADM6992C/CX) at the rising edge of RESETL as CHIPID_0.                                                                                                                                                                                                                         |

### Table 5LED Interface (12 Pins) (cont'd)

| Pin or<br>Ball<br>No. | Name         | Pin<br>Type | Buffer<br>Type       | Function                                                                                                                                                                                                                           |

|-----------------------|--------------|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56                    | LED_FULL_1   | I/O         | TTL,<br>PU,<br>8mA   | <b>PORT1 Full Duplex LED</b><br>This pin indicates current duplex condition of PORT1. When<br>FULL_DUPLEX, this pin will be turned on. When HALF_DUPLEX<br>this pin will be turned off.                                            |

|                       | CHIPID_1     | -           |                      | Chip ID Bit 1During power on reset, value will be latched by NINJA C/CX $(ADM6992C/CX)$ at the rising edge of RESETL as CHIPID_1. $CHIPID_1:CHIPID_0]$ $00_B$ TBD, Master Device $01_B$ TBD, Slave Device $1X_B$ TBD, Slave Device |

| 50                    | LED_LPBK     | I/O         | TTL,<br>PU,          | Loop Back Test LED<br>While performing loop back test this pin is turned on.                                                                                                                                                       |

|                       | CHIPID_2     |             | 8mA                  | Chip ID Bit 2<br>During power on reset, value will be latched by NINJA C/CX<br>(ADM6992C/CX) at the rising edge of RESETL as CHIPID_2.                                                                                             |

| 51                    | LED_WAN_FAIL | P           | O TTL,<br>PD,<br>8mU | <b>WAN Fail LED</b><br>When receiving an OAM frame which has a S2 bit = 1, this pin is turned on.                                                                                                                                  |

|                       | DISBP        |             |                      | Disable Back PressureDuring power on reset, value will be latched by NINJA C/CX(ADM6992C/CX) at the rising edge of RESETL as DISBP. $0_B$ <b>E</b> , Enable back-pressure (Default) $1_B$ <b>D</b> , Disable back-pressure         |

### Table 5LED Interface (12 Pins) (cont'd)

### Table 6EEPROM Interface (4 Pins)

| Pin or<br>Ball<br>No. | Name       | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                   |

|-----------------------|------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                     | EEDO       | I           | TTL,           | EEPROM Data Output                                                                                                                                                         |

|                       |            |             | PU             | Serial data input from EEPROM. This pin is internal pull-up.                                                                                                               |

| 5                     | EECS/IFSEL | I/O         | PD,            | EEPROM Chip Select                                                                                                                                                         |

|                       |            |             | 4mA            | This pin is an active high chip enabled for EEPROM. WhenRESETL is low, it will be tristate. $0_B$ SM, Select Serial Management Interface $1_B$ EE, Select EEPROM interface |

| Pin or<br>Ball<br>No. | Name      | Pin<br>Type | Buffer<br>Type     | Function                                                                                                                                                                                                                |

|-----------------------|-----------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                     | EECK/SDC  | I/O         | TTL,<br>PU,<br>4mA | Serial Clock<br>This pin is the EEPROM clock source. When RESETL is low, it will<br>be tristate. This pin is internal pull-up.<br>If IFSEL is 1, this pin is used as EECK.<br>If IFSEL is 0, this pin is used as SDC.   |

| 3                     | EEDI/SDIO | I/O         | TTL,<br>PU,<br>4mA | <b>EEPROM Serial Data Input</b><br>This pin is the output for serial data transfer. When RESETL is<br>low, it will be tristate.<br>If IFSEL is 1, this pin is used as EEDI.<br>If IFSEL is 0, this pin is used as SDIO. |

### Table 6EEPROM Interface (4 Pins) (cont'd)

| Pin or<br>Ball<br>No. | Name       | Pin<br>Type | Buffer<br>Type | Function                                                                                    |

|-----------------------|------------|-------------|----------------|---------------------------------------------------------------------------------------------|

| 47                    | P0_ANDIS   | I           | TTL,<br>PD     | Auto-Negotiation Disable for PORT0 $0_B$ E, Enable $1_B$ D, Disable                         |

| 46                    | P0_RECHALF | I           | TTL,<br>PD     | Recommend Half Duplex Communication for PORT0 $0_B$ <b>F</b> , Full $1_B$ <b>H</b> , Half   |

| 45                    | P0_REC10   | I           | TTL,<br>PD     | Recommend 10M for PORT0           0 <sub>B</sub> 100, 100M           1 <sub>B</sub> 10, 10M |

| 43                    | P0_FCDIS   | I           | TTL,<br>PD     | Flow Control Disable for PORT0 $0_B$ E, Enable $1_B$ D, Disable                             |

| 42                    | P1_ANDIS   | I           | TTL,<br>PD     | Auto-Negotiation Disable for PORT1 $0_B$ E, Enable $1_B$ D, Disable                         |

| 41                    | P1_RECHALF | I           | TTL,<br>PD     | Recommend Half Duplex Communication for PORT1 $0_B$ F, Full $1_B$ H, Half                   |

| 40                    | P1_REC10   | I           | TTL,<br>PD     | Recommend 10M for PORT1           0 <sub>B</sub> 100, 100M           1 <sub>B</sub> 10, 10M |

| 39                    | P1_FCDIS   | I           | TTL,<br>PD     | Flow Control Disable for PORT1 $0_B$ $\mathbf{E}$ , Enable $1_B$ $\mathbf{D}$ , Disable     |

### Table 7 Configuration Interface (28 Pins)

| Pin or<br>Ball<br>No. | Name   | Pin<br>Type | Buffer<br>Type | Function                                                                                   |

|-----------------------|--------|-------------|----------------|--------------------------------------------------------------------------------------------|

| 34                    | XOVEN  | I           | TTL,<br>PU     | Auto-MDIX Enable.0BD, Disable1BE, Enable                                                   |

| 35                    | P0_MDI | I           | TTL,<br>PU     | MDI/MDIX Control for PORT0This setting will be ignored if enabled Auto-MDIX.00MDIX, MDIX11 |

### Table 7Configuration Interface (28 Pins) (cont'd)

### Table 8 Ground/Power Interface (27 Pins)

| Pin or<br>Ball<br>No. | Name    | Pin<br>Type | Buffer<br>Type | Function                                      |

|-----------------------|---------|-------------|----------------|-----------------------------------------------|

| 20, 28                | GNDTR   | GND, A      |                | Ground used by AD receiver/transmitter block. |

| 17, 31                | VCCA2   | PWR, A      |                | 1.8 V used for Analogue block                 |

| 24                    | VCCAD   | PWR, A      |                | 3.3 V used for TX line driver                 |

| 14                    | GNDBIAS | GND, A      |                | Ground used by digital substrate              |

| 16                    | VCCBIAS | PWR, A      |                | 3.3 V used for bios block                     |

| 11                    | GNDPLL  | GND, A      |                | Ground used by PLL                            |

| 10                    | VCCPLL  | PWR, A      |                | 1.8 V used for PLL                            |

| 6, 32,<br>49          | GNDIK   | GND, A      |                | Ground used by digital core and pre-driver    |

| 33, 44,<br>59         | VCCIK   | PWR, D      |                | 1.8 V used for digital core and pre-driver    |

| 54                    | GNDO    | GND, D      |                | Ground used by digital pad                    |

| 57                    | VCC3O   | PWR, D      |                | 3.3 V used for digital pad.                   |

#### Table 9Miscellaneous (14 Pins)

| Pin or<br>Ball<br>No. | Name        | Pin<br>Type | Buffer<br>Type     | Function                                                                                                                                                                                                           |

|-----------------------|-------------|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | ÎNT         | 0           | TTL,<br>OD,<br>4mA | Interrupt<br>This pin will be used to interrupt external management device.<br>When EEPROM register 0x5 Bit [15] is 0, this pin is low-active.<br>When EEPROM register 0x5 Bit [15] is 1, this pin is high-active. |

| 12                    | CONTROL     | AO          |                    | <b>FET Control Signal</b><br>The pin is used to control FET for 3.3 V to 1.8 V regulator.                                                                                                                          |

| 15                    | RTX         | А           |                    | TX Resistor                                                                                                                                                                                                        |

| 13                    | A_PD_DETECT | А           |                    | Analog Reference Voltage                                                                                                                                                                                           |

| 7                     | RC          | I           | TTL,<br>ST         | <b>RC Input for Power On Reset</b><br>NINJA C/CX (ADM6992C/CX) sample pin RC as RESETL with<br>the clock input from pin XI.                                                                                        |

| Pin or<br>Ball<br>No. | Name    | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                      |

|-----------------------|---------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                     | XI      | AI          |                | <b>25M Crystal Input</b><br>25M Crystal Input. Variation is limited to +/- 50ppm.                                                                                             |

| 9                     | ХО      | AO          |                | <b>25M Crystal Output</b><br>When connected to oscillator, this pin should left unconnected.                                                                                  |

| 37                    | TEST    | 1           | TTL,<br>PD     | <b>Test pin</b><br>During power on reset, value will be latched by NINJA C/CX<br>(ADM6992C/CX) at the rising edge of RESETL as TEST.<br>Connect to GND at normal application. |

| 38                    | SCAN_MD | I           | TTL,<br>PD     | Scan Mode<br>For Test Only. Connect to GND at normal application.                                                                                                             |

### Table 9Miscellaneous (14 Pins) (cont'd)

# **3** Function Description

The NINJA C/CX (ADM6992C/CX) integrates two 100Base-X physical layer devices (PHY), two complete 10BaseT modules, a two-port 10/100 switch controller and memory into a single chip for both 10Mbps and 100 Mbps Ethernet switch operation. It also supports 100Base-FX operations through external fiber-optic transceivers. The device is capable of operating in either Full-Duplex or Half-Duplex mode in both 10 Mbps and 100 Mbps operation. Operation modes can be selected by hardware configuration pins, software settings of management registers, or determined by the on-chip auto negotiation logic.

The NINJA C/CX (ADM6992C/CX) consists of four major blocks:

- OAM Engine

- 10/100M PHY Block

- Switch Controller Block

- Built-in 6Kx64 SSRAM

### 3.1 10/100M PHY Block

The 100Base-X section of the device implements the following functional blocks:

- 100Base-X physical coding sub-layer (PCS)

- 100Base-X physical medium attachment (PMA)

- 100Base-X physical medium dependent (PMD)

The 10Base-T section of the device implements the following functional blocks:

- 10Base-T physical layer signaling (PLS)

- 10Base-T physical medium attachment (PMA)

The 100Base-X and 10Base-T sections share the following functional blocks:

- Clock synthesizer module

- MII Registers

- IEEE 802.3u auto negotiation

The interfaces used for the communication between the PHY block and switch core is a MII interface.

An Auto MDIX function is supported. This function can be Enabled/Disabled using the hardware pin. A digital approach for the integrated PHY of the NINJA C/CX (ADM6992C/CX) has been adopted.

# 3.2 Auto Negotiation and Speed Configuration

### 3.2.1 Auto Negotiation

The Auto Negotiation function provides a mechanism for exchanging configuration information between two ends of a link segment and automatically selecting the highest performance mode of operations supported by both devices. Fast Link Pulse (FLP) Bursts provide the signaling used to communicate auto negotiation abilities between two devices at each end of a link segment. For further details regarding auto negotiation, refer to Clause 28 of the IEEE 802.3u specification. The NINJA C/CX (ADM6992C/CX) supports four different Ethernet protocols, so the inclusion of auto negotiation ensures that the highest performance protocol will be selected based on the ability of the link partner.

The auto negotiation function within the NINJA C/CX (ADM6992C/CX) can be controlled either by internal register access or by the use of configuration pins. If disabled, auto negotiation will not occur until software enables bit 12 in MII Register 0. If auto negotiation is enabled, the negotiation process will commence immediately.

When auto negotiation is enabled, the NINJA C/CX (ADM6992C/CX) transmits the abilities programmed into the auto negotiation advertisement register at address  $04_H$  via FLP bursts. Any combination of 10 Mbps, 100 Mbps, half duplex, and full duplex modes may be selected. Auto negotiation controls the exchange of configuration information. Upon successfully auto negotiating, the abilities reported by the link partner are stored in the auto negotiation link partner ability register at address  $05_H$ .

The contents of the "auto negotiation link partner ability register" are used to automatically configure the highest performance protocol between the local and far-end nodes. Software can determine which mode has been configured by auto negotiation, by comparing the contents of register  $04_{\rm H}$  and  $05_{\rm H}$  and then selecting the technology whose bit is set in both registers of highest priority relative to the following list:

- 1. 100Base-TX full duplex (highest priority)

- 2. 100Base-TX half duplex

- 3. 10Base-T full duplex

- 4. 10Base-T half duplex (lowest priority)

The basic mode control register at address  $0_{\rm H}$  controls the enabling, disabling and restarting of the auto negotiation function. When auto negotiation is disabled, the speed selection bit (bit 13) controls switching between 10 Mbps or 100 Mbps operation, while the duplex mode bit (bit 8) controls switching between full duplex operation and half duplex operation. The speed selection and duplex mode bits have no effect on the mode of operations when the auto negotiation enabled bit (bit 12) is set.

The basic mode status register at address  $1_H$  indicates the set of available abilities for technology types (bit 15 to bit 11), auto negotiation ability (bit 3), and extended register capability (bit 0). These bits are hardwired to indicate the full functionality of the NINJA C/CX (ADM6992C/CX). The BMSR also provides status on:

- Whether auto negotiation is complete (bit 5)

- Whether the Link Partner is advertising that a remote fault has occurred (bit 4)

- Whether a valid link has been established (bit 2)

The auto negotiation advertisement register at address  $04_{H}$  indicates the auto negotiation abilities to be advertised by the NINJA C/CX (ADM6992C/CX). All available abilities are transmitted by default, but writing to this register or configuring external pins can suppress any ability.

The auto negotiation link partner ability register at address  $05_{H}$  indicates the abilities of the Link Partner as indicated by auto negotiation communication. The contents of this register are considered valid when the auto negotiation complete bit (bit 5, register address  $1_{H}$ ) is set.

### 3.2.2 Speed Configuration

The twelve sets of four pins listed in **Table 10** configure the speed capability of each channel of the NINJA C/CX (ADM6992C/CX). The logic states of these pins are latched into the advertisement register (register address  $4_H$ )

Data Sheet

for auto negotiation purpose. These pins are also used for evaluating the default value in the base mode control register (register  $0_H$ ) according to **Table 10**.

In order to make these pins have the same Read/Write priority as software, they should be programmed to  $1111111_{B}$  in case a user wishes to update the advertisement register through software.

| Advertis<br>e all | Advertis<br>e single | Paralle<br>I detect    | Auto<br>Negoti-            | Speed<br>(Pin & | Duplex<br>(Pin & | Auto<br>Negot | Advertise<br>Capability |          |         |         | Parallel Detect<br>Capability |          |         |         |

|-------------------|----------------------|------------------------|----------------------------|-----------------|------------------|---------------|-------------------------|----------|---------|---------|-------------------------------|----------|---------|---------|

| capabilit<br>y    | capabili<br>ty       | follow<br>IEEE<br>std. | ation<br>(Pin &<br>EEPROM) | EEPROM<br>)     | EEPROM<br>)      | iation        | 10<br>0F                | 10<br>0H | 10<br>F | 10<br>H | 10<br>0F                      | 10<br>0H | 10<br>F | 10<br>H |

| 1                 | 0                    | 0                      | 1                          | Х               | Х                | 1             | 1                       | 1        | 1       | 1       | 1                             | 0        | 1       | 0       |

| 1                 | 0                    | 1                      | 1                          | Х               | Х                | 1             | 1                       | 1        | 1       | 1       | 0                             | 1        | 0       | 1       |

| 1                 | 1                    | 0                      | 1                          | Х               | Х                | 1             | 1                       | 0        | 0       | 0       | 1                             | 0        | 0       | 0       |

| 1                 | 1                    | 1                      | 1                          | Х               | Х                | 1             | 1                       | 0        | 0       | 0       | 0                             | 1        | 0       | 0       |

| 0                 | 0                    | 0                      | 1                          | 1               | 1                | 1             | 1                       | 1        | 1       | 1       | 1                             | 0        | 1       | 0       |

| 0                 | 0                    | 1                      | 1                          | 1               | 1                | 1             | 1                       | 1        | 1       | 1       | 0                             | 1        | 0       | 1       |