# **TABLE OF CONTENTS**

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram 1                   |

| Revision History                             |

| General Description                          |

| Specifications                               |

| Timing Characteristics11                     |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| ESD Caution15                                |

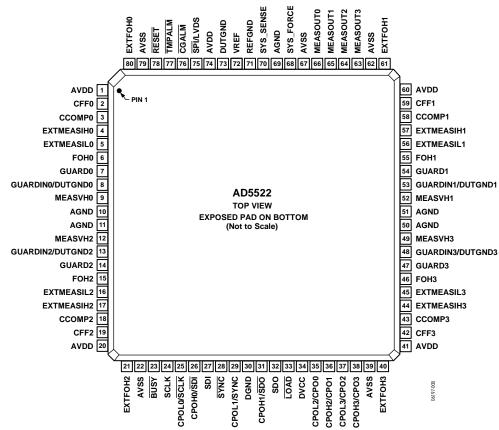

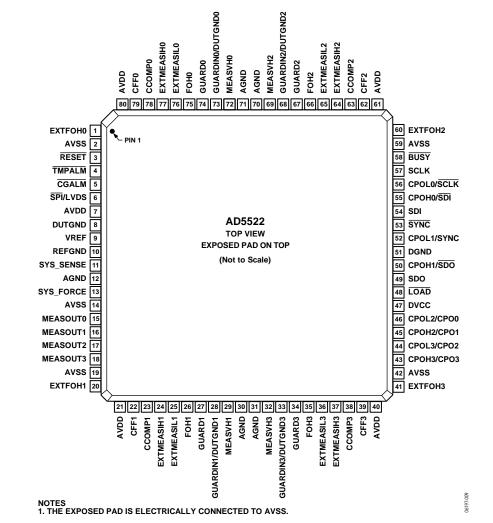

| Pin Configurations and Function Descriptions |

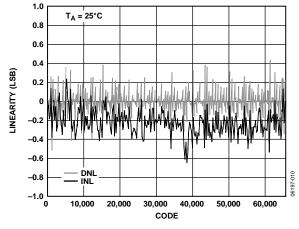

| Typical Performance Characteristics          |

| Terminology                                  |

| Theory of Operation                          |

| Force Amplifier                              |

| Comparators                                  |

| Clamps                                       |

| Current Range Selection                      |

| High Current Ranges                          |

| Measure Current Gains                        |

| VMID Voltage                                 |

| Choosing Power Supply Rails                  |

| Measure Output (MEASOUTx Pins)               |

| Device Under Test Ground (DUTGND)            |

| Guard Amplifier                              |

| Compensation Capacitors                      |

| System Force and Sense Switches              |

| Temperature Sensor                           |

| DAC Levels                                   |

| Offset DAC                                   |

| Gain and Offset Registers                    |

| Cached X2 Registers                          |

| Reference Voltage (VREF)                     |

| Reference Selection                          |

|    | Calibration                            | 38 |

|----|----------------------------------------|----|

|    | Additional Calibration                 | 39 |

|    | System Level Calibration               | 39 |

| Ci | rcuit Operation                        | 40 |

|    | Force Voltage (FV) Mode                | 40 |

|    | Force Current (FI) Mode                | 41 |

| Se | rial Interface                         | 42 |

|    | SPI Interface                          | 42 |

|    | LVDS Interface                         | 42 |

|    | Serial Interface Write Mode            | 42 |

|    | RESET Function                         | 42 |

|    | BUSY and LOAD Functions                | 42 |

|    | Register Update Rates                  | 44 |

|    | Register Selection                     | 44 |

|    | Write System Control Register          | 46 |

|    | Write PMU Register                     | 48 |

|    | Write DAC Register                     | 50 |

|    | Read Registers                         | 53 |

|    | Readback of System Control Register    | 54 |

|    | Readback of PMU Register               | 55 |

|    | Readback of Comparator Status Register | 56 |

|    | Readback of Alarm Status Register      | 56 |

|    | Readback of DAC Register               | 57 |

| Aŗ | pplications Information                | 58 |

|    | Power-On Default                       | 58 |

|    | Setting Up the Device on Power-On      | 58 |

|    | Changing Modes                         | 59 |

|    | Required External Components           | 59 |

|    | Power Supply Decoupling                | 60 |

|    | Power Supply Sequencing                | 60 |

|    | Typical Application for the AD5522     | 60 |

| O  | utline Dimensions                      | 62 |

|    | Ordering Guide                         | 63 |

|    |                                        |    |

## **REVISION HISTORY**

| 6/2018—Rev. E to Rev. F                                   |    |

|-----------------------------------------------------------|----|

| Changes to Table 1                                        | 7  |

| Changes to Table 2                                        | 11 |

| Changes to Figure 5                                       | 13 |

| Changes to Choosing Power Supply Rails Section and Note 2 | 2, |

| Table 10                                                  | 33 |

| Moved Table 11                                            | 34 |

| Changes to MV Transfer Function, Table 11 and Note 3,     |    |

| Table 11                                                  | 34 |

| Changes to Table 39                                       | 60 |

| Changes to Ordering Guide                                 | 63 |

|                                                           |    |

#### 5/2012—Rev. D to Rev. E

| Change to MV Transfer Funct | n, Table 1133 |

|-----------------------------|---------------|

|-----------------------------|---------------|

### 2/2011-Rev. C to Rev. D

| Changes to Measure Current, Gain Error Tempco Paramete | r6 |

|--------------------------------------------------------|----|

| Changes to Force Current, Common Mode Error (Gain = 5) | )  |

| and Common Mode Error (Gain = 10) Parameters           | 7  |

| Changes to Figure 5                                    | 13 |

| Changes to Figure 6                                    | 14 |

| Changes to Figure 15                                   | 22 |

| Changes to High Current Ranges Section                 | 31 |

| Changes to Gain and Offset Registers Section           | 36 |

| Changes to Endnote 1 in Table 17 and Figure 56         | 43 |

| Changes to Register Update Rates and Figure 57         | 44 |

| Changes to Bit 15 to Bit 0 Description in Table 28     | 50 |

### 5/2010—Rev. B to Rev. C

| Changes to Compensation Capacitors Section                                     | 34 |

|--------------------------------------------------------------------------------|----|

| Changes to Gain and Offset Registers Section                                   | 36 |

| Changes to Table 14 and Reducing Zero-Scale Error Section                      | 38 |

| Changes to Serial Interface Write Mode Section and $\overline{\text{BUSY}}$ as | nd |

| LOAD Functions Section                                                         | 42 |

| Changes to Table 17                                                            | 43 |

| Added Table 18; Renumbered Sequentially                                        | 43 |

| Changes to Register Update Rates Section                                       | 44 |

| Changes to Table 23                                                            | 46 |

| Changes to Table 31                                                            | 54 |

|                                                                                |    |

#### 10/2009—Rev. A to Rev. B

| Changes to Table 1                                     | 6  |

|--------------------------------------------------------|----|

| Changes to Table 2                                     | 11 |

| Added Figure 13 and Figure 15; Renumbered Sequentially | 22 |

| Added Figure 16                                        | 23 |

| Changes to Figure 21                                   | 23 |

| Changes to Clamps Section                              | 30 |

| Changes to Table 22, Bit 21 to Bit 18 Description      | 44 |

| Changes to Table 25, Bit 9 Description                 | 47 |

| Changes to Table 28                                    | 49 |

| Changes to Figure 59                                   |    |

| 0 0                                                    |    |

#### 10/2008-Rev. 0 to Rev. A

| Changes to Table 1                                                                      | 6  |

|-----------------------------------------------------------------------------------------|----|

| Change to 4 DAC X1 Parameter, Table 2                                                   | 11 |

| Changes to Table 3                                                                      | 12 |

| Change to Reflow Soldering Parameter, Table 4                                           | 15 |

| Changes to Figure 18, Figure 19, Figure 20, and Figure 21                               | 23 |

| Changes to Figure 25                                                                    | 24 |

| Changes to Force Amplifier Section                                                      | 29 |

| Changes to Clamps Section                                                               | 29 |

| Changes to High Current Ranges Section                                                  | 30 |

| Changes to Choosing Power Supply Rails Section                                          | 32 |

| Changes to Compensation Capacitors Section                                              | 33 |

| Added Table 14, Renumbered Tables Sequentially                                          | 36 |

| Changes to Reference Selection Example                                                  | 36 |

| Changes to Table 15 and $\overline{\text{BUSY}}$ and $\overline{\text{LOAD}}$ Functions |    |

| Section                                                                                 | 40 |

| Changes to Table 17 and Register Update Rates Section                                   | 41 |

| Added Table 38                                                                          | 57 |

| Changes to Ordering Guide                                                               | 60 |

## 7/2008—Revision 0: Initial Version

# **GENERAL DESCRIPTION**

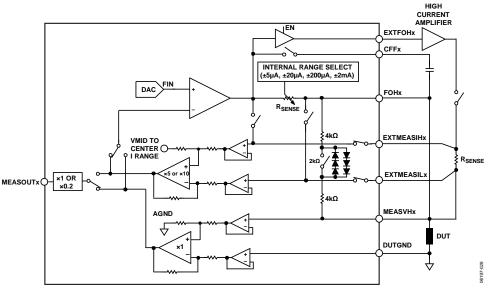

The AD5522 is a high performance, highly integrated parametric measurement unit consisting of four independent channels. Each per-pin parametric measurement unit (PPMU) channel includes five 16-bit, voltage output DACs that set the programmable input levels for the force voltage inputs, clamp inputs, and comparator inputs (high and low). Five programmable force and measure current ranges are available, ranging from  $\pm 5 \ \mu A$  to  $\pm 80 \ mA$ . Four of these ranges use on-chip sense resistors; one high current range up to  $\pm 80 \ mA$  is available per channel using off-chip sense resistors. Currents in excess of  $\pm 80 \ mA$  require an external amplifier. Low capacitance DUT connections (FOHx and EXTFOHx) ensure that the device is suited to relayless test systems.

The PMU functions are controlled via a simple 3-wire serial interface compatible with SPI, QSPI<sup>™</sup>, MICROWIRE<sup>™</sup>, and DSP interface standards. Interface clocks of 50 MHz allow fast updating of modes. The low voltage differential signaling (LVDS) interface protocol at 83 MHz is also supported. Comparator outputs are provided per channel for device go-no-go testing and characterization. Control registers allow the user to easily change force or measure conditions, DAC levels, and selected current ranges. The SDO (serial data output) pin allows the user to read back information for diagnostic purposes.

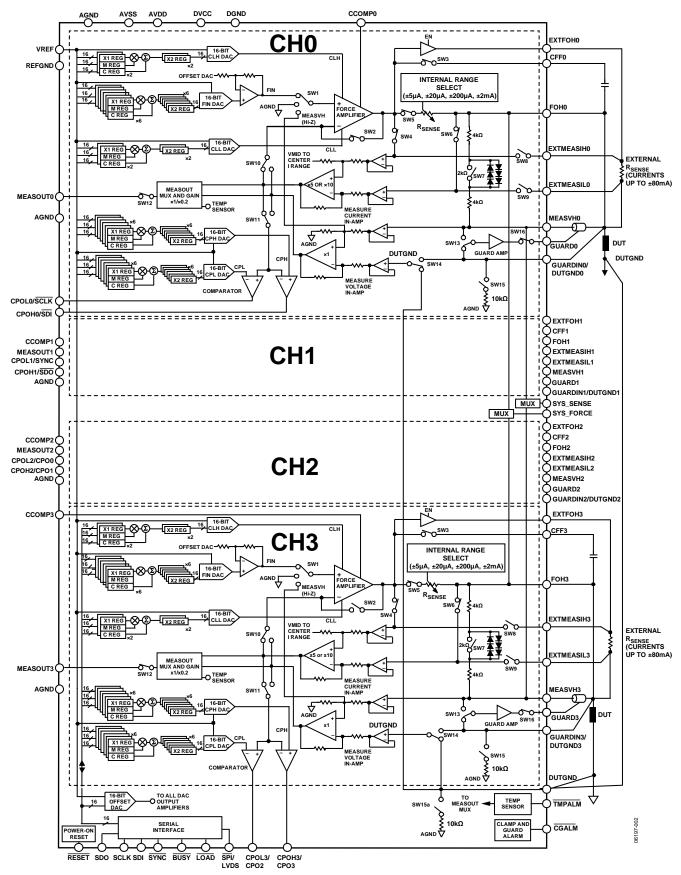

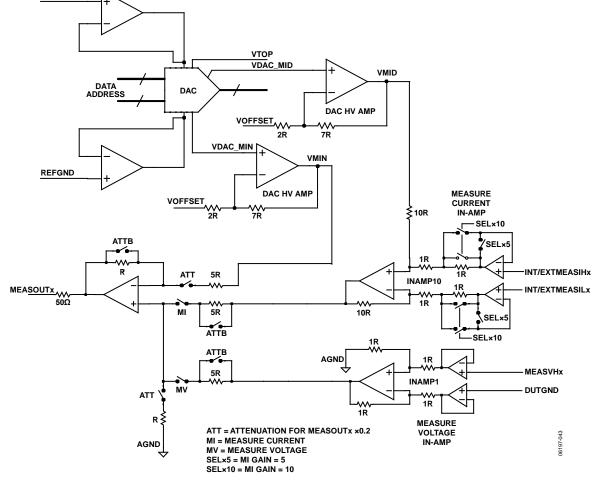

Figure 2. Detailed Block Diagram

# **SPECIFICATIONS**

$AVDD \ge 10 \text{ V}; AVSS \le -5 \text{ V}; |AVDD - AVSS| \ge 20 \text{ V} and \le 33 \text{ V}; DVCC = 2.3 \text{ V} to 5.25 \text{ V}; VREF = 5 \text{ V}; REFGND = DUTGND = AGND = 0 \text{ V};$ gain (M), offset (C), and DAC offset registers at default values;  $T_1 = 25^{\circ}$ C to 90°C, unless otherwise noted. (FV = force voltage, FI = force current, MV = measure voltage, MI = measure current, FS = full scale, FSR = full-scale range, FSVR = full-scale voltage range, FSCR = full-scale current range.)

| Parameter                                     | Min      | Typ <sup>1</sup> | Max      | Unit     | Test Conditions/Comments                                                                                         |

|-----------------------------------------------|----------|------------------|----------|----------|------------------------------------------------------------------------------------------------------------------|

| FORCE VOLTAGE                                 |          |                  |          |          |                                                                                                                  |

| FOHx Output Voltage Range <sup>2</sup>        | AVSS + 4 |                  | AVDD – 4 | v        | All current ranges from FOHx at full-scale current, includes ±1 V dropped across sense resistor                  |

| EXTFOHx Output Voltage Range <sup>2</sup>     | AVSS + 3 |                  | AVDD – 3 | v        | External high current range at full-scale current, does not include ±1 V dropped across sense resistor           |

| Output Voltage Span                           |          | 22.5             |          | V        |                                                                                                                  |

| Offset Error                                  | -50      |                  | +50      | mV       | Measured at midscale code; prior to calibration                                                                  |

| Offset Error Tempco <sup>2</sup>              |          | -10              |          | μV/°C    | Standard deviation = $20 \mu$ V/°C                                                                               |

| Gain Error                                    | -0.5     |                  | +0.5     | % FSR    | Prior to calibration                                                                                             |

| Gain Error Tempco <sup>2</sup>                |          | 0.5              |          | ppm/°C   | Standard deviation = 0.5 ppm/°C                                                                                  |

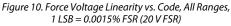

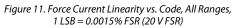

| Linearity Error                               | -0.01    |                  | +0.01    | % FSR    | $FSR = full-scale range (\pm 10 V), gain and offset errors calibrated out$                                       |

| Short-Circuit Current Limit <sup>2</sup>      | -150     |                  | +150     | mA       | ±80 mA range                                                                                                     |

|                                               | -10      |                  | +10      | mA       | All other ranges                                                                                                 |

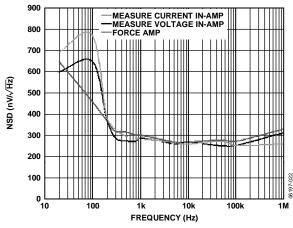

| Noise Spectral Density (NSD) <sup>2</sup>     |          | 320              |          | nV/√Hz   | 1 kHz, at FOHx in FV mode                                                                                        |

| MEASURE CURRENT                               |          |                  |          |          | Measure current = $(I_{DUT} \times R_{SENSE} \times gain)$ , amplifier<br>gain = 5 or 10, unless otherwise noted |

| Differential Input Voltage Range <sup>2</sup> | -1.125   |                  | +1.125   | V        | Voltage across $R_{\text{SENSE}}$ ; gain = 5 or 10                                                               |

| Output Voltage Span                           |          | 22.5             |          | V        | Measure current block with VREF = 5 V, MEASOUT scaling happens after                                             |

| Offset Error                                  | -0.5     |                  | +0.5     | % FSCR   | $V(R_{SENSE}) = \pm 1 V$ , measured with zero current flowing                                                    |

| Offset Error Tempco <sup>2</sup>              |          | 1                |          | μV/°C    | Referred to MI input; standard deviation = $4 \mu V/^{\circ}C$                                                   |

| Gain Error                                    | -1       |                  | +1       | % FSCR   | Using internal current ranges                                                                                    |

|                                               | -0.5     |                  | +0.5     | % FSCR   | Measure current amplifier alone                                                                                  |

| Gain Error Tempco <sup>2</sup>                |          | -2               |          | ppm/°C   | Standard deviation = 2 ppm/°C, measure current amplifier alone; internal sense resistor 25 ppm/°C                |

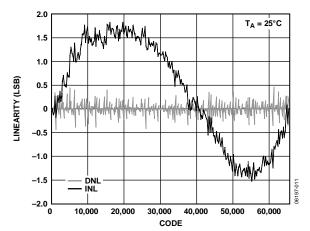

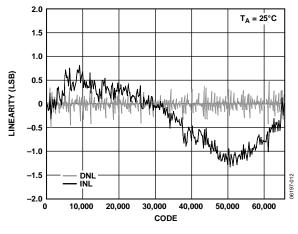

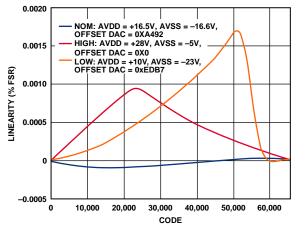

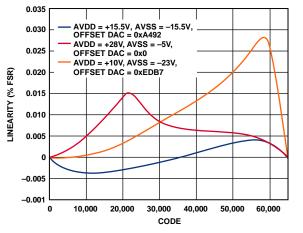

| Linearity Error (MEASOUTx Gain = 1)           | -0.015   |                  | +0.015   | % FSR    | MI gain = 10                                                                                                     |

|                                               | -0.01    |                  | +0.01    | % FSR    | MI gain = 5                                                                                                      |

| Linearity Error (MEASOUTx Gain = 0.2)         | -0.06    |                  | +0.06    | % FSR    | MI gain = 10, AVDD = 28 V, AVSS = -5 V, offset<br>DAC = 0x0                                                      |

|                                               | -0.11    |                  | +0.11    | % FSR    | MI gain = 10, AVDD = 10 V, AVSS = -23 V, offset<br>DAC = 0x0EDB7                                                 |

|                                               | -0.015   |                  | +0.015   | % FSR    | MI gain = 10, AVDD = 15.25 V, AVSS = -15.25 V,<br>offset DAC = 0xA492                                            |

|                                               | -0.06    |                  | +0.06    | % FSR    | MI gain = 5, AVDD = 28 V, AVSS = -5 V, offset<br>DAC = 0x0                                                       |

|                                               | -0.01    |                  | +0.01    | % FSR    | MI gain = 5, AVDD = 10 V, AVSS = -23 V, offset<br>DAC = 0xEDB7                                                   |

|                                               | -0.01    |                  | +0.01    | % FSR    | MI gain = 5, AVDD = 15.25 V, AVSS = -15.25 V, offse<br>DAC = 0xA492                                              |

| Common-Mode Voltage Range <sup>2</sup>        | AVSS + 4 |                  | AVDD – 4 | V        |                                                                                                                  |

| Common-Mode Error (Gain = 5)                  | -0.01    |                  | +0.01    | % FSCR/V | % of full-scale change at force output per V change<br>in DUT voltage                                            |

| Common-Mode Error (Gain = 10)                 | -0.005   |                  | +0.005   | % FSCR/V | % of full-scale change at force output per V change<br>in DUT voltage                                            |

| Sense Resistors                               |          |                  |          |          | Sense resistors are trimmed to within 1%                                                                         |

|                                               |          | 200              |          | kΩ       | ±5 μA range                                                                                                      |

|                                               |          | 50               |          | kΩ       | ±20 μA range                                                                                                     |

|                                               |          | 5                |          | kΩ       | ±200 μA range                                                                                                    |

|                                               |          | 0.5              |          | kΩ       | ±2 mA range                                                                                                      |

| Parameter                                 | Min      | Typ <sup>1</sup> | Max      | Unit      | Test Conditions/Comments                                                                                       |

|-------------------------------------------|----------|------------------|----------|-----------|----------------------------------------------------------------------------------------------------------------|

| Measure Current Ranges <sup>2</sup>       |          |                  |          |           | Specified current ranges are achieved with VREF = 5 V and MI gain = 10, or with VREF = $2.5$ V and MI gain = 5 |

|                                           |          | ±5               |          | μA        | Set using internal sense resistor                                                                              |

|                                           |          | ±20              |          | μA        | Set using internal sense resistor                                                                              |

|                                           |          | ±200             |          | μA        | Set using internal sense resistor                                                                              |

|                                           |          | ±2               |          | mA        | Set using internal sense resistor                                                                              |

|                                           |          |                  | ±80      | mA        | Set using external sense resistor; internal amplifier can drive up to $\pm 80$ mA                              |

| Noise Spectral Density (NSD) <sup>2</sup> |          | 400              |          | nV/√Hz    | 1 kHz, MI amplifier only, inputs grounded                                                                      |

| FORCE CURRENT                             |          |                  |          |           |                                                                                                                |

| Voltage Compliance, FOHx <sup>2</sup>     | AVSS + 4 |                  | AVDD – 4 | v         |                                                                                                                |

| Voltage Compliance, EXTFOHx <sup>2</sup>  | AVSS + 3 |                  | AVDD – 3 | V         | Supports 64 mA sink current and 80 mA source current                                                           |

| 5 1 2                                     | AVSS + 6 |                  | AVDD – 3 | v         | Supports 80 mA sink and source current                                                                         |

| Offset Error                              | -0.5     |                  | +0.5     | % FSCR    | Measured at midscale code, 0 V, prior to calibration                                                           |

| Offset Error Tempco <sup>2</sup>          | 0.0      | 5                | 1010     | ppm FS/°C | Standard deviation = 5 ppm/°C                                                                                  |

| Gain Error                                | -1.5     | 5                | +1.5     | % FSCR    | Prior to calibration                                                                                           |

| Gain Error Tempco <sup>2</sup>            | 1.5      | -6               | 11.5     | ppm/°C    | Standard deviation = 5 ppm/°C                                                                                  |

| Linearity Error                           | -0.02    | 0                | +0.02    | % FSCR    | standard deviation = 5 ppm/ C                                                                                  |

| Common-Mode Error (Gain = 5)              | -0.02    |                  | +0.02    | % FSCR/V  | % of full-scale change per V change in DUT voltage                                                             |

| Common-Mode Error (Gain = $3$ )           |          |                  |          |           |                                                                                                                |

|                                           | -0.006   |                  | +0.006   | % FSCR/V  | % of full-scale change per V change in DUT voltage                                                             |

| Force Current Ranges                      |          |                  |          |           | Specified current ranges achieved with VREF = 5 V and MI gain = 10, or with VREF = $2.5$ V and MI gain = $5$ V |

|                                           |          | ±5               |          | μΑ        | Set using internal sense resistor, 200 k $\Omega$                                                              |

|                                           |          | ±20              |          | μΑ        | Set using internal sense resistor, 50 k $\!\Omega$                                                             |

|                                           |          | ±200             |          | μΑ        | Set using internal sense resistor, 5 k $\Omega$                                                                |

|                                           |          | ±2               |          | mA        | Set using internal sense resistor, 500 $\Omega$                                                                |

|                                           |          | ±64              | ±80      | mA        | Set using external sense resistor, internal amplifier can drive up to $\pm 80$ mA with increased compliance    |

| MEASURE VOLTAGE                           |          |                  |          |           |                                                                                                                |

| Measure Voltage Range <sup>2</sup>        | AVSS + 4 |                  | AVDD – 4 | V         |                                                                                                                |

| Offset Error                              | -10      |                  | +10      | mV        | Gain = 1, measured at 0 V                                                                                      |

|                                           | -25      |                  | +25      | mV        | Gain = 0.2, measured at 0 V                                                                                    |

| Offset Error Tempco <sup>2</sup>          |          | -1               |          | μV/°C     | Standard deviation = $6 \mu V/^{\circ}C$                                                                       |

| Gain Error                                | -0.25    |                  | +0.25    | % FSR     | MEASOUTx gain = 1                                                                                              |

|                                           | -0.5     |                  | +0.5     | % FSR     | MEASOUTx gain = 0.2                                                                                            |

| Gain Error Tempco <sup>2</sup>            |          | 1                |          | ppm/°C    | Standard deviation = 4 ppm/°C                                                                                  |

| Linearity Error (MEASOUTx Gain = 1)       | -0.01    |                  | +0.01    | % FSR     |                                                                                                                |

| Linearity Error (MEASOUTx Gain $=$ 0.2)   | -0.01    |                  | +0.01    | % FSR     | AVDD = 15.25 V, AVSS = -15.25 V, offset DAC = 0xA492                                                           |

| •                                         | -0.06    |                  | +0.06    | % FSR     | AVDD = 28 V, AVSS = -5 V, offset DAC = 0x0                                                                     |

|                                           | -0.1     |                  | +0.1     | % FSR     | AVDD = -10 V, $AVSS = -23 V$ , offset $DAC = 0x3640$                                                           |

| Noise Spectral Density (NSD) <sup>2</sup> |          | 100              |          | nV/√Hz    | 1 kHz; measure voltage amplifier only, inputs grounded                                                         |

| OFFSET DAC                                |          |                  |          |           |                                                                                                                |

| Span Error                                |          | ±30              |          | mV        |                                                                                                                |

| COMPARATOR                                |          |                  |          |           |                                                                                                                |

| Comparator Span                           |          | 22.5             |          | V         |                                                                                                                |

| Offset Error                              | -2       | +1               | +2       | mV        | Measured directly at comparator; does not include measure block errors                                         |

| Offset Error Tempco <sup>2</sup>          |          | 1                |          | μV/°C     | Standard deviation = $2 \mu V/^{\circ}C$                                                                       |

| Propagation Delay <sup>2</sup>            |          | 0.25             |          | μs        |                                                                                                                |

| VOLTAGE CLAMPS                            |          |                  |          |           |                                                                                                                |

| Clamp Span                                |          | 22.5             |          | V         |                                                                                                                |

| Positive Clamp Accuracy                   |          |                  | 155      | mV        |                                                                                                                |

| Negative Clamp Accuracy                   | -155     |                  |          | mV        |                                                                                                                |

| CLL to CLH <sup>2</sup>                   | 500      |                  |          | mV        | CLL < CLH and minimum voltage apart                                                                            |

| Recovery Time <sup>2</sup>                |          | 0.5              | 1.5      | μs        |                                                                                                                |

| Activation Time <sup>2</sup>              | 1        | 1.5              | 3        | μs        |                                                                                                                |

# AD5522

| Parameter                                           | Min                       | Typ <sup>1</sup> | Мах                            | Unit                    | Test Conditions/Comments                                                                                                                              |

|-----------------------------------------------------|---------------------------|------------------|--------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| CURRENT CLAMPS                                      |                           |                  |                                |                         |                                                                                                                                                       |

| Clamp Accuracy                                      | Programmed                |                  | Programmed                     | % FSC                   | MI gain = 10, clamp current scales with selected                                                                                                      |

|                                                     | clamp value               |                  | clamp value $\pm$ 10           |                         | range                                                                                                                                                 |

|                                                     | Programmed<br>clamp value |                  | Programmed<br>clamp value ± 20 | % FSC                   | MI gain = 5, clamp current scales with selected range                                                                                                 |

| CLL to CLH <sup>2</sup>                             | 5                         |                  |                                | % of I <sub>RANGE</sub> | CLL < CLH and minimum setting apart, MI gain = 10                                                                                                     |

|                                                     | 10                        |                  |                                | % of $I_{\text{RANGE}}$ | CLL < CLH and minimum setting apart, MI gain = 5                                                                                                      |

| Recovery Time <sup>2</sup>                          |                           | 0.5              | 1.5                            | μs                      |                                                                                                                                                       |

| Activation Time <sup>2</sup>                        |                           | 1.5              | 3                              | μs                      |                                                                                                                                                       |

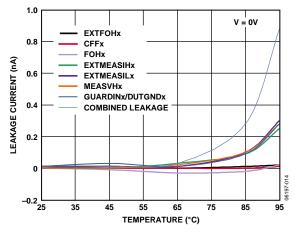

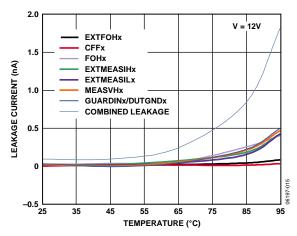

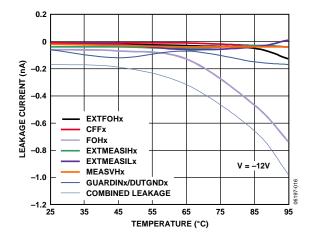

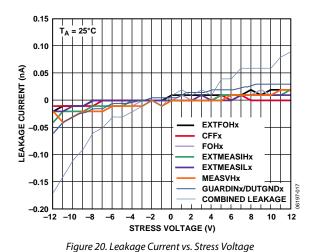

| FOHx, EXTFOHx, EXTMEASILx,<br>EXTMEASIHx, CFFx PINS |                           |                  |                                |                         |                                                                                                                                                       |

| Pin Capacitance <sup>2</sup>                        |                           | 10               |                                | pF                      |                                                                                                                                                       |

| Leakage Current                                     | -3                        |                  | +3                             | nA                      | Individual pin on or off switch leakage, measured with $\pm 11$ V stress applied to pin, channel enabled, but tristate                                |

| Leakage Current Tempco <sup>2</sup>                 |                           | ±0.01            |                                | nA/°C                   |                                                                                                                                                       |

| MEASVHx PIN                                         |                           |                  |                                |                         |                                                                                                                                                       |

| Pin Capacitance <sup>2</sup>                        |                           | 3                |                                | pF                      |                                                                                                                                                       |

| Leakage Current                                     | -3                        |                  | +3                             | nA                      | Measured with $\pm 11$ V stress applied to pin, channel enabled, but tristate                                                                         |

| Leakage Current Tempco <sup>2</sup>                 |                           | ±0.01            |                                | nA/°C                   |                                                                                                                                                       |

| SYS_SENSE PIN                                       |                           |                  |                                |                         | SYS_SENSE connected, force amplifier inhibited                                                                                                        |

| Pin Capacitance <sup>2</sup>                        |                           | 3                |                                | pF                      |                                                                                                                                                       |

| Switch Impedance                                    |                           | 1                | 1.3                            | kΩ                      |                                                                                                                                                       |

| Leakage Current                                     | -3                        |                  | +3                             | nA                      | Measured with $\pm 11$ V stress applied to pin, switch off                                                                                            |

| Leakage Current Tempco <sup>2</sup>                 |                           | ±0.01            |                                | nA/°C                   |                                                                                                                                                       |

| SYS_FORCE PIN                                       |                           |                  |                                |                         | SYS_FORCE connected, force amplifier inhibited                                                                                                        |

| Pin Capacitance <sup>2</sup>                        |                           | 6                |                                | pF                      |                                                                                                                                                       |

| Switch Impedance                                    |                           | 60               | 80                             | Ω                       |                                                                                                                                                       |

| Leakage Current                                     | -3                        |                  | +3                             | nA                      | Measured with $\pm 11$ V stress applied to pin, switch off                                                                                            |

| Leakage Current Tempco <sup>2</sup>                 |                           | ±0.01            |                                | nA/°C                   |                                                                                                                                                       |

| COMBINED LEAKAGE AT DUT                             |                           |                  |                                |                         | Includes FOHx, MEASVHx, SYS_SENSE, SYS_FORCE,<br>EXTMEASILx, EXTMEASIHx, EXTFOHx, and CFFx,<br>calculation of all the individual leakage contributors |

| Leakage Current                                     | -15                       |                  | +15                            | nA                      | $T_J = 25^{\circ}C$ to $70^{\circ}C$                                                                                                                  |

|                                                     | -25                       |                  | +25                            | nA                      | $T_1 = 25^{\circ}$ C to 90°C                                                                                                                          |

| Leakage Current Tempco <sup>2</sup>                 | 25                        | ±0.1             | 125                            | nA/°C                   |                                                                                                                                                       |

| DUTGNDx PIN                                         |                           | ±0.1             |                                | inv c                   |                                                                                                                                                       |

| Voltage Range                                       | -500                      |                  | +500                           | mV                      |                                                                                                                                                       |

| Leakage Current                                     | -30                       |                  | +30                            | nA                      |                                                                                                                                                       |

| MEASOUTX PIN                                        | 50                        |                  | 150                            |                         | With respect to AGND                                                                                                                                  |

| Output Voltage Span                                 |                           | 22.5             |                                | v                       | Software programmable output range                                                                                                                    |

| Output Impedance                                    |                           | 60               | 80                             | Ω                       |                                                                                                                                                       |

| Output Leakage Current                              | -3                        |                  | +3                             | nA                      | With SW12 off                                                                                                                                         |

| Output Capacitance <sup>2</sup>                     | -                         |                  | 15                             | pF                      |                                                                                                                                                       |

| Maximum Load Capacitance <sup>2</sup>               |                           |                  | 0.5                            | μF                      |                                                                                                                                                       |

| Output Current Drive <sup>2</sup>                   |                           | 2                |                                | mA                      |                                                                                                                                                       |

| Short-Circuit Current                               | -10                       |                  | +10                            | mA                      |                                                                                                                                                       |

| Slew Rate <sup>2</sup>                              |                           | 2                |                                | V/µs                    |                                                                                                                                                       |

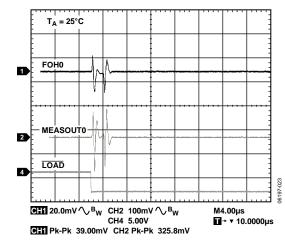

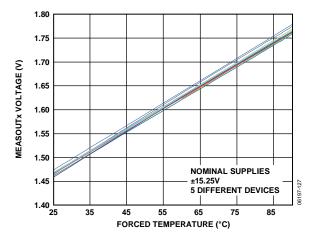

| Enable Time <sup>2</sup>                            |                           | 150              | 320                            | ns                      | Closing SW12, measured from BUSY rising edge                                                                                                          |

| Disable Time <sup>2</sup>                           |                           | 400              | 1100                           | ns                      | Opening SW12, measured from BUSY rising edge                                                                                                          |

| MI to MV Switching Time <sup>2</sup>                |                           | 200              |                                | ns                      | Measured from BUSY rising edge, does not include                                                                                                      |

| An to My Switching fille                            |                           | 200              |                                | 115                     | slewing or settling                                                                                                                                   |

| Parameter                                                        | Min | Typ1         | Max       | Unit         | Test Conditions/Comments                                                                                                                             |

|------------------------------------------------------------------|-----|--------------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| GUARDx PIN                                                       |     |              |           |              |                                                                                                                                                      |

| Output Voltage Span                                              |     | 22.5         |           | V            |                                                                                                                                                      |

| Output Offset                                                    | -10 |              | +10       | mV           |                                                                                                                                                      |

| Short-Circuit Current                                            | -15 |              | +15       | mA           |                                                                                                                                                      |

| Maximum Load Capacitance <sup>2</sup>                            | 15  |              | 100       | nF           |                                                                                                                                                      |

| Output Impedance                                                 |     | 85           | 100       | Ω            |                                                                                                                                                      |

| Tristate Leakage Current <sup>2</sup>                            | -30 | 05           | +30       | nA           | When guard amplifier is disabled                                                                                                                     |

| Slew Rate <sup>2</sup>                                           | -30 | F            | +30       |              | <b>e</b> .                                                                                                                                           |

|                                                                  |     | 5            |           | V/µs         | $C_{LOAD} = 10 \text{ pF}$                                                                                                                           |

| Alarm Activation Time <sup>2</sup>                               |     | 200          |           | μs           | Alarm delayed to eliminate false alarms                                                                                                              |

| FORCE AMPLIFIER <sup>2</sup>                                     |     |              |           |              |                                                                                                                                                      |

| Slew Rate                                                        |     | 0.4          |           | V/µs         | $CCOMPx = 100 \text{ pF}, CFFx = 220 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                          |

| Gain Bandwidth                                                   |     | 1.3          |           | MHz          | CCOMPx = 100 pF, CFFx = 220 pF, C <sub>LOAD</sub> = 200 pF                                                                                           |

| Max Stable Load Capacitance                                      |     |              | 10,000    | pF           | $\label{eq:CCOMP} CCOMPx = 100 \text{ pF, larger } C_{\text{LOAD}} \text{ requires larger } CCOMP \\ \text{capacitor}$                               |

|                                                                  |     |              | 100       | nF           | $CCOMPx = 1 \text{ nF}$ , larger $C_{LOAD}$ requires larger $CCOMP$ capacitor                                                                        |

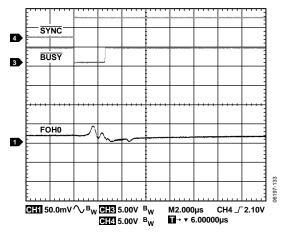

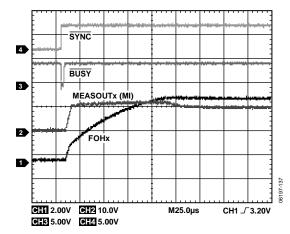

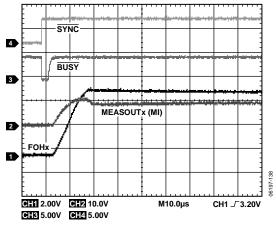

| FV SETTLING TIME TO 0.05% OF FS <sup>2</sup>                     |     |              |           |              | Midscale to full-scale change; measured from SYNC                                                                                                    |

| +90 m A Banga                                                    |     | 22           | 40        |              | rising edge, clamps on $CCOMPx = 100 \text{ pc}$                                                                                                     |

| ±80 mA Range                                                     |     | 22           | 40        | μs           | CCOMPx = 100 pF, CFFx = 220 pF, C <sub>LOAD</sub> = 200 pF                                                                                           |

| ±2 mA Range                                                      |     | 24           | 40        | μs           | $CCOMPx = 100 \text{ pF}, CFFx = 220 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                          |

| ±200 μA Range                                                    |     | 40           | 80        | μs           | CCOMPx = 100 pF, CFFx = 220 pF, C <sub>LOAD</sub> = 200 pF                                                                                           |

| ±20 μA Range                                                     |     | 300          |           | μs           | $CCOMPx = 100 \text{ pF}, CFFx = 220 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                          |

| ±5 μA Range                                                      |     | 1400         |           | μs           | CCOMPx = 100 pF, CFFx = 220 pF, C <sub>LOAD</sub> = 200 pF                                                                                           |

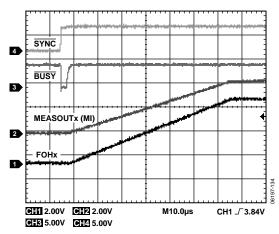

| MI SETTLING TIME TO 0.05% OF FS <sup>2</sup>                     |     |              |           |              | Midscale to full-scale change; driven from force<br>amplifier in FV mode, so includes FV settling time,<br>measured from SYNC rising edge, clamps on |

| ±80 mA Range                                                     |     | 22           | 40        | μs           | CCOMPx = 100 pF, CFFx = 220 pF, C <sub>LOAD</sub> = 200 pF                                                                                           |

| ±2 mA Range                                                      |     | 24           | 40        | -            | $CCOMPx = 100 \text{ pF}, CFFx = 220 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                          |

| 5                                                                |     |              | 40<br>100 | μs           | CCOMPx = 100  pF, CFFx = 220  pF, CLOAD = 200  pF<br>CCOMPx = 100  pF, CFFx = 220  pF, CLOAD = 200  pF                                               |

| ±200 μA Range                                                    |     | 60           | 100       | μs           |                                                                                                                                                      |

| ±20 μA Range                                                     |     | 462          |           | μs           | $CCOMPx = 100 \text{ pF}, CFFx = 220 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                          |

| ±5 μA Range                                                      |     | 1902         |           | μs           | CCOMPx = 100 pF, CFFx = 220 pF, C <sub>LOAD</sub> = 200 pF                                                                                           |

| FI SETTLING TIME TO 0.05% OF FS <sup>2</sup>                     |     |              |           |              | Midscale to full-scale change; measured from SYNC rising edge, clamps on                                                                             |

| ±80 mA Range                                                     |     | 24           | 55        | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| ±2 mA Range                                                      |     | 24           | 60        | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| ±200 μA Range                                                    |     | 50           | 120       | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| ±20 μA Range                                                     |     | 450          |           | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| ±5 μA Range                                                      |     | 2700         |           | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

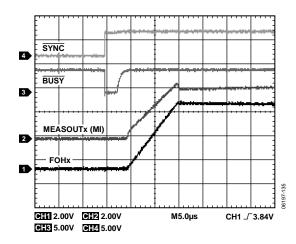

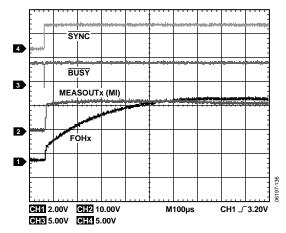

| MV SETTLING TIME TO 0.05% OF FS <sup>2</sup>                     |     |              |           |              | Midscale to full-scale change; driven from force<br>amplifier in FV mode, so includes FV settling time,<br>measured from SYNC rising edge, clamps on |

| ±80 mA Range                                                     |     | 24           | 55        | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| ±2 mA Range                                                      |     | 24           | 60        | μς           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| $\pm 200 \mu\text{A}$ Range                                      |     | 50           | 120       | μς           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| $\pm 200 \mu$ A Range                                            |     | 450          | 120       | μs           | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| · -                                                              |     | 2700         |           | -            | $CCOMPx = 100 \text{ pF}, C_{LOAD} = 200 \text{ pF}$                                                                                                 |

| ±5 μA Range                                                      |     | 2700         |           | μs           | CCOWFX = 100 pr, CLOAD = 200 pr                                                                                                                      |

| DAC SPECIFICATIONS                                               |     |              | 16        | D.1          |                                                                                                                                                      |

| Resolution                                                       |     | <b>a</b> c - | 16        | Bits         |                                                                                                                                                      |

| Output Voltage Span <sup>2</sup>                                 |     | 22.5         |           | V            | VREF = 5 V, within a range of $-16.25$ V to $+22.5$ V                                                                                                |

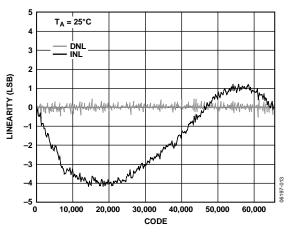

| Differential Nonlinearity <sup>2</sup>                           | -1  |              | +1        | LSB          | Guaranteed monotonic by design over temperature                                                                                                      |

| SPECIFICATIONS <sup>2</sup><br>Output Voltage Settling Time      |     | 1            |           | μs           | 500 mV change to $\pm \frac{1}{2}$ LSB                                                                                                               |

| Slew Rate                                                        |     | 5.5          |           | μs<br>V/μs   |                                                                                                                                                      |

|                                                                  |     |              |           |              |                                                                                                                                                      |

| Digital-to-Analog Glitch Energy<br>Glitch Impulse Peak Amplitude |     | 20<br>10     |           | nV-sec<br>mV |                                                                                                                                                      |

| REFERENCE INPUT                                                  |     |              |           |              |                                                                                                                                                      |

| VREF DC Input Impedance                                          | 1   | 100          |           | MΩ           |                                                                                                                                                      |

| VREF Input Current                                               | -10 | +0.03        | +10       | μΑ           |                                                                                                                                                      |

| VREF Range <sup>2</sup>                                          | 2   |              | 5         | V            |                                                                                                                                                      |

# AD5522

| Parameter                                                      | Min        | Typ <sup>1</sup> | Max     | Unit  | Test Conditions/Comments                                                                                                                                                                 |

|----------------------------------------------------------------|------------|------------------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIE TEMPERATURE SENSOR                                         |            |                  |         |       |                                                                                                                                                                                          |

| Accuracy <sup>2</sup>                                          |            | ±7               |         | °C    |                                                                                                                                                                                          |

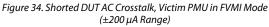

| Output Voltage at 25°C                                         |            | 1.5              |         | V     |                                                                                                                                                                                          |

| Output Voltage at 25 C                                         |            | 4.6              |         | mV/°C |                                                                                                                                                                                          |

| Output Voltage Range <sup>2</sup>                              | 0          | 4.0              | 3       | V     |                                                                                                                                                                                          |

|                                                                | 0          |                  | 5       | v     |                                                                                                                                                                                          |

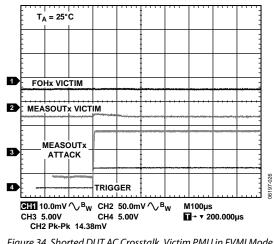

| INTERACTION AND CROSSTALK <sup>2</sup>                         |            |                  |         |       |                                                                                                                                                                                          |

| DC Crosstalk (FOHx)                                            |            | 0.05             | 0.65    | mV    | DC change resulting from a dc change in any DAC in<br>the device, FV and FI modes, $\pm 2$ mA range, C <sub>LOAD</sub> = 200 pF<br>R <sub>LOAD</sub> = 5.6 k $\Omega$                    |

| DC Crosstalk (MEASOUTx)                                        |            | 0.05             | 0.65    | mV    | DC change resulting from a dc change in any DAC in<br>the device, MV and MI modes, $\pm 2$ mA range,<br>$C_{LOAD} = 200$ pF, $R_{LOAD} = 5.6$ k $\Omega$                                 |

| DC Crosstalk Within a Channel                                  |            | 0.05             |         | mV    | All channels in FVMI mode, one channel at midscale,<br>measure the current for one channel in the lowest<br>current range for a change in comparator or clamp<br>DAC levels for that PMU |

| SPI INTERFACE LOGIC INPUTS                                     |            |                  |         |       |                                                                                                                                                                                          |

| Input High Voltage, V <sub>IH</sub>                            | 1.7/2.0    |                  |         | V     | (2.3 V to 2.7 V)/(2.7 V to 5.25 V), JEDEC-compliant input levels                                                                                                                         |

| Input Low Voltage, $V_{IL}$                                    |            |                  | 0.7/0.8 | V     | (2.3 V to 2.7 V)/(2.7 V to 5.25 V), JEDEC-compliant input levels                                                                                                                         |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub>             | -1         |                  | +1      | μΑ    |                                                                                                                                                                                          |

| Input Capacitance, C <sub>IN<sup>2</sup></sub>                 |            |                  | 10      | pF    |                                                                                                                                                                                          |

| CMOS LOGIC OUTPUTS                                             |            |                  |         |       | SDO, CPOx                                                                                                                                                                                |

| Output High Voltage, V <sub>он</sub>                           | DVCC – 0.4 |                  |         | v     |                                                                                                                                                                                          |

| Output Low Voltage, $V_{OL}$                                   | 5100 011   |                  | 0.4     | v     | I <sub>OL</sub> = 500 μA                                                                                                                                                                 |

| Tristate Leakage Current                                       | -2         |                  | +2      | μA    | SDO, CPOH1/SDO                                                                                                                                                                           |

| Instate Leakage Current                                        |            |                  |         |       |                                                                                                                                                                                          |

|                                                                | -1         |                  | +1      | μA    | All other output pins                                                                                                                                                                    |

| Output Capacitance <sup>2</sup>                                |            |                  | 10      | pF    |                                                                                                                                                                                          |

| OPEN-DRAIN LOGIC OUTPUTS                                       |            |                  |         |       | BUSY, TMPALM, CGALM                                                                                                                                                                      |

| Output Low Voltage, Vol                                        |            |                  | 0.4     | V     | $I_{\text{OL}} = 500 \ \mu\text{A}, \ C_{\text{LOAD}} = 50 \ p\text{F}, \ R_{\text{PULLUP}} = 1 \ k\Omega$                                                                               |

| Output Capacitance <sup>2</sup>                                |            |                  | 10      | pF    |                                                                                                                                                                                          |

| LVDS INTERFACE LOGIC INPUTS<br>REDUCED RANGE LINK <sup>2</sup> |            |                  |         |       |                                                                                                                                                                                          |

| Input Voltage Range                                            | 875        |                  | 1575    | mV    |                                                                                                                                                                                          |

| Input Differential Threshold                                   | -100       |                  | +100    | mV    |                                                                                                                                                                                          |

| External Termination Resistance                                | 80         | 100              | 120     | Ω     |                                                                                                                                                                                          |

| Differential Input Voltage                                     | 100        |                  |         | mV    |                                                                                                                                                                                          |

| LVDS INTERFACE LOGIC OUTPUTS<br>REDUCED RANGE LINK             |            |                  |         |       |                                                                                                                                                                                          |

| Output Offset Voltage                                          |            | 1200             |         | mV    |                                                                                                                                                                                          |

| Output Differential Voltage                                    |            | 400              |         | mV    |                                                                                                                                                                                          |

| POWER SUPPLIES                                                 |            | 400              |         | 1110  |                                                                                                                                                                                          |

|                                                                | 10         |                  | 20      |       |                                                                                                                                                                                          |

| AVDD                                                           | 10         |                  | 28      | V     | $ AVDD - AVSS  \le 33 V$                                                                                                                                                                 |

| AVSS                                                           | -23        |                  | -5      | V     |                                                                                                                                                                                          |

| DVCC                                                           | 2.3        |                  | 5.25    | V     |                                                                                                                                                                                          |

| Aldd                                                           |            |                  | 26      | mA    | Internal ranges ( $\pm 5 \ \mu A$ to $\pm 2 \ mA$ ), excluding load conditions; comparators and guard disabled                                                                           |

| Alss                                                           | -26        |                  |         | mA    | Internal ranges ( $\pm 5 \ \mu$ A to $\pm 2 \ m$ A), excluding load conditions; comparators and guard disabled                                                                           |

| Ald                                                            |            |                  | 28      | mA    | Internal ranges ( $\pm$ 5 $\mu$ A to $\pm$ 2 mA), excluding load conditions; comparators and guard enabled                                                                               |

| Alss                                                           | -28        |                  |         | mA    | Internal ranges ( $\pm$ 5 µA to $\pm$ 2 mA), excluding load conditions; comparators and guard enabled                                                                                    |

| Ald                                                            |            |                  | 36      | mA    | External range, excluding load conditions                                                                                                                                                |

| Alss                                                           | -36        |                  |         | mA    | External range, excluding load conditions                                                                                                                                                |

| DIcc                                                           |            |                  | 1.5     | mA    |                                                                                                                                                                                          |

| Maximum Power Dissipation <sup>2</sup>                         |            |                  | 7       | W     | Maximum power that should be dissipated in this<br>package under worst-case load conditions; careful<br>consideration should be given to supply selection<br>and thermal design          |

AD5522

| Parameter                             | Min Typ <sup>1</sup> | Max | Unit | Test Conditions/Comments |

|---------------------------------------|----------------------|-----|------|--------------------------|

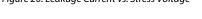

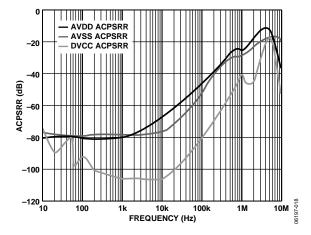

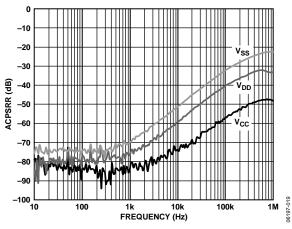

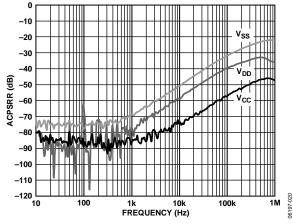

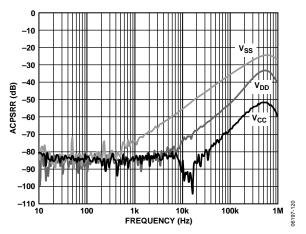

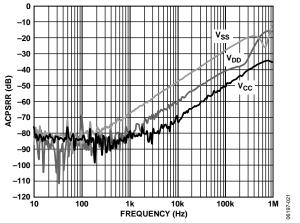

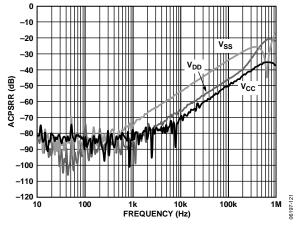

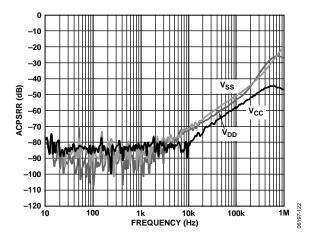

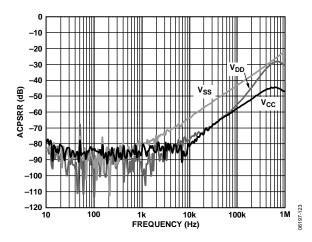

| Power Supply Sensitivity <sup>2</sup> |                      |     |      | From dc to 1 kHz         |

| ΔForced Voltage/ΔAVDD                 | -80                  |     | dB   |                          |

| ΔForced Voltage/ΔAVSS                 | -80                  |     | dB   |                          |

| ΔMeasured Current/ΔAVDD               | -85                  |     | dB   |                          |

| ΔMeasured Current/ΔAVSS               | -75                  |     | dB   |                          |

| ΔForced Current/ΔAVDD                 | -75                  |     | dB   |                          |

| ΔForced Current/ΔAVSS                 | -75                  |     | dB   |                          |

| ΔMeasured Voltage/ΔAVDD               | -85                  |     | dB   |                          |

| ΔMeasured Voltage/ΔAVSS               | -80                  |     | dB   |                          |

| ∆Forced Voltage/∆DVCC                 | -90                  |     | dB   |                          |

| ΔMeasured Current/ΔDVCC               | -90                  |     | dB   |                          |

| ΔForced Current/ΔDVCC                 | -90                  |     | dB   |                          |

| ΔMeasured Voltage/ΔDVCC               | -90                  |     | dB   |                          |

<sup>1</sup> Typical specifications are at 25°C and nominal supply, ±15.25 V, unless otherwise noted. <sup>2</sup> Guaranteed by design and characterization; not production tested. Tempco values are mean and standard deviation, unless otherwise noted.

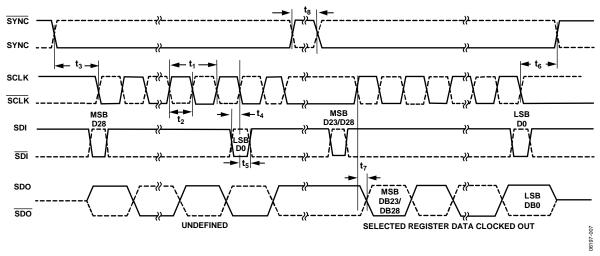

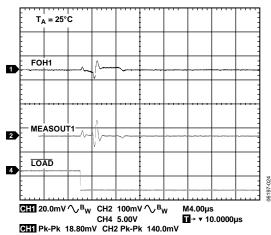

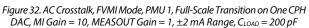

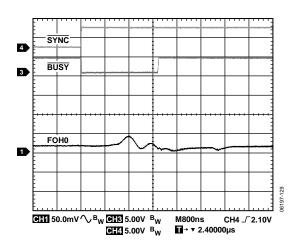

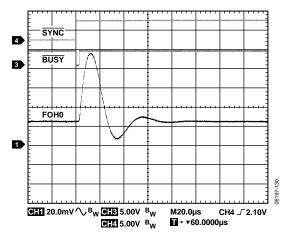

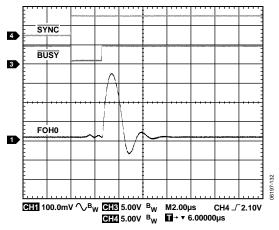

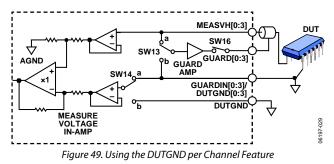

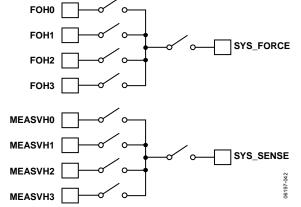

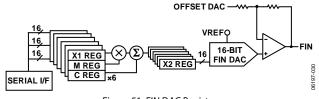

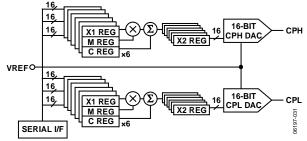

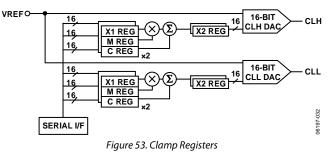

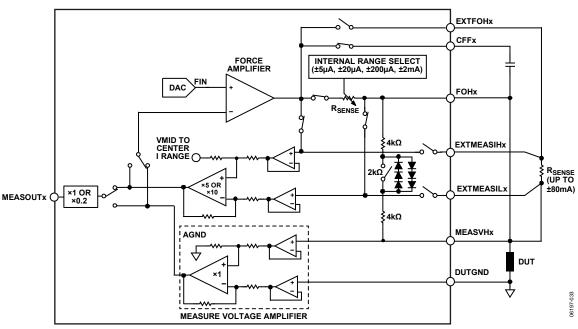

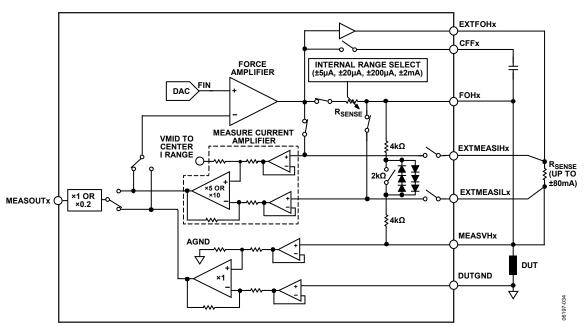

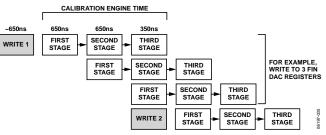

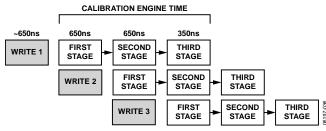

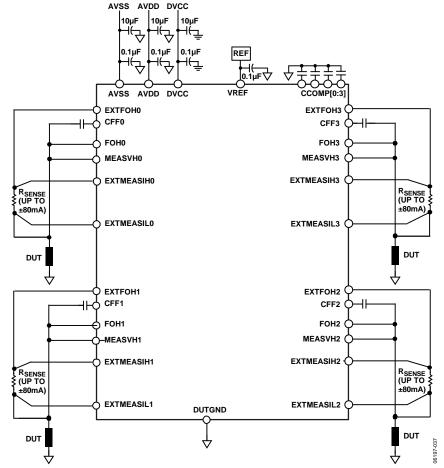

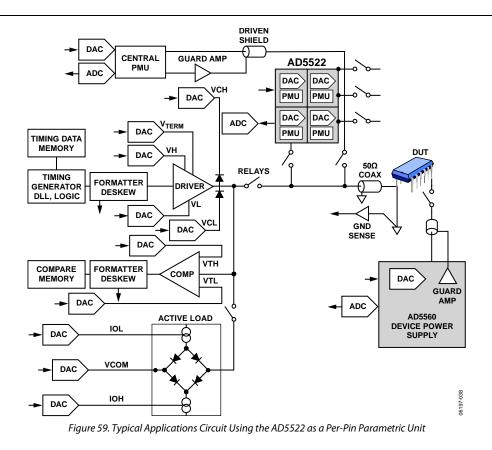

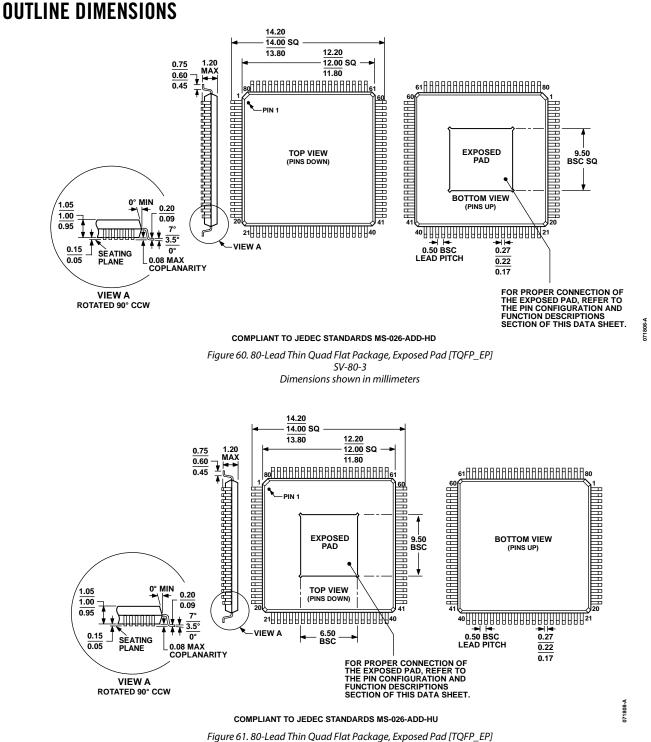

## **TIMING CHARACTERISTICS**