### Contents

| Con | tents     |                                      |   |

|-----|-----------|--------------------------------------|---|

| 1   | Device b  | ock diagram                          | 5 |

| 2   | Pin desc  | ription                              | 6 |

|     | 2.1       | Pinout                               | 6 |

|     | 2.2       | Pin list                             | 7 |

| 3   | Electrica | specifications                       | 8 |

|     | 3.1       | Absolute maximum ratings             | 8 |

|     | 3.2       | Thermal data                         | 8 |

|     | 3.3       | Recommended operating conditions     | 8 |

|     | 3.4       | Electrical specifications            | 9 |

| 4   | Characte  | rization curves1 <sup>·</sup>        | 1 |

|     | 4.1       | PCB layout1                          | 1 |

|     | 4.2       | Characterization curves1             | 2 |

|     |           | 4.2.1 For $R_L = 6 \Omega$           |   |

|     |           | 4.2.2 For $R_L = 8 \Omega$           |   |

| 5   | Applicati | on information10                     | 6 |

|     | 5.1       | Application circuit1                 | 6 |

|     | 5.2       | Mode selection1                      | 7 |

|     | 5.3       | Gain setting1                        |   |

|     | 5.4       | Input resistance and capacitance1    | 9 |

|     | 5.5       | Internal and external clocks2        |   |

|     |           | 5.5.1 Master mode (internal clock)   |   |

|     | 5.0       | 5.5.2 Slave mode (external clock)    |   |

|     | 5.6       | Output low-pass filter               |   |

|     | 5.7       | Protection functions                 |   |

| •   | 5.8       | Diagnostic output                    |   |

| 6   | •         | information23                        |   |

|     | 6.1       | PowerSSO-36 EPU package information2 |   |

| 7   | Revision  | history20                            | 6 |

# List of tables

| Table 1: Device summary                           | 1  |

|---------------------------------------------------|----|

| Table 2: Pin description list                     |    |

| Table 3: Absolute maximum ratings                 | 8  |

| Table 4: Thermal data                             |    |

| Table 5: Recommended operating conditions         | 8  |

| Table 6: Electrical specifications                | 9  |

| Table 7: Mode settings                            | 17 |

| Table 8: Gain settings                            |    |

| Table 9: How to set up SYNCLK                     | 20 |

| Table 10: PowerSSO-36 EPU package mechanical data | 25 |

| Table 11: Document revision history               | 26 |

# List of figures

| Figure 1: Internal block diagram (showing one channel only)       | 5  |

|-------------------------------------------------------------------|----|

| Figure 2: Pin connections (top view, PCB view)                    | 6  |

| Figure 3: Test board                                              | 11 |

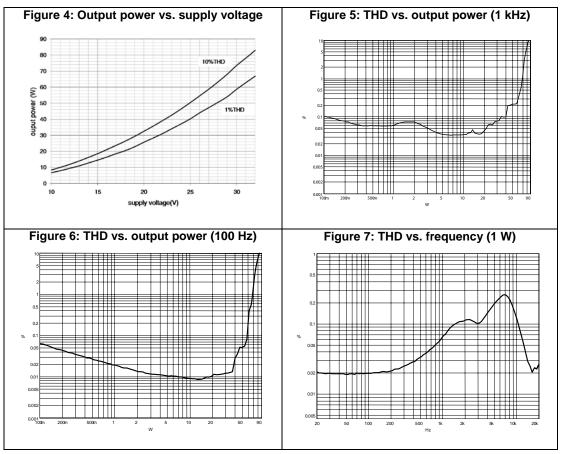

| Figure 4: Output power vs. supply voltage                         | 12 |

| Figure 5: THD vs. output power (1 kHz)                            | 12 |

| Figure 6: THD vs. output power (100 Hz)                           | 12 |

| Figure 7: THD vs. frequency (1 W)                                 | 12 |

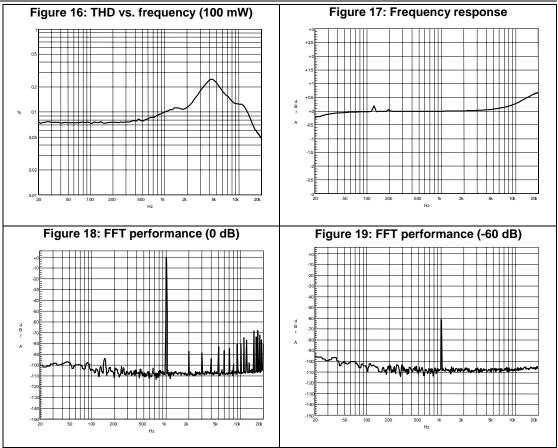

| Figure 8: THD vs. frequency (100 mW)                              |    |

| Figure 9: Frequency response                                      | 13 |

| Figure 10: FFT performance (0 dBFS)                               | 13 |

| Figure 11: FFT performance (-60 dBFS)                             | 13 |

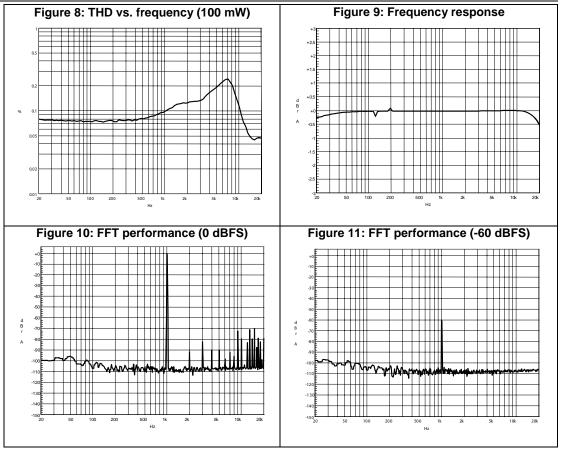

| Figure 12: Output power vs. supply voltage                        | 14 |

| Figure 13: THD vs. output power (1 kHz)                           | 14 |

| Figure 14: THD vs. output power (100 Hz)                          | 14 |

| Figure 15: THD vs. frequency (1 W)                                | 14 |

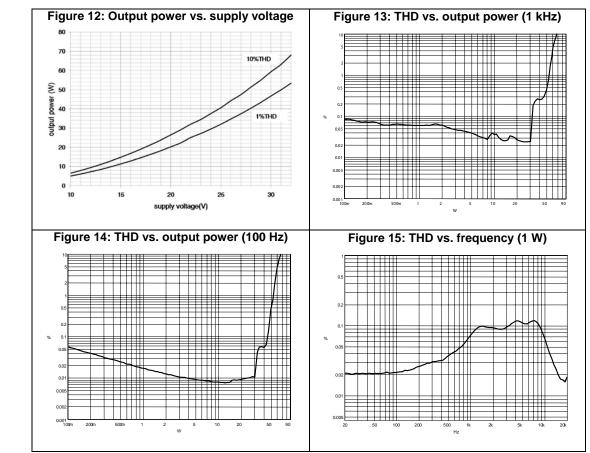

| Figure 16: THD vs. frequency (100 mW)                             | 15 |

| Figure 17: Frequency response                                     |    |

| Figure 18: FFT performance (0 dB)                                 | 15 |

| Figure 19: FFT performance (-60 dB)                               | 15 |

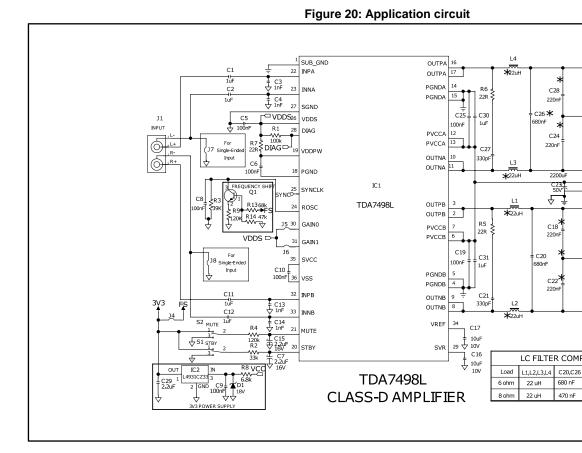

| Figure 20: Application circuit                                    | 16 |

| Figure 21: Standby and mute circuits                              | 17 |

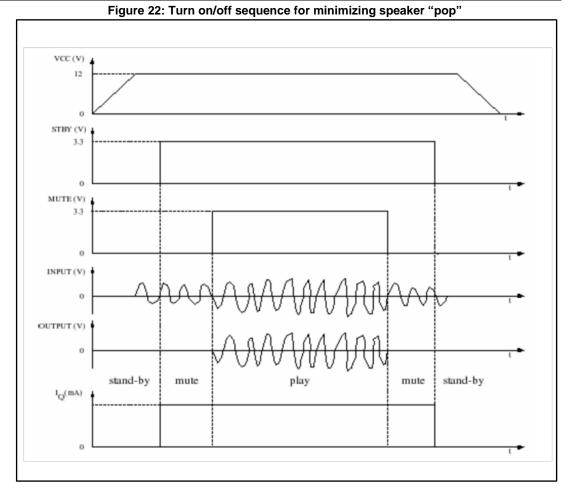

| Figure 22: Turn on/off sequence for minimizing speaker "pop"      |    |

| Figure 23: Input circuit and frequency response                   |    |

| Figure 24: Master and slave connection                            |    |

| Figure 25: Typical LC filter for an 8 $\Omega$ speaker            |    |

| Figure 26: Typical LC filter for a 6 $\Omega$ speaker             |    |

| Figure 27: Behavior of pin DIAG for various protection conditions |    |

| Figure 28: PowerSSO-36 EPU package outline                        | 24 |

# 1 Device block diagram

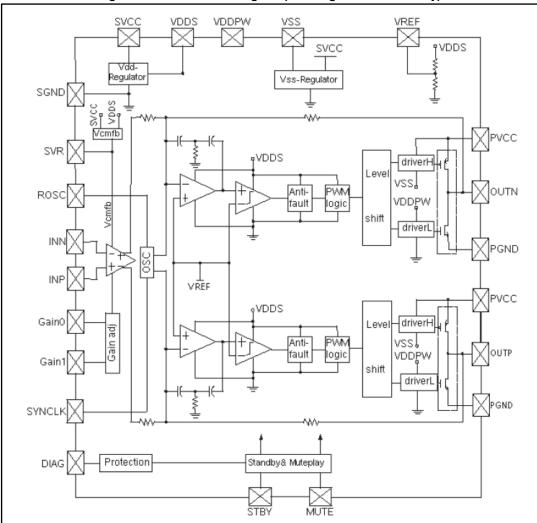

*Figure 1: "Internal block diagram (showing one channel only)"* shows the block diagram of one of the two identical channels of the TDA7498L.

# 2 Pin description

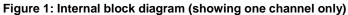

### 2.1 Pinout

# 2.2 Pin list

|        |         | Tak  | ble 2: Pin description list                                           |  |

|--------|---------|------|-----------------------------------------------------------------------|--|

| Number | Name    | Туре | Description                                                           |  |

| 1      | SUB_GND | PWR  | Connect to the frame                                                  |  |

| 2,3    | OUTPB   | 0    | Positive PWM for right channel                                        |  |

| 4,5    | PGNDB   | PWR  | Power stage ground for right channel                                  |  |

| 6,7    | PVCCB   | PWR  | Power supply for right channel                                        |  |

| 8,9    | OUTNB   | 0    | Negative PWM output for right channel                                 |  |

| 10,11  | OUTNA   | 0    | Negative PWM output for left channel                                  |  |

| 12,13  | PVCCA   | PWR  | Power supply for left channel                                         |  |

| 14,15  | PGNDA   | PWR  | Power stage ground for left channel                                   |  |

| 16,17  | OUTPA   | 0    | Positive PWM output for left channel                                  |  |

| 18     | PGND    | PWR  | Power stage ground                                                    |  |

| 19     | VDDPW   | 0    | 3.3-V (nominal) regulator output referred to ground for power stage   |  |

| 20     | STBY    | I    | Standby mode control                                                  |  |

| 21     | MUTE    | I    | Mute mode control                                                     |  |

| 22     | INPA    | I    | Positive differential input of left channel                           |  |

| 23     | INNA    | 1    | Negative differential input of left channel                           |  |

| 24     | ROSC    | 0    | Master oscillator frequency-setting pin                               |  |

| 25     | SYNCLK  | I/O  | Clock in/out for external oscillator                                  |  |

| 26     | VDDS    | 0    | 3.3-V (nominal) regulator output referred to ground for signal blocks |  |

| 27     | SGND    | PWR  | Signal ground                                                         |  |

| 28     | DIAG    | 0    | Open-drain diagnostic output                                          |  |

| 29     | SVR     | 0    | Supply voltage rejection                                              |  |

| 30     | GAIN0   | 1    | Gain setting input 1                                                  |  |

| 31     | GAIN1   | I    | Gain setting input 2                                                  |  |

| 32     | INPB    | 1    | Positive differential input of right channel                          |  |

| 33     | INNB    | I    | Negative differential input of right channel                          |  |

| 34     | VREF    | 0    | Half VDDS (nominal) referred to ground                                |  |

| 35     | SVCC    | PWR  | Signal power supply decoupling                                        |  |

|        |         |      | 3.3-V (nominal) regulator output referred to power supply             |  |

| 36     | VSS     | 0    | 3.3-V (nominal) regulator output referred to power supply             |  |

Table 2: Pin description list

# 3 Electrical specifications

### 3.1 Absolute maximum ratings

| Table | 3: | Absolute | maximum | ratings |

|-------|----|----------|---------|---------|

| Table | э. | Absolute | maximum | raunys  |

| \$ | Symbol              | Parameter                                                                                     | Value      | Unit |  |

|----|---------------------|-----------------------------------------------------------------------------------------------|------------|------|--|

| ١  | V <sub>CC_MAX</sub> | DC supply voltage for pins PVCCA, PVCCB, SVCC                                                 | 45         | V    |  |

|    | $V_{L_{MAX}}$       | Voltage limits for input pins STBY, MUTE, INNA, INPA,<br>INNB, INPB, GAIN0, GAIN1 -0.3 to 3.6 |            |      |  |

|    | T <sub>j_MAX</sub>  | Operating junction temperature                                                                | 0 to 150   | °C   |  |

|    | T <sub>stg</sub>    | Storage temperature                                                                           | -40 to 150 | °C   |  |

Warning: Stresses beyond those listed under "Absolute maximum ratings" make cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended operating condition" are not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. In the real application, the power supply with the nominal value rated in the recommended operating condition for a short time when no or very low current is sunk (amplifier in mute state). In this case the reliability of the device is guaranteed, provided that the absolute maximum rating is not exceeded.

## 3.2 Thermal data

| Table | ۸۰ | Thermal | data |

|-------|----|---------|------|

| Iable | ÷. | THEIMai | uala |

| Symbol                 | Parameter                            |  | Тур | Max | Unit |

|------------------------|--------------------------------------|--|-----|-----|------|

| R <sub>th j-case</sub> | Thermal resistance, junction to case |  | 2   | 3   | °C/W |

## 3.3 Recommended operating conditions

Table 5: Recommended operating conditions

| Symbol          | Symbol Parameter                     |     | Тур | Max | Unit |

|-----------------|--------------------------------------|-----|-----|-----|------|

| V <sub>cc</sub> | Supply voltage for pins PVCCA, PVCCB | 14  | -   | 36  | V    |

| Tamb            | Ambient operating temperature        | -20 | -   | 85  | °C   |

# 3.4 Electrical specifications

Unless otherwise stated, the values in the table below are specified for the conditions:  $V_{CC} = 32 \text{ V}, \text{ R}_L = 6 \Omega, \text{ R}_{OSC} = \text{R3} = 39 \text{ k}\Omega, \text{ C8} = 100 \text{ nF}, \text{ f} = 1 \text{ kHz}, \text{ G}_V = 25.6 \text{ dB}$ Tamb = 25 °C.

| Symbol                          | Parameter                                | Condition                                                                                                                                         | Min  | Тур  | Мах  | Unit |

|---------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| lq                              | Total quiescent current                  | No LC filter, no load                                                                                                                             | -    | 40   | 60   | mA   |

| I <sub>qSTBY</sub>              | Quiescent current in standby             | -                                                                                                                                                 | -    | 1    | 10   | μA   |

| M                               |                                          | Play mode                                                                                                                                         | -100 | -    | 100  | m)/  |

| V <sub>OS</sub>                 | Output offset voltage                    | Mute mode                                                                                                                                         | -60  | -    | 60   | mV   |

| I <sub>OCP</sub>                | Overcurrent protection threshold         | R <sub>L</sub> = 0 Ω                                                                                                                              | 5.0  | 6.0  | -    | А    |

| T <sub>jS</sub>                 | Junction temperature at thermal shutdown | -                                                                                                                                                 | -    | 150  | -    | °C   |

| Ri                              | Input resistance                         | Differential input                                                                                                                                | 48   | 60   | -    | kΩ   |

| V <sub>OVP</sub>                | Overvoltage protection threshold         | -                                                                                                                                                 | 42   | 43   | -    | V    |

| V <sub>UVP</sub>                | Undervoltage protection threshold        | -                                                                                                                                                 | -    | -    | 8    | V    |

| D                               | Power transistor on-resistance           | High side                                                                                                                                         | -    | 0.2  | -    | Ω    |

| $R_{dsON}$                      | Fower transistor on-resistance           | Low side                                                                                                                                          | -    | 0.2  | -    | Ω    |

| Po                              |                                          | THD = 10%                                                                                                                                         | -    | 80   | -    | w    |

| F <sub>0</sub>                  | Output power                             | THD = 1%                                                                                                                                          | -    | 65   | -    |      |

| Po                              | Output power                             | $R_L$ = 8 Ω, THD = 10%,<br>V <sub>CC</sub> = 32 V                                                                                                 | -    | 65   | -    | W    |

| PD                              | Dissipated power                         | P <sub>o</sub> = 80 W + 80 W,<br>THD = 10%                                                                                                        | -    | 16   | -    | W    |

| η                               | Efficiency                               | $P_{o} = 80 W + 80 W$                                                                                                                             | -    | 90   | -    | %    |

| THD                             | Total harmonic distortion                | P <sub>o</sub> = 1 W                                                                                                                              | -    | 0.1  | -    | %    |

|                                 |                                          | GAIN0 = L, GAIN1 = L                                                                                                                              | 24.6 | 25.6 | 26.6 |      |

| 0                               | Classed loop goin                        | GAIN0 = L, GAIN1 = H                                                                                                                              | 30.6 | 31.6 | 32.6 | ٩D   |

| Gv                              | Closed-loop gain                         | GAIN0 = H, GAIN1 = L                                                                                                                              | 34.1 | 35.1 | 36.1 | dB   |

|                                 |                                          | GAIN0 = H, GAIN1 = H                                                                                                                              | 36.6 | 37.6 | 38.6 |      |

| $\Delta G_{\rm V}$              | Gain matching                            | -                                                                                                                                                 | -1   | -    | 1    | dB   |

| CT                              | Crosstalk                                | $f = 1 \text{ kHz}, P_0 = 1 \text{ W}$                                                                                                            | 50   | 70   | -    | dB   |

| oN                              | Total input paiga                        | A Curve, $G_V = 20 \text{ dB}$                                                                                                                    | -    | 15   | -    |      |

| eN                              | Total input noise                        | f = 22 Hz to 22 kHz                                                                                                                               | -    | 25   | 50   | μV   |

| SVRR                            | Supply voltage rejection ratio           | $\label{eq:rescaled} \begin{array}{l} \mbox{fr} = 100 \mbox{ Hz}, \mbox{ Vr} = 0.5 \mbox{ Vpp}, \\ \mbox{C}_{SVR} = 10  \mu \mbox{F} \end{array}$ | -    | 70   | -    | dB   |

| T <sub>r</sub> , T <sub>f</sub> | Rise and fall times                      | -                                                                                                                                                 | -    | 50   | -    | ns   |

| f <sub>SW</sub>                 | Switching frequency                      | Internal oscillator                                                                                                                               | 290  | 310  | 330  | kHz  |

| f                               | Output switching frequency               | With internal oscillator <sup>(1)</sup>                                                                                                           | 250  | -    | 400  | kHz  |

| f <sub>SWR</sub>                | range                                    | With external oscillator <sup>(2)</sup>                                                                                                           | 250  | -    | 400  | NIIZ |

**Table 6: Electrical specifications**

#### Electrical specifications

#### TDA7498L

| Symbol            | Parameter                 | Condition                 | Min | Тур | Max | Unit |

|-------------------|---------------------------|---------------------------|-----|-----|-----|------|

| VinH              | Digital input high (H)    |                           | 2.3 | -   | -   | V    |

| VinL              | Digital input low (L)     | -                         | -   | -   | 0.8 | v    |

| N                 | Pin STBY voltage high (H) |                           | 2.7 | -   | -   | N    |

| V <sub>STBY</sub> | Pin STBY voltage low (L)  | ] -                       | -   | -   | 0.5 | V    |

| N                 | Pin MUTE voltage high (H) |                           | 2.5 | -   | -   |      |

| V <sub>MUTE</sub> | Pin MUTE voltage low (L)  | ] -                       | -   | -   | 0.8 | V    |

| A <sub>MUTE</sub> | Mute attenuation          | V <sub>MUTE</sub> < 0.8 V | -   | 70  | -   | dB   |

#### Notes:

$^{(1)}f_{SW}$  = 10<sup>6</sup> / ((16 \* R<sub>OSC</sub> + 182) \* 4) kHz,  $f_{SYNCLK}$  = 2 \*  $f_{SW}$  with R3 = 39 k $\Omega$  (see Figure 20: "Application circuit").

$^{(2)}f_{SW}$  =  $f_{SYNCLK}$  / 2 with the external oscillator.

# 4 Characterization curves

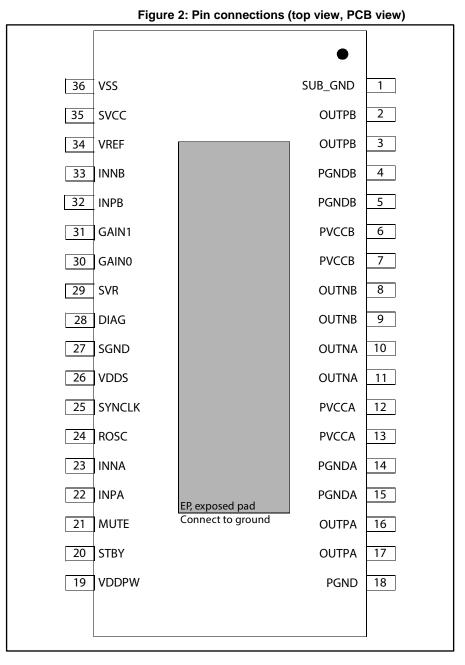

*Figure 20: "Application circuit"* shows the test circuit with which the characterization curves, shown in the next sections, were measured. *Figure 3: "Test board"* below shows the PCB layout.

# 4.1 PCB layout

DocID16504 Rev 4

57

### 4.2 Characterization curves

Unless otherwise stated the measurements were made under the following conditions:  $V_{CC} = 32 \text{ V}, \text{ f} = 1 \text{ kHz}, \text{ G}_{V} = 25.6 \text{ dB}, \text{ R}_{OSC} = 39 \text{ k}\Omega, \text{ C}_{OSC} = 100 \text{ nF}, \text{ Tamb} = 25 \text{ °C}$

### 4.2.1 For $R_L = 6 \Omega$

12/27

#### **Characterization curves**

### 4.2.2 For $R_L = 8 \Omega$

14/27

**Characterization curves**

**Application information**

# 5 Application information

# 5.1 Application circuit

### 5.2 Mode selection

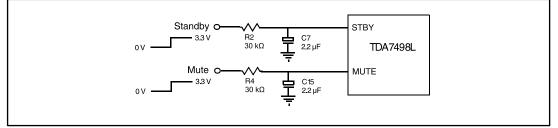

The three operating modes of the TDA7498L are set by the two inputs, STBY (pin 20) and MUTE (pin 21).

- Standby mode: all circuits are turned off, very low current consumption.

- Mute mode: inputs are connected to ground and the positive and negative PWM outputs are at 50% duty cycle.

- Play mode: the amplifiers are active.

The protection functions of the TDA7498L are enabled by pulling down the voltages of the STBY and MUTE inputs shown in *Figure 21: "Standby and mute circuits"*. The input current of the corresponding pins must be limited to 200  $\mu$ A.

| Mode    | STBY                             | MUTE |  |  |

|---------|----------------------------------|------|--|--|

| Standby | dby L <sup>(1)</sup> X (don't ca |      |  |  |

| Mute    | H <sup>(1)</sup>                 | L    |  |  |

| Play    | Н                                | Н    |  |  |

#### Table 7: Mode settings

#### Notes:

<sup>(1)</sup>Drive levels defined in *Table 6: "Electrical specifications "*

#### Figure 21: Standby and mute circuits

#### Application information

# 5.3 Gain setting

The gain of the TDA7498L is set by the two inputs, GAIN0 (pin 30) and GAIN1 (pin31). Internally, the gain is set by changing the feedback resistors of the amplifier.

| GAIN0 | GAIN1 | Nominal gain, $G_v$ (dB) |  |

|-------|-------|--------------------------|--|

| L     | L     | 25.6                     |  |

| L     | Н     | 31.6                     |  |

| Н     | L     | 35.6                     |  |

| Н     | Н     | 37.6                     |  |

Table 8: Gain settings

## 5.4 Input resistance and capacitance

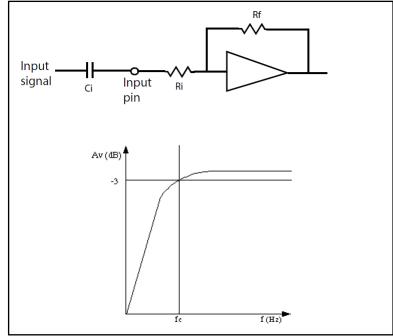

The input impedance is set by an internal resistor  $Ri = 60 k\Omega$  (typical). An input capacitor (Ci) is required to couple the AC input signal.

The equivalent circuit and frequency response of the input components are shown in *Figure 23: "Input circuit and frequency response"*. For Ci = 470 nF the high-pass filter cutoff frequency is below 20 Hz:

$f_{C} = 1 / (2 * \pi * Ri * Ci)$

### 5.5 Internal and external clocks

The clock of the class-D amplifier can be generated internally or can be driven by an external source.

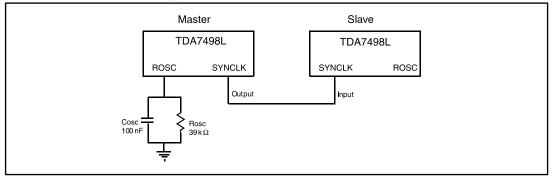

If two or more class-D amplifiers are used in the same system, it is recommended that all devices operate at the same clock frequency. This can be implemented by using one TDA7498L as master clock, while the other devices are in slave mode, that is, externally clocked. The clock interconnect is via pin SYNCLK of each device. As explained below, SYNCLK is an output in master mode and an input in slave mode.

#### 5.5.1 Master mode (internal clock)

Using the internal oscillator, the output switching frequency,  $f_{SW}$ , is controlled by the resistor,  $R_{OSC}$ , connected to pin ROSC:

$f_{SW} = 10^6 / [(R_{OSC} * 16 + 182) * 4] \text{ kHz}$

where  $R_{OSC}$  is in k $\Omega$ .

In master mode, pin SYNCLK is used as a clock output pin whose frequency is:

$f_{\text{SYNCLK}} = 2 * f_{\text{SW}}$

For master mode to operate correctly then resistor  $R_{OSC}$  must be less than 60 k $\Omega$  as given below in *Table 9: "How to set up SYNCLK"*.

#### 5.5.2 Slave mode (external clock)

In order to accept an external clock input the pin ROSC must be left open, that is, floating. This forces pin SYNCLK to be internally configured as an input as given in *Table 9: "How to set up SYNCLK"*.

The output switching frequency of the slave devices is:

$f_{SW} = f_{SYNCLK} / 2$

#### Table 9: How to set up SYNCLK

| Mode   | ROSC                     | SYNCLK |  |  |  |

|--------|--------------------------|--------|--|--|--|

| Master | R <sub>osc</sub> < 60 kΩ | Output |  |  |  |

| Slave  | Floating (not connected) | Input  |  |  |  |

#### Figure 24: Master and slave connection

## 5.6 Output low-pass filter

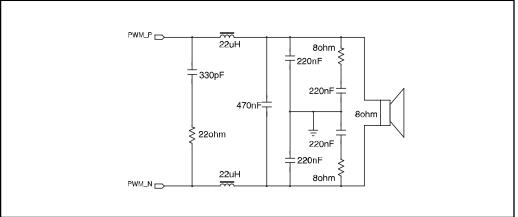

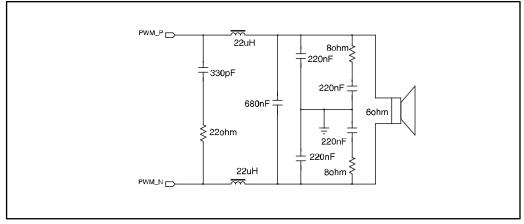

To avoid EMI problems, it may be necessary to use a low-pass filter before the speaker. The cutoff frequency should be larger than 22 kHz and much lower than the output switching frequency. It is necessary to choose the L and C component values depending on the loudspeaker impedance. Some typical values, which give a cutoff frequency of 27 kHz, are shown in *Figure 25: "Typical LC filter for an 8 \Omega speaker"* and *Figure 26: "Typical LC filter for a 6 \Omega speaker"* below.

Figure 25: Typical LC filter for an 8  $\Omega$  speaker

### 5.7 **Protection functions**

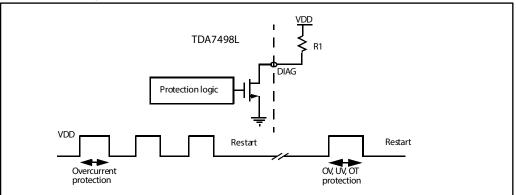

The TDA7498L is fully protected against overvoltages, undervoltages, overcurrents and thermal overloads as explained here.

#### **Overvoltage protection (OVP)**

If the supply voltage exceeds the value for  $V_{OVP}$  given in *Table 6: "Electrical specifications*", the overvoltage protection is activated which forces the outputs to the high-impedance state. When the supply voltage falls back to within the operating range, the device restarts.

#### **Undervoltage protection (UVP)**

If the supply voltage drops below the value for  $V_{UVP}$  given in *Table 6: "Electrical specifications*", the undervoltage protection is activated which forces the outputs to the high-impedance state. When the supply voltage falls back to within the operating range, the device restarts.

#### **Overcurrent protection (OCP)**

If the output current exceeds the value for  $I_{OCP}$  given in *Table 6: "Electrical specifications"*, the overcurrent protection is activated which forces the outputs to the high-impedance state. Periodically, the device attempts to restart. If the overcurrent condition is still present then the OCP remains active. The restart time,  $T_{OC}$ , is determined by the RC components connected to pin STBY.

#### Thermal protection (OTP)

If the junction temperature,  $T_j$ , reaches 145 °C (nominally), the device goes to mute mode and the positive and negative PWM outputs are forced to 50% duty cycle. If the junction temperature reaches the value for  $T_j$  given in *Table 6: "Electrical specifications "*, the device shuts down and the output is forced to the high-impedance state. When the device cools sufficiently, the device restarts.

### 5.8 Diagnostic output

The output pin DIAG is an open drain transistor. When any protection is activated it switches to the high-impedance state. The pin can be connected to a power supply (< 36 V) by a pull-up resistor whose value is limited by the maximum sinking current (200  $\mu$ A) of the pin.

22/27

DocID16504 Rev 4

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

### 6.1 PowerSSO-36 EPU package information

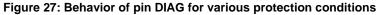

The device comes in a 36-pin PowerSSO package with exposed pad up (EPU).

*Figure 28: "PowerSSO-36 EPU package outline"* shows the package outline and *Table 10: "PowerSSO-36 EPU package mechanical data"* gives the dimensions.

| Package informati<br>Table 10: PowerSSO-36 EPU package mechanical data |                  |      |            |                      |       |            |

|------------------------------------------------------------------------|------------------|------|------------|----------------------|-------|------------|

| Symbol                                                                 | Dimensions in mm |      |            | Dimensions in inches |       |            |

|                                                                        | Min.             | Тур. | Max.       | Min.                 | Тур.  | Max.       |

| А                                                                      | 2.15             | -    | 2.45       | 0.085                | -     | 0.096      |

| A2                                                                     | 2.15             | -    | 2.35       | 0.085                | -     | 0.093      |

| a1                                                                     | 0                | -    | 0.10       | 0                    | -     | 0.004      |

| b                                                                      | 0.18             | -    | 0.36       | 0.007                | -     | 0.014      |

| С                                                                      | 0.23             | -    | 0.32       | 0.009                | -     | 0.013      |

| D                                                                      | 10.10            | -    | 10.50      | 0.398                | -     | 0.413      |

| E                                                                      | 7.40             | -    | 7.60       | 0.291                | -     | 0.299      |

| е                                                                      | -                | 0.5  | -          | -                    | 0.020 | -          |

| e3                                                                     | -                | 8.5  | -          | -                    | 0.335 | -          |

| F                                                                      | -                | 2.3  | -          | -                    | 0.091 | -          |

| G                                                                      | -                | -    | 0.10       | -                    | -     | 0.004      |

| Н                                                                      | 10.10            | -    | 10.50      | 0.398                | -     | 0.413      |

| h                                                                      | -                | -    | 0.40       | -                    | -     | 0.016      |

| k                                                                      | 0                | -    | 8 degrees  | 0                    | -     | 8 degrees  |

| L                                                                      | 0.55             | -    | 0.85       | 0.022                | -     | 0.033      |

| М                                                                      | -                | 4.30 | -          | -                    | 0.169 | -          |

| Ν                                                                      | -                | -    | 10 degrees | -                    | -     | 10 degrees |

| 0                                                                      | -                | 1.20 | -          | -                    | 0.047 | -          |

| Q                                                                      | -                | 0.80 | -          | -                    | 0.031 | -          |

| S                                                                      | -                | 2.90 | -          | -                    | 0.114 | -          |

| Т                                                                      | -                | 3.65 | -          | -                    | 0.144 | -          |

| U                                                                      | -                | 1.00 | -          | -                    | 0.039 | -          |

| Х                                                                      | 4.10             | -    | 4.70       | 0.161                | -     | 0.185      |

| Y                                                                      | 4.90             | -    | 7.10       | 0.193                | -     | 0.280      |

# 7 Revision history

Table 11: Document revision history

\_\_\_\_\_

| Date        | Revision | Changes                                                                                                                                                 |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 04-Dec-2009 | 1        | Initial release.                                                                                                                                        |  |

| 02-Jul-2010 | 2        | Removed datasheet preliminary status, updated Section "Features" list and Table 1: "Device summary"                                                     |  |

|             |          | Updated minimum supply voltage and temperature range in <i>Table 5:</i> " <i>Recommended operating conditions</i> "                                     |  |

|             |          | Updated typical power output for 8 $\Omega$ to 32 V in Table 6: "Electrical specifications "                                                            |  |

| 12-Sep-2011 | 3        | Updated OUTNA in <i>Table 2: "Pin description list"</i> ; minor textual updates                                                                         |  |

| 09-Sep-2015 | 4        | Updated V <sub>CC_MAX</sub> in <i>Table 3: "Absolute maximum ratings"</i> and dimension L in <i>Table 10: "PowerSSO-36 EPU package mechanical data"</i> |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved