### 1.3 Device comparison

Table 1 summarizes the functions of the blocks present on the MPC5606BK.

Table 1. MPC5606BK family comparison<sup>1</sup>

| Feature                                       |                  | MPC5605BK |             |                  | MPC5606BK |             |

|-----------------------------------------------|------------------|-----------|-------------|------------------|-----------|-------------|

| Package                                       | 100 LQFP         | 144 LQFP  | 176 LQFP    | 100 LQFP         | 144 LQFP  | 176 LQFP    |

| CPU                                           |                  | l         | e200        | Oz0h             | l         |             |

| Execution speed <sup>2</sup>                  |                  |           | Up to 6     | 64 MHz           |           |             |

| Code flash memory                             |                  | 768 KB    |             |                  | 1 MB      |             |

| Data flash memory                             |                  |           | 64 (4 x     | 16) KB           |           |             |

| SRAM                                          |                  | 64 KB     |             |                  | 80 KB     |             |

| MPU                                           |                  |           | 8-e         | ntry             |           |             |

| eDMA                                          |                  |           | 16          | ch               |           |             |

| 10-bit ADC                                    |                  |           | Y           | es               |           |             |

| dedicated <sup>3</sup>                        | 7 ch             | 15 ch     | 29 ch       | 7 ch             | 15 ch     | 29 ch       |

| shared with 12-bit ADC                        |                  | •         | 19          | ch               | •         |             |

| 12-bit ADC                                    |                  |           | Y           | es               |           |             |

| dedicated <sup>4</sup>                        |                  |           | 5           | ch               |           |             |

| shared with 10-bit ADC                        |                  |           | 19          | ch               |           |             |

| Total timer I/O <sup>5</sup> eMIOS            | 37 ch,<br>16-bit | 64<br>16  | ch,<br>-bit | 37 ch,<br>16-bit | 64<br>16  | ch,<br>-bit |

| Counter / OPWM / ICOC <sup>6</sup>            |                  | l         | 10          | ch               | l         |             |

| O(I)PWM / OPWFMB / OPWMCB / ICOC <sup>7</sup> |                  |           | 7           | ch               |           |             |

| O(I)PWM / ICOC <sup>8</sup>                   | 7 ch             |           |             | 14 ch            |           |             |

| OPWM / ICOC <sup>9</sup>                      | 13 ch            |           |             | 33 ch            |           |             |

| SCI (LINFlex)                                 | 4                | 6         | 8           | 4                | 6         | 8           |

| SPI (DSPI)                                    | 3                | 5         | 6           | 3                | 5         | 6           |

| CAN (FlexCAN)                                 |                  | •         | (           | 6                | •         |             |

| I <sup>2</sup> C                              |                  |           | ,           | 1                |           |             |

| 32 KHz oscillator                             |                  |           | Y           | es               |           |             |

| GPIO <sup>10</sup>                            | 77               | 121       | 149         | 77               | 121       | 149         |

| Debug                                         |                  |           | JT.         | AG               |           |             |

|                                               |                  |           |             |                  |           |             |

<sup>1</sup> Feature set dependent on selected peripheral multiplexing; table shows example.

#### MPC5606BK Microcontroller Data Sheet, Rev. 4

<sup>&</sup>lt;sup>2</sup> Based on 125 °C ambient operating temperature.

<sup>&</sup>lt;sup>3</sup> Not shared with 12-bit ADC, but possibly shared with other alternate functions.

<sup>&</sup>lt;sup>4</sup> Not shared with 10-bit ADC, but possibly shared with other alternate functions.

<sup>&</sup>lt;sup>5</sup> Refer to eMIOS section of device reference manual for information on the channel configuration and functions.

<sup>&</sup>lt;sup>6</sup> Each channel supports a range of modes including Modulus counters, PWM generation, Input Capture, Output Compare.

<sup>&</sup>lt;sup>7</sup> Each channel supports a range of modes including PWM generation with dead time, Input Capture, Output Compare.

Each channel supports a range of modes including PWM generation, Input Capture, Output Compare, Period and Pulse width measurement.

<sup>&</sup>lt;sup>9</sup> Each channel supports a range of modes including PWM generation, Input Capture, and Output Compare.

<sup>&</sup>lt;sup>10</sup> Maximum I/O count based on multiplexing with peripherals.

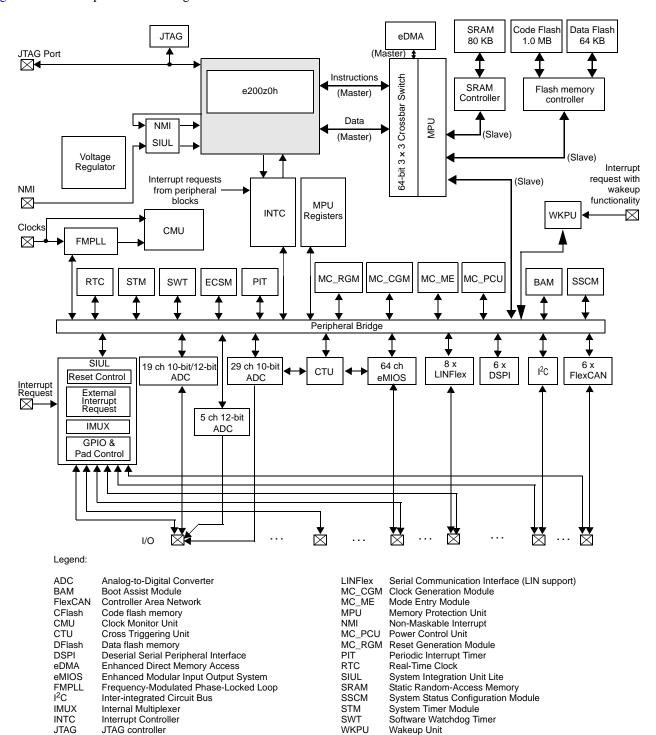

### 1.4 Block diagram

Figure 1 shows a top-level block diagram of the MPC5606BK.

Figure 1. MPC5606BK block diagram

MPC5606BK Microcontroller Data Sheet, Rev. 4

# 2 Package pinouts and signal descriptions

## 2.1 Package pinouts

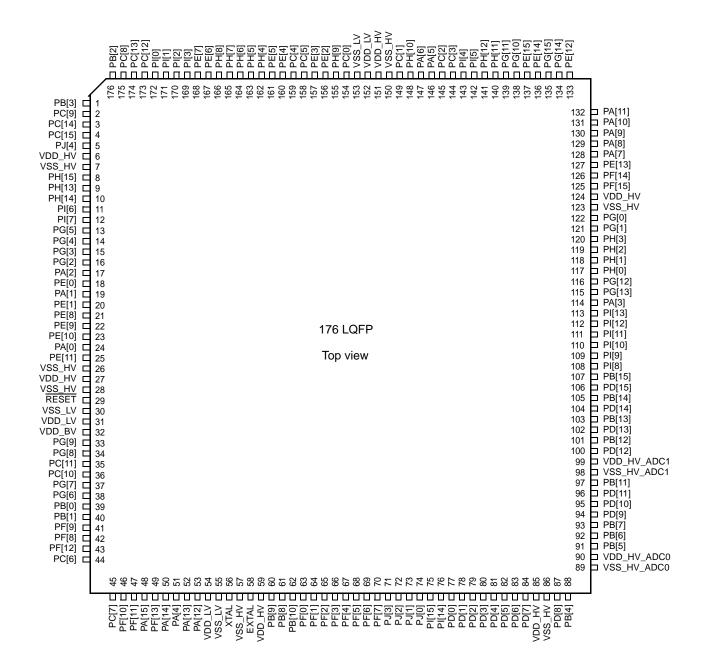

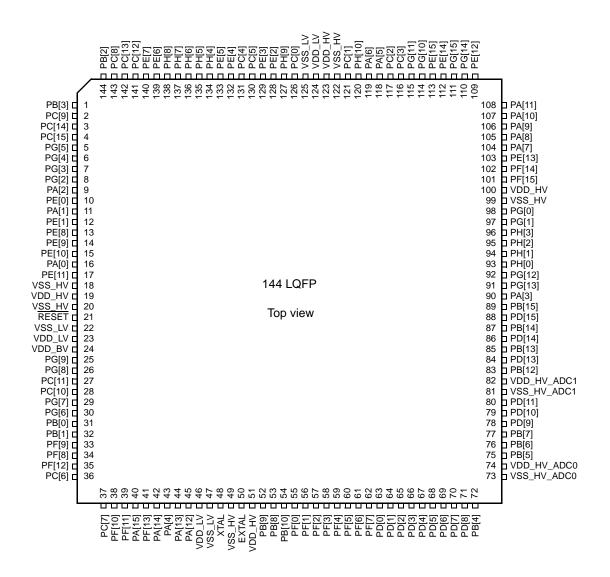

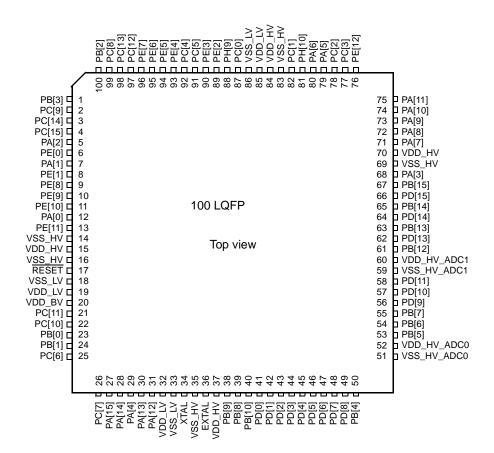

The available LQFP pinouts are provided in the following figures. For pin signal descriptions, please see Table 2.

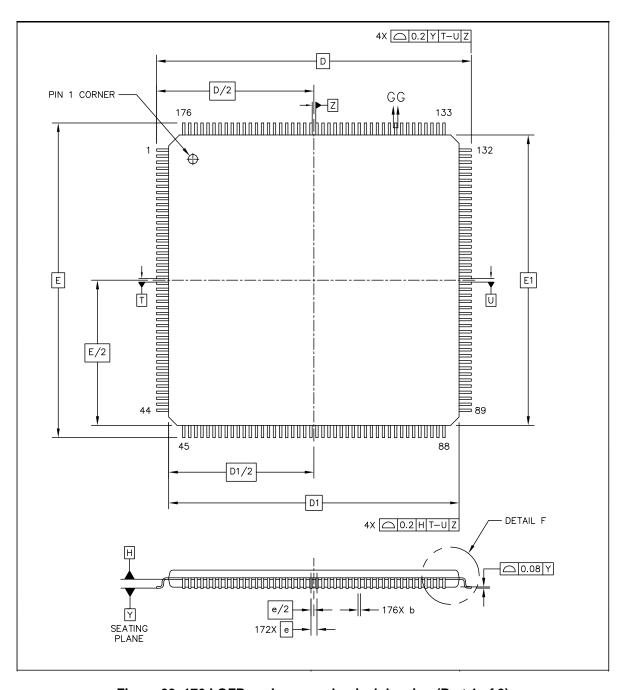

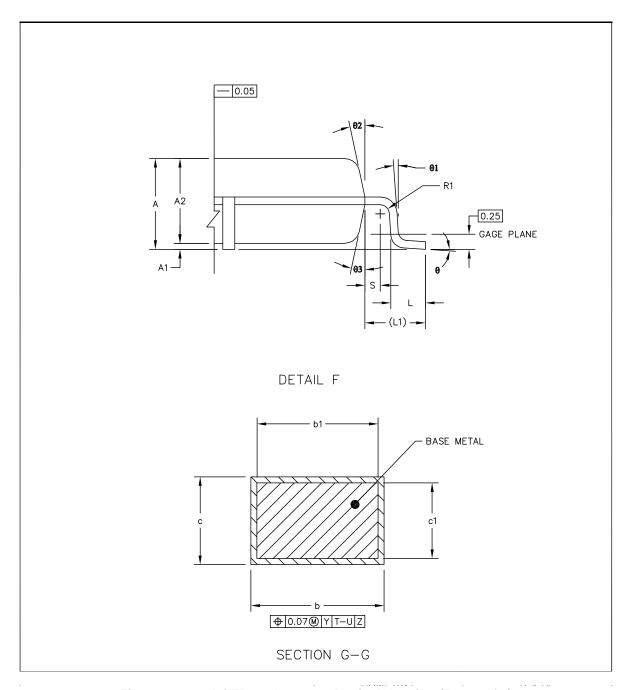

Figure 2 shows the MPC5606BK in the 176 LQFP package.

Figure 2. 176 LQFP pinout

MPC5606BK Microcontroller Data Sheet, Rev. 4

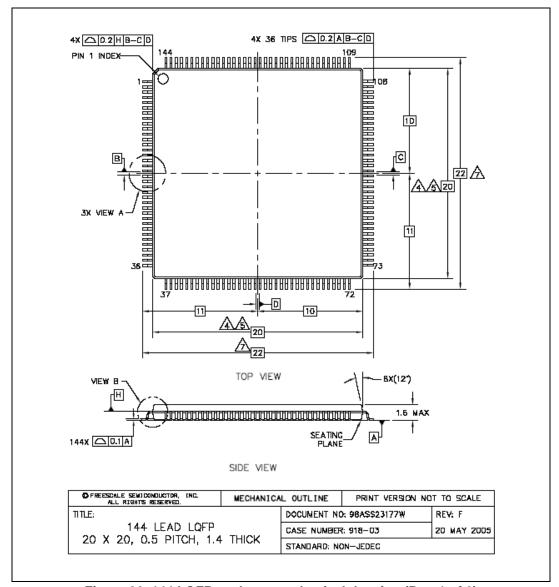

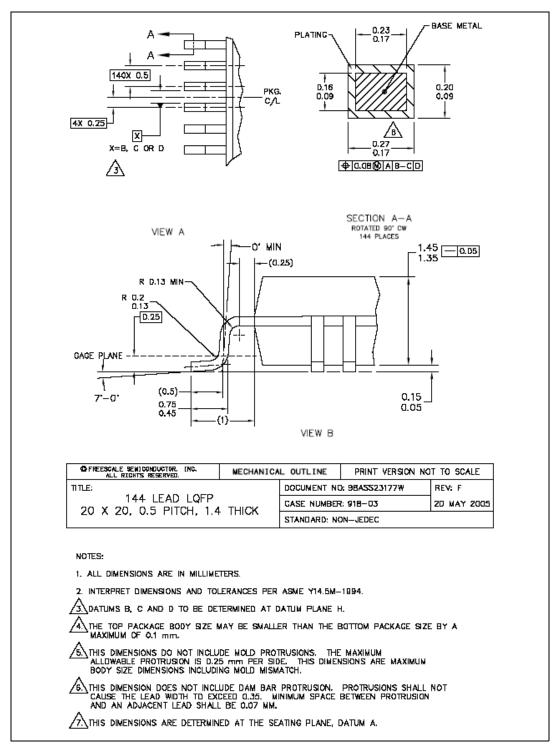

Figure 3 shows the MPC5606BK in the 144 LQFP package.

Figure 3. 144 LQFP pinout

Figure 4 shows the MPC5606BK in the 100 LQFP package.

Figure 4. 100 LQFP pinout

## 2.2 Pin muxing

Table 2 defines the pin list and muxing for this device.

Each entry of Table 2 shows all the possible configurations for each pin, via the alternate functions. The default function assigned to each pin after reset is indicated by AFO.

**Table 2. Functional port pins**

| Port  | PCR      | Alternate                     |                                                                     | eral                                                    | noi                         | pe <sup>2</sup>       | F. E.                         | Pi          | n numb      | er          |

|-------|----------|-------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-----------------------------|-----------------------|-------------------------------|-------------|-------------|-------------|

| pin   | register | function <sup>1</sup>         | Function                                                            | Peripheral                                              | I/O<br>direction            | Pad type <sup>2</sup> | RESET<br>config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

|       |          |                               |                                                                     | Port A                                                  |                             |                       |                               |             |             |             |

| PA[0] | PCR[0]   | AF0<br>AF1<br>AF2<br>AF3      | GPIO[0]<br>E0UC[0]<br>CLKOUT<br>E0UC[13]<br>WKUP[19] <sup>4</sup>   | SIUL<br>eMIOS_0<br>MC_CGM<br>eMIOS_0<br>WKUP            | I/O<br>I/O<br>O<br>I/O      | M                     | Tristate                      | 12          | 16          | 24          |

| PA[1] | PCR[1]   | AF0<br>AF1<br>AF2<br>AF3      | GPIO[1]<br>E0UC[1]<br>NMI <sup>5</sup><br>—<br>WKUP[2] <sup>4</sup> | SIUL<br>eMIOS_0<br>WKUP<br>—<br>WKUP                    | I/O<br>I/O<br>I<br>—        | S                     | Tristate                      | 7           | 11          | 19          |

| PA[2] | PCR[2]   | AF0<br>AF1<br>AF2<br>AF3      | GPIO[2]<br>E0UC[2]<br>—<br>MA[2]<br>WKUP[3] <sup>4</sup>            | SIUL<br>eMIOS_0<br>—<br>ADC_0<br>WKUP                   | I/O<br>I/O<br>—<br>O<br>I   | S                     | Tristate                      | 5           | 9           | 17          |

| PA[3] | PCR[3]   | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[3] E0UC[3] LIN5TX CS4_1 EIRQ[0] ADC1_S[0]                      | SIUL<br>eMIOS_0<br>LINFlex_5<br>DSPI_1<br>SIUL<br>ADC_1 | I/O<br>I/O<br>O<br>O        | J                     | Tristate                      | 68          | 90          | 114         |

| PA[4] | PCR[4]   | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[4]<br>E0UC[4]<br>—<br>CS0_1<br>LIN5RX<br>WKUP[9] <sup>4</sup>  | SIUL<br>eMIOS_0<br>—<br>DSPI_1<br>LINFlex_5<br>WKUP     | I/O<br>I/O<br>—<br>I/O<br>I | S                     | Tristate                      | 29          | 43          | 51          |

| PA[5] | PCR[5]   | AF0<br>AF1<br>AF2<br>AF3      | GPIO[5]<br>E0UC[5]<br>LIN4TX<br>—                                   | SIUL<br>eMIOS_0<br>LINFlex_4                            | I/O<br>I/O<br>O             | М                     | Tristate                      | 79          | 118         | 146         |

| PA[6] | PCR[6]   | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[6]<br>E0UC[6]<br>—<br>CS1_1<br>EIRQ[1]<br>LIN4RX               | SIUL<br>eMIOS_0<br>—<br>DSPI_1<br>SIUL<br>LINFlex_4     | I/O<br>I/O<br>—<br>O<br>I   | S                     | Tristate                      | 80          | 119         | 147         |

Table 2. Functional port pins (continued)

| Port    | PCR      | Alternate                                    |                                                  | eral                                                            | ion                         | pe <sup>2</sup>       | F                          | Pi          | in numb     | er          |

|---------|----------|----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|-----------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin     | register | function <sup>1</sup>                        | Function                                         | Peripheral                                                      | I/O<br>direction            | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PA[7]   | PCR[7]   | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[7]<br>E0UC[7]<br>LIN3TX                     | SIUL<br>eMIOS_0<br>LINFlex_3                                    | I/O<br>I/O<br>O             | J                     | Tristate                   | 71          | 104         | 128         |

|         |          | —<br>—                                       | EIRQ[2]<br>ADC1_S[1]                             | SIUL<br>ADC_1                                                   | <br>                        |                       |                            |             |             |             |

| PA[8]   | PCR[8]   | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[8]<br>E0UC[8]<br>E0UC[14]<br>—              | SIUL<br>eMIOS_0<br>eMIOS_0                                      | I/O<br>I/O<br>I/O           | S                     | Input,<br>weak<br>pull-up  | 72          | 105         | 129         |

|         |          | N/A <sup>6</sup>                             | EIRQ[3]<br>ABS[0]<br>LIN3RX                      | SIUL<br>BAM<br>LINFlex_3                                        | <br> <br>                   |                       |                            |             |             |             |

| PA[9]   | PCR[9]   | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>6</sup> | GPIO[9]<br>E0UC[9]<br>—<br>CS2_1<br>FAB          | SIUL<br>eMIOS_0<br>—<br>DSPI_1<br>BAM                           | I/O<br>I/O<br>—<br>O        | S                     | Pull-<br>down              | 73          | 106         | 130         |

| PA[10]  | PCR[10]  | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[10] E0UC[10] SDA LIN2TX ADC1_S[2]           | SIUL<br>eMIOS_0<br>I <sup>2</sup> C_0<br>LINFlex_2<br>ADC_1     | I/O<br>I/O<br>I/O<br>O      | J                     | Tristate                   | 74          | 107         | 131         |

| PA[11]  | PCR[11]  | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPIO[11] E0UC[11] SCL — EIRQ[16] LIN2RX          | SIUL<br>eMIOS_0<br>I <sup>2</sup> C_0<br>—<br>SIUL<br>LINFlex_2 | I/O<br>I/O<br>I/O<br>—<br>I | J                     | Tristate                   | 75          | 108         | 132         |

| PA[12]  | PCR[12]  | AF0                                          | ADC1_S[3]<br>GPIO[12]                            | ADC_1<br>SIUL                                                   | I<br>I/O                    | S                     | Tristate                   | 31          | 45          | 53          |

| .,,[,2] | . 6.(12) | AF1<br>AF2<br>AF3<br>—                       | E0UC[28]<br>CS3_1<br>EIRQ[17]<br>SIN_0           | eMIOS_0<br>DSPI_1<br>SIUL<br>DSPI_0                             |                             |                       | motato                     | 0.          |             |             |

| PA[13]  | PCR[13]  | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[13]<br>SOUT_0<br>E0UC[29]<br>—              | SIUL<br>DSPI_0<br>eMIOS_0                                       | I/O<br>O<br>I/O             | М                     | Tristate                   | 30          | 44          | 52          |

| PA[14]  | PCR[14]  | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[14]<br>SCK_0<br>CS0_0<br>E0UC[0]<br>EIRQ[4] | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>SIUL                     | I/O<br>I/O<br>I/O<br>I/O    | М                     | Tristate                   | 28          | 42          | 50          |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                          |                                                                     | eral                                                            | uo                                   | pe <sup>2</sup>       | Fr. ga                     | Pi          | n numb      | er          |

|--------|----------|------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>              | Function                                                            | Peripheral                                                      | I/O<br>direction                     | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PA[15] | PCR[15]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[15]<br>CS0_0<br>SCK_0<br>E0UC[1]<br>WKUP[10] <sup>4</sup>      | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>WKUP                     | I/O<br>I/O<br>I/O<br>I/O             | М                     | Tristate                   | 27          | 40          | 48          |

|        |          |                                    |                                                                     | Port B                                                          |                                      |                       |                            |             |             |             |

| PB[0]  | PCR[16]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[16]<br>CAN0TX<br>E0UC[30]<br>LIN0TX                            | SIUL<br>FlexCAN_0<br>eMIOS_0<br>LINFlex_0                       | I/O<br>O<br>I/O<br>O                 | М                     | Tristate                   | 23          | 31          | 39          |

| PB[1]  | PCR[17]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[17]  E0UC[31]  WKUP[4] <sup>4</sup> CANORX LINORX              | SIUL — eMIOS_0 — WKUP FlexCAN_0 LINFlex_0                       | I/O<br>—<br>I/O<br>—<br>I<br>I       | S                     | Tristate                   | 24          | 32          | 40          |

| PB[2]  | PCR[18]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[18]<br>LINOTX<br>SDA<br>E0UC[30]                               | SIUL<br>LINFlex_0<br>I <sup>2</sup> C_0<br>eMIOS_0              | I/O<br>O<br>I/O<br>I/O               | М                     | Tristate                   | 100         | 144         | 176         |

| PB[3]  | PCR[19]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[19]<br>E0UC[31]<br>SCL<br>—<br>WKUP[11] <sup>4</sup><br>LIN0RX | SIUL<br>eMIOS_0<br>I <sup>2</sup> C_0<br>—<br>WKUP<br>LINFlex_0 | I/O<br>I/O<br>I/O<br>—<br>—<br>I     | S                     | Tristate                   | 1           | 1           | 1           |

| PB[4]  | PCR[20]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | —<br>—<br>—<br>ADC0_P[0]<br>ADC1_P[0]<br>GPIO[20]                   | —<br>—<br>—<br>ADC_0<br>ADC_1<br>SIUL                           | -<br>-<br>-<br>-<br>-<br>-<br>-<br>- | I                     | Tristate                   | 50          | 72          | 88          |

| PB[5]  | PCR[21]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | —<br>—<br>—<br>ADC0_P[1]<br>ADC1_P[1]<br>GPIO[21]                   | —<br>—<br>—<br>ADC_0<br>ADC_1<br>SIUL                           | -<br>-<br>-<br>-<br>!                | I                     | Tristate                   | 53          | 75          | 91          |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                               |                                                                      | eral                                    | uo                                        | pe <sup>2</sup>       | F                          | Pi          | in numb     | er          |

|--------|----------|-----------------------------------------|----------------------------------------------------------------------|-----------------------------------------|-------------------------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>                   | Function                                                             | Peripheral                              | I/O<br>direction                          | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PB[6]  | PCR[22]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | —<br>—<br>—<br>—<br>ADC0_P[2]<br>ADC1_P[2]<br>GPIO[22]               | —<br>—<br>—<br>ADC_0<br>ADC_1<br>SIUL   |                                           | I                     | Tristate                   | 54          | 76          | 92          |

| PB[7]  | PCR[23]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | —<br>—<br>—<br>—<br>ADC0_P[3]<br>ADC1_P[3]<br>GPIO[23]               | —<br>—<br>—<br>ADC_0<br>ADC_1<br>SIUL   |                                           | I                     | Tristate                   | 55          | 77          | 93          |

| PB[8]  | PCR[24]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[24] — — — OSC32K_XTAL <sup>7</sup> WKUP[25] ADC0_S[0] ADC1_S[4] | SIUL  OSC32K WKUP ADC_0 ADC_1           |                                           | 1                     | _                          | 39          | 53          | 61          |

| PB[9]  | PCR[25]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[25]  OSC32K_EXTAL <sup>7</sup> WKUP[26]  ADC0_S[1]  ADC1_S[5]   | SIUL  OSC32K WKUP ADC_0 ADC_1           | <br> -<br> -<br> -<br> -<br> -<br> -      | ı                     | _                          | 38          | 52          | 60          |

| PB[10] | PCR[26]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[26]  WKUP[8] <sup>4</sup> ADC0_S[2] ADC1_S[6]                   | SIUL  WKUP ADC_0 ADC_1                  | I/O — — — — — — — — — — — — — — — — — — — | J                     | Tristate                   | 40          | 54          | 62          |

| PB[11] | PCR[27]  | AF0<br>AF1<br>AF2<br>AF3                | GPIO[27]<br>E0UC[3]<br>—<br>CS0_0<br>ADC0_S[3]                       | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>—<br>I/O<br>I               | J                     | Tristate                   | _           | _           | 97          |

| PB[12] | PCR[28]  | AF0<br>AF1<br>AF2<br>AF3                | GPIO[28]<br>E0UC[4]<br>—<br>CS1_0<br>ADC0_X[0]                       | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>—<br>O                      | J                     | Tristate                   | 61          | 83          | 101         |

Table 2. Functional port pins (continued)

| Port               | PCR      | Alternate                          |                                                     | eral                                                              | noi                            | pe <sup>2</sup>       | F                          | Pi          | in numb     | er          |

|--------------------|----------|------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------|--------------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin                | register | function <sup>1</sup>              | Function                                            | Peripheral                                                        | I/O<br>direction               | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PB[13]             | PCR[29]  | AF0<br>AF1<br>AF2                  | GPIO[29]<br>E0UC[5]                                 | SIUL<br>eMIOS_0                                                   | I/O<br>I/O                     | J                     | Tristate                   | 63          | 85          | 103         |

|                    |          | AF3                                | CS2_0<br>ADC0_X[1]                                  | DSPI_0<br>ADC_0                                                   | O<br>                          |                       |                            |             |             |             |

| PB[14]             | PCR[30]  | AF0<br>AF1<br>AF2                  | GPIO[30]<br>E0UC[6]                                 | SIUL<br>eMIOS_0                                                   | I/O<br>I/O                     | J                     | Tristate                   | 65          | 87          | 105         |

|                    |          | AF3                                | <br>CS3_0<br>ADC0_X[2]                              | DSPI_0<br>ADC_0                                                   | <u>о</u><br>І                  |                       |                            |             |             |             |

| PB[15]             | PCR[31]  | AF0<br>AF1<br>AF2                  | GPIO[31]<br>E0UC[7]                                 | SIUL<br>eMIOS_0                                                   | I/O<br>I/O                     | J                     | Tristate                   | 67          | 89          | 107         |

|                    |          | AF3                                | <br>CS4_0<br>ADC0_X[3]                              | DSPI_0<br>ADC_0                                                   | <u>о</u><br>І                  |                       |                            |             |             |             |

|                    |          |                                    |                                                     | Port C                                                            |                                |                       |                            |             |             |             |

| PC[0] <sup>8</sup> | PCR[32]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[32]<br>—<br>TDI<br>—                           | SIUL<br>—<br>JTAGC<br>—                                           | I/O<br>—<br>I                  | М                     | Input,<br>weak<br>pull-up  | 87          | 126         | 154         |

| PC[1] <sup>8</sup> | PCR[33]  | AF0<br>AF1                         | GPIO[33]                                            | SIUL<br>—                                                         | I/O<br>—                       | F <sup>9</sup>        | Tristate                   | 82          | 121         | 149         |

|                    |          | AF2<br>AF3                         | TDO<br>—                                            | JTAGC<br>—                                                        | <u>0</u>                       |                       |                            |             |             |             |

| PC[2]              | PCR[34]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[34]<br>SCK_1<br>CAN4TX<br>DEBUG[0]<br>EIRQ[5]  | SIUL<br>DSPI_1<br>FlexCAN_4<br>SSCM<br>SIUL                       | I/O<br>I/O<br>O<br>O           | M                     | Tristate                   | 78          | 117         | 145         |

| PC[3]              | PCR[35]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[35] CS0_1 MA[0] DEBUG[1] EIRQ[6] CAN1RX CAN4RX | SIUL<br>DSPI_1<br>ADC_0<br>SSCM<br>SIUL<br>FlexCAN_1<br>FlexCAN_4 | I/O<br>I/O<br>O<br>O<br>I<br>I | S                     | Tristate                   | 77          | 116         | 144         |

| PC[4]              | PCR[36]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[36] E1UC[31] — DEBUG[2] EIRQ[18] SIN_1 CAN3RX  | SIUL<br>eMIOS_1<br>—<br>SSCM<br>SIUL<br>DSPI_1<br>FlexCAN_3       | I/O<br>I/O<br>—<br>O<br>I      | M                     | Tristate                   | 92          | 131         | 159         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                          |                                                                          | eral                                        | uo                        | pe <sup>2</sup>       | F                          | P           | in numb     | er          |

|--------|----------|------------------------------------|--------------------------------------------------------------------------|---------------------------------------------|---------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>              | Function                                                                 | Peripheral                                  | I/O<br>direction          | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PC[5]  | PCR[37]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[37]<br>SOUT_1<br>CAN3TX<br>DEBUG[3]<br>EIRQ[7]                      | SIUL<br>DSPI_1<br>FlexCAN_3<br>SSCM<br>SIUL | I/O<br>O<br>O<br>O        | М                     | Tristate                   | 91          | 130         | 158         |

| PC[6]  | PCR[38]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[38]<br>LIN1TX<br>E1UC[28]<br>DEBUG[4]                               | SIUL<br>LINFlex_1<br>eMIOS_1<br>SSCM        | I/O<br>O<br>I/O<br>O      | S                     | Tristate                   | 25          | 36          | 44          |

| PC[7]  | PCR[39]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[39]<br>—<br>E1UC[29]<br>DEBUG[5]<br>LIN1RX<br>WKUP[12] <sup>4</sup> | SIUL  eMIOS_1 SSCM LINFlex_1 WKUP           | I/O<br>—<br>I/O<br>O<br>I | S                     | Tristate                   | 26          | 37          | 45          |

| PC[8]  | PCR[40]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[40]<br>LIN2TX<br>E0UC[3]<br>DEBUG[6]                                | SIUL<br>LINFlex_2<br>eMIOS_0<br>SSCM        | I/O<br>O<br>I/O<br>O      | S                     | Tristate                   | 99          | 143         | 175         |

| PC[9]  | PCR[41]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[41]<br>—<br>E0UC[7]<br>DEBUG[7]<br>WKUP[13] <sup>4</sup><br>LIN2RX  | SIUL eMIOS_0 SSCM WKUP LINFlex_2            | I/O<br>—<br>I/O<br>O<br>I | S                     | Tristate                   | 2           | 2           | 2           |

| PC[10] | PCR[42]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[42]<br>CAN1TX<br>CAN4TX<br>MA[1]                                    | SIUL<br>FlexCAN_1<br>FlexCAN_4<br>ADC_0     | I/O<br>O<br>O             | М                     | Tristate                   | 22          | 28          | 36          |

| PC[11] | PCR[43]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[43]  —  MA[2]  WKUP[5] <sup>4</sup> CAN1RX  CAN4RX                  | SIUL  ADC_0  WKUP FlexCAN_1 FlexCAN_4       | I/O<br>—<br>O<br>I<br>I   | S                     | Tristate                   | 21          | 27          | 35          |

| PC[12] | PCR[44]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[44]<br>E0UC[12]<br>—<br>—<br>EIRQ[19]<br>SIN_2                      | SIUL<br>eMIOS_0<br>—<br>—<br>SIUL<br>DSPI_2 | I/O<br>I/O<br>—<br>—<br>I | М                     | Tristate                   | 97          | 141         | 173         |

| PC[13] | PCR[45]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[45]<br>E0UC[13]<br>SOUT_2<br>—                                      | SIUL<br>eMIOS_0<br>DSPI_2<br>—              | I/O<br>I/O<br>O<br>—      | S                     | Tristate                   | 98          | 142         | 174         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                          |                                        | eral                      | ion                            | pe <sup>2</sup>       | L °S                       | Pi          | in numb     | er          |

|--------|----------|------------------------------------|----------------------------------------|---------------------------|--------------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>              | Function                               | Peripheral                | I/O<br>direction               | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PC[14] | PCR[46]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[46]<br>E0UC[14]<br>SCK_2          | SIUL<br>eMIOS_0<br>DSPI_2 | I/O<br>I/O<br>I/O              | S                     | Tristate                   | 3           | 3           | 3           |

|        |          | —                                  | EIRQ[8]                                | SIUL                      | I                              |                       |                            |             |             |             |

| PC[15] | PCR[47]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[47]<br>E0UC[15]<br>CS0_2          | SIUL<br>eMIOS_0<br>DSPI_2 | I/O<br>I/O<br>I/O              | М                     | Tristate                   | 4           | 4           | 4           |

|        |          | — —                                | EIRQ[20]                               | SIUL                      | 1                              |                       |                            |             |             |             |

|        |          |                                    |                                        | Port D                    |                                |                       |                            |             |             |             |

| PD[0]  | PCR[48]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[48]  WKUP[27] ADC0_P[4] ADC1_P[4] | SIUL  WKUP ADC_0 ADC_1    | <br> -<br> -<br> -<br> -<br> - | I                     | Tristate                   | 41          | 63          | 77          |

| PD[1]  | PCR[49]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[49]  WKUP[28] ADC0_P[5] ADC1_P[5] | SIUL  WKUP ADC_0 ADC_1    | -<br>-<br>-<br>-<br>-          | I                     | Tristate                   | 42          | 64          | 78          |

| PD[2]  | PCR[50]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[50]  ADC0_P[6] ADC1_P[6]          | SIUL  ADC_0 ADC_1         | -                              | I                     | Tristate                   | 43          | 65          | 79          |

| PD[3]  | PCR[51]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[51]  — — — ADC0_P[7] ADC1_P[7]    | SIUL  ADC_0 ADC_1         | -                              | I                     | Tristate                   | 44          | 66          | 80          |

| PD[4]  | PCR[52]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[52]  ADC0_P[8] ADC1_P[8]          | SIUL  ADC_0 ADC_1         | -                              | I                     | Tristate                   | 45          | 67          | 81          |

Table 2. Functional port pins (continued)

| Port    | PCR       | Alternate             |                          | eral           | ion              | pe <sup>2</sup>       | 9:3                           | Pi          | in numb     | er          |

|---------|-----------|-----------------------|--------------------------|----------------|------------------|-----------------------|-------------------------------|-------------|-------------|-------------|

| pin     | register  | function <sup>1</sup> | Function                 | Peripheral     | I/O<br>direction | Pad type <sup>2</sup> | RESET<br>config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PD[5]   | PCR[53]   | AF0<br>AF1            | GPIO[53]                 | SIUL           | I<br>_           | I                     | Tristate                      | 46          | 68          | 82          |

|         |           | AF2<br>AF3            | _                        | _              | _                |                       |                               |             |             |             |

|         |           | —<br>—                | ADC0_P[9]                | ADC_0          |                  |                       |                               |             |             |             |

| PD[6]   | PCR[54]   | AF0                   | ADC1_P[9]<br>GPIO[54]    | ADC_1<br>SIUL  | I                | 1                     | Tristate                      | 47          | 69          | 83          |

|         | . [. ]    | AF1<br>AF2            | _                        |                | _                |                       |                               |             |             |             |

|         |           | AF3                   | —<br>ADCO DIAOI          |                | _<br>            |                       |                               |             |             |             |

|         |           | _                     | ADC0_P[10]<br>ADC1_P[10] | ADC_0<br>ADC_1 | I                |                       |                               |             |             |             |

| PD[7]   | PCR[55]   | AF0<br>AF1            | GPIO[55]                 | SIUL           | I<br>_           | I                     | Tristate                      | 48          | 70          | 84          |

|         |           | AF2<br>AF3            | _                        | _              | _                |                       |                               |             |             |             |

|         |           | _                     | ADC0_P[11]               | ADC_0          | I<br>!           |                       |                               |             |             |             |

| PD[8]   | PCR[56]   | AF0                   | ADC1_P[11]<br>GPIO[56]   | ADC_1<br>SIUL  |                  | <u> </u>              | Tristate                      | 49          | 71          | 87          |

| 1 0[0]  | i Ortiooj | AF1<br>AF2            | —<br>—                   | —              | <u> </u>         |                       | motate                        | 40          | ''          |             |

|         |           | AF2<br>AF3            |                          | _              | _<br>_           |                       |                               |             |             |             |

|         |           | _                     | ADC0_P[12]<br>ADC1_P[12] | ADC_0<br>ADC_1 | l<br>I           |                       |                               |             |             |             |

| PD[9]   | PCR[57]   | AF0<br>AF1            | GPIO[57]                 | SIUL           | 1                | I                     | Tristate                      | 56          | 78          | 94          |

|         |           | AF2                   | _                        | _              | _                |                       |                               |             |             |             |

|         |           | AF3<br>—              | —<br>ADC0_P[13]          | ADC_0          | <u> </u>         |                       |                               |             |             |             |

| PD[10]  | PCR[58]   | —<br>AF0              | ADC1_P[13]<br>GPIO[58]   | ADC_1<br>SIUL  | I                | 1                     | Tristate                      | 57          | 79          | 95          |

| I D[10] | r Civ[30] | AF1                   | —<br>—                   | —<br>—         | _                | <b>'</b>              | Tristate                      | 37          | 79          | 93          |

|         |           | AF2<br>AF3            | _                        | _              | _                |                       |                               |             |             |             |

|         |           | _                     | ADC0_P[14]<br>ADC1_P[14] | ADC_0<br>ADC_1 | l<br>I           |                       |                               |             |             |             |

| PD[11]  | PCR[59]   | AF0                   | GPIO[59]                 | SIUL           | I                | I                     | Tristate                      | 58          | 80          | 96          |

|         |           | AF1<br>AF2            | _                        | _              | _                |                       |                               |             |             |             |

|         |           | AF3<br>—              | ADC0_P[15]               | ADC_0          |                  |                       |                               |             |             |             |

| PD[12]  | PCR[60]   | AF0                   | ADC1_P[15]<br>GPIO[60]   | ADC_1<br>SIUL  | I<br>I/O         | J                     | Tristate                      |             | _           | 100         |

| 1 0[12] | r Ort[00] | AF1                   | CS5_0                    | DSPI_0         | 0                |                       | molate                        | _ <b>_</b>  |             | 100         |

|         |           | AF2<br>AF3            | E0UC[24]<br>—            | eMIOS_0        | I/O<br>—         |                       |                               |             |             |             |

|         |           | _                     | ADC0_S[4]                | ADC_0          | ļ                |                       |                               |             |             |             |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                     |                                                     | eral                                        | uo                        | pe <sup>2</sup>       | Fr. g                      | P           | in numb     | er          |

|--------|----------|-------------------------------|-----------------------------------------------------|---------------------------------------------|---------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>         | Function                                            | Peripheral                                  | I/O<br>direction          | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PD[13] | PCR[61]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[61]<br>CS0_1<br>E0UC[25]                       | SIUL<br>DSPI_1<br>eMIOS_0                   | I/O<br>I/O<br>I/O         | J                     | Tristate                   | 62          | 84          | 102         |

|        |          | — —                           | ADC0_S[5]                                           | ADC_0                                       | ı                         |                       |                            |             |             |             |

| PD[14] | PCR[62]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[62]                                            | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC_0     | I/O<br>O<br>I/O<br>—<br>I | J                     | Tristate                   | 64          | 86          | 104         |

| PD[15] | PCR[63]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>ADC0_S[7]     | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC_0     | I/O<br>O<br>I/O<br>—      | J                     | Tristate                   | 66          | 88          | 106         |

|        |          |                               | <u> </u>                                            | Port E                                      | '                         |                       |                            |             |             |             |

| PE[0]  | PCR[64]  | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[64] E0UC[16] — — WKUP[6] <sup>4</sup> CAN5RX   | SIUL<br>eMIOS_0<br>—<br>WKUP<br>FlexCAN_5   | I/O<br>I/O<br>—<br>—<br>I | S                     | Tristate                   | 6           | 10          | 18          |

| PE[1]  | PCR[65]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[65]<br>E0UC[17]<br>CAN5TX<br>—                 | SIUL<br>eMIOS_0<br>FlexCAN_5<br>—           | I/O<br>I/O<br>O           | М                     | Tristate                   | 8           | 12          | 20          |

| PE[2]  | PCR[66]  | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[66]<br>E0UC[18]<br>—<br>—<br>EIRQ[21]<br>SIN_1 | SIUL<br>eMIOS_0<br>—<br>—<br>SIUL<br>DSPI_1 | I/O<br>I/O<br>—<br>—<br>I | М                     | Tristate                   | 89          | 128         | 156         |

| PE[3]  | PCR[67]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[67]<br>E0UC[19]<br>SOUT_1<br>—                 | SIUL<br>eMIOS_0<br>DSPI_1<br>—              | I/O<br>I/O<br>O           | М                     | Tristate                   | 90          | 129         | 157         |

| PE[4]  | PCR[68]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[68]<br>E0UC[20]<br>SCK_1<br>—<br>EIRQ[9]       | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>SIUL      | I/O<br>I/O<br>I/O<br>—    | М                     | Tristate                   | 93          | 132         | 160         |

| PE[5]  | PCR[69]  | AF0<br>AF1<br>AF2<br>AF3      | GPIO[69]<br>E0UC[21]<br>CS0_1<br>MA[2]              | SIUL<br>eMIOS_0<br>DSPI_1<br>ADC_0          | I/O<br>I/O<br>I/O<br>O    | М                     | Tristate                   | 94          | 133         | 161         |

**Table 2. Functional port pins (continued)**

| Port   | PCR     | Alternate                          |                                                                       | eral                                                | noi                       | pe <sup>2</sup>       | H. 3                       | Pi          | in numb     | er          |

|--------|---------|------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|---------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    |         | function <sup>1</sup>              | Function                                                              | Peripheral                                          | I/O<br>direction          | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PE[6]  | PCR[70] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[70]<br>E0UC[22]<br>CS3_0<br>MA[1]<br>EIRQ[22]                    | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC_0<br>SIUL          | I/O<br>I/O<br>O<br>O      | M                     | Tristate                   | 95          | 139         | 167         |

| PE[7]  | PCR[71] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[71]<br>E0UC[23]<br>CS2_0<br>MA[0]<br>EIRQ[23]                    | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC_0<br>SIUL          | I/O<br>I/O<br>O<br>O      | М                     | Tristate                   | 96          | 140         | 168         |

| PE[8]  | PCR[72] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[72]<br>CAN2TX<br>E0UC[22]<br>CAN3TX                              | SIUL<br>FlexCAN_2<br>eMIOS_0<br>FlexCAN_3           | I/O<br>O<br>I/O<br>O      | М                     | Tristate                   | 9           | 13          | 21          |

| PE[9]  | PCR[73] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[73]  — E0UC[23]  — WKUP[7] <sup>4</sup> CAN2RX CAN3RX            | SIUL — eMIOS_0 — WKUP FlexCAN_2 FlexCAN_3           | I/O<br>—<br>I/O<br>—<br>I | S                     | Tristate                   | 10          | 14          | 22          |

| PE[10] | PCR[74] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[74]<br>LIN3TX<br>CS3_1<br>E1UC[30]<br>EIRQ[10]                   | SIUL<br>LINFlex_3<br>DSPI_1<br>eMIOS_1<br>SIUL      | I/O<br>O<br>O<br>I/O<br>I | S                     | Tristate                   | 11          | 15          | 23          |

| PE[11] | PCR[75] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[75]<br>E0UC[24]<br>CS4_1<br>—<br>LIN3RX<br>WKUP[14] <sup>4</sup> | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>LINFlex_3<br>WKUP | I/O<br>I/O<br>O<br>—<br>I | S                     | Tristate                   | 13          | 17          | 25          |

| PE[12] | PCR[76] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[76]  — E1UC[19] <sup>10</sup> — EIRQ[11]  SIN_2 ADC1_S[7]        | SIUL  eMIOS_1  SIUL DSPI_2 ADC_1                    | I/O<br><br>I/O<br><br>I   | J                     | Tristate                   | 76          | 109         | 133         |

| PE[13] | PCR[77] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[77]<br>SOUT_2<br>E1UC[20]<br>—                                   | SIUL<br>DSPI_2<br>eMIOS_1                           | I/O<br>O<br>I/O           | S                     | Tristate                   | _           | 103         | 127         |

Table 2. Functional port pins (continued)

| Port   | PCR       | Alternate                             |                                                  | eral                                    | o                    | pe <sup>2</sup>       | F. E.                      | Pi          | in numb     | er          |

|--------|-----------|---------------------------------------|--------------------------------------------------|-----------------------------------------|----------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register  | function <sup>1</sup>                 | Function                                         | Peripheral                              | I/O<br>direction     | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PE[14] | PCR[78]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[78]<br>SCK_2<br>E1UC[21]                    | SIUL<br>DSPI_2<br>eMIOS_1               | I/O<br>I/O<br>I/O    | S                     | Tristate                   | _           | 112         | 136         |

|        |           | _                                     | EIRQ[12]                                         | SIUL                                    | I                    |                       |                            |             |             |             |

| PE[15] | PCR[79]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[79]<br>CS0_2<br>E1UC[22]<br>—               | SIUL<br>DSPI_2<br>eMIOS_1<br>—          | I/O<br>I/O<br>I/O    | М                     | Tristate                   |             | 113         | 137         |

|        |           |                                       |                                                  | Port F                                  |                      | •                     |                            |             |             |             |

| PF[0]  | PCR[80]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[80]<br>E0UC[10]<br>CS3_1<br>—               | SIUL<br>eMIOS_0<br>DSPI_1<br>—          | I/O<br>I/O<br>O      | J                     | Tristate                   | _           | 55          | 63          |

|        |           | _                                     | ADC0_S[8]                                        | ADC_0                                   | I                    |                       |                            |             |             |             |

| PF[1]  | PCR[81]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[81]<br>E0UC[11]<br>CS4_1<br>—               | SIUL<br>eMIOS_0<br>DSPI_1               | I/O<br>I/O<br>O      | J                     | Tristate                   | _           | 56          | 64          |

| DEIO   | DCD[00]   | AF0                                   | ADC0_S[9]<br>GPIO[82]                            | ADC_0<br>SIUL                           | I<br>I/O             | J                     | Tristate                   |             | <i>E7</i>   | 65          |

| PF[2]  | PCR[82]   | AF1<br>AF2<br>AF3                     | E0UC[12]<br>CS0_2<br>—                           | eMIOS_0<br>DSPI_2<br>—                  | 1/0<br>0<br>—        | J                     | mstate                     |             | 57          | 65          |

| PF[3]  | PCR[83]   | AF0                                   | ADC0_S[10]<br>GPIO[83]                           | ADC_0<br>SIUL                           | I/O                  | J                     | Tristate                   |             | 58          | 66          |

| 11[0]  | i Citiooj | AF1<br>AF2<br>AF3                     | E0UC[13]<br>CS1_2                                | eMIOS_0<br>DSPI_2                       | 1/0                  | 3                     | Tilstate                   |             | 30          | 00          |

|        |           | — — — — — — — — — — — — — — — — — — — | ADC0_S[11]                                       | ADC_0                                   | I                    |                       |                            |             |             |             |

| PF[4]  | PCR[84]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[84]<br>E0UC[14]<br>CS2_2<br>—<br>ADC0_S[12] | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>ADC_0 | I/O<br>I/O<br>O<br>  | J                     | Tristate                   |             | 59          | 67          |

| PF[5]  | PCR[85]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[85]<br>E0UC[22]<br>CS3_2<br>—<br>ADC0_S[13] | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>ADC_0 | I/O<br>I/O<br>O<br>— | J                     | Tristate                   | _           | 60          | 68          |

| PF[6]  | PCR[86]   | AF0<br>AF1<br>AF2<br>AF3              | GPIO[86]<br>E0UC[23]<br>CS1_1                    | SIUL<br>eMIOS_0<br>DSPI_1               | I/O<br>I/O<br>O      | J                     | Tristate                   | _           | 61          | 69          |

|        |           | — —                                   | ADC0_S[14]                                       | ADC_0                                   | -                    |                       |                            |             |             |             |

**Table 2. Functional port pins (continued)**

| Port   | PCR     | Alternate                          |                                                                   | eral                                                             | ion                            | pe <sup>2</sup>       | H. 93.3                    | Pi          | in numb     | er          |

|--------|---------|------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    |         | function <sup>1</sup>              | Function                                                          | Peripheral                                                       | I/O<br>direction               | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PF[7]  | PCR[87] | AF0<br>AF1                         | GPIO[87]                                                          | SIUL                                                             | I/O                            | J                     | Tristate                   | _           | 62          | 70          |

|        |         | AF2                                | <br>CS2_1                                                         | DSPI_1                                                           | 0                              |                       |                            |             |             |             |

|        |         | AF3<br>—                           | —<br>ADC0_S[15]                                                   | ADC_0                                                            | 1                              |                       |                            |             |             |             |

| PF[8]  | PCR[88] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[88]<br>CAN3TX<br>CS4_0<br>CAN2TX                             | SIUL<br>FlexCAN_3<br>DSPI_0<br>FlexCAN_2                         | I/O<br>O<br>O                  | М                     | Tristate                   | _           | 34          | 42          |

| PF[9]  | PCR[89] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[89] E1UC[1] CS5_0 — WKUP[22] <sup>4</sup> CAN2RX CAN3RX      | SIUL<br>eMIOS_1<br>DSPI_0<br>—<br>WKUP<br>FlexCAN_2<br>FlexCAN_3 | I/O<br>I/O<br>O<br>—<br>I<br>I | S                     | Tristate                   |             | 33          | 41          |

| PF[10] | PCR[90] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[90]<br>CS1_0<br>LIN4TX<br>E1UC[2]                            | SIUL<br>DSPI_0<br>LINFlex_4<br>eMIOS_1                           | I/O<br>O<br>O<br>I/O           | M                     | Tristate                   | _           | 38          | 46          |

| PF[11] | PCR[91] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[91]<br>CS2_0<br>E1UC[3]<br>—<br>WKUP[15] <sup>4</sup>        | SIUL<br>DSPI_0<br>eMIOS_1<br>—<br>WKUP                           | I/O<br>O<br>I/O<br>—           | S                     | Tristate                   | _           | 39          | 47          |

| DEI401 | DCDIOOL | AF0                                | LIN4RX                                                            | LINFlex_4 SIUL                                                   | I/O                            | М                     | Triototo                   |             | 25          | 42          |

| PF[12] | PCR[92] | AF1<br>AF2<br>AF3                  | GPIO[92]<br>E1UC[25]<br>LIN5TX<br>—                               | eMIOS_1<br>LINFlex_5                                             | 1/O<br>O<br>—                  | IVI                   | Tristate                   | _           | 35          | 43          |

| PF[13] | PCR[93] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[93]<br>E1UC[26]<br>—<br>—<br>WKUP[16] <sup>4</sup><br>LIN5RX | SIUL<br>eMIOS_1<br>—<br>—<br>WKUP<br>LINFlex_5                   | I/O<br>I/O<br>—<br>—<br>I      | S                     | Tristate                   |             | 41          | 49          |

| PF[14] | PCR[94] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[94]<br>CAN4TX<br>E1UC[27]<br>CAN1TX                          | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_1                        | I/O<br>O<br>I/O<br>O           | М                     | Tristate                   | _           | 102         | 126         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                          |                                                                   | eral                                                        | ion                            | pe <sup>2</sup>       | F::6                       | Pi          | in numb     | er          |

|--------|----------|------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>              | Function                                                          | Peripheral                                                  | I/O<br>direction               | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PF[15] | PCR[95]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[95] E1UC[4] — — EIRQ[13] CAN1RX CAN4RX                       | SIUL<br>eMIOS_1<br>—<br>—<br>SIUL<br>FlexCAN_1<br>FlexCAN_4 | I/O<br>I/O<br>—<br>—<br>I<br>I | S                     | Tristate                   | 1           | 101         | 125         |

|        |          |                                    |                                                                   | Port G                                                      |                                |                       |                            |             |             |             |

| PG[0]  | PCR[96]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[96]<br>CAN5TX<br>E1UC[23]<br>—                               | SIUL<br>FlexCAN_5<br>eMIOS_1                                | I/O<br>O<br>I/O                | М                     | Tristate                   | _           | 98          | 122         |

| PG[1]  | PCR[97]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[97] — E1UC[24] — EIRQ[14] CAN5RX                             | SIUL eMIOS_1 SIUL FlexCAN_5                                 | I/O<br>—<br>I/O<br>—<br>I      | S                     | Tristate                   | _           | 97          | 121         |

| PG[2]  | PCR[98]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[98]<br>E1UC[11]<br>SOUT_3<br>—                               | SIUL<br>eMIOS_1<br>DSPI_3<br>—                              | I/O<br>I/O<br>O                | М                     | Tristate                   | _           | 8           | 16          |

| PG[3]  | PCR[99]  | AF0<br>AF1<br>AF2<br>AF3           | GPIO[99]<br>E1UC[12]<br>CS0_3<br>—<br>WKUP[17] <sup>4</sup>       | SIUL<br>eMIOS_1<br>DSPI_3<br>—<br>WKUP                      | I/O<br>I/O<br>O<br>—           | S                     | Tristate                   | _           | 7           | 15          |

| PG[4]  | PCR[100] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[100]<br>E1UC[13]<br>SCK_3<br>—                               | SIUL<br>eMIOS_1<br>DSPI_3<br>—                              | I/O<br>I/O<br>I/O              | М                     | Tristate                   | _           | 6           | 14          |

| PG[5]  | PCR[101] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[101]<br>E1UC[14]<br>—<br>—<br>WKUP[18] <sup>4</sup><br>SIN_3 | SIUL<br>eMIOS_1<br>—<br>—<br>WKUP<br>DSPI_3                 | I/O<br>I/O<br>—<br>—<br>I      | S                     | Tristate                   | _           | 5           | 13          |

| PG[6]  | PCR[102] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[102]<br>E1UC[15]<br>LIN6TX<br>—                              | SIUL<br>eMIOS_1<br>LINFlex_6                                | I/O<br>I/O<br>O                | М                     | Tristate                   | _           | 30          | 38          |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                     |                                                                        | eral                                                | ion                         | pe <sup>2</sup>       | ET                         | Pi          | in numb     | er          |

|--------|----------|-------------------------------|------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    |          | function <sup>1</sup>         | Function                                                               | Peripheral                                          | I/O<br>direction            | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PG[7]  | PCR[103] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[103]<br>E1UC[16]<br>E1UC[30]                                      | SIUL<br>eMIOS_1<br>eMIOS_1                          | I/O<br>I/O<br>I/O           | S                     | Tristate                   | _           | 29          | 37          |

|        |          | —<br>—                        | WKUP[20] <sup>4</sup><br>LIN6RX                                        | WKUP<br>LINFlex_6                                   | 1                           |                       |                            |             |             |             |

| PG[8]  | PCR[104] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[104]<br>E1UC[17]<br>LIN7TX<br>CS0_2<br>EIRQ[15]                   | SIUL<br>eMIOS_1<br>LINFlex_7<br>DSPI_2<br>SIUL      | I/O<br>I/O<br>O<br>I/O      | S                     | Tristate                   | _           | 26          | 34          |

| PG[9]  | PCR[105] | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[105]<br>E1UC[18]<br>—<br>SCK_2<br>WKUP[21] <sup>4</sup><br>LIN7RX | SIUL<br>eMIOS_1<br>—<br>DSPI_2<br>WKUP<br>LINFlex_7 | I/O<br>I/O<br>—<br>I/O<br>I | S                     | Tristate                   | _           | 25          | 33          |

| PG[10] | PCR[106] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[106]<br>E0UC[24]<br>E1UC[31]                                      | SIUL<br>eMIOS_0<br>eMIOS_1                          | I/O<br>I/O<br>I/O           | S                     | Tristate                   | _           | 114         | 138         |

| PG[11] | PCR[107] | AF0<br>AF1<br>AF2<br>AF3      | SIN_4<br>GPIO[107]<br>E0UC[25]<br>CS0_4                                | SIUL<br>eMIOS_0<br>DSPI_4                           | I/O<br> /O<br>  O<br> -     | M                     | Tristate                   | _           | 115         | 139         |

| PG[12] | PCR[108] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[108]<br>E0UC[26]<br>SOUT_4<br>—                                   | SIUL<br>eMIOS_0<br>DSPI_4<br>—                      | I/O<br>I/O<br>O             | М                     | Tristate                   |             | 92          | 116         |

| PG[13] | PCR[109] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[109]<br>E0UC[27]<br>SCK_4<br>—                                    | SIUL<br>eMIOS_0<br>DSPI_4<br>—                      | I/O<br>I/O<br>I/O           | М                     | Tristate                   | _           | 91          | 115         |

| PG[14] | PCR[110] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[110]<br>E1UC[0]<br>—<br>—                                         | SIUL<br>eMIOS_1<br>—                                | I/O<br>I/O<br>—             | S                     | Tristate                   | ı           | 110         | 134         |

| PG[15] | PCR[111] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[111]<br>E1UC[1]<br>—<br>—<br>—                                    | SIUL<br>eMIOS_1<br>—<br>—                           | I/O<br>I/O<br>—             | M                     | Tristate                   | _           | 111         | 135         |

|        |          |                               |                                                                        | Port H                                              |                             |                       |                            |             |             |             |

Table 2. Functional port pins (continued)

| Port                | PCR      | Alternate                |                                         | eral                               | uo                   | pe <sup>2</sup>       | L. Ex                         | Pi          | in numb     | er          |

|---------------------|----------|--------------------------|-----------------------------------------|------------------------------------|----------------------|-----------------------|-------------------------------|-------------|-------------|-------------|

| pin                 | register | function <sup>1</sup>    | Function                                | Peripheral                         | I/O<br>direction     | Pad type <sup>2</sup> | RESET<br>config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PH[0]               | PCR[112] | AF0<br>AF1<br>AF2        | GPIO[112]<br>E1UC[2]<br>—               | SIUL<br>eMIOS_1<br>—               | I/O<br>I/O<br>—      | М                     | Tristate                      | _           | 93          | 117         |

|                     |          | AF3<br>—                 | SIN_1                                   | DSPI_1                             | _<br>                |                       |                               |             |             |             |

| PH[1]               | PCR[113] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[113]<br>E1UC[3]<br>SOUT_1<br>—     | SIUL<br>eMIOS_1<br>DSPI_1<br>—     | I/O<br>I/O<br>O      | М                     | Tristate                      | _           | 94          | 118         |

| PH[2]               | PCR[114] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[114]<br>E1UC[4]<br>SCK_1<br>—      | SIUL<br>eMIOS_1<br>DSPI_1<br>—     | I/O<br>I/O<br>I/O    | М                     | Tristate                      | _           | 95          | 119         |

| PH[3]               | PCR[115] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[115]<br>E1UC[5]<br>CS0_1<br>—      | SIUL<br>eMIOS_1<br>DSPI_1<br>—     | I/O<br>I/O<br>I/O    | М                     | Tristate                      | _           | 96          | 120         |

| PH[4]               | PCR[116] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[116]<br>E1UC[6]<br>—<br>—          | SIUL<br>eMIOS_1<br>—               | I/O<br>I/O<br>—      | М                     | Tristate                      | -           | 134         | 162         |

| PH[5]               | PCR[117] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[117]<br>E1UC[7]<br>—<br>—          | SIUL<br>eMIOS_1<br>—               | I/O<br>I/O<br>—      | S                     | Tristate                      | _           | 135         | 163         |

| PH[6]               | PCR[118] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[118]<br>E1UC[8]<br>—<br>MA[2]      | SIUL<br>eMIOS_1<br>—<br>ADC_0      | I/O<br>I/O<br>—<br>O | М                     | Tristate                      |             | 136         | 164         |

| PH[7]               | PCR[119] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[119]<br>E1UC[9]<br>CS3_2<br>MA[1]  | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC_0 | I/O<br>I/O<br>O      | М                     | Tristate                      | 1           | 137         | 165         |

| PH[8]               | PCR[120] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[120]<br>E1UC[10]<br>CS2_2<br>MA[0] | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC_0 | I/O<br>I/O<br>O      | М                     | Tristate                      |             | 138         | 166         |

| PH[9] <sup>8</sup>  | PCR[121] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[121]<br>—<br>TCK<br>—              | SIUL<br>—<br>JTAGC<br>—            | I/O<br>—<br>I<br>—   | S                     | Input,<br>weak<br>pull-up     | 88          | 127         | 155         |

| PH[10] <sup>8</sup> | PCR[122] | AF0<br>AF1<br>AF2<br>AF3 | GPIO[122]<br>—<br>TMS<br>—              | SIUL<br>—<br>JTAGC<br>—            | I/O<br>—<br>I<br>—   | М                     | Input,<br>weak<br>pull-up     | 81          | 120         | 148         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                     |                                                               | eral                                   | lon                       | pe <sup>2</sup>       | F::6                          | P           | in numb     | er          |

|--------|----------|-------------------------------|---------------------------------------------------------------|----------------------------------------|---------------------------|-----------------------|-------------------------------|-------------|-------------|-------------|

| pin    |          | function <sup>1</sup>         | Function                                                      | Peripheral                             | I/O<br>direction          | Pad type <sup>2</sup> | RESET<br>config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PH[11] | PCR[123] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[123]<br>SOUT_3<br>CS0_4<br>E1UC[5]                       | SIUL<br>DSPI_3<br>DSPI_4<br>eMIOS_1    | I/O<br>O<br>I/O<br>I/O    | М                     | Tristate                      | _           | _           | 140         |

| PH[12] | PCR[124] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[124]<br>SCK_3<br>CS1_4<br>E1UC[25]                       | SIUL<br>DSPI_3<br>DSPI_4<br>eMIOS_1    | I/O<br>I/O<br>I/O         | М                     | Tristate                      | _           | _           | 141         |

| PH[13] | PCR[125] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[125]<br>SOUT_4<br>CS0_3<br>E1UC[26]                      | SIUL<br>DSPI_4<br>DSPI_3<br>eMIOS_1    | I/O<br>O<br>I/O<br>—      | М                     | Tristate                      | _           | _           | 9           |

| PH[14] | PCR[126] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[126]<br>SCK_4<br>CS1_3<br>E1UC[27]                       | SIUL<br>DSPI_4<br>DSPI_3<br>eMIOS_1    | I/O<br>I/O<br>I/O         | М                     | Tristate                      |             | _           | 10          |

| PH[15] | PCR[127] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[127]<br>SOUT_5<br>—<br>E1UC[17]                          | SIUL<br>DSPI_5<br>—<br>eMIOS_1         | I/O<br>O<br>—             | М                     | Tristate                      |             | _           | 8           |

|        |          |                               |                                                               | Port I                                 |                           |                       |                               |             | l           |             |

| PI[0]  | PCR[128] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[128]<br>E0UC[28]<br>—<br>—                               | SIUL<br>eMIOS_0<br>—                   | I/O<br>I/O<br>—           | S                     | Tristate                      | _           | _           | 172         |

| PI[1]  | PCR[129] | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[129]<br>E0UC[29]<br>—<br>—<br>WKUP[24] <sup>4</sup><br>— | SIUL<br>eMIOS_0<br>—<br>—<br>WKUP      | I/O<br>I/O<br>—<br>—<br>— | S                     | Tristate                      | _           | _           | 171         |

| PI[2]  | PCR[130] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[130]<br>E0UC[30]<br>—<br>—                               | SIUL<br>eMIOS_0<br>—                   | I/O<br>I/O<br>—           | S                     | Tristate                      | _           | _           | 170         |

| PI[3]  | PCR[131] | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[131]<br>E0UC[31]<br>—<br>—<br>WKUP[23] <sup>4</sup><br>— | SIUL<br>eMIOS_0<br>—<br>—<br>WKUP<br>— | I/O<br>I/O<br>—<br>—<br>— | S                     | Tristate                      | _           | _           | 169         |

| PI[4]  | PCR[132] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[132]<br>E1UC[28]<br>SOUT_4<br>—                          | SIUL<br>eMIOS_1<br>DSPI_4<br>—         | I/O<br>I/O<br>O           | S                     | Tristate                      | _           | _           | 143         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                     |                                             | eral                              | uo                        | pe <sup>2</sup>       | L. Ex                      | Pi          | in numb     | er          |

|--------|----------|-------------------------------|---------------------------------------------|-----------------------------------|---------------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    |          | function <sup>1</sup>         | Function                                    | Peripheral                        | I/O<br>direction          | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PI[5]  | PCR[133] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[133]<br>E1UC[29]<br>SCK_4<br>—         | SIUL<br>eMIOS_1<br>DSPI_4<br>—    | I/O<br>I/O<br>I/O         | S                     | Tristate                   | _           | _           | 142         |

| PI[6]  | PCR[134] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[134]<br>E1UC[30]<br>CS0_4<br>—         | SIUL<br>eMIOS_1<br>DSPI_4<br>—    | I/O<br>I/O<br>I/O         | S                     | Tristate                   | -           | _           | 11          |

| PI[7]  | PCR[135] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[135]<br>E1UC[31]<br>CS1_4<br>—         | SIUL<br>eMIOS_1<br>DSPI_4<br>—    | I/O<br>I/O<br>I/O         | S                     | Tristate                   | _           | _           | 12          |

| PI[8]  | PCR[136] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[136]<br>—<br>—<br>—<br>—<br>ADC0_S[16] | SIUL  ADC_0                       | I/O<br>—<br>—<br>—<br>I   | J                     | Tristate                   | _           | _           | 108         |

| PI[9]  | PCR[137] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[137]<br>—<br>—<br>—<br>—<br>ADC0_S[17] | SIUL  ADC_0                       | I/O<br>—<br>—<br>—<br>I   | J                     | Tristate                   | _           | _           | 109         |

| PI[10] | PCR[138] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[138]<br>—<br>—<br>—<br>—<br>ADC0_S[18] | SIUL  ADC_0                       | I/O<br>—<br>—<br>—<br>I   | J                     | Tristate                   | _           | _           | 110         |

| PI[11] | PCR[139] | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[139]<br><br><br>ADC0_S[19]<br>SIN_3    | SIUL  ADC_0 DSPI_3                | I/O<br>—<br>—<br>—<br>I   | J                     | Tristate                   |             | _           | 111         |

| PI[12] | PCR[140] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[140]<br>CS0_3<br>—<br>—<br>ADC0_S[20]  | SIUL<br>DSPI_3<br>—<br>—<br>ADC_0 | I/O<br>I/O<br>—<br>—<br>I | J                     | Tristate                   | _           | _           | 112         |

| PI[13] | PCR[141] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[141]<br>CS1_3<br>—<br>—<br>ADC0_S[21]  | SIUL<br>DSPI_3<br>—<br>—<br>ADC_0 | I/O<br>I/O<br>—<br>—<br>I | J                     | Tristate                   | _           | _           | 113         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate             |                 | eral       | uo               | pe <sup>2</sup>       | ET.                        | Pi          | in numb     | er          |

|--------|----------|-----------------------|-----------------|------------|------------------|-----------------------|----------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup> | Function        | Peripheral | I/O<br>direction | Pad type <sup>2</sup> | RESET config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PI[14] | PCR[142] |                       | GPIO[142]       | SIUL       | I/O              | J                     | Tristate                   | -           | _           | 76          |

|        |          | AF1                   | _               | _          | _                |                       |                            |             |             |             |

|        |          | AF2<br>AF3            | _               | _          | _                |                       |                            |             |             |             |

|        |          | —<br>—                | <br>ADC0_S[22]  | ADC_0      | _<br>            |                       |                            |             |             |             |

|        |          | _                     | SIN_4           | DSPI_4     | i                |                       |                            |             |             |             |

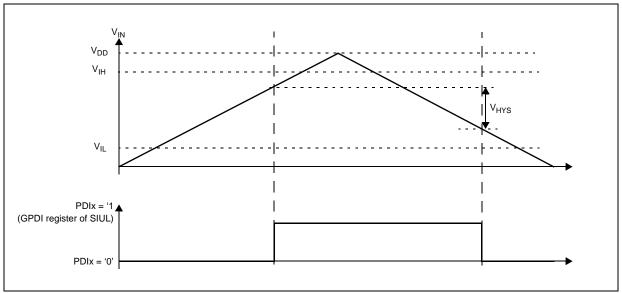

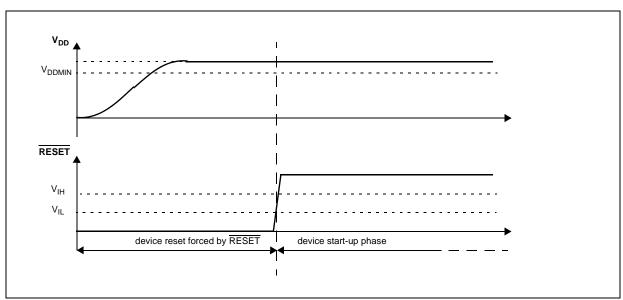

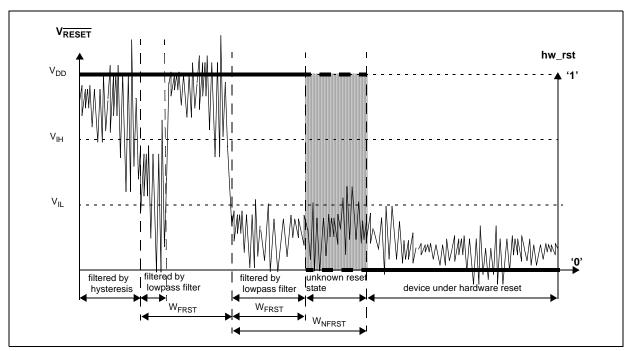

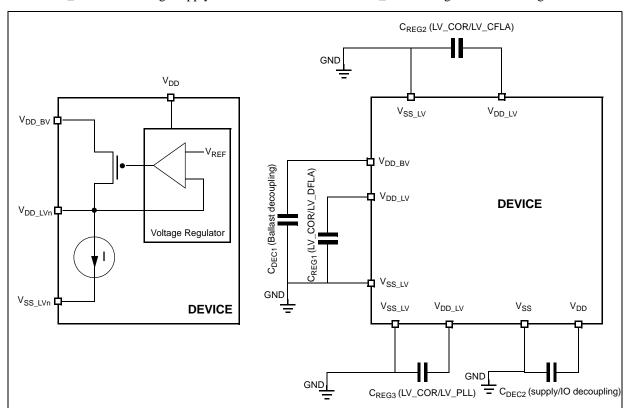

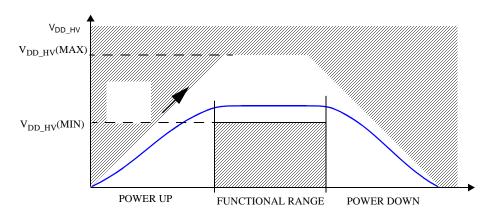

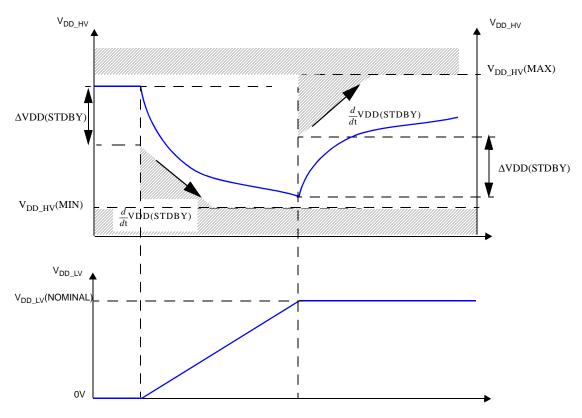

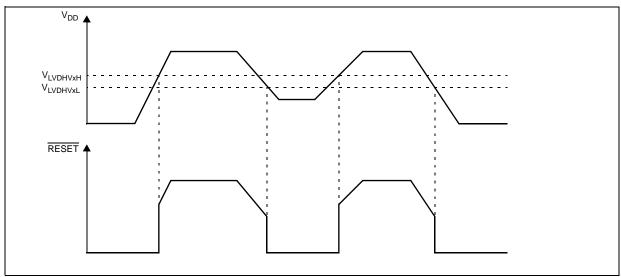

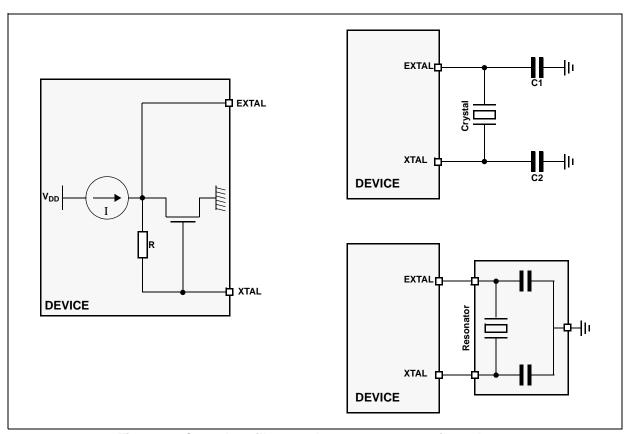

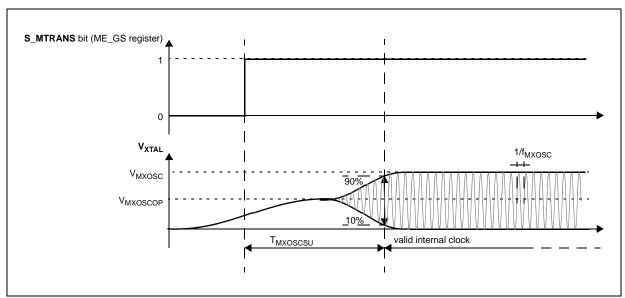

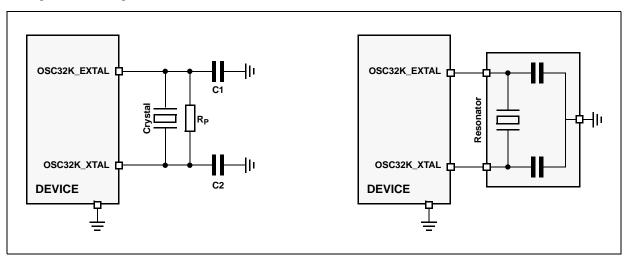

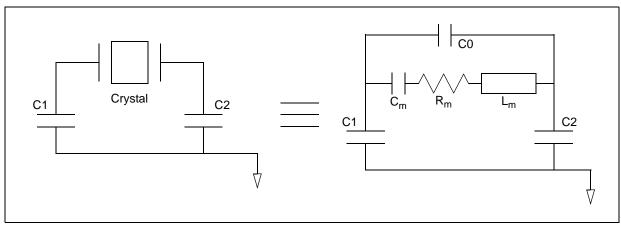

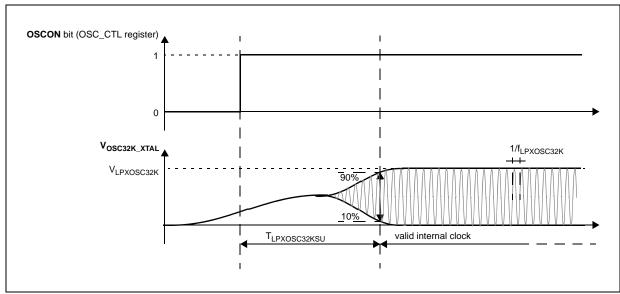

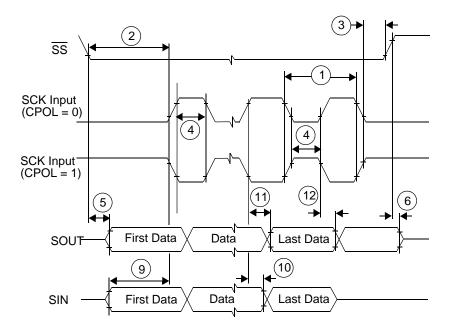

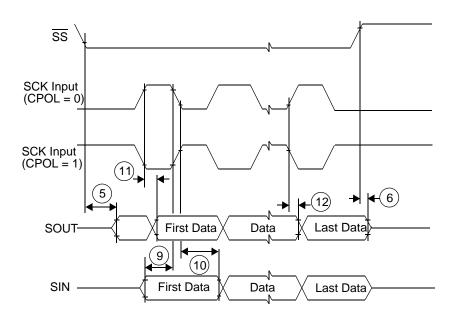

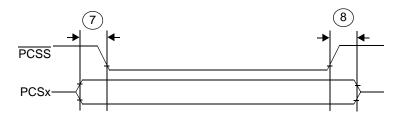

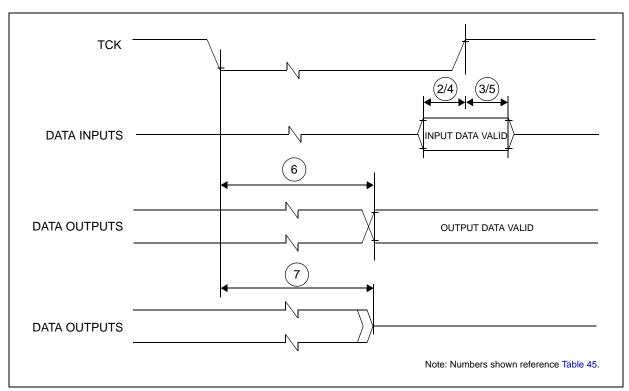

| PI[15] | PCR[143] | AF0                   | GPIO[143]       | SIUL       | I/O              | J                     | Tristate                   | _           | _           | 75          |