# 1 Orderable parts

The 33912G5 data sheet is within MC33912G5 product specifications, Pages 3 to 52 The 33912BAC data sheet is within MC33912BAC product specifications, Pages 53 to 103

### Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package | Generation | Changes                                                                                                                                                                              |

|----------------------------|-------------------------------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC33912G5AC                | -40 to 125 °C                 | _       |            | <ol> <li>Increase ESD Gun IEC61000-4-2 (gun test contact with 150 pF,<br/>330 ohm test conditions) performance to achieve ±6.0 kV min on the<br/>LIN pin.</li> </ol>                 |

| MC34912G5AC                | -40 to 85 °C                  | 32-LQFP | 2.5        | <ol> <li>Immunity against ISO7637 pulse 3b</li> <li>Reduce EMC emission level on LIN</li> <li>Improve EMC immunity against RF - target new specification including 3x68pF</li> </ol> |

| MC33912BAC                 | -40 to 125 °C                 | -       |            | 5. Comply with J2602 conformance test                                                                                                                                                |

| MC34912BAC                 | -40 to 85 °C                  | -       | 2.0        | Initial release                                                                                                                                                                      |

Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

2 MC33912G5 product specifications, Pages 3 to 52

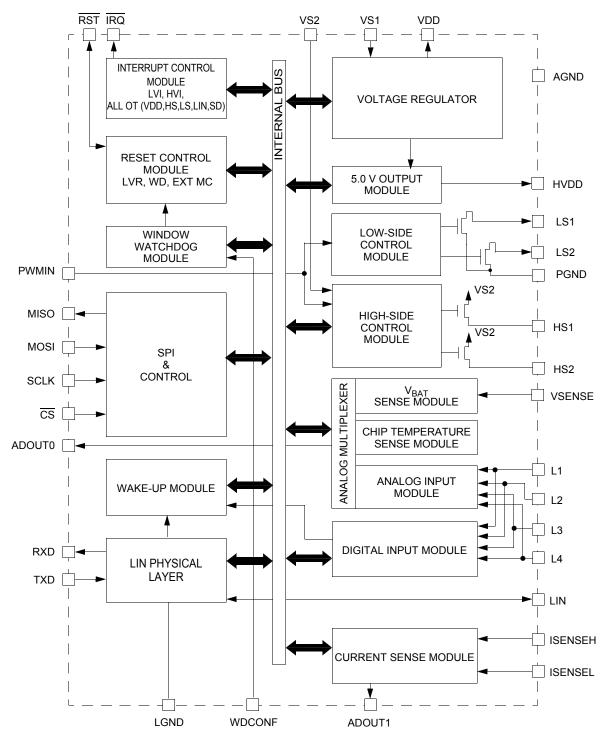

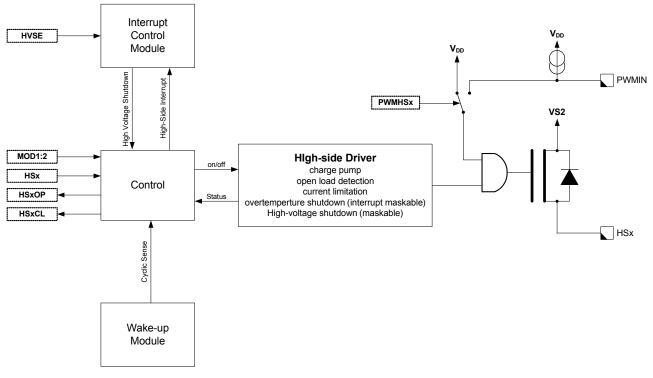

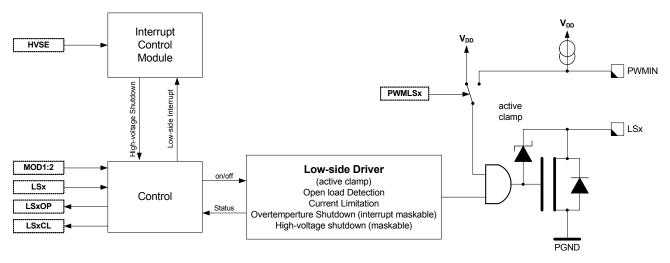

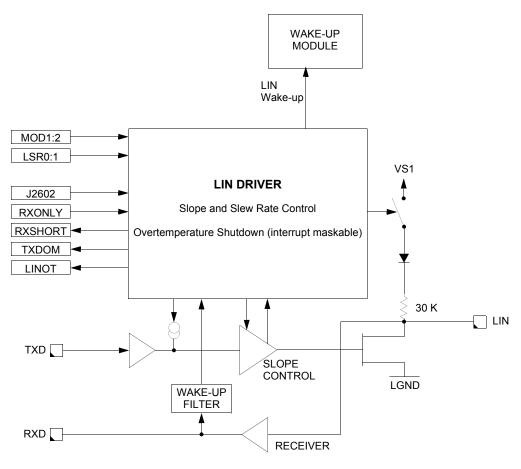

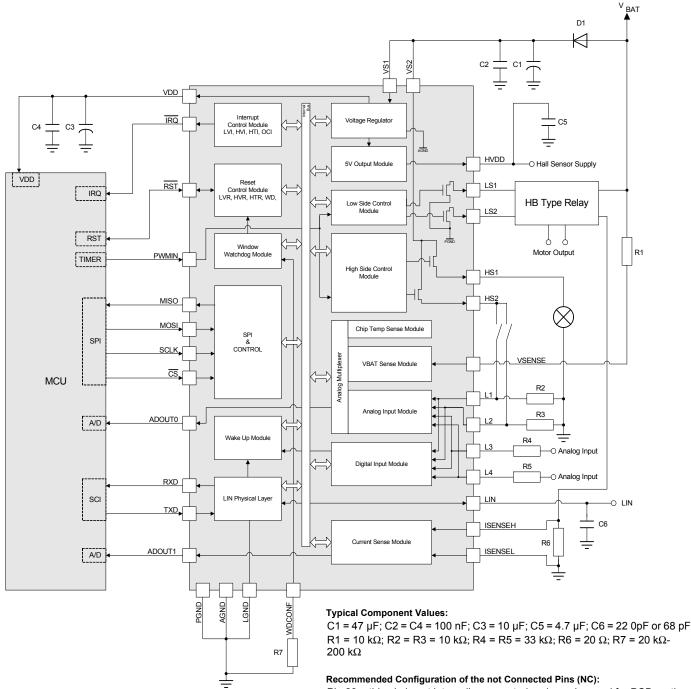

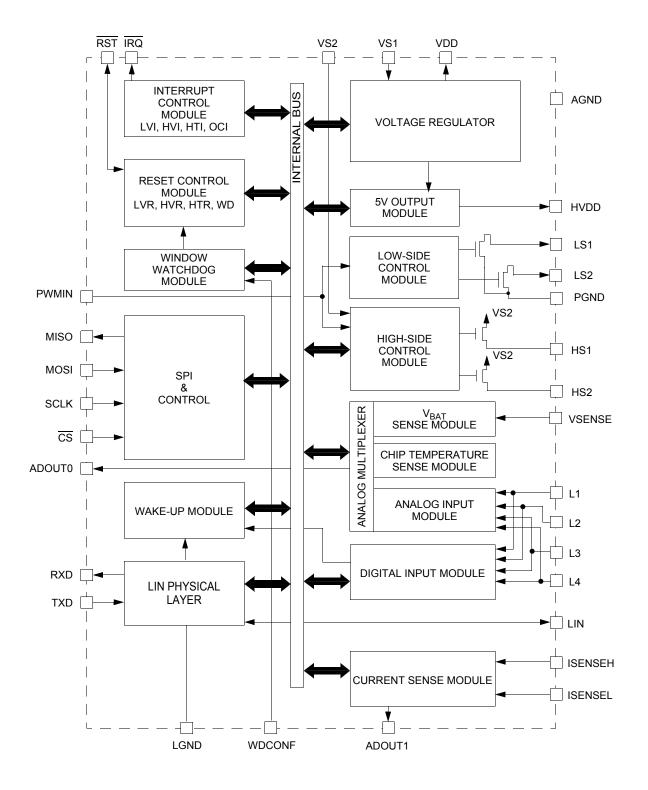

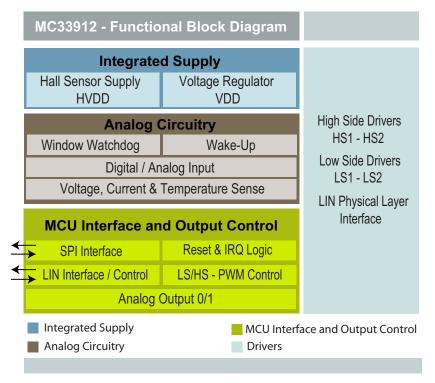

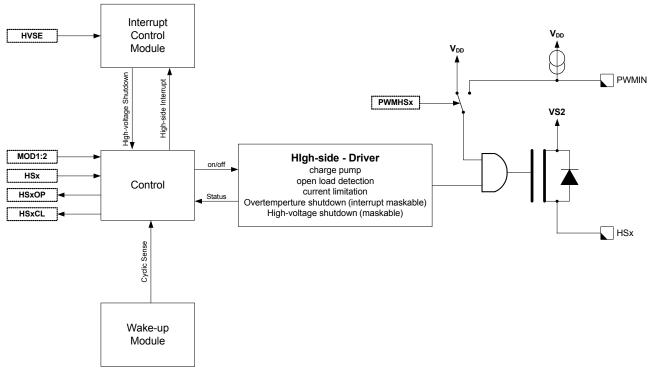

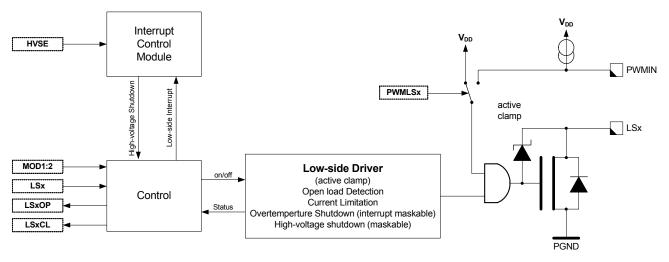

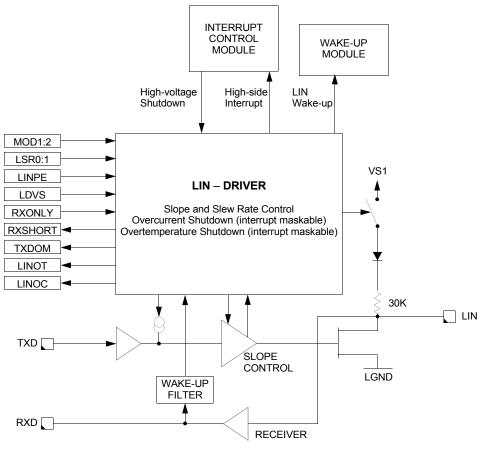

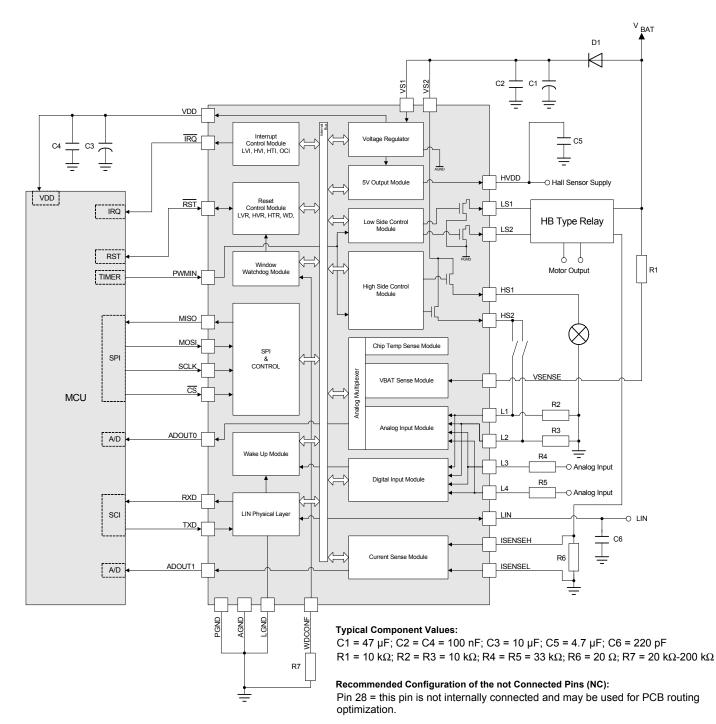

# 3 Internal block diagram

Figure 2. 33912 simplified internal block diagram

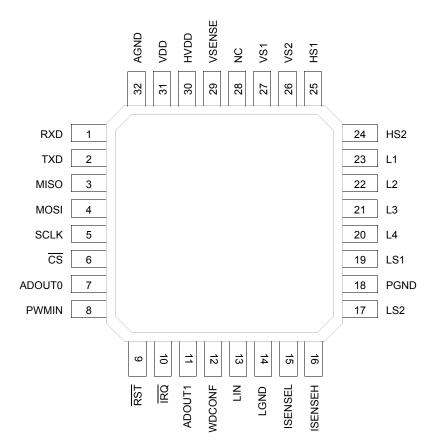

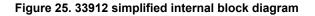

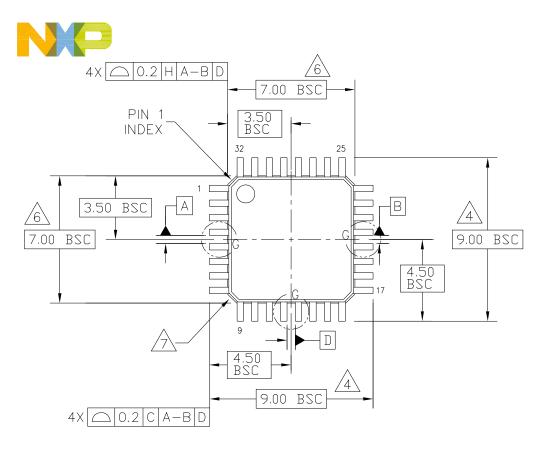

# 4 Pin connections

# 4.1 Pinout diagram

A functional description of each pin can be found in the Functional pin description section beginning on page 23.

### Table 2. 33912 pin definitions

| Pin | Pin name | Formal name         | Definition                                                                                                              |

|-----|----------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1   | RXD      | Receiver Output     | This pin is the receiver output of the LIN interface which reports the state of the bus voltage to the MCU interface.   |

| 2   | TXD      | Transmitter Input   | This pin is the transmitter input of the LIN interface which controls the state of the bus output.                      |

| 3   | MISO     | SPI Output          | SPI (Serial Peripheral Interface) data output. When $\overline{\text{CS}}$ is high, pin is in the high-impedance state. |

| 4   | MOSI     | SPI Input           | SPI (Serial Peripheral Interface) data input.                                                                           |

| 5   | SCLK     | SPI Clock           | SPI (Serial Peripheral Interface) clock Input.                                                                          |

| 6   | CS       | SPI Chip Select     | SPI (Serial Peripheral Interface) chip select input pin. $\overline{CS}$ is active low.                                 |

| 7   | ADOUT0   | Analog Output Pin 0 | Analog Multiplexer Output.                                                                                              |

| 8   | PWMIN    | PWM Input           | High-side and Low-side Pulse Width Modulation Input.                                                                    |

| 9   | RST      | Internal Reset I/O  | Bidirectional Reset I/O pin - driven low when any internal reset source is asserted. RST is active low.                 |

### Table 2. 33912 pin definitions (continued)

| Pin                  | Pin name             | Formal name                   | Definition                                                                                                                                     |

|----------------------|----------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                   | IRQ                  | Internal Interrupt<br>Output  | Interrupt output pin, indicating wake-up events from Stop mode or events from Normal and Normal request modes. IRQ is active low.              |

| 11                   | ADOUT1               | Analog Output Pin 1           | Current sense analog output.                                                                                                                   |

| 12                   | WDCONF               | Watchdog<br>Configuration Pin | This input pin is for configuration of the watchdog period and allows the disabling of the watchdog.                                           |

| 13                   | LIN                  | LIN Bus                       | This pin represents the single-wire bus transmitter and receiver.                                                                              |

| 14                   | LGND                 | LIN Ground Pin                | This pin is the device LIN ground connection. It is internally connected to the PGND pin.                                                      |

| 15<br>16             | ISENSEL<br>ISENSEH   | Current Sense Pins            | Current Sense differential inputs.                                                                                                             |

| 17<br>19             | LS2<br>LS1           | Low-side Outputs              | Relay drivers low-side outputs.                                                                                                                |

| 18                   | PGND                 | Power Ground Pin              | This pin is the device low-side ground connection. It is internally connected to the LGND pin.                                                 |

| 20<br>21<br>22<br>23 | L4<br>L3<br>L2<br>L1 | Wake-up Inputs                | These pins are the wake-up capable digital inputs <sup>(2)</sup> . In addition, all Lx inputs can be sensed analog via the analog multiplexer. |

| 24<br>25             | HS2<br>HS1           | High-side Outputs             | High-side switch outputs.                                                                                                                      |

| 26<br>27             | VS2<br>VS1           | Power Supply Pin              | These pins are device battery level power supply pins. VS2 is supplying the HSx drivers while VS1 supplies the remaining blocks. $^{(3)}$      |

| 28                   | NC                   | Not Connected                 | This pin can be left open or connected to any potential ground or power supply.                                                                |

| 29                   | VSENSE               | Voltage Sense Pin             | Battery voltage sense input. <sup>(4)</sup>                                                                                                    |

| 30                   | HVDD                 | Hall Sensor Supply<br>Output  | +5.0 V switchable supply output pin. <sup>(5)</sup>                                                                                            |

| 31                   | VDD                  | Voltage Regulator<br>Output   | +5.0 V main voltage regulator output pin. <sup>(6)</sup>                                                                                       |

| 32                   | AGND                 | Analog Ground Pin             | This pin is the device analog ground connection.                                                                                               |

Notes

2. When used as digital input, a series 33 k $\Omega$  resistor must be used to protect against automotive transients.

3. Reverse battery protection series diodes must be used externally to protect the internal circuitry.

4. This pin can be connected directly to the battery line for voltage measurements. The pin is self protected against reverse battery connections. It is strongly recommended to connect a 10 k $\Omega$  resistor in series with this pin for protection purposes.

- 5. External capacitor (1.0  $\mu$ F < C < 10  $\mu$ F; 0.1  $\Omega$  < ESR < 5.0  $\Omega$ ) required.

- 6. External capacitor (2.0  $\mu$ F < C < 100  $\mu$ F; 0.1  $\Omega$  < ESR < 10  $\Omega$ ) required.

# 5 Electrical characteristics

# 5.1 Maximum ratings

### Table 3. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                       | Ratings                                                                                                                                                                                                       | Value                                      | Unit | Notes      |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------------|

| ectrical ratir                               | ngs                                                                                                                                                                                                           | 1                                          |      |            |

| V <sub>SUP(SS)</sub><br>V <sub>SUP(PK)</sub> | Supply Voltage at VS1 and VS2<br>• Normal Operation (DC)<br>• Transient Conditions (load dump)                                                                                                                | -0.3 to 27<br>-0.3 to 40                   | V    |            |

| $V_{DD}$                                     | Supply Voltage at VDD                                                                                                                                                                                         | -0.3 to 5.5                                | V    |            |

| V <sub>IN</sub><br>V <sub>IN(IRQ)</sub>      | Input / Output Pins Voltage<br>• CS, RST, SCLK, PWMIN, ADOUT0, ADOUT1, MOSI, MISO, TXD, RXD,<br>HVDD<br>• Interrupt Pin (IRQ)                                                                                 | -0.3 to V <sub>DD</sub> +0.3<br>-0.3 to 11 | V    | (7)<br>(8) |

| V <sub>HS</sub>                              | HS1 and HS2 Pin Voltage (DC)                                                                                                                                                                                  | -0.3 to V <sub>SUP</sub> +0.3              | V    |            |

| V <sub>LS</sub>                              | LS1 and LS2 Pin Voltage (DC)                                                                                                                                                                                  | -0.3 to 45                                 | V    |            |

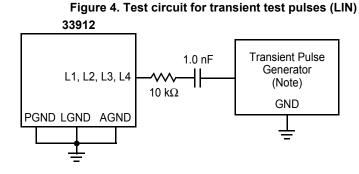

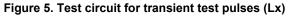

| V <sub>LxDC</sub><br>V <sub>LxTR</sub>       | L1, L2, L3 and L4 Pin Voltage <ul> <li>Normal Operation with a series 33 k resistor (DC)</li> <li>Transient input voltage with external component (according to ISO7637-2) (See Figure 5, page 19)</li> </ul> | -18 to 40<br>±100                          | V    |            |

| VISENSE                                      | ISENSEH and ISENSEL Pin Voltage (DC)                                                                                                                                                                          | -0.3 to 40                                 | V    |            |

| V <sub>VSENSE</sub>                          | VSENSE Pin Voltage (DC)                                                                                                                                                                                       | -27 to 40                                  | V    |            |

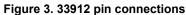

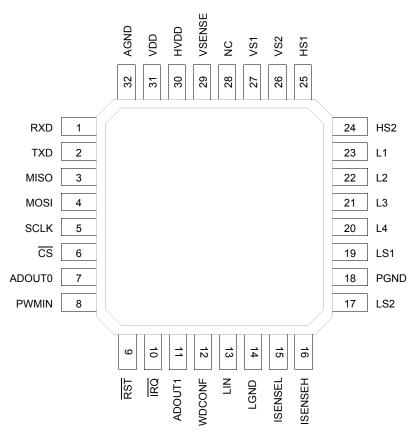

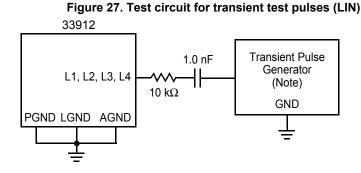

| V <sub>BUSDC</sub><br>V <sub>BUSTR</sub>     | LIN Pin Voltage <ul> <li>Normal Operation (DC)</li> <li>Transient input voltage with external component (according to ISO7637-2) (See Figure 4, page 19)</li> </ul>                                           | -18 to 40<br>-150 to 100                   | V    |            |

| I <sub>VDD</sub>                             | VDD output current                                                                                                                                                                                            | Internally Limited                         | А    |            |

Notes

7. Exceeding voltage limits on specified pins may cause a malfunction or permanent damage to the device.

8. Extended voltage range for programming purpose only.

### Table 3. Maximum ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol              | Ratings                                                                                                                                                               | Value | Unit | Notes |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|

|                     | ESD Capability                                                                                                                                                        |       |      |       |

|                     | • AECQ100                                                                                                                                                             |       |      |       |

|                     | • Human Body Model - JESD22/A114 (C <sub>ZAP</sub> = 100 pF, R <sub>ZAP</sub> = 1500 $\Omega$ )                                                                       |       |      |       |

| V <sub>ESD1-1</sub> | • LIN Pin                                                                                                                                                             | ±8.0k |      |       |

| V <sub>ESD1-2</sub> | • L1, L2, L3, and L4                                                                                                                                                  | ±6.0k |      |       |

| V <sub>ESD1-3</sub> | • all other Pins                                                                                                                                                      | ±2000 |      |       |

|                     | Charge Device Model - JESD22/C101 (C <sub>ZAP</sub> = 4.0 pF)                                                                                                         |       |      |       |

| V <sub>ESD2-1</sub> | • Corner Pins (Pins 1, 8, 9, 16, 17, 24, 25 and 32)                                                                                                                   | ±750  |      |       |

| V <sub>ESD2-2</sub> | • All other Pins (Pins 2-7, 10-15, 18-23, 26-31)                                                                                                                      | ±500  |      |       |

|                     | <ul> <li>According to LIN Conformance Test Specification / LIN EMC Test<br/>Specification, August 2004 (C<sub>7AP</sub> = 150 pF, R<sub>7AP</sub> = 330 Ω)</li> </ul> |       | V    |       |

|                     | Contact Discharge, Unpowered                                                                                                                                          |       | v    |       |

| V <sub>ESD3-1</sub> | LIN pin with 220 pF                                                                                                                                                   | ±20k  |      |       |

| V <sub>ESD3-2</sub> | LIN pin without capacitor                                                                                                                                             | ±11k  |      |       |

| V <sub>ESD3-3</sub> | • VS1/VS2 (100 nF to ground)                                                                                                                                          | >±12k |      |       |

| V <sub>ESD3-4</sub> | • Lx inputs (33 k $\Omega$ serial resistor)                                                                                                                           | ±6000 |      |       |

|                     | • According to IEC 61000-4-2 (C <sub>ZAP</sub> = 150 pF, R <sub>ZAP</sub> = 330 Ω)                                                                                    |       |      |       |

|                     | • Unpowered                                                                                                                                                           |       |      |       |

| V <sub>ESD4-1</sub> | LIN pin with 220 pF and without capacitor                                                                                                                             | ±8000 |      |       |

| V <sub>ESD4-2</sub> | VS1/VS2 (100 nF to ground)                                                                                                                                            | ±8000 |      |       |

| V <sub>ESD4-3</sub> | <ul> <li>Lx inputs (33 kΩ serial resistor)</li> </ul>                                                                                                                 | ±8000 |      |       |

Thermal ratings

| Τ <sub>Α</sub>      | Operating Ambient Temperature<br>33912<br>34912                                                                                       | -40 to 125<br>-40 to 85 | °C   | (9)                    |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------------------------|

| Т <sub>Ј</sub>      | Operating Junction Temperature                                                                                                        | -40 to 150              | °C   |                        |

| T <sub>STG</sub>    | Storage Temperature                                                                                                                   | -55 to 150              | °C   |                        |

| $R_{	hetaJA}$       | Thermal Resistance, Junction to Ambient<br>Natural Convection, Single Layer board (1s)<br>Natural Convection, Four Layer board (2s2p) | 85<br>56                | °C/W | (9), (10)<br>(9), (11) |

| $R_{	ext{	heta}JC}$ | Thermal Resistance, Junction to Case                                                                                                  | 23                      | °C/W | (12)                   |

| T <sub>PPRT</sub>   | Peak Package Reflow Temperature During Reflow                                                                                         | Note 14                 | °C   | (13), (14)             |

Notes

9. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

10. Per JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

11. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

12. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

13. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

14. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to www.NXP.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

# 5.2 Static electrical characteristics

### Table 4. Static electrical characteristics

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                           | Characteristic                                                                                                                                                                                               | Min.      | Тур.            | Max.            | Unit | Notes                  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|-----------------|------|------------------------|

| pply voltage r                                   | ange (VS1, VS2)                                                                                                                                                                                              |           |                 |                 |      |                        |

| V <sub>SUP</sub>                                 | Nominal Operating Voltage                                                                                                                                                                                    | 5.5       | -               | 18              | V    |                        |

| V <sub>SUPOP</sub>                               | Functional Operating Voltage                                                                                                                                                                                 | -         | -               | 27              | V    | (15)                   |

| V <sub>SUPLD</sub>                               | Load Dump                                                                                                                                                                                                    | -         | -               | 40              | V    |                        |

| pply current ra                                  | ange (V <sub>SUP</sub> = 13.5 V)                                                                                                                                                                             |           |                 |                 |      | •                      |

| I <sub>RUN</sub>                                 | Normal Mode ( $I_{OUT}$ at $V_{DD}$ = 10 mA), LIN Recessive State                                                                                                                                            | -         | 4.5             | 10              | mA   | (16)                   |

| I <sub>STOP</sub>                                | Stop Mode, VDD ON with $I_{OUT}$ = 100 µA, LIN Recessive State<br>• 5.5 V < V <sub>SUP</sub> < 12 V<br>• V <sub>SUP</sub> = 13.5 V<br>• 13.5 V < V <sub>SUP</sub> < 18 V                                     |           | 47<br>62<br>180 | 80<br>90<br>400 | μA   | (16), (17<br>(18), (19 |

| I <sub>SLEEP</sub>                               | Sleep Mode, VDD OFF, LIN Recessive State<br>• 5.5 V < $V_{SUP}$ < 12 V<br>• $V_{SUP}$ = 13.5 V<br>• 13.5 V $\leq V_{SUP}$ < 18 V                                                                             |           | 27<br>33<br>160 | 35<br>48<br>300 | μA   | (16), (18              |

| ICYCLIC                                          | Cyclic Sense Supply Current Adder                                                                                                                                                                            | -         | 10              | _               | μA   | (20)                   |

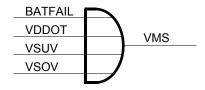

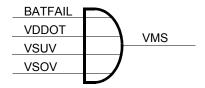

| pply under/ov                                    | ervoltage detections                                                                                                                                                                                         | 1         |                 |                 |      |                        |

| V <sub>BATFAIL</sub><br>V <sub>BATFAIL_HYS</sub> | Power-On Reset (BATFAIL) <ul> <li>Threshold (measured on VS1)</li> <li>Hysteresis (measured on VS1)</li> </ul>                                                                                               | 1.5<br>-  | 3.0<br>0.9      | 3.9<br>-        | V    | (21), (20              |

| V <sub>SUV</sub><br>V <sub>SUV_HYS</sub>         | <ul> <li>V<sub>SUP</sub> Undervoltage Detection (VSUV Flag) (Normal and Normal<br/>Request Modes, Interrupt Generated)</li> <li>Threshold (measured on VS1)</li> <li>Hysteresis (measured on VS1)</li> </ul> | 5.55<br>- | 6.0<br>0.2      | 6.6<br>_        | V    |                        |

| V <sub>SOV</sub><br>V <sub>SOV_HYS</sub>         | V <sub>SUP</sub> Overvoltage Detection (VSOV Flag) (Normal and Normal<br>Request Modes, Interrupt Generated)<br>• Threshold (measured on VS1)<br>• Hysteresis (measured on VS1)                              | 18        | 19.25<br>1.0    | 20.5            | V    |                        |

Notes

15. Device is fully functional. All features are operating.

16. Total current ( $I_{VS1}$  +  $I_{VS2}$ ) measured at GND pins excluding all loads, cyclic sense disabled.

17. Total I<sub>DD</sub> current (including loads) below 100  $\mu$ A.

18. Stop and Sleep Modes current increases if  $V_{SUP}$  exceeds13.5 V.

19. This parameter is guaranteed after 90 ms.

20. This parameter is guaranteed by process monitoring but not production tested.

21. The Flag is set during power up sequence. To clear the flag, a SPI read must be performed.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                  | Characteristic                                                                                                                                                         | Min. | Тур. | Max.     | Unit | Notes |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| tage regulato                           | or <sup>(22)</sup> (VDD)                                                                                                                                               |      |      | •        |      |       |

| V <sub>DDRUN</sub>                      | Normal Mode Output Voltage<br>• 1.0 mA < I <sub>VDD</sub> < 50 mA; 5.5 V < V <sub>SUP</sub> < 27 V                                                                     | 4.75 | 5.00 | 5.25     | V    |       |

| IVDDRUN                                 | Normal Mode Output Current Limitation                                                                                                                                  | 60   | 110  | 200      | mA   |       |

| V <sub>DDDROP</sub>                     | Dropout Voltage<br>• I <sub>VDD</sub> = 50 mA                                                                                                                          | -    | 0.1  | 0.25     | V    | (23)  |

| V <sub>DDSTOP</sub>                     | Stop Mode Output Voltage<br>• I <sub>VDD</sub> < 5.0 mA                                                                                                                | 4.75 | 5.0  | 5.25     | V    |       |

| IVDDSTOP                                | Stop Mode Output Current Limitation                                                                                                                                    | 6.0  | 13   | 36       | mA   |       |

| LR <sub>RUN</sub><br>LR <sub>STOP</sub> | Line Regulation<br>• Normal Mode, 5.5 V < V <sub>SUP</sub> < 18 V; I <sub>VDD</sub> = 10 mA<br>• Stop Mode, 5.5 V < V <sub>SUP</sub> < 18 V; I <sub>VDD</sub> = 1.0 mA |      |      | 25<br>25 | mV   |       |

| LD <sub>RUN</sub><br>LD <sub>STOP</sub> | Load Regulation<br>• Normal Mode, 1.0 mA < I <sub>VDD</sub> < 50 mA<br>• Stop Mode, 0.1 mA < I <sub>VDD</sub> < 5.0 mA                                                 |      |      | 80<br>50 | mV   |       |

| T <sub>PRE</sub>                        | Overtemperature Prewarning (Junction) <ul> <li>Interrupt generated, VDDOT Bit Set</li> </ul>                                                                           | 90   | 115  | 140      | °C   | (24)  |

| T <sub>PRE_HYS</sub>                    | Overtemperature Prewarning Hysteresis                                                                                                                                  | -    | 13   | -        | °C   | (24)  |

| T <sub>SD</sub>                         | Overtemperature Shutdown Temperature (Junction)                                                                                                                        | 150  | 170  | 190      | °C   | (24)  |

| T <sub>SD_HYS</sub>                     | Overtemperature Shutdown Hysteresis                                                                                                                                    | -    | 13   | -        | °C   | (24)  |

Hall sensor supply output <sup>(25)</sup> (HVDD)

| H <sub>VDDACC</sub>  | V <sub>DD</sub> Voltage matching H <sub>VDDACC</sub> = (HVDD-VDD) / VDD * 100%<br>• I <sub>HVDD</sub> = 15 mA | -2.0 | -   | 2.0 | %  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------|------|-----|-----|----|--|

| I <sub>HVDD</sub>    | Current Limitation                                                                                            | 20   | 35  | 50  | mA |  |

| H <sub>VDDDROP</sub> | Dropout Voltage<br>• I <sub>HVDD =</sub> 15 mA; I <sub>VDD</sub> = 5.0 mA                                     | _    | 160 | 300 | mV |  |

| LR <sub>HVDD</sub>   | Line Regulation<br>• I <sub>HVDD</sub> = 5.0 mA; I <sub>VDD</sub> = 5.0 mA                                    | _    | _   | 40  | mV |  |

| LD <sub>HVDD</sub>   | Load Regulation<br>• 1.0 mA > I <sub>HVDD</sub> > 15 mA; I <sub>VDD</sub> = 5.0 mA                            | _    | _   | 20  | mV |  |

Notes

22. Specification with external capacitor 2.0  $\mu$ F < C < 100  $\mu$ F and 100 m $\Omega$  ≤ ESR ≤ 10  $\Omega$ .

23. Measured when voltage has dropped 250 mV below its nominal Value (5.0 V).

24. This parameter is guaranteed by process monitoring but not production tested.

25. Specification with external capacitor 1.0  $\mu$ F < C < 10  $\mu$ F and 100 m $\Omega \le$  ESR  $\le$  10  $\Omega$ .

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol               | Characteristic                                                                              | Min.                  | Тур. | Max.                  | Unit | Note |

|----------------------|---------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|------|

| T input/outpu        | it pin (RST)                                                                                | · · · · ·             |      |                       |      |      |

| VRSTTH               | VDD Low Voltage Reset Threshold                                                             | 4.3                   | 4.5  | 4.7                   | V    |      |

| V <sub>OL</sub>      | Low-state Output Voltage<br>• $I_{OUT}$ = 1.5 mA; 3.5 V $\leq$ V <sub>SUP</sub> $\leq$ 27 V | 0.0                   | -    | 0.9                   | V    |      |

| I <sub>OH</sub>      | High-state Output Current (0 V < V <sub>OUT</sub> < 3.5 V)                                  | -150                  | -250 | -350                  | μA   |      |

| I <sub>PD_MAX</sub>  | Pull-down Current Limitation (internally limited)<br>$V_{OUT} = V_{DD}$                     | 1.5                   | _    | 8.0                   | mA   |      |

| V <sub>IL</sub>      | Low-state Input Voltage                                                                     | -0.3                  | _    | 0.3 x V <sub>DD</sub> | V    |      |

| V <sub>IH</sub>      | High-state Input Voltage                                                                    | 0.7 x V <sub>DD</sub> | _    | V <sub>DD</sub> +0.3  | V    |      |

| SO SPI outpu         | t pin (MISO)                                                                                |                       |      |                       |      | •    |

| V <sub>OL</sub>      | Low-state Output Voltage<br>• I <sub>OUT</sub> = 1.5 mA                                     | 0.0                   | _    | 1.0                   | V    |      |

| V <sub>OH</sub>      | High-state Output Voltage<br>• I <sub>OUT</sub> = -250 μA                                   | V <sub>DD</sub> -0.9  | _    | V <sub>DD</sub>       | V    |      |

| I <sub>TRIMISO</sub> | Tri-state Leakage Current<br>• 0 V $\leq$ V <sub>MISO</sub> $\leq$ V <sub>DD</sub>          | -10                   | _    | 10                    | μA   |      |

| l input pins (I      | NOSI, SCLK, CS)                                                                             |                       |      |                       |      |      |

| V <sub>IL</sub>      | Low-state Input Voltage                                                                     | -0.3                  | _    | 0.3 x V <sub>DD</sub> | V    |      |

| V <sub>IH</sub>      | High-state Input Voltage                                                                    | 0.7 x V <sub>DD</sub> | _    | V <sub>DD</sub> +0.3  | V    |      |

| I <sub>IN</sub>      | MOSI, SCLK Input Current<br>• $0 V \le V_{IN} \le V_{DD}$                                   | -10                   | _    | 10                    | μA   |      |

| I <sub>PUCS</sub>    | $\frac{\overline{\text{CS}}}{\bullet 0} \text{ V} < \text{V}_{\text{IN}} < 3.5 \text{ V}$   | 10                    | 20   | 30                    | μA   |      |

| terrupt output       | t pin (IRQ)                                                                                 |                       |      |                       |      |      |

| V <sub>OL</sub>      | Low-state Output Voltage<br>• I <sub>OUT</sub> = 1.5 mA                                     | 0.0                   | _    | 0.8                   | V    |      |

| V <sub>OH</sub>      | High-state Output Voltage<br>• I <sub>OUT</sub> = -250 μA                                   | V <sub>DD</sub> -0.8  | _    | V <sub>DD</sub>       | V    |      |

| I <sub>OUT</sub>     | Leakage Current<br>• $V_{DD} \le V_{OUT} \le 10 \text{ V}$                                  | -                     | _    | 2.0                   | mA   |      |

| lse width mod        | dulation input pin (PWMIN)                                                                  | I                     |      | 1 1                   |      |      |

| V <sub>IL</sub>      | Low-state Input Voltage                                                                     | -0.3                  | _    | 0.3 x V <sub>DD</sub> | V    |      |

| V <sub>IH</sub>      | High-state Input Voltage                                                                    | 0.7 x V <sub>DD</sub> | _    | V <sub>DD</sub> +0.3  | V    | 1    |

| I <sub>PUPWMIN</sub> | Pull-up current<br>• 0 V < V <sub>IN</sub> < 3.5 V                                          | 10                    | 20   | 30                    | μA   |      |

|                      |                                                                                             |                       |      | 1                     |      | 1    |

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                | Characteristic                                                                   | Min.                  | Тур.        | Max.            | Unit | Notes     |

|-----------------------|----------------------------------------------------------------------------------|-----------------------|-------------|-----------------|------|-----------|

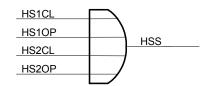

| igh-side output       | ts HS1 and HS2 Pins (HS1, HS2)                                                   |                       |             |                 |      | •         |

| R <sub>DS(on)</sub>   |                                                                                  |                       | -<br>-<br>- | 7.0<br>10<br>14 | Ω    | (26)      |

| I <sub>LIMHSX</sub>   | Output Current Limitation<br>• 0 V < V <sub>OUT</sub> < V <sub>SUP</sub> - 2.0 V | 60                    | 90          | 250             | mA   | (27)      |

| I <sub>OLHSX</sub>    | Open Load Current Detection                                                      | -                     | 5.0         | 7.5             | mA   | (28)      |

| I <sub>LEAK</sub>     | Leakage Current<br>• -0.2 V < V <sub>HSX</sub> < V <sub>S2</sub> + 0.2 V         | -                     | -           | 10              | μΑ   |           |

| V <sub>THSC</sub>     | Short-circuit Detection Threshold<br>• 5.5 V < V <sub>SUP</sub> < 27 V           | V <sub>SUP</sub> -2.0 | -           | _               | V    | (29)      |

| T <sub>HSSD</sub>     | Overtemperature Shutdown                                                         | 140                   | 160         | 180             | °C   | (30), (34 |

| T <sub>HSSD_HYS</sub> | Overtemperature Shutdown Hysteresis                                              | -                     | 10          | -               | °C   | (34)      |

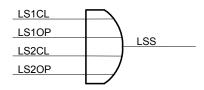

| R <sub>DS(on)</sub>   | Output Drain-to-Source On Resistance         • $T_J = 25 \degree C$ , $I_{LOAD} = 150 \ mA$ , $V_{SUP} > 9.0 \ V$ • $T_J = 125 \degree C$ , $I_{LOAD} = 150 \ mA$ , $V_{SUP} > 9.0 \ V$ • $T_J = 125 \degree C$ , $I_{LOAD} = 120 \ mA$ , $5.5 \ V < V_{SUP} < 9.0 \ V$ |                       |     | 2.5<br>4.5<br>10      | Ω  |            |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|----|------------|

| I <sub>LIMLSX</sub>   | Output Current Limitation<br>• 2.0 V < V <sub>OUT</sub> < V <sub>SUP</sub>                                                                                                                                                                                              | 160                   | 275 | 350                   | mA | (31)       |

| I <sub>OLLSX</sub>    | Open Load Current Detection                                                                                                                                                                                                                                             | -                     | 7.5 | 12                    | mA | (32)       |

| I <sub>LEAK</sub>     | Leakage Current<br>• -0.2 V < V <sub>OUT</sub> < VS1                                                                                                                                                                                                                    | -                     | -   | 10                    | μA |            |

| V <sub>CLAMP</sub>    | Active Output Energy Clamp<br>• I <sub>OUT</sub> = 150 mA                                                                                                                                                                                                               | V <sub>SUP</sub> +2.0 | -   | V <sub>SUP</sub> +5.0 | V  |            |

| V <sub>THSC</sub>     | Short-circuit Detection Threshold<br>• 5.5 V < V <sub>SUP</sub> < 27 V                                                                                                                                                                                                  | 2.0                   | -   | -                     | V  | (29)       |

| T <sub>LSSD</sub>     | Overtemperature Shutdown                                                                                                                                                                                                                                                | 140                   | 160 | 180                   | °C | (33), (34) |

| T <sub>LSSD_HYS</sub> | Overtemperature Shutdown Hysteresis                                                                                                                                                                                                                                     | -                     | 10  | -                     | °C |            |

Notes

26. This parameter is production tested up to  $T_A$  = 125 °C, and guaranteed by process monitoring up to  $T_J$  = 150 °C.

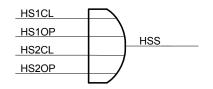

27. When overcurrent occurs, the corresponding high-side stays ON with limited current capability and the HSxCL flag is set in the HSSR.

28. When open load occurs, the flag (HSxOP) is set in the HSSR.

29. HS and LS automatically shutdown if HSOT or LSOT occurs or if the HVSE flag is enabled and an overvoltage occurs.

30. When overtemperature shutdown occurs, both high-sides are turned off. All flags in HSSR are set.

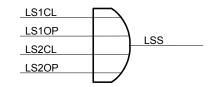

31. When overcurrent occurs, the corresponding low-side stays ON with limited current capability and the LSxCL flag is set in the LSSR.

32. When open load occurs, the flag (LSxOP) is set in the LSSR.

33. When overtemperature shutdown occurs, both low-sides are turned off. All flags in LSSR are set.

34. Guaranteed by characterization but not production tested

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                      | Characteristic                                                                                                                                                | Min.              | Тур.          | Max.              | Unit | Notes |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|-------------------|------|-------|

| L1, L2, L3 and L4           | input pins (L1, L2, L3, L4)                                                                                                                                   |                   |               |                   |      |       |

| V <sub>THL</sub>            | Low Detection Threshold<br>• 5.5 V < V <sub>SUP</sub> < 27 V                                                                                                  | 2.0               | 2.5           | 3.0               | V    | (35)  |

| V <sub>THH</sub>            | High Detection Threshold<br>• 5.5 V < V <sub>SUP</sub> < 27 V                                                                                                 | 3.0               | 3.5           | 4.0               | V    | (35)  |

| V <sub>HYS</sub>            | Hysteresis<br>• 5.5 V < V <sub>SUP</sub> < 27 V                                                                                                               | 0.4               | 0.8           | 1.4               | V    | (35)  |

| I <sub>IN</sub>             | Input Current<br>• -0.2 V < V <sub>IN</sub> < VS1                                                                                                             | -10               | _             | 10                | μA   | (36)  |

| R <sub>LXIN</sub>           | Analog Input Impedance                                                                                                                                        | 2000              | kΩ            | (37)              |      |       |

| RATIO <sub>LX</sub>         | Analog Input Divider Ratio (RATIO <sub>Lx</sub> = V <sub>Lx</sub> / V <sub>ADOUT0</sub> )<br>• LXDS (Lx Divider Select) = 0<br>• LXDS (Lx Divider Select) = 1 | 0.95<br>3.42      | 1.0<br>3.6    | 1.05<br>3.78      |      |       |

| V <sub>RATIOLx-OFFSET</sub> | Analog Output offset Ratio<br>• LXDS (Lx Divider Select) = 0<br>• LXDS (Lx Divider Select) = 1                                                                | -80<br>-22        | 6.0<br>2.0    | 80<br>22          | mV   |       |

| LX <sub>MATCHING</sub>      | Analog Inputs Matching<br>• LXDS (Lx Divider Select) = 0<br>• LXDS (Lx Divider Select) = 1                                                                    | 96<br>96          | 100<br>100    | 104<br>104        | %    |       |

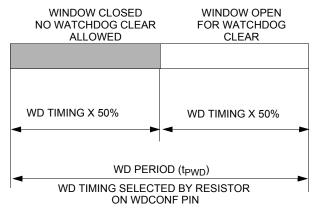

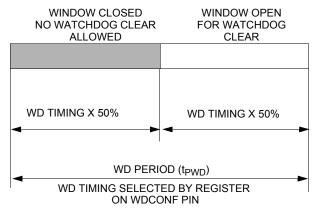

| Window watchdog             | g configuration pin (WDCONF) <sup>(38)</sup>                                                                                                                  |                   |               | L                 |      |       |

| R <sub>EXT</sub>            | External Resistor Range                                                                                                                                       | 20                | _             | 200               | kΩ   |       |

| WD <sub>ACC</sub>           | Watchdog Period Accuracy with External Resistor (Excluding Resistor Accuracy)                                                                                 | -15               | -             | 15                | %    | (39)  |

| Analog multiplexe           | r                                                                                                                                                             |                   |               |                   |      |       |

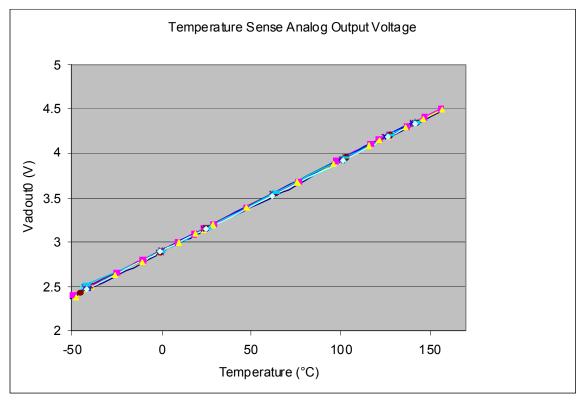

| Vadout0_temp                | Temperature Sense Analog Output Voltage<br>• $T_A = -40 \text{ °C}$<br>• $T_A = 25 \text{ °C}$<br>• $T_A = 125 \text{ °C}$                                    | 2.0<br>2.8<br>3.6 | -<br>3.0<br>- | 2.8<br>3.6<br>4.6 | V    |       |

| V <sub>ADOUT0_25</sub>      | Temperature Sense Analog Output Voltage per characterization<br>$\bullet$ T <sub>A</sub> = 25 °C                                                              | 3.1               | 3.15          | 3.2               | V    | (40)  |

| S <sub>TTOV</sub>           | Internal Chip Temperature Sense Gain                                                                                                                          | 9.0               | 10.5          | 12                | mV/K |       |

| S <sub>TTOV_3T</sub>        | Internal Chip Temperature Sense Gain per characterization at 3 temperatures. See Figure 16. Temperature sense gain                                            | 9.9               | 10.2          | 10.5              | mV/K | (40)  |

| RATIO <sub>VSENSE</sub>     | VSENSE Input Divider Ratio (RATIO <sub>VSENSE</sub> = V <sub>VSENSE</sub> / V <sub>ADOUT0</sub> )<br>• 5.5 V < V <sub>SUP</sub> < 27 V                        | 5.0               | 5.25          | 5.5               |      |       |

| RATIO <sub>VSENSECZ</sub>   | VSENSE Input Divider Ratio (RATIOVSENSE=V <sub>SENSE</sub> /V <sub>ADOUT0</sub> ) per<br>characterization<br>• 5.5 <v<sub>SUP&lt; 27 V</v<sub>                | 5.15              | 5.25          | 5.35              |      | (40)  |

Notes

35. The unused Lx pins must be connected to ground.

36. Analog multiplexer input disconnected from Lx input pin.

37. Analog multiplexer input connected to Lx input pin.

38. For  $V_{SUP}$  4.7 V to 18 V

39. Watchdog timing period calculation formula:  $t_{PWD}$  [ms] = [0.466 \* (R<sub>EXT</sub> - 20)] + 10 with (R<sub>EXT</sub> in k $\Omega$ )

40. These limits have been defined after laboratory characterization on 3 lots and 30 samples. These tighten limits could not be guaranteed by production test.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                             | Characteristic                                                                                                   | Min.                  | Тур.       | Max.                  | Unit | Notes |

|------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------|------------|-----------------------|------|-------|

| Analog multiplexe                  | r (continued)                                                                                                    |                       |            |                       |      |       |

| OFFSET <sub>VSENSE</sub>           | VSENSE Output Related Offset                                                                                     | -30                   | -10        | 30                    | mV   |       |

| OFFSET <sub>VSENSE_C</sub><br>z    | V <sub>SENSE</sub> Output Related Offset per characterization                                                    | -30                   | -12.6      | 0                     | mV   | (41)  |

| Analog outputs (A                  | DOUT0 and ADOUT1)                                                                                                |                       |            |                       |      |       |

| V <sub>OUT_MAX</sub>               | Maximum Output Voltage<br>• -5.0 mA < I <sub>O</sub> < 5.0 mA                                                    | V <sub>DD</sub> -0.35 | _          | V <sub>DD</sub>       | V    |       |

| V <sub>OUT_MIN</sub>               | Minimum Output Voltage<br>• -5.0 mA < I <sub>O</sub> < 5.0 mA                                                    | 0.0                   | _          | 0.35                  | V    |       |

| Current sense am                   | plifier (ISENSEH, ISENSEL)                                                                                       |                       |            |                       |      |       |

| G                                  | Gain                                                                                                             |                       | 30<br>14.5 | 31<br>15              |      |       |

| DIFF                               | Differential Input Impedance<br>• CSGS (Current Sense Gain Select) = 0<br>• CSGS (Current Sense Gain Select) = 1 | 2.0<br>5.0            | 10<br>20   | 30<br>50              | kΩ   |       |

| СМ                                 | Common Mode Input Impedance<br>• CSGS (Current Sense Gain Select) = 0<br>• CSGS (Current Sense Gain Select) = 1  | 100<br>100            |            | 200<br>200            | kΩ   |       |

| V <sub>IN</sub>                    | ISENSEH, ISENSEL Input Voltage Range                                                                             | -0.2                  | _          | 3.0                   | V    |       |

| V <sub>IN_OFFSET</sub>             | Input Offset Voltage<br>• CSAZ (Current Sense Auto Zero) = 0<br>• CSAZ (Current Sense Auto Zero) = 1             | -15<br>-2.0           |            | 15<br>2.0             | mV   |       |

| RxD output pin (Ll                 | N physical layer) (RxD)                                                                                          |                       |            |                       |      | •     |

| V <sub>OL</sub>                    | Low-state Output Voltage<br>• I <sub>OUT</sub> = 1.5 mA                                                          | 0.0                   | _          | 0.8                   | V    |       |

| V <sub>OH</sub>                    | High-state Output Voltage<br>• I <sub>OUT</sub> = -250 μA                                                        | V <sub>DD</sub> -0.8  | _          | V <sub>DD</sub>       | V    |       |

| TXD input pin (LIN                 | l physical layer) (TXD)                                                                                          |                       |            |                       |      |       |

| V <sub>IL</sub>                    | Low-state Input Voltage                                                                                          | -0.3                  | _          | 0.3 x V <sub>DD</sub> | V    |       |

| V <sub>IH</sub>                    | High-state Input Voltage                                                                                         | 0.7 x V <sub>DD</sub> | _          | V <sub>DD</sub> +0.3  | V    |       |

| I <sub>PUIN</sub>                  | Pin Pull-up Current, 0 V < V <sub>IN</sub> < 3.5 V                                                               | 10                    | 20         | 30                    | μΑ   |       |

| LIN physical layer                 | with J2602 feature enabled (bit DIS_J2602 = 0)                                                                   |                       |            |                       |      |       |

| V <sub>TH_UNDER_</sub> VOLTA<br>GE | LIN Undervoltage threshold<br>• Positive and Negative threshold (V <sub>THP</sub> , V <sub>THN</sub> )           | 5.0                   | -          | 6.0                   | V    |       |

| V <sub>J2602_DEG</sub>             | Hysteresis (V <sub>THP</sub> - V <sub>THN</sub> )                                                                | -                     | 400        | -                     | mV   |       |

|                                    |                                                                                                                  |                       |            |                       |      |       |

Notes

41. These limits have been defined after laboratory characterization on 3 lots and 30 samples. These tighten limits could not be guaranteed by production test.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                  | Characteristic                                                                                                                                | Min.  | Тур. | Max.  | Unit             | Notes |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|-------|

| LIN physical laye       | r, transceiver (LIN) <sup>(42)</sup>                                                                                                          |       |      |       |                  |       |

| V <sub>BAT</sub>        | Operating Voltage Range                                                                                                                       | 8.0   | -    | 18    | V                |       |

| V <sub>SUP</sub>        | Supply Voltage Range                                                                                                                          | 7.0   | -    | 18    | V                |       |

| V <sub>SUP_NON_OP</sub> | Voltage Range within which the device is not destroyed                                                                                        | -0.3  | -    | 40    | V                |       |

| I <sub>BUS_LIM</sub>    | Current Limitation for Driver Dominant State<br>• Driver ON, V <sub>BUS</sub> = 18 V                                                          | 40    | 90   | 200   | mA               |       |

| IBUS_PAS_DOM            | Input Leakage Current at the receiver<br>• Driver off; V <sub>BUS</sub> = 0 V; V <sub>BAT</sub> = 12 V                                        | -1.0  | -    | _     | mA               |       |

| IBUS_PAS_REC            | Leakage Output Current to GND<br>• Driver Off; 8.0 V < V <sub>BAT</sub> < 18 V; 8.0 V < V <sub>BUS</sub> < 18 V; V <sub>BUS</sub> ≥ $V_{BAT}$ | _     | -    | 20    | μA               |       |

| I <sub>BUS_NO_GND</sub> | Control unit disconnected from ground<br>• GND <sub>DEVICE</sub> = V <sub>SUP</sub> ; V <sub>BAT</sub> = 12 V; 0 < V <sub>BUS</sub> < 18 V    |       |      | 1.0   | mA               | (43)  |

| I <sub>BUSNO_BAT</sub>  | V <sub>BAT</sub> Disconnected; V <sub>SUP_DEVICE</sub> = GND; 0 V < V <sub>BUS</sub> < 18 V                                                   | _     | -    | 100   | μA               | (44)  |

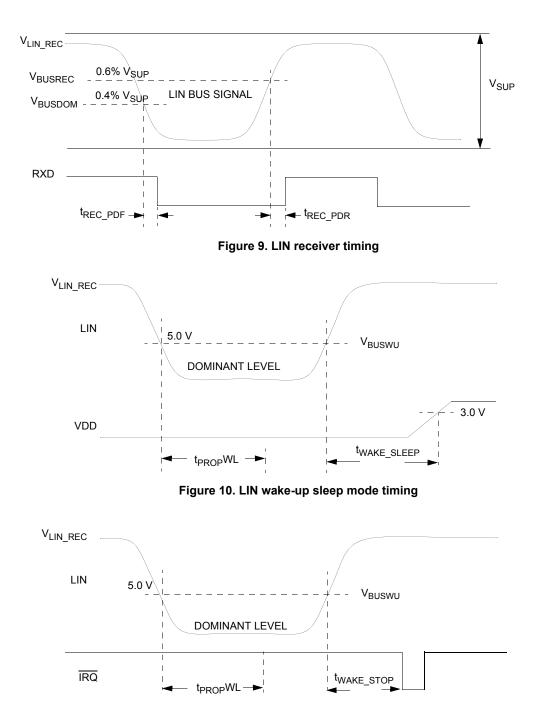

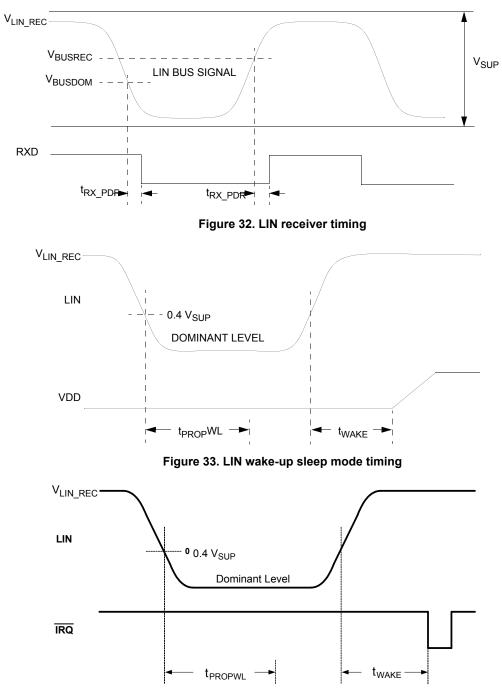

| V <sub>BUSDOM</sub>     | Receiver Dominant State                                                                                                                       | _     | -    | 0.4   | V <sub>SUP</sub> |       |

| V <sub>BUSREC</sub>     | Receiver Recessive State                                                                                                                      | 0.6   | -    | -     | V <sub>SUP</sub> |       |

| V <sub>BUS_CNT</sub>    | Receiver Threshold Center<br>• (V <sub>TH_DOM</sub> + V <sub>TH_REC</sub> )/2                                                                 | 0.475 | 0.5  | 0.525 | V <sub>SUP</sub> |       |

| V <sub>HYS</sub>        | Receiver Threshold Hysteresis<br>• (V <sub>TH_REC</sub> - V <sub>TH_DOM</sub> )                                                               | -     | -    | 0.175 | V <sub>SUP</sub> |       |

| V <sub>SERDIODE</sub>   | Voltage Drop at the serial Diode in pull-up path                                                                                              | 0.4   |      | 1.0   | V                |       |

| V <sub>SHIFT_BAT</sub>  | VBAT_SHIFT                                                                                                                                    | 0     |      | 11.5% | V <sub>BAT</sub> |       |

| V <sub>SHIFT_GND</sub>  | GND_SHIFT                                                                                                                                     | 0     |      | 11.5% | V <sub>BAT</sub> |       |

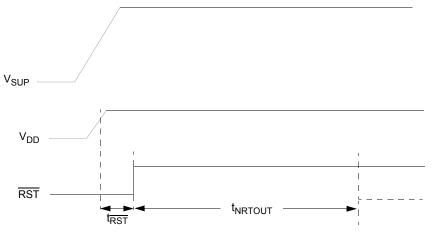

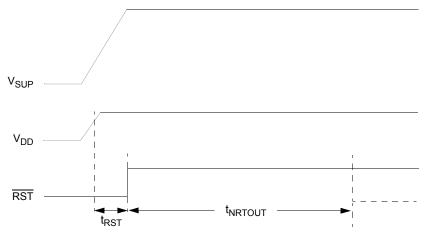

| V <sub>BUSWU</sub>      | LIN Wake-up threshold from Stop or Sleep mode                                                                                                 |       | 5.3  | 5.8   | V                | (45)  |

| R <sub>SLAVE</sub>      | LIN Pull-up Resistor to V <sub>SUP</sub>                                                                                                      | 20    | 30   | 60    | kΩ               |       |

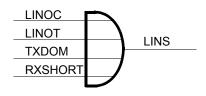

| T <sub>LINSD</sub>      | Overtemperature Shutdown                                                                                                                      | 140   | 160  | 180   | °C               | (46)  |

| T <sub>LINSD_HYS</sub>  | Overtemperature Shutdown Hysteresis                                                                                                           | _     | 10   | -     | °C               |       |

Notes

42. Parameters guaranteed for 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V.

43. Loss of local ground must not affect communication in the residual network.

44. Node has to sustain the current which can flow under this condition. Bus must remain operational under this condition.

45. This parameter is 100% tested on an Automatic Tester. However, since it has not been monitored during reliability stresses, NXP does not guarantee this parameter during the product's life time.

46. When overtemperature shutdown occurs, the LIN bus goes in recessive state and the flag LINOT in LINSR is set.

# 5.3 Dynamic electrical characteristics

### Table 5. Dynamic electrical characteristics

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                  | Characteristic                                                                                                           | Min.       | Тур.            | Max.               | Unit | Notes |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|-----------------|--------------------|------|-------|

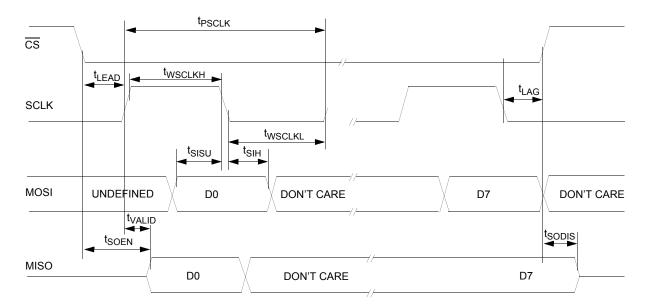

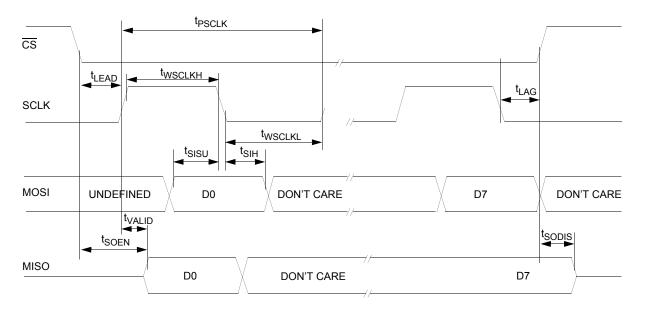

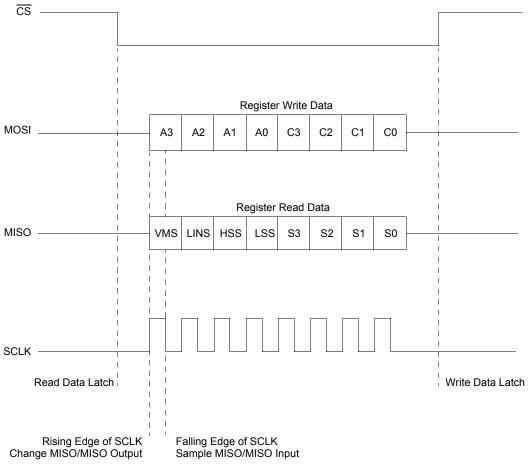

| PI interface tin                        | ning (see <u>Figure 13</u> , page <u>22</u> )                                                                            |            |                 |                    |      | •     |

| f <sub>SPIOP</sub>                      | SPI Operating Frequency                                                                                                  | -          | -               | 4.0                | MHz  |       |

| t <sub>PSCLK</sub>                      | SCLK Clock Period                                                                                                        | 250        | -               | N/A                | ns   |       |

| t <sub>WSCLKH</sub>                     | SCLK Clock High Time                                                                                                     | 110        | -               | N/A                | ns   | (47)  |

| t <sub>WSCLKL</sub>                     | SCLK Clock Low Time                                                                                                      | 110        | -               | N/A                | ns   | (47)  |

| t <sub>LEAD</sub>                       | Falling Edge of $\overline{CS}$ to Rising Edge of SCLK                                                                   | 100        | -               | N/A                | ns   | (47)  |

| t <sub>LAG</sub>                        | Falling Edge of SCLK to CS Rising Edge                                                                                   | 100        | -               | N/A                | ns   | (47)  |

| t <sub>SISU</sub>                       | MOSI to Falling Edge of SCLK                                                                                             | 40         | -               | N/A                | ns   | (47)  |

| t <sub>SIH</sub>                        | Falling Edge of SCLK to MOSI                                                                                             | 40         | -               | N/A                | ns   | (47)  |

| t <sub>RSO</sub>                        | MISO Rise Time<br>• C <sub>L</sub> = 220 pF                                                                              | -          | 40              | _                  | ns   | (47)  |

| t <sub>FSO</sub>                        | MISO Fall Time<br>• $C_L = 220 \text{ pF}$ - 40 -                                                                        |            |                 |                    |      | (47)  |

| <sup>t</sup> soen<br><sup>t</sup> sodis | Time from Falling or Rising Edges of $\overline{\text{CS}}$ to:<br>- MISO Low-impedance<br>- MISO High-impedance         | 0.0<br>0.0 |                 | 50<br>50           | ns   | (47)  |

| t <sub>VALID</sub>                      | Time from Rising Edge of SCLK to MISO Data Valid<br>$\bullet$ 0.2 x V_{DD} $\leq$ MISO $\geq$ 0.8 x V_{DD}, C_L = 100 pF | 0.0        | _               | 75                 | ns   | (47)  |

| ST output pin                           |                                                                                                                          |            | 1               | I                  | 1    |       |

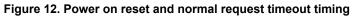

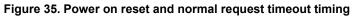

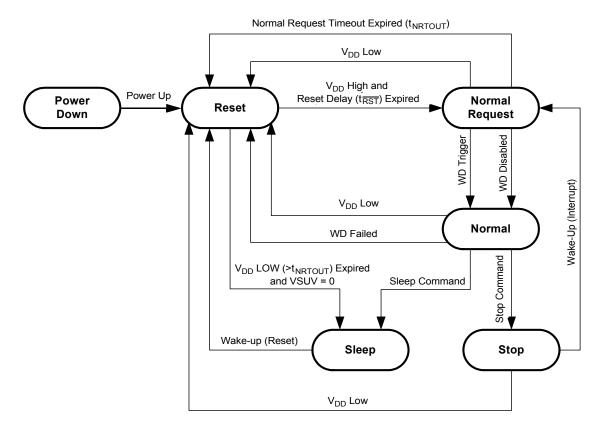

| t <sub>RST</sub>                        | Reset Low-level Duration After V <sub>DD</sub> High (see Figure 12, page 22)                                             | 0.65       | 1.0             | 1.35               | ms   |       |

| t <sub>RSTDF</sub>                      | Reset Deglitch Filter Time                                                                                               | 350        | 480             | 900                | ns   |       |

| indow watchd                            | log configuration pin (WDCONF)                                                                                           |            | 1               |                    |      | 1     |

| t <sub>PWD</sub>                        | Watchdog Time Period<br>• External Resistor R <sub>EXT</sub> = 20 kΩ (1%)                                                |            | 10<br>94<br>150 | 11.5<br>108<br>205 | ms   | (48)  |

| urrent sense a                          | mplifier <sup>(47)</sup>                                                                                                 |            |                 |                    |      |       |

| CMR                                     | Common Mode Rejection Ratio                                                                                              | 70         | -               | -                  | dB   |       |

| SVR                                     | Supply Voltage Rejection Ratio                                                                                           | 60         | _               | _                  | dB   | (49)  |

0.75

0.5

3.0

\_

\_

\_

MHz

V/µs

Notes

GBP

SR

47. This parameter is guaranteed by process monitoring but not production tested.

48. Watchdog timing period calculation formula:  $t_{PWD}$  [ms] = [0.466 \* (R<sub>EXT</sub> - 20)] + 10 with (R<sub>EXT</sub> in k $\Omega$ )

49. Analog Outputs are supplied by  $\rm V_{DD}$  and from 100 Hz to 4.0 kHz

Gain Bandwidth Product

**Output Slew-Rate**

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                   | Characteristic                                                                                         | Min. | Тур.    | Max.      | Unit | Notes |

|------------------------------------------|--------------------------------------------------------------------------------------------------------|------|---------|-----------|------|-------|

| 1, L2, L3 and L                          | 4 inputs                                                                                               |      |         |           |      | •     |

| t <sub>WUF</sub>                         | Lx Filter Time Deglitcher                                                                              | 8.0  | 20      | 38        | μs   | (50)  |

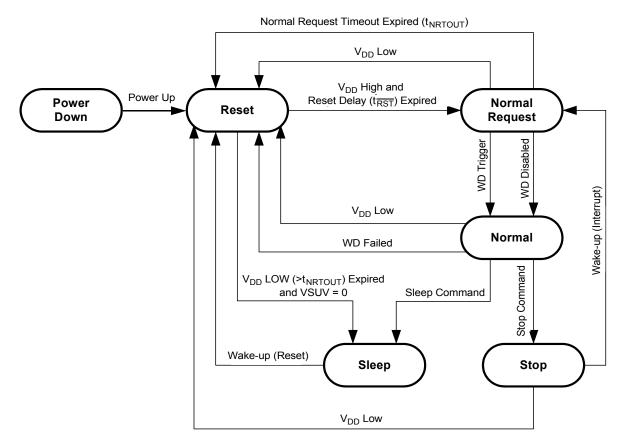

| tate machine t                           | iming                                                                                                  |      |         |           |      |       |

| t <sub>STOP</sub>                        | Delay Between CS LOW-to-HIGH Transition (at End of SPI Stop Command) and Stop Mode Activation          | -    | _       | 5.0       | μs   | (50)  |

| t <sub>NRTOUT</sub>                      | Normal Request Mode Timeout (see Figure 12, page 22)                                                   | 110  | 150     | 205       | ms   |       |

| T <sub>ON</sub>                          | Cyclic Sense ON Time from Stop and Sleep mode                                                          | 130  | 200     | 270       | μs   | (51)  |

|                                          | Cyclic Sense Accuracy                                                                                  | -35  |         | +35       | %    | (50)  |

| t <sub>S-ON</sub>                        | Delay Between the SPI Command and HS/LS Turn On<br>• 9.0 V < V <sub>SUP</sub> < 27 V                   |      | -       | 10        | μs   | (52)  |

| t <sub>S-OFF</sub>                       | Delay Between the SPI Command and HS/LS Turn Off<br>• 9.0 V < V <sub>SUP</sub> < 27 V                  | _    | -       | 10        | μs   | (52)  |

| t <sub>SNR2N</sub>                       | Delay Between Normal Request and Normal mode After a Watchdog<br>Trigger Command (Normal Request Mode) | -    | _       | 10        | μs   | (50)  |

| t <sub>WU</sub> cs<br>t <sub>WUSPI</sub> |                                                                                                        |      | 15<br>— | 80<br>N/A | μs   |       |

| t <sub>2CS</sub>                         | Minimum Time Between Rising and Falling Edge on the CS                                                 | 4.0  | _       | —         | μs   |       |

#### J2602 deglitcher

| t <sub>J2602_DEG</sub> | V <sub>SUP</sub> Deglitcher<br>• (DIS_J2602 = 0) | 35 | 50 | 70 | μs | (53) |

|------------------------|--------------------------------------------------|----|----|----|----|------|

|------------------------|--------------------------------------------------|----|----|----|----|------|

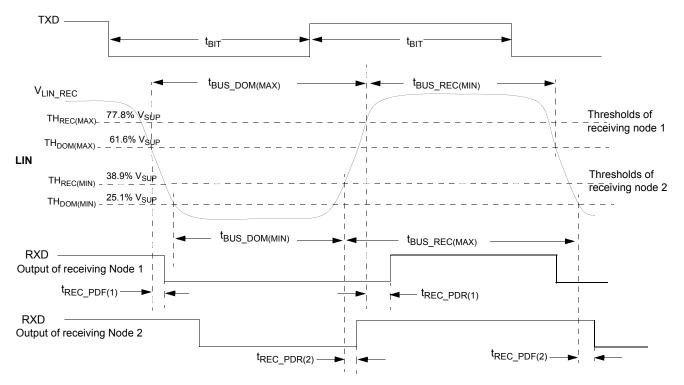

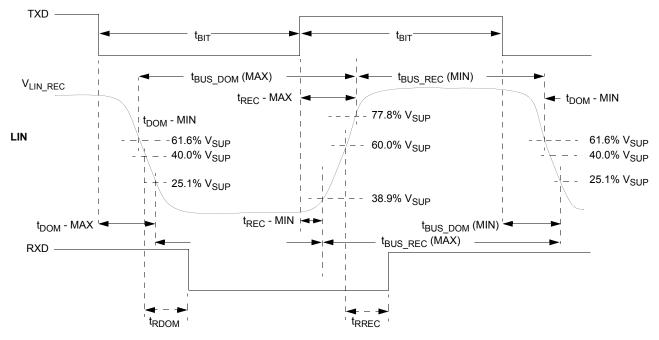

LIN physical layer: driver characteristics for normal slew rate - 20.0 kbit/sec according to lin physical layer specification<sup>(54), (55)</sup>

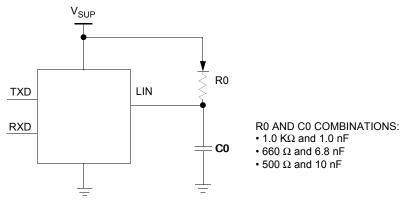

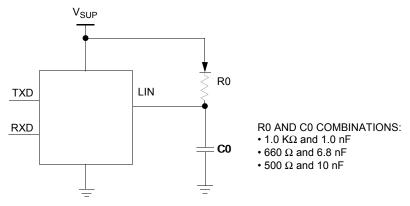

| D1 | $ \begin{array}{ l l l l l l l l l l l l l l l l l l l$                                                                                                                                                                                                                                    | 0.396 | _ | _     |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|-------|--|

| D2 | $ \begin{array}{l} \mbox{Duty Cycle 2:} & & \\ \bullet \ TH_{REC(MIN)} = 0.422 \ ^* \ V_{SUP} & \\ \bullet \ TH_{DOM(MIN)} = 0.284 \ ^* \ V_{SUP} & \\ \bullet \ D2 = t_{BUS\_REC(MAX)} / (2 \ x \ t_{BIT}), \ t_{BIT} = 50 \ \mu s, \ 7.6 \ V \leq V_{SUP} \leq 18 \ V & \\ \end{array} $ | _     | _ | 0.581 |  |

Notes

50. This parameter is guaranteed by process monitoring but not production tested.

51. This parameter is 100% tested on an Automatic Tester. However, since it has not been monitored during reliability stresses, NXP does not guarantee this parameter during the product's life time.

52. Delay between turn on or off command (rising edge on CS) and HS or LS ON or OFF, excluding rise or fall time due to external load.

53. This parameter has not been monitoring during operating life test.

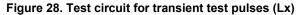

54. Bus load R<sub>BUS</sub> and C<sub>BUS</sub> 1.0 nF / 1.0 kΩ, 6.8 nF / 660 Ω, 10 nF / 500 Ω. Measurement thresholds: 50% of TXD signal to LIN signal threshold defined at each parameter.

55. See Figure 7, page 20.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C for the 33912 and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C for the 34912, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                            | Characteristic                                                                                                                                                                                                                                                                                                                | Min.          | Тур.         | Max.                       | Unit   | Notes             |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|----------------------------|--------|-------------------|

| physical lay                                      | er: driver characteristics for slow slew rate - 10.4 kbit/sec according t                                                                                                                                                                                                                                                     | to lin physic | al layer spe | cification <sup>(56)</sup> | , (57) |                   |

| D3                                                |                                                                                                                                                                                                                                                                                                                               | 0.417         | _            | _                          |        |                   |

| D4                                                | $ \begin{array}{l} \mbox{Duty Cycle 4:} & & \\ \bullet \mbox{TH}_{REC(MIN)} = 0.389 * \mbox{V}_{SUP} & & \\ \bullet \mbox{TH}_{DOM(MIN)} = 0.251 * \mbox{V}_{SUP} & & \\ \bullet \mbox{D4} = \mbox{t}_{BUS\_REC(MAX)}/(2 \ x \ t_{BIT}), \ t_{BIT} = 96 \ \mu s, \ 7.6 \ V \leq \mbox{V}_{SUP} \leq 18 \ V & \\ \end{array} $ | _             | _            | 0.590                      |        |                   |

| IN physical lay                                   | er: driver characteristics for fast slew rate                                                                                                                                                                                                                                                                                 |               |              |                            |        |                   |