#### **Contents**

| Description                         | 1 |

|-------------------------------------|---|

| Features                            | 1 |

| Application                         | 1 |

| Contents                            |   |

| 1. Pin Assignment                   | 3 |

| 2. Block Diagram                    |   |

| 3. Functional Descriptions          | 4 |

| 4. Operation Sequence               | 6 |

| 5. Absolute Maximum Ratings         | 7 |

| 6. Recommended Operating Conditions |   |

| 7 Floctrical Characteristics        | 8 |

| 7.1 DC Characteristics                       | 8  |

|----------------------------------------------|----|

| 7.2 AC Characteristics                       | 9  |

| 8. Typical Characteristic Curves             | 10 |

| 9. Application Circuit                       |    |

| 10. Notes on Use                             |    |

| 11. Ordering Information                     | 25 |

| 12. RoHS Compliance Information of Lead (Pb) |    |

| Free version                                 | 25 |

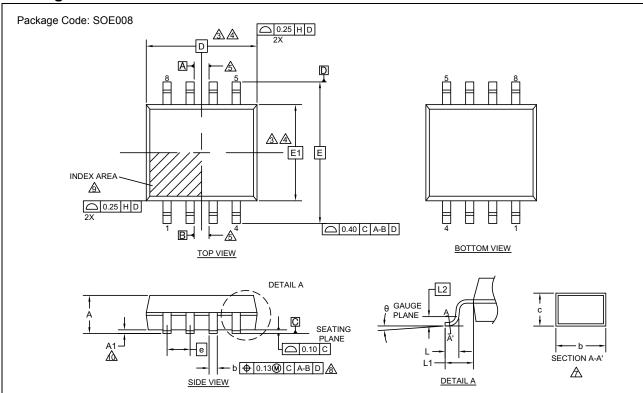

| 13. Package Dimension                        | 26 |

| Document History                             | 27 |

| Sales Solutions and Legal Information        |    |

1. Pin Assignment

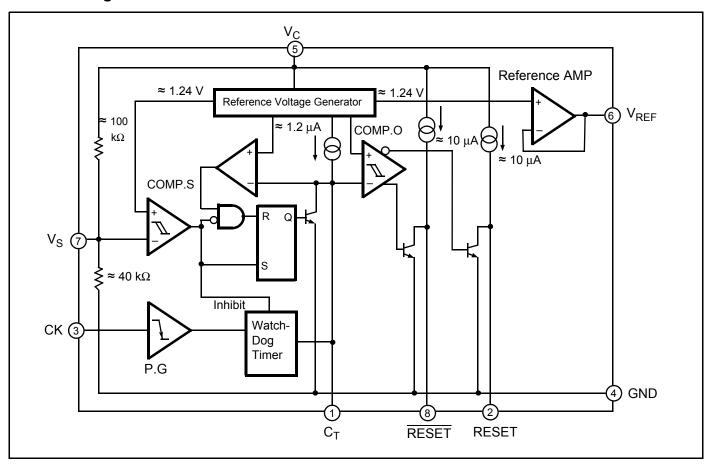

# 2. Block Diagram

## 3. Functional Descriptions

Comp.S is comparator including hysteresis. it compare the reference voltage and the voltage of Vs, so that when the voltage of Vs terminal falls below approximately 1.23 V, reset signal outputs.

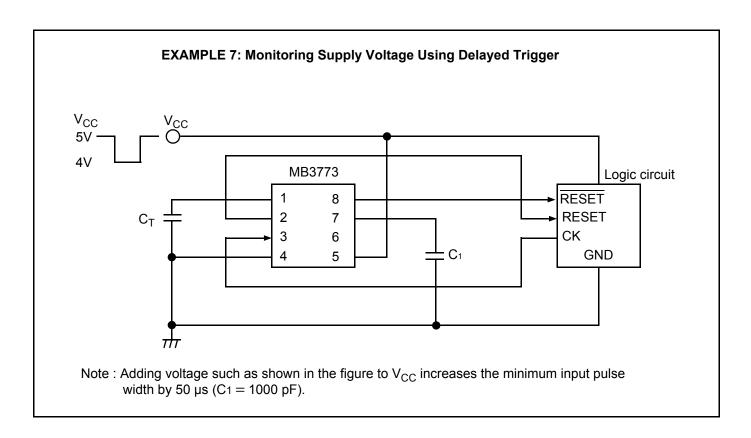

Instantaneous breaks or drops in the power can be detected as abnormal conditions by the MB3773 within a 2 µs interval.

However because momentary breaks or drops of this duration do not cause problems in actual systems in some cases, a delayed trigger function can be created by connecting capacitors to the Vs terminal.

Comp.O is comparator for turning on/off the RESET/RESET outputs and, compare the voltage of the C<sub>T</sub> terminal and the threshold voltage. Because the RESET/RESET outputs have built-in pull-up circuit, there is no need to connect to external pull-up resistor when connected to a high impedance load such as CMOS logic IC.

(It corresponds to  $500~\text{k}\Omega$  at Vcc = 5~V.) when the voltage of the CK terminal changes from the "high" level into the "Low" level, pulse generator is sent to the watch-dog timer by generating the pulse momentarily at the time of drop from the threshold level.

When power-supply voltages fall more than detecting voltages, the watch-dog timer becomes an interdiction.

The Reference amplifier is an op-amp to output the reference voltage.

If the comparator is put up outside, two or more power-supply voltage monitor and overvoltage monitor can be done.

If it uses a comparator of the open-collector output, and the output of the comparator is connected with the Vs terminal of MB3773 without the pull-up resistor, it is possible to voltage monitor with reset-hold time.

Document Number: 002-08513 Rev. \*C Page 4 of 28

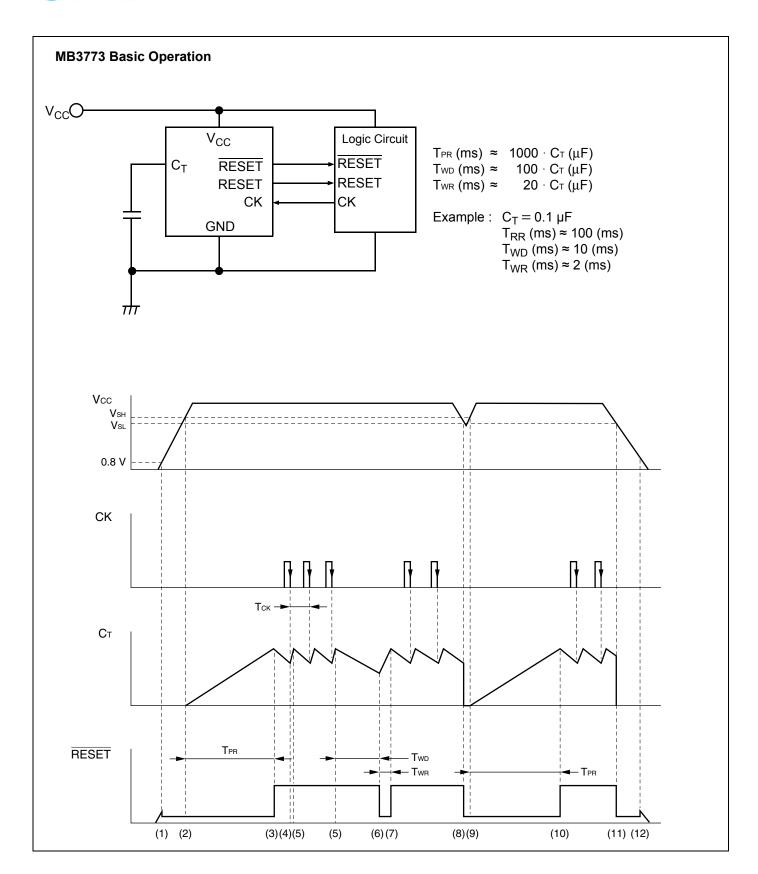

## 4. Operation Sequence

- 1. When Vcc rises to about 0.8 V,  $\overline{\text{RESET}}$  goes "Low" and RESET goes "High". The pull-up current of approximately 1  $\mu$ A (Vcc = 0.8 V) is output from RESET.

- 2. When Vcc rises to  $V_{SH}$  ( $\approx$  4.3V), the charge with  $C_T$  starts. At this time, the output is being reset.

- 3. When  $C_T$  begins charging, RESET goes "High" and RESET goes "Low".

After T<sub>PR</sub> reset of the output is released.

Reset hold time:  $T_{PR}$  (ms)  $\approx 1000 \times C_T$  ( $\mu F$ )

After releasing reset, the discharge of C<sub>T</sub> starts, and watch-dog timer operation starts.

T<sub>PR</sub> is not influenced by the CK input.

- 4. C changes from the discharge into the charge if the clock (Negative edge) is input to the CK terminal while discharging C<sub>T</sub>.

- C changes from the charge into the discharge when the voltage of C<sub>T</sub> reaches a constant threshold (≈ 1.4 V).

- 4 and 5 are repeated while a normal clock is input by the logic system.

- 6. When the clock is cut off, gets, and the voltage of C<sub>T</sub> falls on threshold (≈ 0.4 V) of reset on, RESET goes "Low" and RESET goes "High".

Discharge time of C<sub>T</sub> until reset is output: T<sub>WD</sub> is watch-dog timer monitoring time.

$T_{WD}$  (ms)  $\approx 100 \times C_T$  ( $\mu$ F)

Because the charging time of  $C_T$  is added at accurate time from stop of the clock and getting to the output of reset of the clock,  $T_{WD}$  becomes maximum  $T_{WD} + T_{WR}$  by minimum  $T_{WD}$ .

Reset time in operating watch-dog timer: T<sub>WR</sub> is charging time where the voltage of C<sub>T</sub> goes up to off threshold (≈ 1.4 V) for reset.

$T_{WR}$  (ms)  $\approx 20 \times C_T$  (µF)

Reset of the output is released after  $C_T$  reaches an off threshold for reset, and  $C_T$  starts the discharge, after that if the clock is normally input, operation repeats 4 and 5, when the clock is cut off, operationrepeats 6 and 7.

- 8. When Vcc falls on  $V_{SI}$  ( $\approx$  4.2 V), reset is output.  $C_T$  is rapidly discharged of at the same time.

- 9. When Vcc goes up to  $V_{SH}$ , the charge with  $C_T$  is started.

When Vcc is momentarily low,

After falling  $V_{SL}$  or less Vcc, the time to going up is the standard value of the Vcc input pulse width in  $V_{SH}$  or more. After the charge of  $C_T$  is discharged, the charge is started if it is  $T_{Pl}$  or more.

- 10.Reset of the output is released after T<sub>PR</sub>, after Vcc becomes V<sub>SH</sub> or more, and the watch-dog timer starts. After that, when Vcc becomes V<sub>SL</sub> or less, 8 to 10 is repeated.

- 11. While power supply is off, when Vcc becomes  $V_{SL}$  or less, reset is output.

- 12. The reset output is maintained until Vcc becomes 0.8 V when Vcc falls on 0 V.

Document Number: 002-08513 Rev. \*C Page 6 of 28

## 5. Absolute Maximum Ratings

| Parameter                      | Symbol           | Symbol Rating |                                |      |

|--------------------------------|------------------|---------------|--------------------------------|------|

| Farameter                      | Symbol           | Min           | Max                            | Unit |

| Supply voltage                 | V <sub>CC</sub>  | - 0.3         | + 18                           | V    |

| Input voltage                  | V <sub>S</sub>   | - 0.3         | V <sub>CC</sub> + 0.3 ( ≤ +18) | V    |

|                                | V <sub>CK</sub>  | - 0.3         | + 18                           | V    |

| RESET, RESET Supply voltage    | V <sub>OH</sub>  | - 0.3         | V <sub>CC</sub> + 0.3 ( ≤ +18) | V    |

| Power dissipation (Ta ≤ +85°C) | P <sub>D</sub>   | _             | 200                            | mW   |

| Storage temperature            | T <sub>STG</sub> | - 55          | + 125                          | °C   |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 6. Recommended Operating Conditions

| Parameter                     | Symbol                            | Va    | Unit |       |

|-------------------------------|-----------------------------------|-------|------|-------|

| Farameter                     | Symbol                            | Min   | Max  | Oilit |

| Supply voltage                | V <sub>CC</sub>                   | + 3.5 | + 16 | V     |

| RESET, RESET sink current     | I <sub>OL</sub>                   | 0     | 20   | mA    |

| VREF output current           | I <sub>OUT</sub>                  | - 200 | + 5  | μA    |

| Watch clock setting time      | t <sub>WD</sub>                   | 0.1   | 1000 | ms    |

| CK Rising/falling time        | t <sub>FC</sub> , t <sub>RC</sub> | _     | 100  | μs    |

| Terminal capacitance          | C <sub>T</sub>                    | 0.001 | 10   | μF    |

| Operating ambient temperature | Та                                | - 40  | + 85 | °C    |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their Cypress representatives beforehand.

Document Number: 002-08513 Rev. \*C Page 7 of 28

## 7. Electrical Characteristics

## 7.1 DC Characteristics

$(V_{CC} = 5 \text{ V}, \text{Ta} = + 25^{\circ}\text{C})$

| Parameter                                    | Symbol             | Condition                                                                                       |       | Value | v, 1a – 1 | Unit  |  |

|----------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------|-------|-------|-----------|-------|--|

| Parameter                                    | Symbol             | Symbol                                                                                          |       | Тур   | Max       | Unit  |  |

| Supply current                               | I <sub>CC</sub>    | Watch-dog timer operating                                                                       | _     | 600   | 900       | μA    |  |

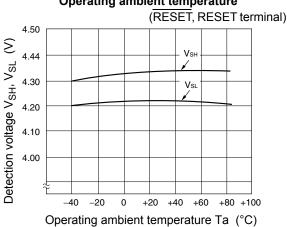

|                                              | V                  | V <sub>CC</sub>                                                                                 | 4.10  | 4.20  | 4.30      |       |  |

| Detection voltage                            | V <sub>SL</sub>    | Ta = - 40°C to + 85°C                                                                           | 4.05  | 4.20  | 4.35      | V     |  |

| Detection voltage                            | V                  | V <sub>CC</sub>                                                                                 | 4.20  | 4.30  | 4.40      | , v   |  |

|                                              | V <sub>SH</sub>    | Ta = - 40°C to + 85°C                                                                           | 4.15  | 4.30  | 4.45      |       |  |

| Hysteresis width                             | V <sub>HYS</sub>   | V <sub>CC</sub>                                                                                 | 50    | 100   | 150       | mV    |  |

| Reference voltage                            | V                  | _                                                                                               | 1.227 | 1.245 | 1.263     | V     |  |

| Neierence voitage                            | V <sub>REF</sub>   | Ta = - 40°C to + 85°C                                                                           | 1.215 | 1.245 | 1.275     | , v   |  |

| Reference voltage change rate                | ΔV <sub>REF1</sub> | V <sub>CC</sub> = 3.5 V to 16 V                                                                 | _     | 3     | 10        | mV    |  |

| Reference voltage output loading change rate | $\Delta V_{REF2}$  | I <sub>OUT</sub> = - 200 μA to + 5 μA                                                           | - 5   | _     | + 5       | mV    |  |

| CK threshold voltage                         | V <sub>TH</sub>    | Ta = - 40°C to + 85°C                                                                           | 0.8   | 1.25  | 2.0       | V     |  |

| CK input current                             | I <sub>IH</sub>    | V <sub>CK</sub> = 5.0 V                                                                         | _     | 0     | 1.0       | - μΑ  |  |

|                                              | I <sub>IL</sub>    | V <sub>CK</sub> = 0.0 V                                                                         | - 1.0 | - 0.1 | _         |       |  |

| C <sub>T</sub> discharge current             | I <sub>CTD</sub>   | Watch-dog timer operating V <sub>CT</sub> = 1.0 V                                               | 7     | 10    | 14        | μA    |  |

| High level output voltage                    | V <sub>OH1</sub>   | V <sub>S</sub> open, I <sub>RESET</sub> = - 5 μA                                                | 4.5   | 4.9   | _         |       |  |

| Tigit level output voltage                   | V <sub>OH2</sub>   | V <sub>S</sub> = 0 V, I <sub>RESET</sub> = - 5 μA                                               | 4.5   | 4.9   | _         | \ \ \ |  |

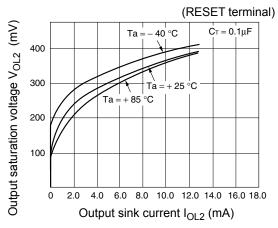

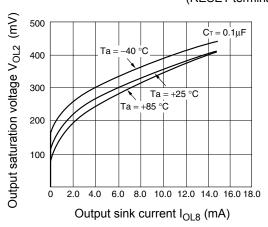

|                                              | V <sub>OL1</sub>   | V <sub>S</sub> = 0 V, I <sub>RESET</sub> = 3 mA                                                 | _     | 0.2   | 0.4       |       |  |

| Output saturation voltage                    | V <sub>OL2</sub>   | V <sub>S</sub> = 0 V, I <sub>RESET</sub> = 10 mA                                                | _     | 0.3   | 0.5       | V     |  |

| Julput Saturation Voltage                    | V <sub>OL3</sub>   | V <sub>S</sub> open, I <sub>RESET</sub> = 3 mA                                                  | _     | 0.2   | 0.4       | v     |  |

|                                              | V <sub>OL4</sub>   | V <sub>S</sub> open, I <sub>RESET</sub> = 10 mA                                                 | _     | 0.3   | 0.5       |       |  |

| Output sink current                          | I <sub>OL1</sub>   | V <sub>S</sub> = 0 V, V <sub>RESET</sub> = 1.0 V                                                | 20    | 60    | _         | mA    |  |

| Output sink current                          | I <sub>OL2</sub>   | V <sub>S</sub> open, V <sub>RESET</sub> = 1.0 V                                                 | 20    | 60    | _         | IIIA  |  |

| C <sub>T</sub> charge current                | I <sub>CTU</sub>   | Power on reset operating V <sub>CT</sub> = 1.0 V                                                | 0.5   | 1.2   | 2.5       | μΑ    |  |

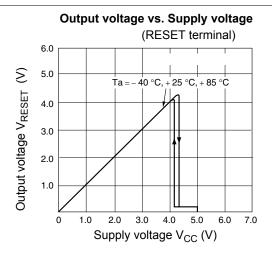

| Min supply voltage for RESET                 | V <sub>CCL1</sub>  | V <sub>RESET</sub> = 0.4 V,<br>I <sub>RESET</sub> = 0.2 mA                                      | _     | 0.8   | 1.2       | V     |  |

| Min supply voltage for RESET                 | V <sub>CCL2</sub>  | $V_{RESET} = V_{CC} - 0.1 \text{ V},$ $R_L \text{ (between pin 2 and GND)} = 1 \text{ M}\Omega$ | _     | 0.8   | 1.2       | ٧     |  |

Document Number: 002-08513 Rev. \*C

#### 7.2 AC Characteristics

$(V_{CC} = 5 \text{ V}, Ta = + 25^{\circ}C)$

| Parameter                         | Symbol           | Condition                                                   | Value |     |     | Unit  |

|-----------------------------------|------------------|-------------------------------------------------------------|-------|-----|-----|-------|

| Farameter                         | Symbol           | Condition                                                   | Min   | Тур | Max | Offic |

| V <sub>CC</sub> input pulse width | T <sub>Pl</sub>  | 5 V V <sub>CC</sub> 4 V                                     | 8.0   | _   | _   | μs    |

| CK input pulse width              | T <sub>CKW</sub> | CKor                                                        | 3.0   | _   | _   | μs    |

| CK input frequency                | T <sub>CK</sub>  | _                                                           | 20    | _   | _   | μs    |

| Watch-dog timer watching time     | T <sub>WD</sub>  | $C_T = 0.1  \mu F$                                          | 5     | 10  | 15  | ms    |

| Watch-dog timer reset time        | T <sub>WR</sub>  | C <sub>T</sub> = 0.1 μF                                     | 1     | 2   | 3   | ms    |

| Rising reset hold time            | T <sub>PR</sub>  | C <sub>T</sub> = 0.1 μF, V <sub>CC</sub>                    | 50    | 100 | 150 | ms    |

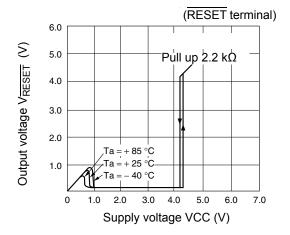

| Output propagation                | T <sub>PD1</sub> | RESET, $R_L = 2.2 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ | _     | 2   | 10  | 110   |

| delay time from VCC               | T <sub>PD2</sub> | RESET, $R_L = 2.2 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ | _     | 3   | 10  | μs    |

| Output rising time*               | t <sub>R</sub>   | $R_L = 2.2 \text{ k}\Omega,$<br>$C_L = 100 \text{ pF}$      | _     | 1.0 | 1.5 | 116   |

| Output falling time*              | t <sub>F</sub>   | $R_L = 2.2 \text{ k}\Omega,$<br>$C_L = 100 \text{ pF}$      | _     | 0.1 | 0.5 | μs    |

$<sup>^{\</sup>star}$  : Output rising/falling time are measured at 10 % to 90 % of voltage.

Document Number: 002-08513 Rev. \*C Page 9 of 28

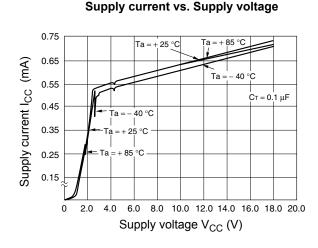

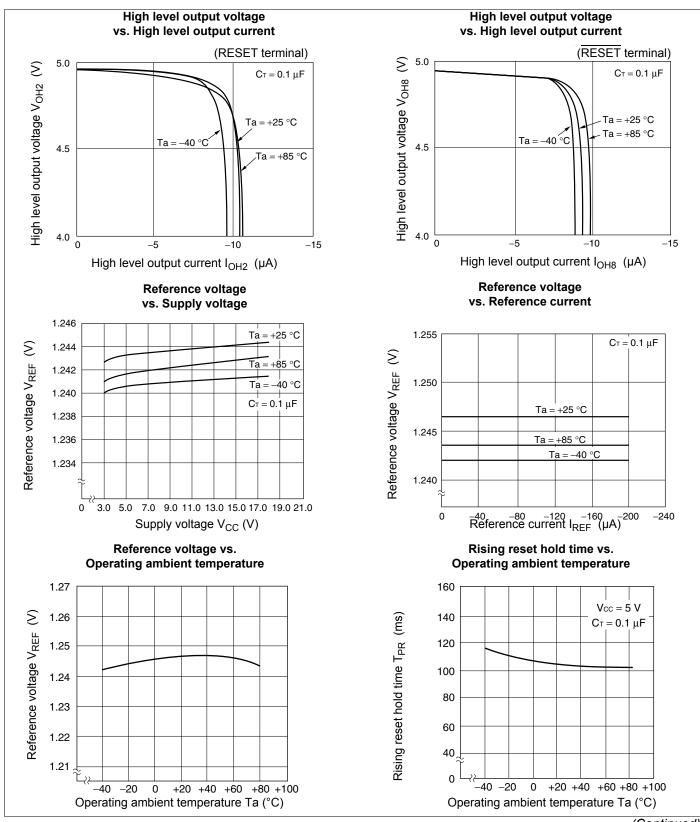

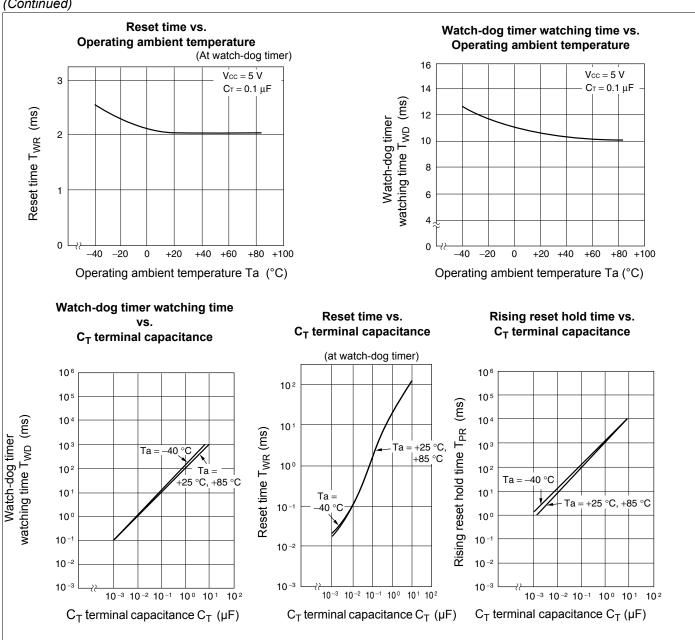

## 8. Typical Characteristic Curves

#### Output voltage vs. Supply voltage

Output saturation voltage vs. Output sink current

Detection voltage (VSH, VSL) vs. Operating ambient temperature

Output saturation voltage vs. Output sink current

(Continued)

Document Number: 002-08513 Rev. \*C Page 10 of 28

(Continued)

#### (Continued)

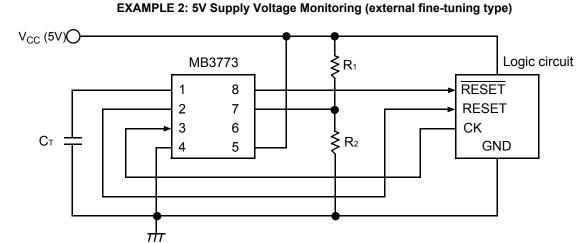

# 9. Application Circuit

**EXAMPLE 1: Monitoring 5V Supply Voltage and Watch-dog Timer** VCC (5V) MB3773 Logic circuit 1 8 RESET 2 7 **RESET** 3 6 CK 5 **GND** Notes: • Supply voltage is monitored using V<sub>S</sub>. • Detection voltage are V<sub>SH</sub> and V<sub>SL</sub>.

# Notes :

- · Vs detection voltage can be adjusted externally.

- Based on selecting R<sub>1</sub> and R<sub>2</sub> values that are sufficiently lower than the resistance of the IC's internal voltage divider, the detection voltage can be set according to the resistance ratio of R<sub>1</sub> and R<sub>2</sub> (Refer to the table below.)

| R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | Detection voltage: V <sub>SL</sub> (V) | Detection voltage: V <sub>SH</sub> (V) |

|---------------------|---------------------|----------------------------------------|----------------------------------------|

| 10                  | 3.9                 | 4.4                                    | 4.5                                    |

| 9.1                 | 3.9                 | 4.1                                    | 4.2                                    |

Document Number: 002-08513 Rev. \*C

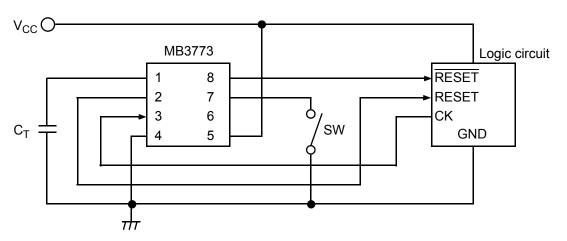

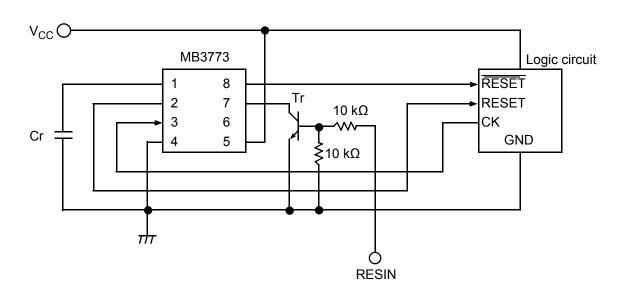

#### **EXAMPLE 3: With Forced Reset (with reset hold)**

(a)

Note: Grounding pin 7 at the time of SW ON sets RESET (pin 8) to Low and RESET (pin 2) to High.

(b)

Note : Feeding the signal to terminal RESIN and turning on Tr sets the  $\overline{\text{RESET}}$  terminal to Low and the RESET terminal to High.

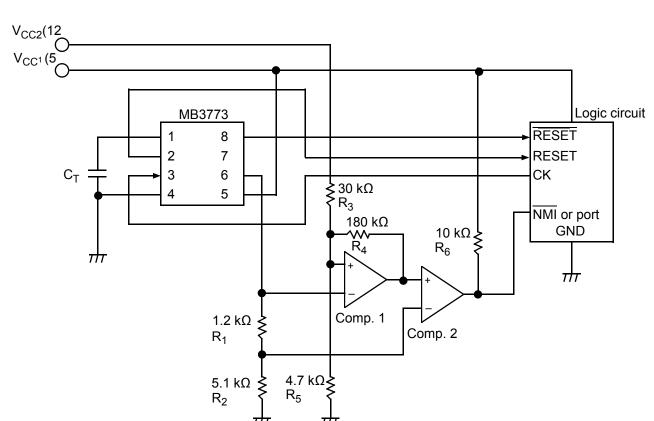

**EXAMPLE 4: Monitoring Two Supply Voltages (with hysteresis, reset output and NMI)**

Example : Comp. 1, Comp. 2 : MB4204, MB47393

#### Notes:

• The 5 V supply voltage is monitored by the MB3773.

- The 12 V supply voltage is monitored by the external circuit. Its output is connected to the NMI terminal and, when voltage drops, Comp. 2 interrupts the logic circuit.

- Use V<sub>CC1</sub> ( = 5 V) to power the comparators (Comp. 1 and Comp. 2) in the external circuit shown above.

- The detection voltage of the V<sub>CC2</sub> (= 12 V) supply voltage is approximately 9.2 V/9.4 V and has a hysteresis width

of approximately 0.2 V.

V<sub>CC2</sub> detection voltage and hysteresis width can be found using the following formulas:

→ Detection voltage

$$V_{2H} = \frac{R_3 + (R_4 /\!/ R_5)}{R_4 /\!/ R_5} \times V_{REF}$$

(Approximately 9.4 V in the above illustration)

$$V_{2L} = \frac{R_3 + R_5}{R_5} \times V_{REF}$$

(Approximately 9.2 V in the above illustration)

$\rightarrow$  Hysteresis width  $V_{HYS} = V_{2H} - V_{2L}$

Page 16 of 28

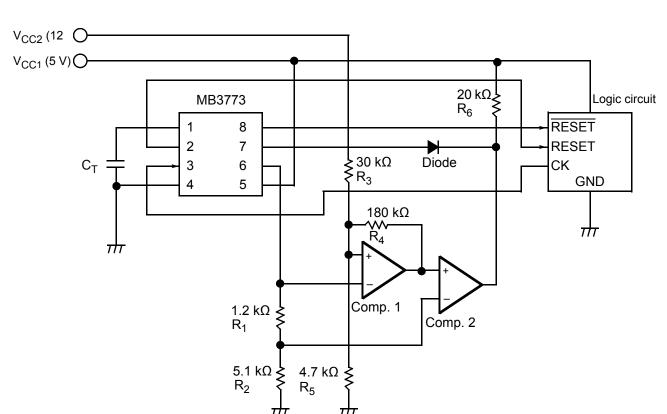

**EXAMPLE 5: Monitoring Two Supply Voltages (with hysteresis and reset output)**

Example : Comp. 1, Comp. 2 : MB4204, MB47393

#### Notes:

• When either 5 V or 12 V supply voltage decreases below its detection voltage ( $V_{SL}$ ), the MB3773 RESET terminal is set to High and the MB3773 RESET terminal is set to Low.

- Use V<sub>CC1</sub> (= 5 V) to power the comparators (Comp. 1 and Comp. 2) in the external circuit shown above.

- The detection voltage of the  $V_{CC2}$  ( = 12 V) supply voltage is approximately 9.2 V/9.4 V and has a hysteresis width of approximately 0.2 V. For the formulas for finding hysteresis width and detection voltage, refer to section 4.

Document Number: 002-08513 Rev. \*C

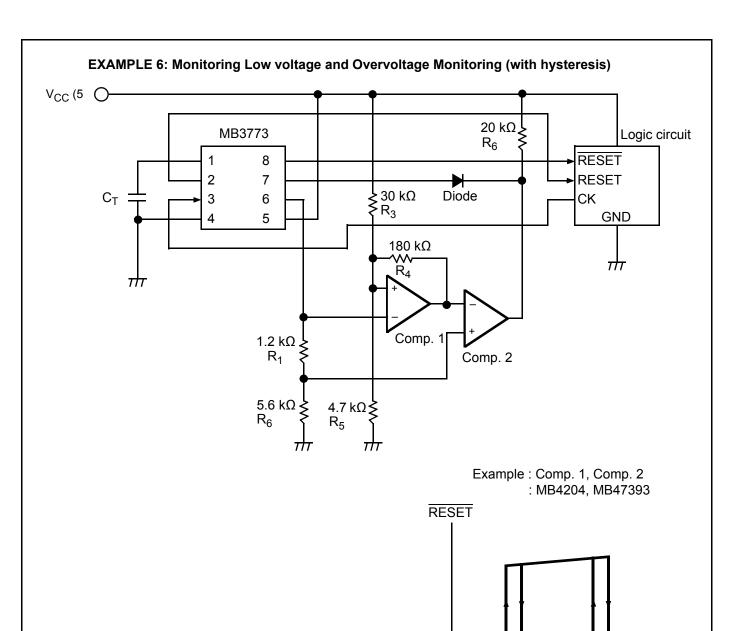

#### Notes:

Comp. 1 and Comp. 2 are used to monitor for overvoltage while the MB3773 is used to monitor for low voltage.

Detection voltages V<sub>1L</sub>/V<sub>1H</sub> at the time of low voltage are approximately 4.2 V/4.3 V. Detection voltages V<sub>2L</sub>/V<sub>2H</sub> at the time of overvoltage are approximately 6.0 V/6.1 V.For the formulas for finding hysteresis width and detection voltage, see EXAMPLE 4.

0

$V_{1L} V_{1H}$

• Use V<sub>CC</sub> (= 5 V) to power the comparators (Comp. 1 and Comp. 2) in the external circuit shown above.

$V_{CC}$

${\sf V}_{\sf 2L}\,{\sf V}_{\sf 2H}$

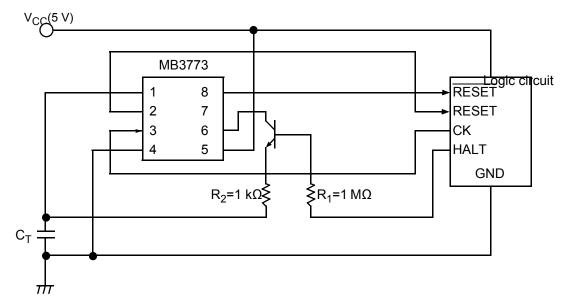

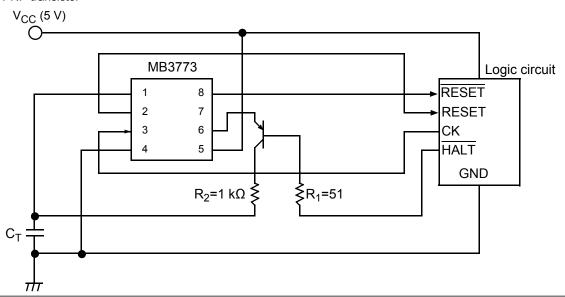

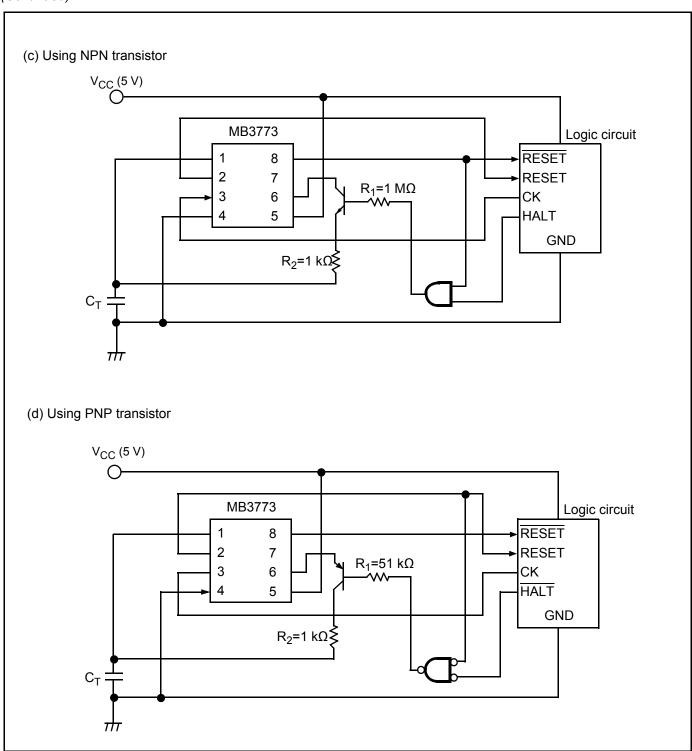

#### **EXAMPLE 8: Stopping Watch-dog Timer (Monitoring only supply voltage)**

These are example application circuits in which the MB3773 monitors supply voltage alone without resetting the microprocessor even if the latter, used in standby mode, stops sending the clock pulse to the MB3773.

• The watch-dog timer is inhibited by clamping the C<sub>T</sub> terminal voltage to V<sub>REF</sub>.

The supply voltage is constantly monitored even while the watch-dog timer is inhibited.

For this reason, a reset signal is output at the occurrence of either instantaneous disruption or a sudden drop to low voltage. Note that in application examples (a) and (b), the hold signal is inactive when the watch-dog timer is inhibited at the time of resetting.

If the hold signal is active when tie microprocessor is reset, the solution is to add a gate, as in examples (c) and (d).

#### (a) Using NPN transistor

## (b) Using PNP transistor

(Continued)

Document Number: 002-08513 Rev. \*C Page 19 of 28

#### (Continued)

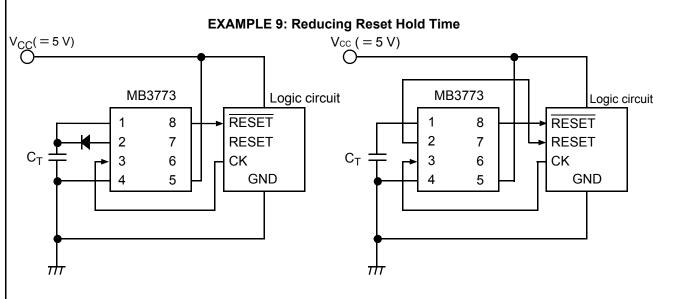

# (a) T<sub>PR</sub> reduction method

#### (b) Standard usage

#### Notes:

- RESET is the only output that can be used.

- Standard  $T_{PR}$ ,  $T_{WD}$  and  $T_{WR}$  value can be found using the following formulas. Formulas:  $T_{PR}$  (ms)  $\approx$  100 × CT ( $\mu$ F)  $T_{WD}$  (ms)  $\approx$  100 × CT ( $\mu$ F)  $T_{WR}$  (ms)  $\approx$  16 × CT ( $\mu$ F)

$$T_{WD}$$

(ms)  $\approx 100 \times CT$  (µF)

• The above formulas become standard values in determining  $T_{PR}$ ,  $T_{WD}$  and  $T_{WR}$ . Reset hold time is compared below between the reduction circuit and the standard circuit.

$$C_T = 0.1 \ \mu F$$

|                   | TPR reduction circuit | Standard circuit |

|-------------------|-----------------------|------------------|

| T <sub>PR</sub> ≈ | 10 ms                 | 100 ms           |

| T <sub>WD</sub> ≈ | 10 ms                 | 10 ms            |

| T <sub>WR</sub> ≈ | 1.6 ms                | 2.0 ms           |

#### **Description of Application Circuits**

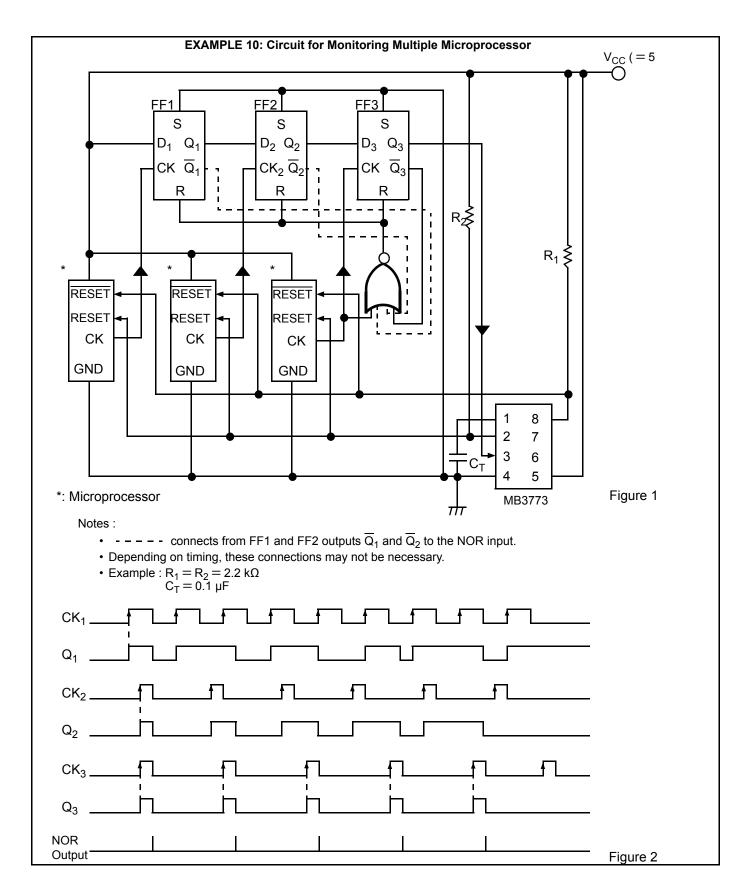

Using one MB3773, this application circuit monitors multiple microprocessor in one system. Signals from each microprocessor are sent to FF1, FF2 and FF3 clock inputs. Figure 2 shows these timings. Each flip-flop operates using signals sent from microprocessor as its clock pulse. When even one signal stops, the relevant receiving flip-flop stops operating. As a result, cyclical pulses are not generated at output  $Q_3$ . Since the clock pulse stops arriving at the CK terminal of the MB3773, the MB3773 generates a reset signal. Note that output  $Q_3$  frequency f will be in the following range, where the clock frequencies of  $CK_1$ ,  $CK_2$  and  $CK_3$  are  $f_1$ ,  $f_2$  and  $f_3$  respectively.

$$\frac{1}{f_0} \le \frac{1}{f} \le \frac{1}{f_1} + \frac{1}{f_2} + \frac{1}{f_3}$$

where fo is the lowest frequency among  $f_1$ ,  $f_2$  and  $f_3$ .

Document Number: 002-08513 Rev. \*C Page 23 of 28

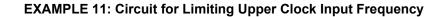

#### Notes:

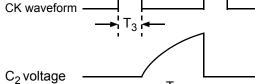

- This is an example application to limit upper frequency fH of clock pulses sent from the microprocessor.

If the CK cycle sent from the microprocessor exceeds fH, the circuit generates a reset signal.

(The lower frequency has already been set using C<sub>T</sub>.)

- When a clock pulse such as shown below is sent to terminal CK, a short T<sub>2</sub> prevents C<sub>2</sub> voltage from reaching the CK input threshold level ( := 1.25 V), and will cause a reset signal to be output.

The T<sub>1</sub> value can be found using the following formula :

$$T_1 \approx 0.3 C_2 R_2$$

where  $V_{CC} = 5 V$ ,  $T_3 \ge 3.0 \mu s$ ,  $T_2 \ge 20 \mu s$

Example : Setting C and R allow the upper  $T_1$  value to be set (Refer to the table below).

| С       | R     | <b>T</b> 1 |

|---------|-------|------------|

| 0.01 μF | 10 kΩ | 30 µs      |

| 0.1 μF  | 10 kΩ | 300 µs     |

Document Number: 002-08513 Rev. \*C

#### 10. Notes on Use

- Take account of common impedance when designing the earth line on a printed wiring board.

- Take measures against static electricity.

- □ For semiconductors, use antistatic or conductive containers.

- □ When storing or carrying a printed circuit board after chip mounting, put it in a conductive bag or container.

- ☐ The work table, tools and measuring instruments must be grounded.

- $\Box$  The worker must put on a grounding device containing 250 k $\Omega$  to 1 M $\Omega$  resistors in series.

- Do not apply a negative voltage

- □ Applying a negative voltage of −0.3 V or less to an LSI may generate a parasitic transistor, resulting in malfunction

## 11. Ordering Information

| Part number    | Package                       | Remarks |

|----------------|-------------------------------|---------|

| MB3773PF-DDDE1 | 8-pin plastic SOP<br>(SOE008) | -       |

## 12. RoHS Compliance Information of Lead (Pb) Free version

The LSI products of Cypress with "E1" are compliant with RoHS Directive, and has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

The product that conforms to this standard is added "E1" at the end of the part number.

Document Number: 002-08513 Rev. \*C Page 25 of 28

## 13. Package Dimension

| SYMBOL  | DI       | MENSIC   | N    |  |

|---------|----------|----------|------|--|

| STWIBOL | MIN.     | NOM.     | MAX. |  |

| А       | _        | _        | 2.25 |  |

| A1      | 0.05     | 1        | 0.20 |  |

| D       | 6        | 6.35 BSC |      |  |

| Е       | 7.80 BSC |          |      |  |

| E1      | 5.30 BSC |          |      |  |

| θ       | 0°       |          | 8°   |  |

| С       | 0.13     | _        | 0.20 |  |

| b       | 0.39     | 0.47     | 0.55 |  |

| L       | 0.45     | 0.60     | 0.75 |  |

| L 1     | 1.25 REF |          |      |  |

| L 2     | 0.25 BSC |          |      |  |

| е       | 1.27 BSC |          |      |  |

#### NOTES

- 1. ALL DIMENSIONS ARE IN MILLIMETER.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- ⚠ DIMENSIONING D INCLUDE MOLD FLASH, DIMENSIONING E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.025 mm PER SIDE. D and E1 DIMENSION ARE DETERMINED AT DATUM H

- ⚠THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM.

DIMENSIONING D and E1 ARE DETERMINED AT THE OUTERMOST

EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH,

THE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING

ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- ⚠DATUMS A & B TO BE DETERMINED AT DATUM H.

- 6. "N" IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

- THE DIMENSION APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 mm TO 0.25mm FROM THE LEAD TIP.

- MIMENSION "b" DOES NOT INCLUDE THE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.10mm TOTAL IN EXCESS OF THE "b" DIMENSION AT MAXIMUM MATERIAL CONDITION.

- THE DAMBAR MAY NOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT.

- ⚠ THIS CHAMFER FEATURE IS OPTIONAL. LF IT IS NOT PRESENT, THEN A PIN 1 IDENTIFIER MUST BE LOCATED WITHIN THE INDEX AREA INDICATED

- "A1" IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY EXCLUDING THE LID AND OR THERMAL ENHANCEMENT ON CAVITY DOWN PACKAGE CONFIGURATIONS.

- 11. JEDEC SPECIFICATION NO. REF: N/A

002-15857 Rev. \*\*

# **Document History**

Spansion Publication Number: DS04-27401-8Ea

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | -       | TAOA               | 05/11/2006         | Migrated to Cypress and assigned document number 002-08513. No change to document contents or format.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *A       | 5199075 | TAOA               | 04/04/2016         | Updated to Cypress format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *B       | 5592858 | HIXT               | 01/23/2017         | Updated Pin Assignment: Change the package name from FPT-8P-M01 to SOE008 Updated Ordering Information: Change the package name from FPT-8P-M01 to SOE008 Updated Package Dimension: Updated to Cypress format Deleted "Marking Format (Lead Free version)" Deleted "Labeling Sample (Lead free version)" Deleted "MB3773PF- □ □ □ E1 Recommended Conditions of Moisture Sensitivity Level" Deleted the part number, "MB3773PF- □ □ □ ", from Ordering Information Deleted the words in the Remarks, "Lead Free version", from Ordering Information |

| *C       | 5788613 | MASG               | 06/28/2017         | Adapted Cypress new logo.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Document Number: 002-08513 Rev. \*C Page 27 of 28

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch **USB Controllers** cypress.com/usb Wireless/RF cypress.com/wireless

#### PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries

© Cypress Semiconductor Corporation, 2003-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress parally a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners..