### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND | 0.3V to +6.0V |

|------------------------|---------------|

| All Other Pins to GND  | 0.3V to +6.0V |

| Input Currents         |               |

| V <sub>DD</sub>        |               |

| GND                    |               |

| All Input Pins         | ±20mA         |

| Output Current         |               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ | 2)             |

|-----------------------------------------------------|----------------|

| 20-Pin TSSOP (derate 11.0mW/°C                      |                |

| above $T_A = +70^{\circ}C$ )                        | 879.1mW        |

| 16-Pin TSSOP (derate 9.4mW/°C                       |                |

| above $T_A = +70^{\circ}C$ )                        | 754.7mW        |

| Operating Temperature Range                         | 40°C to +85°C  |

| Junction Temperature                                | +150°C         |

| Storage Temperature Range                           | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                   | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS (3.3V SUPPLY)**

$(V_{DD} = 2.3V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{DD} = 3.3V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                       | SYMBOL                      | CONDITIONS                                                                                                     | MIN                      | ТҮР | MAX                       | UNITS |

|---------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|-----|---------------------------|-------|

| POWER SUPPLY                    | •                           |                                                                                                                | •                        |     |                           |       |

| Supply Voltage                  | V <sub>DD</sub>             |                                                                                                                | 2.3                      |     | 3.6                       | V     |

| Standby Current                 | I <sub>STB</sub>            | No load, all inputs = $V_{DD}$ or GND, $V_{DD}$ = 3.6V, all channels disabled                                  |                          | 0.1 | 1                         | μA    |

| Supply Current                  | I <sub>DD</sub>             | No load, all inputs = $V_{DD}$ or GND,<br>f <sub>SCL</sub> = 100kHz, $V_{DD}$ = 3.6V,<br>all channels disabled |                          | 6   | 30                        | μΑ    |

| Power-On-Reset (POR)<br>Voltage | V <sub>POR</sub>            | V <sub>DD</sub> rising                                                                                         |                          | 1.4 | 2.1                       | V     |

| Power-On-Reset Hysteresis       | V <sub>HYST</sub>           |                                                                                                                |                          | 0.4 |                           | V     |

| INPUT SCL, INPUT/OUTPU          | T SDA                       |                                                                                                                |                          |     |                           |       |

| Low-Level Input Voltage         | VIL                         | (Note 2)                                                                                                       | -0.2                     |     | +0.3 x<br>V <sub>DD</sub> | V     |

| High-Level Input Voltage        | VIH                         |                                                                                                                | 0.7 x<br>V <sub>DD</sub> |     | 5.5                       | V     |

| Low-Level Output Current        | le.                         | $V_{OL} = 0.4V$                                                                                                | 3                        | 30  |                           | mA    |

| Low-Level Output Current        | I <sub>OL</sub>             | $V_{OL} = 0.6V$                                                                                                | 6                        | 50  |                           | ША    |

| Input Leakage Current           | ١L                          |                                                                                                                | -1                       |     | +1                        | μA    |

| Input Capacitance               | CI                          | All inputs = GND                                                                                               |                          | 15  |                           | рF    |

| SELECT INPUTS A2, A1, A         | 0, <del>INTO–INT3</del> , I | RESET                                                                                                          | T                        |     |                           |       |

| Low-Level Input Voltage         | V <sub>IL</sub>             | (Note 2)                                                                                                       | -0.2                     |     | +0.3 x<br>V <sub>DD</sub> | V     |

| High-Level Input Voltage        | VIH                         |                                                                                                                | 0.7 x<br>V <sub>DD</sub> |     | 5.5                       | V     |

| Input Leakage Current           | ١L                          |                                                                                                                | -1                       |     | +1                        | μA    |

| Input Capacitance               | CI                          | All inputs = GND                                                                                               |                          | 5   |                           | pF    |

### ELECRTICAL CHARACTERISTICS (3.3V SUPPLY) (continued)

$(V_{DD} = 2.3V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{DD} = 3.3V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                 | SYMBOL          | CONDITIONS                                               | MIN | ТҮР | МАХ | UNITS |

|---------------------------|-----------------|----------------------------------------------------------|-----|-----|-----|-------|

| PASS GATE                 |                 |                                                          |     |     |     |       |

| Switch On-Resistance      | Devi            | $V_{DD} = 3V$ to 3.6V, $I_{O} = 15$ mA, $V_{O} = 0.4V$   | 5   | 16  | 30  | Ω     |

| Switch On-Resistance      | R <sub>ON</sub> | $V_{DD} = 2.3V$ to 2.7V, $I_O = 10$ mA, $V_O = 0.4V$     | 7   | 23  | 55  |       |

|                           |                 | $V_{I(SW)} = V_{DD} = 3.0V$ to 3.6V, $I_{O} = -100\mu A$ | 1.6 | 1.9 | 2.8 |       |

| Switch Output Voltage     | VPASS           | $V_{I(SW)} = V_{DD} = 2.3V$ to 2.7V, $I_{O} = -100\mu A$ | 1.1 |     | 2.0 | V     |

|                           |                 | $V_{I(SW)} = V_{DD} = 2.5V, I_O = -100 \mu A$            |     | 1.5 |     |       |

| Leakage Current           | ١L              |                                                          | -1  |     | +1  | μA    |

| Input/Output Capacitance  | CIO             | All inputs = GND                                         |     | 6   |     | pF    |

| ÎNT OUTPUT                |                 |                                                          |     |     |     |       |

| Low-Level Output Current  | IOL             | $V_{OL} = 0.4V$                                          | 3   |     |     | mA    |

| High-Level Output Current | IOH             |                                                          |     |     | 1   | μΑ    |

### **ELECRTICAL CHARACTERISTICS (5V SUPPLY)**

$(V_{DD} = 4.5V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{DD} = 5V, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                                  | SYMBOL                      | CONDITIONS                                                                                        | MIN                      | ТҮР | МАХ                       | UNITS |  |

|--------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------|--------------------------|-----|---------------------------|-------|--|

| POWER SUPPLY                               |                             |                                                                                                   |                          |     |                           |       |  |

| Supply Voltage                             | V <sub>DD</sub>             |                                                                                                   | 4.5                      |     | 5.5                       | V     |  |

| Standby Current                            | ISTB                        | No load, all inputs = $V_{DD}$ or GND, $V_{DD}$ = 5.5V, all channels disabled                     |                          | 0.3 | 1                         | μA    |  |

| Supply Current                             | IDD                         | No load, all inputs = $V_{DD}$ or GND, $f_{SCL}$ = 100kHz, $V_{DD}$ = 5.5V, all channels disabled |                          | 12  | 50                        | μA    |  |

| Power-On-Reset Voltage                     | VPOR                        | V <sub>DD</sub> rising                                                                            |                          | 1.4 | 2.1                       | V     |  |

| POR Hysteresis                             | VHYST                       |                                                                                                   |                          | 0.4 |                           | V     |  |

| INPUT SCL, INPUT/OUTPUT                    | INPUT SCL, INPUT/OUTPUT SDA |                                                                                                   |                          |     |                           |       |  |

| Low-Level Input Voltage                    | VIL                         | (Note 2)                                                                                          | -0.2                     |     | +0.3 x<br>V <sub>DD</sub> | V     |  |

| High-Level Input Voltage                   | VIH                         |                                                                                                   | 0.7 x<br>V <sub>DD</sub> |     | 5.5                       | V     |  |

|                                            | Le.                         | $V_{OL} = 0.4V$                                                                                   | 3                        | 30  |                           |       |  |

| Low-Level Output Current                   | IOL                         | $V_{OL} = 0.6V$                                                                                   | 6                        | 50  |                           | mA    |  |

| Input Leakage Current                      | ١L                          |                                                                                                   | -1                       |     | +1                        | μA    |  |

| Input Capacitance                          | CI                          | All inputs = GND                                                                                  |                          | 15  |                           | pF    |  |

| SELECT INPUTS A2, A1, A0, INTO-INT3, RESET |                             |                                                                                                   |                          |     |                           |       |  |

| Low-Level Input Voltage                    | VIL                         | (Note 2)                                                                                          | -0.2                     |     | +0.3 x<br>V <sub>DD</sub> | V     |  |

| High-Level Input Voltage                   | V <sub>IH</sub>             |                                                                                                   | 0.7 x<br>V <sub>DD</sub> |     | 5.5                       | V     |  |

### ELECRTICAL CHARACTERISTICS (5V SUPPLY) (continued)

$(V_{DD} = 4.5V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at V_{DD} = 5V, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                 | SYMBOL          | CONDITIONS                                           | MIN | ТҮР | МАХ | UNITS |

|---------------------------|-----------------|------------------------------------------------------|-----|-----|-----|-------|

| Input Leakage Current     | ١L              |                                                      | -1  |     | +1  | μA    |

| Input Capacitance         | CI              | All inputs = GND                                     |     | 5   |     | рF    |

| PASS GATE                 |                 |                                                      |     |     |     |       |

| Switch On-Resistance      | R <sub>ON</sub> | $V_{DD} = 4.5V$ to 5.5V, $I_O = 15$ mA, $V_O = 0.4V$ | 4   | 12  | 24  | Ω     |

| Switch Output Voltage     | VPASS           | $V_{I(SW)} = V_{DD}, I_{O} = -100 \mu A$             | 2.6 | 3.6 | 4.5 | V     |

| Leakage Current           | ١L              |                                                      | -1  |     | +1  | μΑ    |

| Input/Output Capacitance  | C <sub>IO</sub> | All inputs = GND                                     |     | 6   |     | pF    |

| INT OUTPUT                |                 | ·                                                    |     |     |     |       |

| Low-Level Output Current  | IOL             | $V_{OL} = 0.4V$                                      | 3   |     |     | mA    |

| High-Level Output Current | Іон             |                                                      |     |     | 1   | μA    |

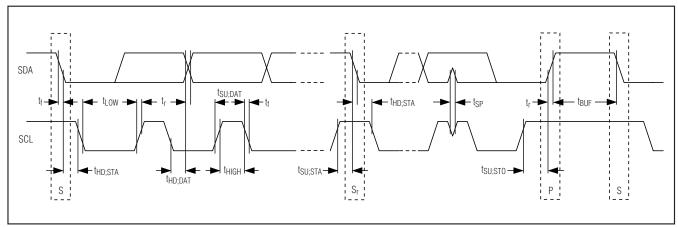

## **TIMING CHARACTERISTICS (Figure 1)**

(V<sub>DD</sub> = 2.3V to 5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                       | SYMBOL              | CONDITIONS                                               | MIN           | ТҮР | МАХ  | UNITS |

|-----------------------------------------------------------------|---------------------|----------------------------------------------------------|---------------|-----|------|-------|

| Propagation Delay from SDA To<br>SD_ or SCL to SC_              | t <sub>pd</sub>     | (Note 3)                                                 |               |     | 0.3  | ns    |

| SCL Clock Frequency                                             | fscl                |                                                          | 0             |     | 400  | kHz   |

| Bus Free Time Between a STOP<br>and START Condition             | <sup>t</sup> BUF    | $f_{SCL} = 100 \text{kHz}$<br>$f_{SCL} = 400 \text{kHz}$ | 4.7           |     |      | μs    |

| Hold Time (Repeated) START<br>Condition (after this period, the | thd:sta             | f <sub>SCL</sub> = 100kHz                                | 4.0           |     |      | μs    |

| first clock pulse is generated)                                 | 41D,31A             | $f_{SCL} = 400 kHz$                                      | 0.6           |     |      | μo    |

| Low Period of the SCL Clock                                     | ti our              | f <sub>SCL</sub> = 100kHz                                | 4.7           |     |      | 19    |

| Low Period of the SCE Clock                                     | tLOW                | $f_{SCL} = 400 \text{kHz}$                               | 1.3           |     |      | μs    |

| High Period of the SCL Clock                                    | thigh               | $f_{SCL} = 100 kHz$                                      | 4.0           |     |      | μs    |

| Flight end of the SOE Clock                                     |                     | f <sub>SCL</sub> = 400kHz                                | 0.6           |     |      |       |

| Setup Time for a Repeated START                                 | tsu;sta             | f <sub>SCL</sub> = 100kHz                                | 4.7           |     |      | μs    |

| Condition                                                       | 150;51A             | $f_{SCL} = 400 \text{kHz}$                               | 0.6           |     |      | μs    |

| Setup Time for STOP Condition                                   | toulotto            | $f_{SCL} = 100 kHz$                                      | 4.0           |     |      | 110   |

| Setup Time to STOP Condition                                    | tsu;sto             | f <sub>SCL</sub> = 400kHz                                | 0.6           |     |      | μs    |

| Data Hold Time (Nate 4)                                         | tup pat             | $f_{SCL} = 100 kHz$                                      | 0             |     | 3.45 | μs    |

| Data Hold Time (Note 4)                                         | <sup>t</sup> hd;dat | f <sub>SCL</sub> = 400kHz                                | 0             |     | 0.9  |       |

| Data Setup Time                                                 | ta                  | f <sub>SCL</sub> = 100kHz                                | 250           |     |      | 20    |

|                                                                 | <sup>t</sup> SU;DAT | f <sub>SCL</sub> = 400kHz                                | 100           |     |      | ns    |

|                                                                 |                     | f <sub>SCL</sub> = 100kHz                                |               |     | 1000 |       |

| Rise Time of Both SDA and SCL<br>Signals                        | tr                  | $f_{SCL} = 400 \text{kHz} (\text{Note 5})$               | 20 +<br>0.1Cb |     | 300  | ns    |

M/XI/M

### TIMING CHARACTERISTICS (Figure 1) (continued)

$(V_{DD} = 2.3V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

|                      |                                                                              |                                                                                                                                                                                                                                                      | TYP                                                                                                                                                                              | MAX                                                                      | UNITS                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | $f_{SCL} = 100 \text{kHz}$                                                   |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 300                                                                      |                                                                                                                                                                                                                                                                                                                                                            |

| tf                   | f <sub>SCL</sub> = 400kHz (Note 5)                                           | 20 +<br>0.1Cb                                                                                                                                                                                                                                        |                                                                                                                                                                                  | 300                                                                      | ns                                                                                                                                                                                                                                                                                                                                                         |

| Cb                   | (Note 6)                                                                     |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 400                                                                      | pF                                                                                                                                                                                                                                                                                                                                                         |

| tsp                  |                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 50                                                                       | ns                                                                                                                                                                                                                                                                                                                                                         |

| tvd;datl             | (Note 7)                                                                     |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 1                                                                        | μs                                                                                                                                                                                                                                                                                                                                                         |

| tvd;dath             | (Note 7)                                                                     |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 0.6                                                                      | μs                                                                                                                                                                                                                                                                                                                                                         |

| tvd;ack              |                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 1                                                                        | μs                                                                                                                                                                                                                                                                                                                                                         |

|                      |                                                                              | ·                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |                                                                          |                                                                                                                                                                                                                                                                                                                                                            |

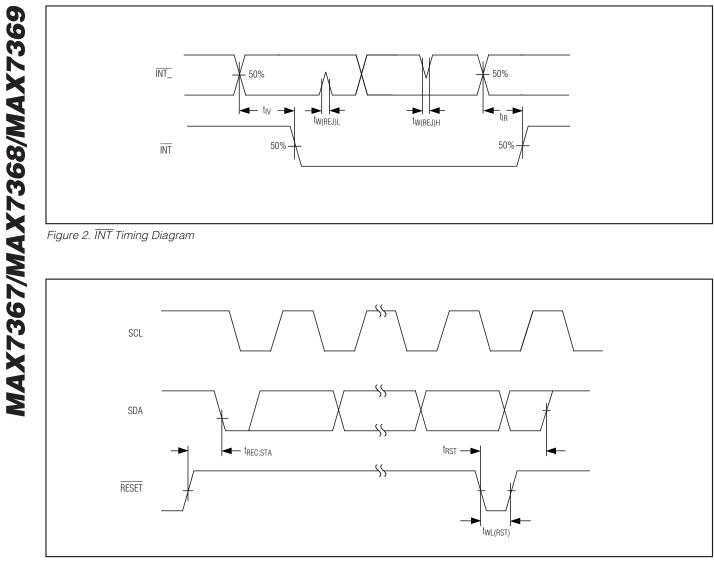

| tıv                  |                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 4                                                                        | μs                                                                                                                                                                                                                                                                                                                                                         |

| tıR                  |                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 2                                                                        | μs                                                                                                                                                                                                                                                                                                                                                         |

| <sup>t</sup> W(REJ)L |                                                                              | 1                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |                                                                          | μs                                                                                                                                                                                                                                                                                                                                                         |

| tw(REJ)H             |                                                                              | 0.5                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |                                                                          | μs                                                                                                                                                                                                                                                                                                                                                         |

|                      |                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                  |                                                                          |                                                                                                                                                                                                                                                                                                                                                            |

| twL(RST)             |                                                                              |                                                                                                                                                                                                                                                      | 4                                                                                                                                                                                |                                                                          | ns                                                                                                                                                                                                                                                                                                                                                         |

| <b>t</b> RST         |                                                                              | 500                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |                                                                          | ns                                                                                                                                                                                                                                                                                                                                                         |

| trec;sta             |                                                                              | 0                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |                                                                          | ns                                                                                                                                                                                                                                                                                                                                                         |

|                      | Cb<br>tSP<br>tVD;DATL<br>tVD;ACK<br>tVD;ACK<br>tVD;ACK<br>tVD;ACK<br>tVD;ACK | fSCL = 400kHz (Note 5)         Cb       (Note 6)         tSP         tVD;DATL       (Note 7)         tVD;DATH       (Note 7)         tVD;ACK         tiv         tIV         tVD;ACK         tw(REJ)L         tW(REJ)H         tWL(RST)         tRST | $f_{SCL} = 400$ kHz (Note 5) $0.1C_b$ $C_b$ (Note 6)       (Note 7) $tVD;DATL$ (Note 7)       (Note 7) $tVD;ACK$ (Note 7) $tVD;ACK$ 1 $tW(REJ)L$ 1 $tW(REJ)H$ 0.5 $tWL(RST)$ 500 | fSCL = 400kHz (Note 5)     LC 1<br>0.1Cb       Cb     (Note 6)       tSP | fSCL = 400kHz (Note 5)       0.1Cb       300         Cb       (Note 6)       400         tSP       50         tVD;DATL       (Note 7)       1         tVD;DATH       (Note 7)       0.6         tVD;ACK       1       1         tIV       4       1         tW(REJ)L       1       2         tW(REJ)L       1       0.5         tWL(RST)       4       500 |

**Note 1:** All parameters are production tested at  $T_A = +25^{\circ}C$  and guaranteed by design over the specified temperature range.

Note 2: Minimum value is not production tested. Guaranteed by design.

Note 3: Pass gate propagation delay is calculated from 20Ω (typ) R<sub>ON</sub> and the 15pF load capacitance. Not production tested.

Note 4: A master device must provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IL</sub> of the SCL) in order to bridge the undefined region of SCL's falling edge.

**Note 5:**  $C_b$  = total capacitance of one bus line in pF.

Note 6: Guaranteed by design.

**Note 7:** Measurements taken with a  $1k\Omega$  pullup resistor and 50pF load.

Figure 1. 2-Wire Serial-Interface Timing Diagram

M/X/M

Figure 3. RESET Timing Diagram

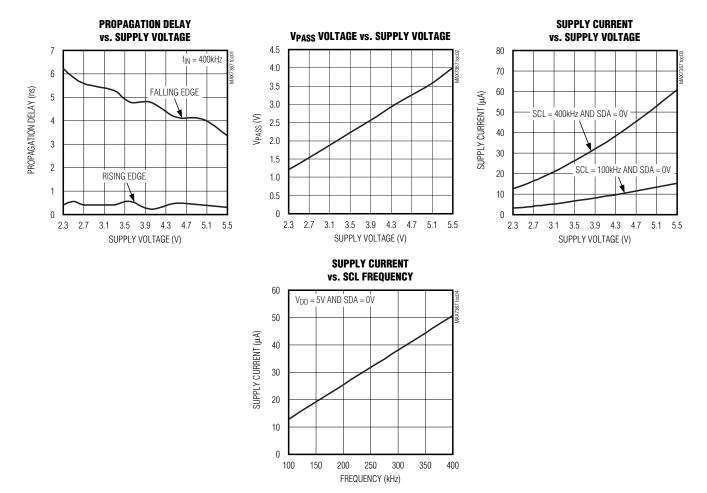

**Typical Operating Characteristics**

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

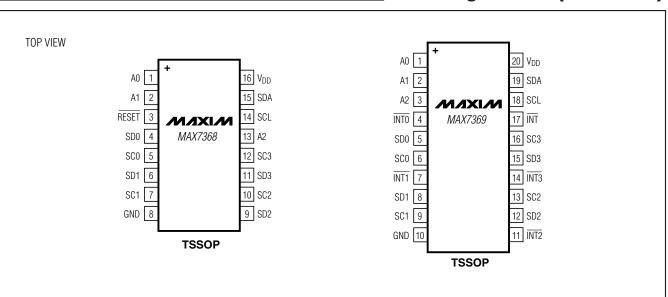

## **Pin Description**

|         | PIN     |         |                                                                                                                                   | FUNCTION                                                                                                                                                                                           |

|---------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX7367 | MAX7368 | MAX7369 | NAME                                                                                                                              | FUNCTION                                                                                                                                                                                           |

| 1       | 1       | 1       | A0                                                                                                                                | Device Address Bit 0 (LSB)                                                                                                                                                                         |

| 2       | 2       | 2       | A1                                                                                                                                | Device Address Bit 1                                                                                                                                                                               |

| 3       | 3       | —       | RESET                                                                                                                             | Active-Low Reset Input                                                                                                                                                                             |

| 4       | _       | 4       | <b>INTO</b>                                                                                                                       | Channel 0 Active-Low Interrupt Input. A logic-low $\overline{\text{INTO}}$ asserts $\overline{\text{INT}}$ . If not used, pull up $\overline{\text{INTO}}$ through a resistor to VDD.              |

| 5       | 4       | 5       | SD0                                                                                                                               | Channel 0 Serial Data                                                                                                                                                                              |

| 6       | 5       | 6       | SC0                                                                                                                               | Channel 0 Serial Clock                                                                                                                                                                             |

| 7       | _       | 7       | INT1 Channel 1 Active-Low Interrupt Input. A logic-low INT1 asserts IN used, pull up INT1 through a resistor to V <sub>DD</sub> . |                                                                                                                                                                                                    |

| 8       | 6       | 8       | SD1                                                                                                                               | Channel 1 Serial Data                                                                                                                                                                              |

| 9       | 7       | 9       | SC1                                                                                                                               | Channel 1 Serial Clock                                                                                                                                                                             |

| 10      | 8       | 10      | GND                                                                                                                               | Ground                                                                                                                                                                                             |

| 11      | _       | 11      | INT2                                                                                                                              | Channel 2 Active-Low Interrupt Input. A logic-low $\overline{\text{INT2}}$ asserts $\overline{\text{INT}}$ . If not used, pull up $\overline{\text{INT2}}$ through a resistor to V <sub>DD</sub> . |

| 12      | 9       | 12      | SD2                                                                                                                               | Channel 2 Serial Data                                                                                                                                                                              |

| 13      | 10      | 13      | SC2                                                                                                                               | Channel 2 Serial Clock                                                                                                                                                                             |

| 14      | _       | 14      | ĪNT3                                                                                                                              | Channel 3 Active-Low Interrupt Input. A logic-low $\overline{\text{INT3}}$ asserts $\overline{\text{INT}}$ . If not used, pull up $\overline{\text{INT3}}$ through a resistor to V <sub>DD</sub> . |

| 15      | 11      | 15      | SD3                                                                                                                               | Channel 3 Serial Data                                                                                                                                                                              |

| 16      | 12      | 16      | SC3                                                                                                                               | Channel 3 Serial Clock                                                                                                                                                                             |

|         | 13      | 3       | A2                                                                                                                                | Device Address Bit 2                                                                                                                                                                               |

| 17      | _       | 17      | ĪNT                                                                                                                               | Active-Low, Open-Drain Interrupt Output. Connect a pullup resistor to VDD.                                                                                                                         |

| 18      | 14      | 18      | SCL                                                                                                                               | Main Serial Clock                                                                                                                                                                                  |

| 19      | 15      | 19      | SDA                                                                                                                               | Main Serial Data                                                                                                                                                                                   |

| 20      | 16      | 20      | V <sub>DD</sub>                                                                                                                   | Power Supply. Bypass to GND with 0.1µF capacitor.                                                                                                                                                  |

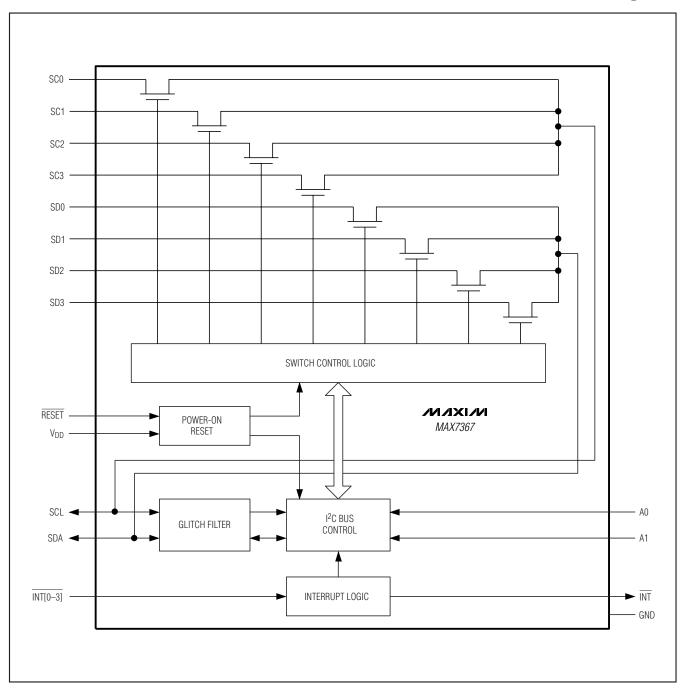

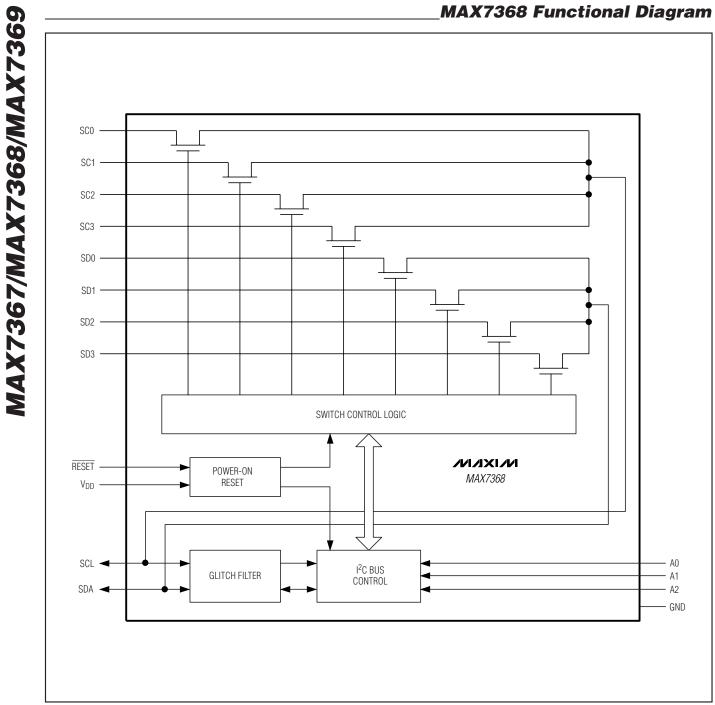

## \_MAX7367 Functional Diagram

MAX7367/MAX7368/MAX7369

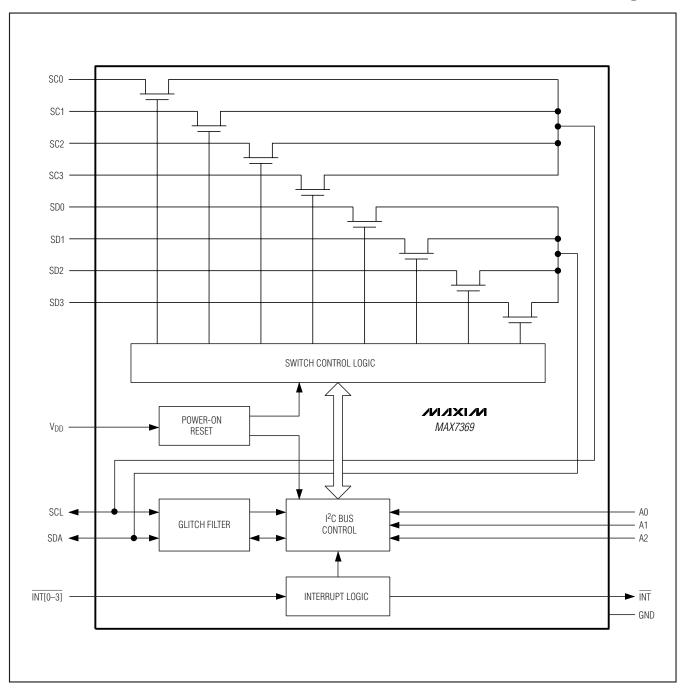

## \_MAX7369 Functional Diagram

MAX7367/MAX7368/MAX7369

### **Detailed Description**

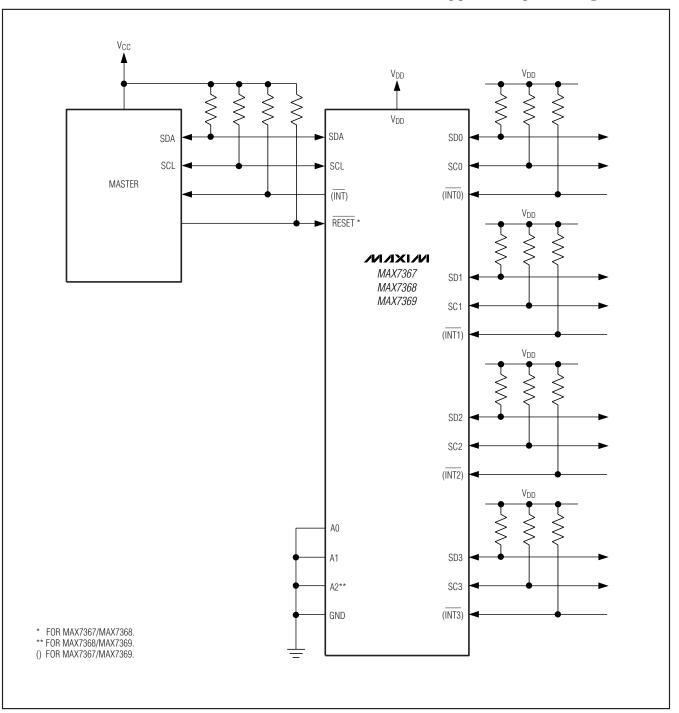

The MAX7367/MAX7368/MAX7369 bidirectional, fourchannel I<sup>2</sup>C switches/multiplexer expand the main I<sup>2</sup>C bus up to four extended buses. The MAX7369 is a 1:4 multiplexer that connects the main I<sup>2</sup>C bus to one channel at a time. The MAX7367/MAX7368 are four-channel switches that can connect the main I<sup>2</sup>C bus to one or more channels at a time. These devices isolate bus loading by separating available I<sup>2</sup>C devices into groups on the channels. The total loading capacitance of the main bus plus those of the connected channel must not exceed 400pF. The extended buses are connected or disconnected through the main I<sup>2</sup>C bus by writing to the control register of the MAX7367/MAX7368/MAX7369.

Any device connected to an I<sup>2</sup>C bus can transmit and receive signals. The MAX7367/MAX7368/MAX7369 are transparent to signals sent and received at each channel, allowing multiple masters on the buses. These devices are compatible with the I<sup>2</sup>C protocol of clock stretch, synchronization, and arbitration in case of multiple masters addressing the bus at the same time. The MAX7367/MAX7368 have a RESET input that allows external circuitry to set the MAX7367/MAX7368 to its default state anytime after the device has powered up. The MAX7367/MAX7369 have interrupt inputs, allowing devices on the extended bus to send an interrupt signal to the master on the main bus.

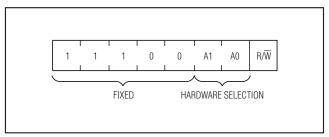

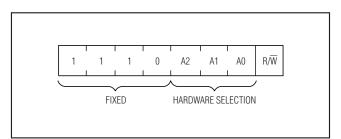

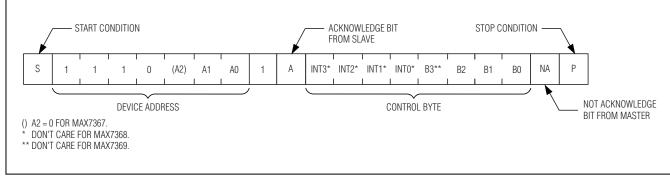

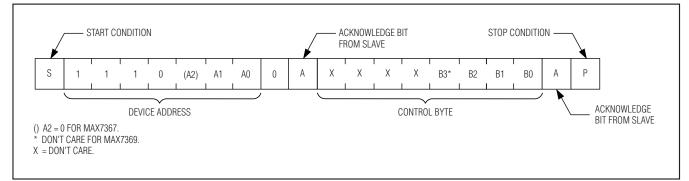

#### **Device Address**

The MAX7367/MAX7368/MAX7369 have selectable device addresses through external inputs. The MAX7367 slave address consists of 5 fixed bits (A6–A2, set to 11100), followed by 2 pin-programmable bits (A1 and A0), as shown in Figure 4. The MAX7368/MAX7369 slave address consists of 4 fixed bits (A6–A3, set to 1110), followed by 3 pin-programmable bits (A2, A1 and A0), as shown in Figure 5. The most significant address bit (A6) is transmitted first, followed by the remaining bits. The addresses A2 (for MAX7368/MAX7369), A1, and A0 can also be driven dynamically if required, but the values must be stable when they are expected in the address sequence.

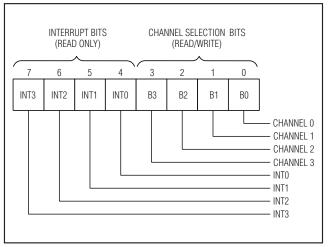

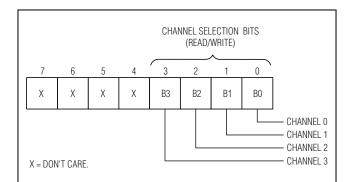

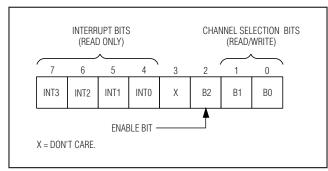

### **Control/Interrupt Register**

There is a control/interrupt register inside the MAX7367/ MAX7369 (Figures 6 and 8). There is a control (only) register inside the MAX7368 (Figure 7). Use the main I<sup>2</sup>C bus to write or read from this register. Following the successful acknowledgement of the slave address, the master bus sends a byte or the master bus receives a byte from/to the MAX7367/MAX7368/MAX7369. The last 3 bits (for the MAX7369) or 4 bits (for the MAX7367/MAX7368) of the byte are stored in the control/interrupt register (B0 to B2 or B0 to B3) for channel selection. If multiple bytes are received, only the last byte received is saved. The first four bits of the register represent the interrupt condition (for the MAX7367/MAX7367/MAX7369 only).

Figure 4. MAX7367 Slave Address

Figure 5. MAX7368/MAX7369 Slave Address

Figure 6. MAX7367 Control/Interrupt Register

Figure 7. MAX7368 Control Register

Figure 8. MAX7369 Control/Interrupt Register

#### **Channel Selection**

Each channel selected contains an SD\_ and SC\_ pair. Select a channel by writing a control byte after a successful acknowledge of the slave address. The last 4 bits of the control byte determine which channel(s) is selected for the MAX7367/MAX7368 as shown in Table 1. The last 3 bits of the control byte determine which channel is selected for the MAX7369 as shown in Table 2. The selected channels are activated after the stop condition. When a channel is selected, the respective SD\_/SC\_ pair is logic-high, ensuring no false conditions occur on the bus.

#### Interrupt Logic (MAX7367/MAX7369)

The MAX7367/MAX7369 have four interrupt inputs, one for each channel, and one INT output. The INT output is an open-drain output that requires a pullup resistor. The INT output is asserted by a low-logic signal on any of the INT\_ inputs, and it is deasserted only when all the INT\_ inputs are logic-high. Bits 4–7 of the MAX7367/MAX7369 control/interrupt register store the state of the INT\_ for each channel as shown in Table 3 and Figures 6 and 8. The logic level of INT\_ is not latched. Drive the respective INT\_ input high to remove the interrupt condition for the channel. An interrupt can occur on any channel, regardless of whether it is selected or not selected.

After a device generates an interrupt on one of the channels, the interrupt input is loaded into the control/interrupt register when a read is performed. To determine which device is generating the interrupt, read the contents of the control/interrupt register to determine which channel is issuing the interrupt, then write the appropriate command to the control/interrupt register to select the interrupted channel. Read from all devices on the interrupt.

# Table 1. MAX7367/MAX7368 Control Bitsfor Channel Selection

| CONTROL BIT | COMMAND                                                   |

|-------------|-----------------------------------------------------------|

| BO          | 0 = Channel 0 disabled (default)<br>1 = Channel 0 enabled |

| B1          | 0 = Channel 1 disabled (default)<br>1 = Channel 1 enabled |

| B2          | 0 = Channel 2 disabled (default)<br>1 = Channel 2 enabled |

| B3          | 0 = Channel 3 disabled (default)<br>1 = Channel 3 enabled |

# Table 2. MAX7369 Control Bits forChannel Selection

| B2 | B1 | B0 | COMMAND                       |

|----|----|----|-------------------------------|

| 0  | 0  | 0  | No channel selected (default) |

| 0  | Х  | Х  | No channel selected           |

| 1  | 0  | 0  | Channel 0 selected            |

| 1  | 0  | 1  | Channel 1 selected            |

| 1  | 1  | 0  | Channel 2 selected            |

| 1  | 1  | 1  | Channel 3 selected            |

# Table 3. MAX7367/MAX7369 InterruptIndicator Bits

| INTERRUPT BIT | STATE                                                           |

|---------------|-----------------------------------------------------------------|

| INTO          | 0 = No channel 0 interrupt (default)<br>1 = Channel 0 interrupt |

| INT1          | 0 = No channel 1 interrupt (default)<br>1 = Channel 1 interrupt |

| INT2          | 0 = No channel 2 interrupt (default)<br>1 = Channel 2 interrupt |

| INT3          | 0 = No channel 3 interrupt (default)<br>1 = Channel 3 interrupt |

### **RESET** Input (MAX7367/MAX7368)

The MAX7367/MAX7368 feature an active-low RESET input. When RESET is driven low for more than 4ns, the MAX7367/MAX7368 reset the internal register and  $I^2C$  state machine to their default states, allowing a master to recover from a bus fault condition.

### **Power-On Reset (POR)**

When power is applied to V<sub>DD</sub>, internal POR circuitry holds the MAX7367/MAX7368/MAX7369 in a reset state until V<sub>DD</sub> has reached the V<sub>POR</sub> threshold. At this point, the reset condition is released, and the MAX7367/MAX7368/MAX7369 register and I<sup>2</sup>C state machine are initialized to their default states (all zeroes), causing all the channels to be deselected.

#### **Voltage Translation**

The MAX7367/MAX7368/MAX7369 can be used as a voltage translator from the main bus to the extended buses. The output voltage (V<sub>PASS</sub>) is limited by the supply voltage (V<sub>DD</sub>) (see the *Typical Operation Characteristics*). For the MAX7367/MAX7368/MAX7369 to be used as a voltage translator, the V<sub>PASS</sub> voltage should be lower than or equal to the lowest bus voltage.

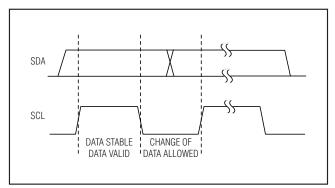

**I<sup>2</sup>C Interface** The MAX7367/MAX7368/MAX7369 feature an I<sup>2</sup>C-compatible, 2-wire serial interface consisting of a bidirectional serial-data line (SDA) and a serial-clock line (SCL). The master (typically a microcontroller) initiates data transfer on the bus and generates the SCL.

#### Bit Transfer

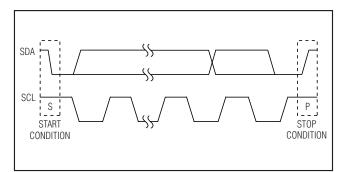

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable while SCL is high (Figure 9).

### Start and Stop Conditions

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning the SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 10).

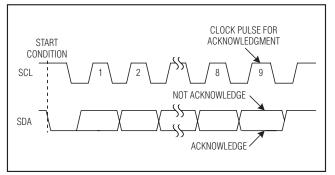

#### Acknowledge Bit

Successful data transfers are acknowledged with an acknowledge bit (A) or a not-acknowledge bit (NA). Both the master and the MAX7367/MAX7368/MAX7369 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the

high period of the clock pulse (Figure 11). In the case of an unsuccessful data transfer, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse and leaves it high during the high period of the clock pulse.

Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the master should reattempt communication at a later time.

Figure 9. Bit Transfer

Figure 10. Start and Stop Conditions

Figure 11. Acknowledge

#### Serial Addressing

A master initiates communication with a slave device by issuing a START condition followed by a slave address byte. The slave address byte consists of 7 address bits and a read/write bit ( $R/\overline{W}$ ). When idle, the MAX7367/MAX7368/MAX7369 continuously wait for a START condition followed by its slave address. After recognizing a start condition followed by the correct address, the MAX7367/MAX7368/MAX7369 are ready to accept or send data. The least significant bit (LSB) of the address byte (R/W) determines whether the master is writing to or reading from the MAX7367/MAX7368/ MAX7369 (R/ $\overline{W}$  = 0 selects a write command, R/ $\overline{W}$  = 1 selects a read command as shown in Figures 12 and 13). After receiving the proper address, the MAX7367/MAX7368/MAX7369 (slave) issue an ACK by pulling SDA low for one clock cycle.

### **Applications Information**

### **Repeated Slave Addresses**

The MAX7367/MAX7368/MAX7369 allow systems to reuse slave addresses individually on each channel of the extended bus. To reuse slave addresses on the extended bus channels of the MAX7367/MAX7368, ensure no more than one channel with a reused address is selected at the same time.

#### **Power-Supply Considerations**

The MAX7367/MAX7368/MAX7369 operate from a +2.3V to +5.5V power-supply voltage. Good power-supply decoupling is needed to maintain the performance of these parts. Bypass V<sub>DD</sub> to GND with a 0.1 $\mu$ F surface-mount ceramic capacitor. Mount the bypass capacitor as close as possible to the device.

Figure 12. Read Command

Figure 13. Write Command

### **Choosing Pullup Resistors**

I<sup>2</sup>C requires pullup resistors to provide a logic-high level to data and clock lines. There are tradeoffs between power dissipation and speed, and a compromise must be made in choosing pullup resistor values. Every device connected to the bus introduces some capacitance even when the device is not in operation. I<sup>2</sup>C specifies 300ns rise times to go from low to high (30% to 70%) for fast mode, which is defined for a data rate of 400kbps (refer to I<sup>2</sup>C specifications for details). In order to meet the rise time requirement, choose the pullup resistors such that the rise time (t<sub>R</sub> = 0.85R<sub>PULLUP</sub> x C<sub>BUS</sub>) is less than 300ns. For a bus capacitance of 400pF, choose a pullup resistor less than 880 $\Omega$ . Often I<sup>2</sup>C devices work when the maximum specified rise time is exceeded. However, if the rise times become too slow, the devices on the bus do not recognize the command signals. Optional resistors (24 $\Omega$ ) in series with SDA and SCL protect the device inputs from high-voltage spikes on the bus lines and also minimize crosstalk and undershoot of the bus signals.

**Chip Information**

PROCESS: BICMOS

### **Pin Configurations (continued)**

**Typical Operating Circuit**

MAX7367/MAX7368/MAX7369

### **Package Information**

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 20 TSSOP     | U20-3        | <u>21-0066</u> |

| 16 TSSOP     | U16-1        | <u>21-0066</u> |

## **Revision History**

| REVISION | REVISION | DESCRIPTION                            | PAGES CHANGED |

|----------|----------|----------------------------------------|---------------|

| 0        | 10/06    | Initial release of the MAX7369         | —             |

| 1        | 12/06    | Initial release of the MAX7367/MAX7368 | 1             |

| 2        | 2/09     | Changed the minimum $V_{IL}$ spec      | 2–5           |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2009 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

\_\_\_\_ 19