Power Matters.\*

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

www.microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revis | ion His          | story                                                         | 1   |

|---|-------|------------------|---------------------------------------------------------------|-----|

|   | 1.1   | Revisio          | on 11.0                                                       | 1   |

|   | 1.2   |                  | on 10.0                                                       |     |

|   | 1.3   |                  | on 9.0                                                        |     |

|   | 1.4   |                  | on 8.0                                                        |     |

|   |       |                  |                                                               |     |

|   | 1.5   |                  | on 7.0                                                        |     |

|   | 1.6   |                  | on 6.0                                                        |     |

|   | 1.7   |                  | on 5.0                                                        |     |

|   | 1.8   |                  | on 4.0                                                        |     |

|   | 1.9   | Revisio          | on 3.0                                                        | 3   |

|   | 1.10  | Revisio          | on 2.0                                                        | 3   |

|   | 1.11  | Revisio          | on 1.0                                                        | 3   |

| 2 | IGLO  | O2 FP            | GA and SmartFusion2 SoC FPGA                                  | 4   |

| _ | 2.1   |                  | Status                                                        |     |

|   | 2.2   | Referer          | nces                                                          | 5   |

|   | 2.3   |                  | cal Specifications                                            |     |

|   | 2.0   | 2.3.1            | Operating Conditions                                          |     |

|   |       | 2.3.2            | Power Consumption                                             |     |

|   |       | 2.3.3            | Average Fabric Temperature and Voltage Derating Factors       |     |

|   |       | 2.3.4            | Timing Model                                                  |     |

|   |       | 2.3.5            | User I/O Characteristics                                      |     |

|   |       | 2.3.6            | Logic Element Specifications                                  |     |

|   |       | 2.3.7            | Global Resource Characteristics                               |     |

|   |       | 2.3.8            | FPGA Fabric SRAM                                              |     |

|   |       | 2.3.9            | Programming Times                                             |     |

|   |       | 2.3.10<br>2.3.11 | Math Block Timing Characteristics                             |     |

|   |       | 2.3.11           | SRAM PUF                                                      |     |

|   |       | 2.3.13           | Non-Deterministic Random Bit Generator (NRBG) Characteristics |     |

|   |       | 2.3.14           | Cryptographic Block Characteristics                           |     |

|   |       | 2.3.15           | Crystal Oscillator                                            |     |

|   |       | 2.3.16           | On-Chip Oscillator                                            |     |

|   |       | 2.3.17           | Clock Conditioning Circuits (CCC)                             |     |

|   |       | 2.3.18           | JTAG                                                          |     |

|   |       | 2.3.19           | System Controller SPI Characteristics                         |     |

|   |       | 2.3.20           | Power-up to Functional Times                                  |     |

|   |       | 2.3.21           | DEVRST_N Characteristics                                      |     |

|   |       | 2.3.22           | DEVRST_N to Functional Times                                  |     |

|   |       |                  | Flash*Freeze Timing Characteristics                           |     |

|   |       | 2.3.24<br>2.3.25 | DDR Memory Interface Characteristics                          |     |

|   |       | 2.3.26           | SerDes Electrical and Timing AC and DC Characteristics        |     |

|   |       | 2.3.27           | SmartFusion2 Specifications                                   |     |

|   |       | 2.3.28           | CAN Controller Characteristics                                |     |

|   |       | 2.3.29           | USB Characteristics                                           |     |

|   |       | 2.3.30           | MMUART Characteristics                                        |     |

|   |       | 2.3.31           | IGLOO2 Specifications                                         | 129 |

# **Figures**

| Figure 1  | High Tomporature Data Potention (HTP)                             | 0   |

|-----------|-------------------------------------------------------------------|-----|

| J         | High Temperature Data Retention (HTR)                             |     |

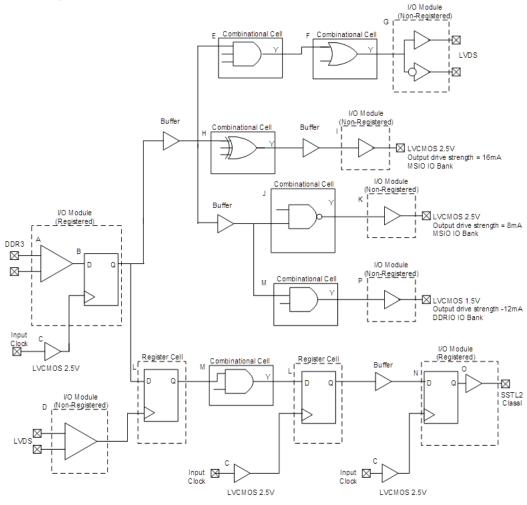

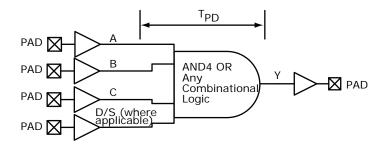

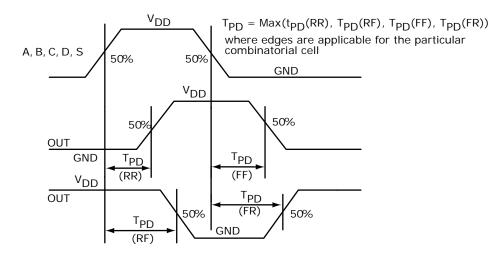

| Figure 2  | Timing Model                                                      |     |

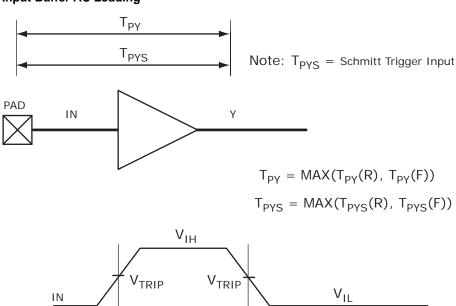

| Figure 3  | Input Buffer AC Loading                                           | 17  |

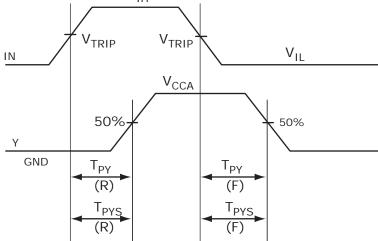

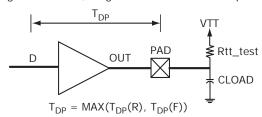

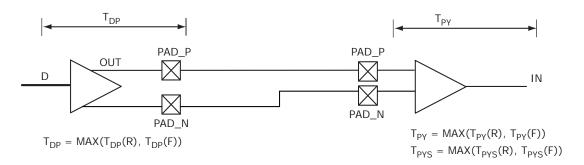

| Figure 4  | Output Buffer AC Loading                                          | 18  |

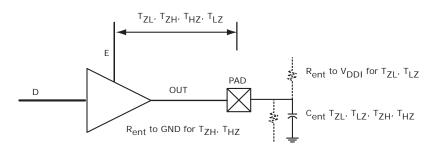

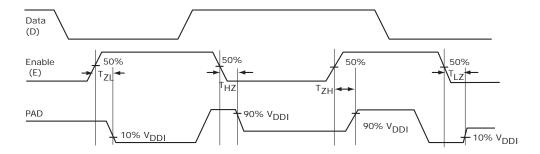

| Figure 5  | Tristate Buffer for Enable Path Test Point                        | 19  |

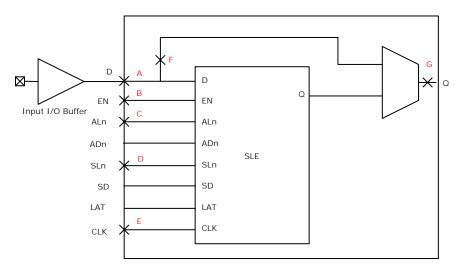

| Figure 6  | Timing Model for Input Register                                   | 65  |

| Figure 7  | I/O Register Input Timing Diagram                                 | 66  |

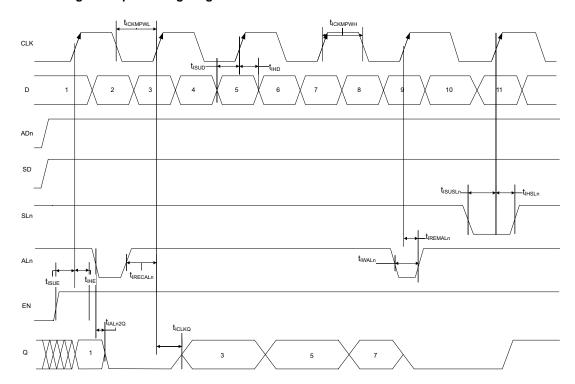

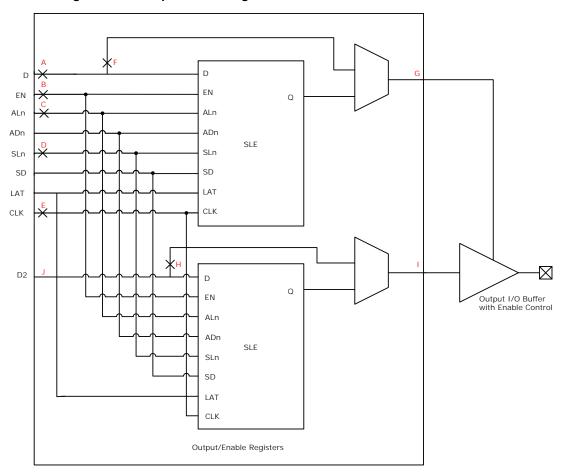

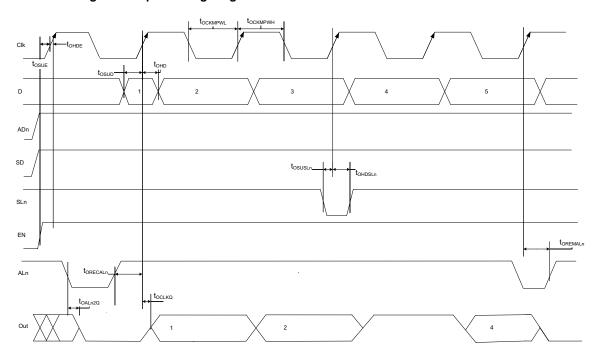

| Figure 8  | Timing Model for Output/Enable Register                           | 68  |

| Figure 9  | I/O Register Output Timing Diagram                                | 69  |

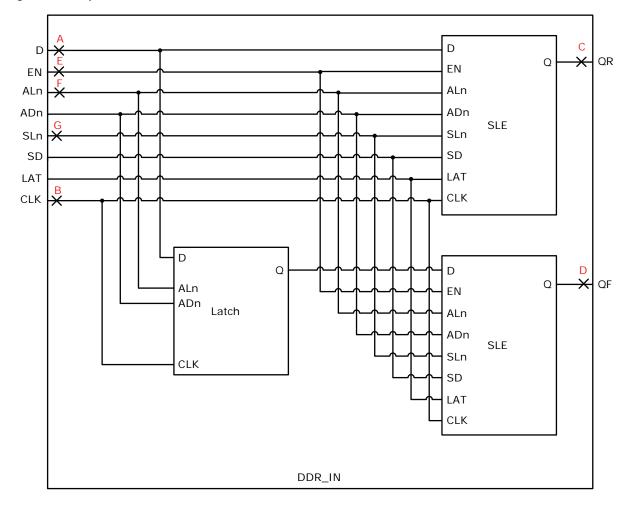

| Figure 10 | Input DDR Module                                                  | 70  |

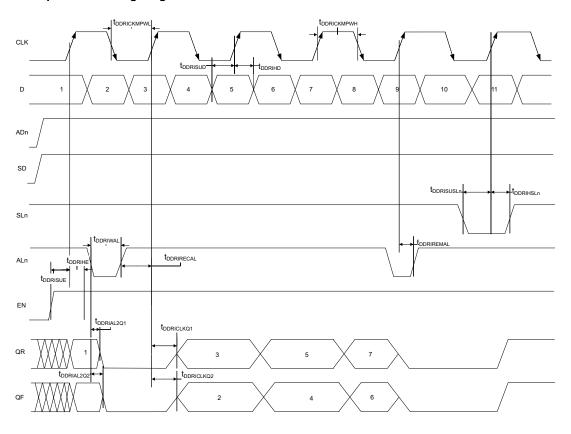

| Figure 11 | Input DDR Timing Diagram                                          | 71  |

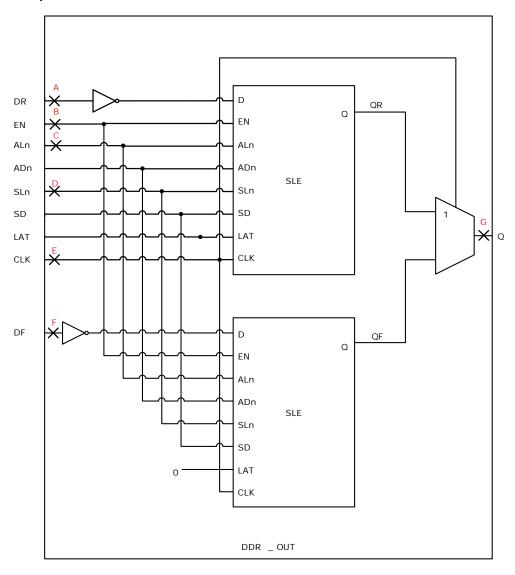

| Figure 12 | Output DDR Module                                                 | 73  |

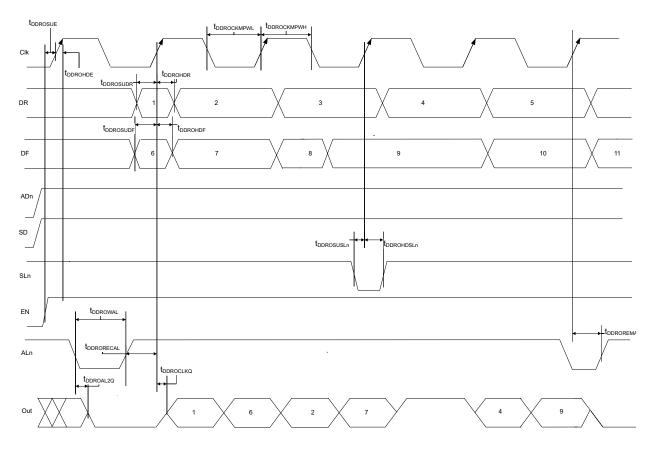

| Figure 13 | Output DDR Timing Diagram                                         | 74  |

| Figure 14 | LUT-4                                                             | 75  |

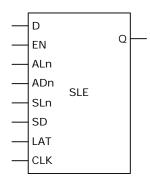

| Figure 15 | Sequential Module                                                 | 76  |

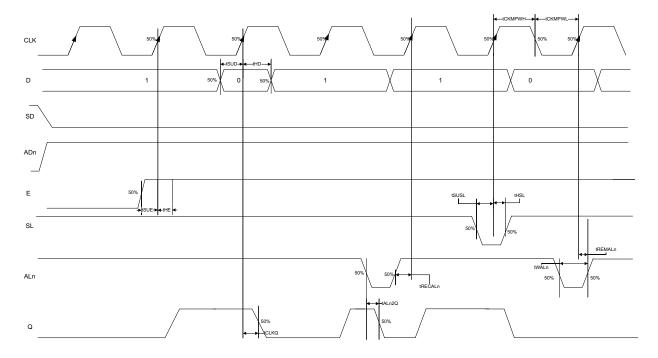

| Figure 16 | Sequential Module Timing Diagram                                  | 77  |

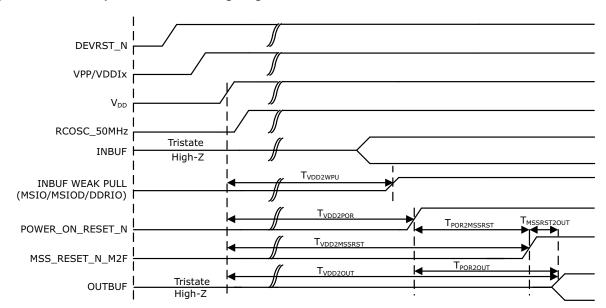

| Figure 17 | Power-up to Functional Timing Diagram for SmartFusion2            | 115 |

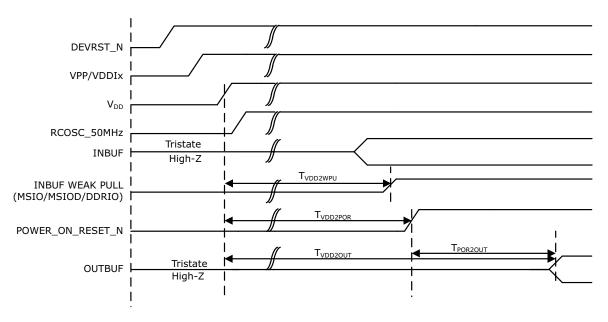

| Figure 18 | Power-up to Functional Timing Diagram for IGLOO2                  | 116 |

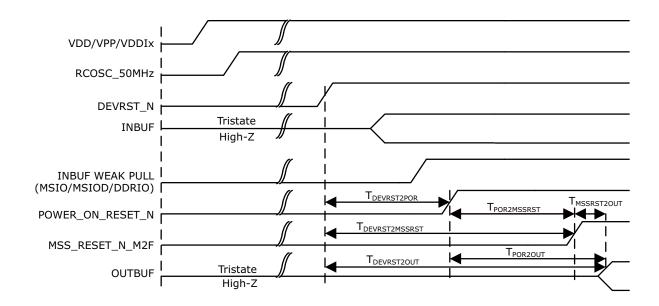

| Figure 19 | DEVRST_N to Functional Timing Diagram for SmartFusion2            | 117 |

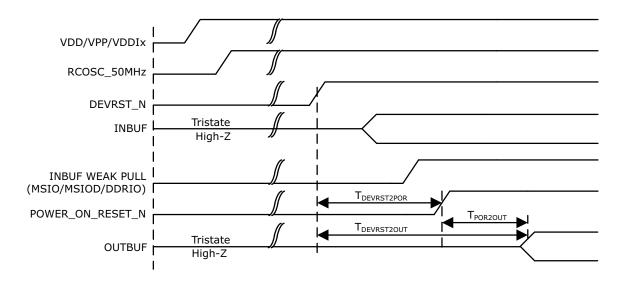

| Figure 20 | DEVRST_N to Functional Timing Diagram for IGLOO2                  | 119 |

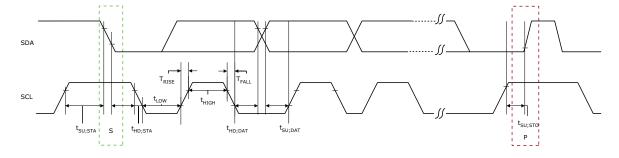

| Figure 21 | I2C Timing Parameter Definition                                   | 125 |

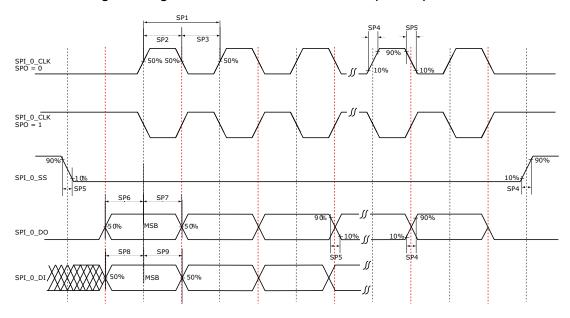

| Figure 22 | SPI Timing for a Single Frame Transfer in Motorola Mode (SPH = 1) | 128 |

| Figure 23 | SPI Timing for a Single Frame Transfer in Motorola Mode (SPH = 1) | 131 |

# **Tables**

| Table 1<br>Table 2 | IGLOO2 and SmartFusion2 Design Security Densities                                                | . 4  |

|--------------------|--------------------------------------------------------------------------------------------------|------|

| Table 3            | Absolute Maximum Ratings                                                                         |      |

| Table 4            | Recommended Operating Conditions                                                                 |      |

| Table 5            | FPGA Operating Limits                                                                            |      |

| Table 6            | Embedded Operating Flash Limits                                                                  |      |

| Table 7            | Device Storage Temperature and Retention                                                         |      |

| Table 8            | High Temperature Data Retention (HTR) Lifetime                                                   | . 8  |

| Table 9            | Package Thermal Resistance of SmartFusion2 and IGLOO2 Devices                                    | . 10 |

| Table 10           | Quiescent Supply Current Characteristics                                                         |      |

| Table 11           | SmartFusion2 and IGLOO2 Quiescent Supply Current (V <sub>DD</sub> = 1.2 V) – Typical Process     |      |

| Table 12           | Currents During Program Cycle, 0 °C < = T <sub>J</sub> <= 85 °C – Typical Process                | . 13 |

| Table 13           | Currents During Verify Cycle, 0 °C <= T <sub>J</sub> <= 85 °C – Typical Process                  | . 13 |

| Table 14           | SmartFusion2 and IGLOO2 Quiescent Supply Current (V <sub>DD</sub> = 1.26 V) – Worst-Case Process | . 13 |

| Table 15           | Average Junction Temperature and Voltage Derating Factors for Fabric Timing Delays               | . 14 |

| Table 16           | Inrush Currents at Power up, –40 °C <= T <sub>J</sub> <= 100 °C – Typical Process                | . 14 |

| Table 17           | Timing Model Parameters                                                                          |      |

| Table 18           | Maximum Data Rate Summary Table for Single-Ended I/O in Worst-Case Industrial Conditions .       | . 19 |

| Table 19           | Maximum Data Rate Summary Table for Voltage-Referenced I/O in Worst-Case Industrial Conditions   |      |

| Table 20           | Maximum Data Rate Summary Table for Differential I/O in Worst-Case Industrial Conditions         | 20   |

| Table 21           | Maximum Frequency Summary Table for Single-Ended I/O in Worst-Case Industrial Conditions .       | 20   |

| Table 22           | Maximum Frequency Summary Table for Voltage-Referenced I/O in Worst-Case Industrial Conditions   | 21   |

| Table 23           | Maximum Frequency Summary Table for Differential I/O in Worst-Case Industrial Conditions         |      |

| Table 24           | Input Capacitance, Leakage Current, and Ramp Time                                                |      |

| Table 25           | I/O Weak Pull-up/Pull-down Resistances for DDRIO I/O Bank                                        |      |

| Table 26           | I/O Weak Pull-Up/Pull-Down Resistances for MSIO I/O Bank                                         |      |

| Table 27           | I/O Weak Pull-up/Pull-down Resistances for MSIOD I/O Bank                                        |      |

| Table 28           | Schmitt Trigger Input Hysteresis                                                                 |      |

| Table 29           | LVTTL/LVCMOS 3.3 V DC Recommended DC Operating Conditions (Applicable to MSIO I/O                |      |

|                    | Bank Only)                                                                                       | 24   |

| Table 30           | LVTTL/LVCMOS 3.3 V Input Voltage Specification (Applicable to MSIO I/O Bank Only)                | 24   |

| Table 31           | LVCMOS 3.3 V DC Output Voltage Specification (Applicable to MSIO I/O Bank Only)                  |      |

| Table 32           | LVTTL 3.3 V DC Output Voltage Specification (Applicable to MSIO I/O Bank Only)                   |      |

| Table 33           | LVTTL/LVCMOS 3.3 V AC Maximum Switching Speed (Applicable to MSIO I/O Bank Only)                 |      |

| Table 34           | LVTTL/LVCMOS 3.3 V Receiver Characteristics for MSIO I/O Bank (Input Buffers)                    |      |

| Table 35           | LVTTL/LVCMOS 3.3 V Transmitter Characteristics for MSIO I/O Bank (Output and                     |      |

|                    | Tristate Buffers)                                                                                | 25   |

| Table 36           | LVTTL/LVCMOS 3.3 V AC Test Parameter Specifications (Applicable to MSIO I/O Bank Only)           |      |

| Table 37           | LVTTL/LVCMOS 3.3 V Transmitter Drive Strength Specifications for MSIO I/O Bank                   | 25   |

| Table 38           | LVCMOS 2.5 V DC Recommended DC Operating Conditions                                              | 26   |

| Table 39           | LVCMOS 2.5 V DC Input Voltage Specification                                                      |      |

| Table 40           | LVCMOS 2.5 V DC Output Voltage Specification                                                     |      |

| Table 41           | LVCMOS 2.5 V AC Minimum and Maximum Switching Speed                                              |      |

| Table 42           | LVCMOS 2.5 V AC Calibrated Impedance Option                                                      |      |

| Table 43           | LVCMOS 2.5 V Receiver Characteristics (Input Buffers)                                            |      |

| Table 44           | LVCMOS 2.5 V Transmitter Characteristics for DDRIO Bank (Output and Tristate Buffers)            | 27   |

| Table 45           | LVCMOS 2.5 V AC Test Parameter Specifications                                                    |      |

| Table 46           | LVCMOS 2.5 V Transmitter Drive Strength Specifications                                           | 27   |

| Table 47           | LVCMOS 2.5 V Transmitter Characteristics for MSIO Bank (Output and Tristate Buffers)             | 28   |

| Table 48           | LVCMOS 1.8 V DC Recommended Operating Conditions                                                 |      |

| Table 49           | LVCMOS 1.8 V DC Input Voltage Specification                                                      |      |

| Table 50           | LVCMOS 1.8 V DC Output Voltage Specification                                                     |      |

| Table 51   | LVCMOS 1.8 V Minimum and Maximum AC Switching Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 52   | LVCMOS 2.5 V Transmitter Characteristics for MSIOD Bank (Output and Tristate Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| Table 53   | LVCMOS 1.8 V Receiver Characteristics (Input Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 30 |

| Table 54   | LVCMOS 1.8 V AC Calibrated Impedance Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 30 |

| Table 55   | LVCMOS 1.8 V AC Test Parameter Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Table 56   | LVCMOS 1.8 V Transmitter Drive Strength Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 30 |

| Table 57   | LVCMOS 1.8 V Transmitter Characteristics for DDRIO I/O Bank with Fixed Code (Output and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|            | Tristate Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| Table 58   | LVCMOS 1.5 V DC Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| Table 59   | LVCMOS 1.5 V DC Input Voltage Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 32 |

| Table 60   | LVCMOS 1.8 V Transmitter Characteristics for MSIO I/O Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Table 61   | LVCMOS 1.8 V Transmitter Characteristics for MSIOD I/O Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 32 |

| Table 62   | LVCMOS 1.5 V DC Output Voltage Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 33 |

| Table 63   | LVCMOS 1.5 V AC Minimum and Maximum Switching Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 33 |

| Table 64   | LVCMOS 1.5 V AC Calibrated Impedance Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 33 |

| Table 65   | LVCMOS 1.5 V AC Test Parameter Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Table 66   | LVCMOS 1.5 V Transmitter Drive Strength Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Table 67   | LVCMOS 1.5 V Receiver Characteristics for DDRIO I/O Bank with Fixed Codes (Input Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 34 |

| Table 68   | LVCMOS 1.5 V Receiver Characteristics for MSIO I/O Bank (Input Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 34 |

| Table 69   | LVCMOS 1.5 V Receiver Characteristics for MSIOD I/O Bank (Input Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Table 70   | LVCMOS 1.5 V Transmitter Characteristics for DDRIO I/O Bank (Output and Tristate Buffers) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Table 71   | LVCMOS 1.5 V Transmitter Characteristics for MSIO I/O Bank (Output and Tristate Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Table 72   | LVCMOS 1.2 V DC Recommended DC Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Table 73   | LVCMOS 1.2 V DC Input Voltage Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Table 74   | LVCMOS 1.2 V DC Output Voltage Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Table 75   | LVCMOS 1.2 V Minimum and Maximum AC Switching Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Table 76   | LVCMOS 1.5 V Transmitter Characteristics for MSIOD I/O Bank (Output and Tristate Buffers) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Table 77   | LVCMOS 1.2 V Receiver Characteristics for DDRIO I/O Bank with Fixed Code (Input Buffers) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Table 78   | LVCMOS 1.2 V Receiver Characteristics for MSIO I/O Bank (Input Buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |