### **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| V <sub>IN</sub> Voltage               | 16V            |

|---------------------------------------|----------------|

| SW1, SW2 Voltage                      |                |

| FB1N, FB1P, FB2N, FB2P Voltage12      |                |

| SHDN/SS1, SHDN/SS2 Voltage            | 16V            |

| V <sub>REF</sub> Voltage              | 1.5V           |

| Maximum Junction Temperature          | 125°C          |

| Operating Temperature Range (Note 2). | 40°C to 85°C   |

| Storage Temperature Range             | –65°C to 125°C |

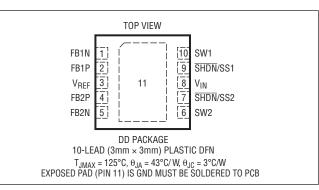

### **PIN CONFIGURATION**

### **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL   | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|-----------------|--------------|---------------------------------|-------------------|

| LT3471EDD#PBF     | LT3471EDD#TRPBF | LBHM         | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LEAD BASED FINISH | TAPE AND REEL   | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

| LT3471EDD         | LT3471EDD#TR    | LBHM         | 10-Lead (3mm × 3mm) Plastic DFN | –40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ .  $V_{IN} = V_{SHDN} = 3V$  unless otherwise noted.

| PARAMETER                         | CONDITIONS                                                                           |   | MIN            | ТҮР          | MAX            | UNITS   |

|-----------------------------------|--------------------------------------------------------------------------------------|---|----------------|--------------|----------------|---------|

| Minimum Operating Voltage         |                                                                                      |   |                | 2.1          | 2.4            | V       |

| Reference Voltage                 |                                                                                      | • | 0.991<br>0.987 | 1.000        | 1.009<br>1.013 | V<br>V  |

| Reference Voltage Current Limit   | (Note 3)                                                                             |   | 1              | 1.4          |                | mA      |

| Reference Voltage Load Regulation | $0mA \le I_{REF} \le 100\mu A$ (Note 3)                                              |   |                | 0.1          | 0.2            | %/100µA |

| Reference Voltage Line Regulation | $2.6V \le V_{IN} \le 16V$                                                            |   |                | 0.03         | 0.08           | %/V     |

| Error Amplifier Offset            | Transition from Not Switching to Switching, V <sub>FBP</sub> = V <sub>FBN</sub> = 1V |   |                | ±2           | ±3             | mV      |

| FB Pin Bias Current               | V <sub>FB</sub> = 1V (Note 3)                                                        | • |                | 60           | 100            | nA      |

| Quiescent Current                 | V <sub>SHDN</sub> = 1.8V, Not Switching                                              |   |                | 2.5          | 4              | mA      |

| Quiescent Current in Shutdown     | $V_{\overline{SHDN}} = 0.3V, V_{IN} = 3V$                                            |   |                | 0.01         | 1              | μA      |

| Switching Frequency               |                                                                                      |   | 1              | 1.2          | 1.4            | MHz     |

| Maximum Duty Cycle                |                                                                                      | • | 90<br>86       | 94           |                | %<br>%  |

| Minimum Duty Cycle                |                                                                                      |   |                | 15           |                | %       |

| Switch Current Limit              | At Minimum Duty Cycle<br>At Maximum Duty Cycle (Note 4)                              |   | 1.5<br>0.9     | 2.05<br>1.45 | 2.6<br>2.0     | A<br>A  |

| Switch V <sub>CESAT</sub>         | I <sub>SW</sub> = 0.5A (Note 5)                                                      |   |                | 150          | 250            | mV      |

| Switch Leakage Current            | V <sub>SW</sub> = 5V                                                                 |   |                | 0.01         | 1              | μA      |

| SHDN/SS Input Voltage High        |                                                                                      |   | 1.8            |              |                | V       |

|                                   |                                                                                      |   |                |              |                | 3471fb  |

# **ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply temperature range, otherwise specifications are $T_A = 25^{\circ}C$ . $V_{IN} = V_{SHDN} = 3V$ unless otherwise noted.

The • denotes specifications which apply over the full operating

| PARAMETER CONDITIONS   |                                                                       |  | MIN | ТҮР     | MAX       | UNITS    |

|------------------------|-----------------------------------------------------------------------|--|-----|---------|-----------|----------|

| SHDN Input Voltage Low | Quiescent Current $\leq 1\mu A$                                       |  |     |         | 0.3       | V        |

| SHDN Pin Bias Current  | $V_{\overline{SHDN}} = 3V, V_{IN} = 4V$<br>$V_{\overline{SHDN}} = 0V$ |  |     | 22<br>0 | 36<br>0.1 | μA<br>μA |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LT3471E is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the -40°C to 85°C operating

temperature range are assured by design, characterization and correlation with statistical process controls.

Note 3: Current flows out of the pin.

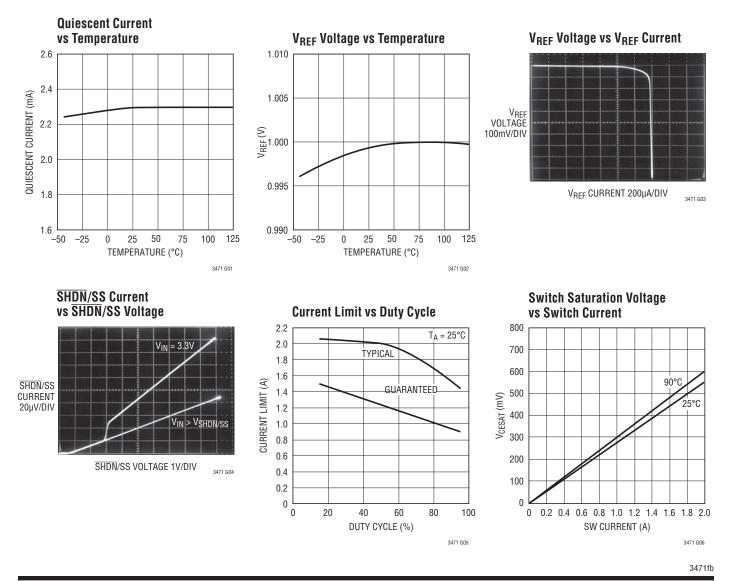

Note 4: See Typical Performance Characteristics for guaranteed current limit vs duty cycle.

Note 5: V<sub>CESAT</sub> is 100% tested at wafer level only.

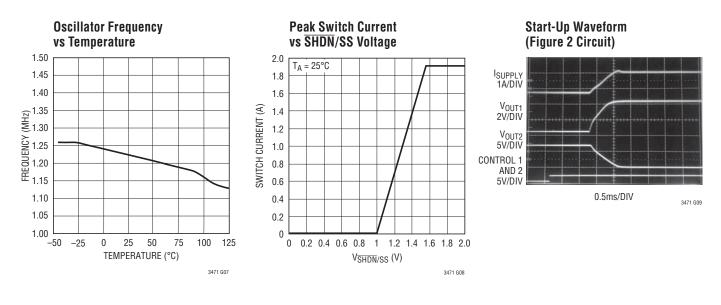

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### PIN FUNCTIONS

**FB1N (Pin 1):** Negative Feedback Pin for Switcher 1. Connect resistive divider tap here. Minimize trace area at FB1N. Set  $V_{OUT} = V_{FB1P}(1 + R1/R2)$ , or connect to ground for inverting topologies.

**FB1P (Pin 2):** Positive Feedback Pin for Switcher 1. Connect either to  $V_{REF}$  or a divided down version of  $V_{REF}$ , or connect to a resistive divider tap for inverting topologies.

$V_{REF}$  (Pin 3): 1.00V Reference Pin. Can supply up to 1mA of current. Do not pull this pin high. Must be locally bypassed with *no less than 0.01µF and no more than 1µF*. A 0.1µF ceramic capacitor is recommended. Use this pin as the positive feedback reference or connect a resistor divider here for a smaller reference voltage.

FB2P (Pin 4): Same as FB1P but for Switcher 2.

FB2N (Pin 5): Same as FB1N but for Switcher 2.

**SW2 (Pin 6):** Switch Pin for Switcher 2 (Collector of internal NPN power switch). Connect inductor/diode here

and minimize the metal trace area connected to this pin to minimize EMI.

**SHDN/SS2 (Pin 7):** Shutdown and Soft-Start Pin. Tie to 1.8V or more to enable device. Ground to shut down. Soft-start function is provided when the voltage at this pin is ramped slowly to 1.8V with an external RC circuit.

VIN (Pin 8): Input Supply. Must be locally bypassed.

**SHDN/SS1 (Pin 9):** Same as SHDN/SS2 but for Switcher 1. Note: taking either SHDN/SS pin high will enable the part. Each switcher is individually enabled with its respective SHDN/SS pin.

SW1 (Pin 10): Same as SW2 but for Switcher 1.

**Exposed Pad (Pin 11):** Ground. Connect directly to local ground plane. This ground plane also serves as a heat sink for optimal thermal performance.

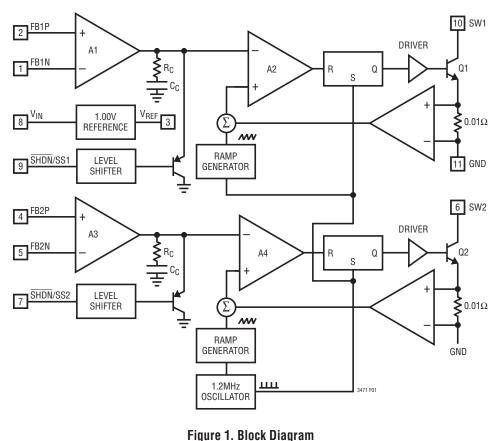

#### **BLOCK DIAGRAM**

OPERATION

The LT3471 uses a constant frequency, current mode control scheme to provide excellent line and load regulation. Refer to the Block Diagram. At the start of each oscillator cycle, the SR latch is set, which turns on the power switch, Q1 (Q2). A voltage proportional to the switch current is added to a stabilizing ramp and the resulting sum is fed into the positive terminal of the PWM comparator A2 (A4). When this voltage exceeds the level at the negative input of A2 (A4), the SR latch is reset, turning off the power switch Q1 (Q2). The level at the negative input of A2 (A4) is set by the error amplifier A1 (A3) and is simply an amplified version of the difference between the negative feedback voltage and the positive feedback voltage, usually tied to the reference voltage V<sub>REG</sub>. In this manner, the error amplifier sets the correct peak current level to keep the output in regulation. If the error amplifier's output increases, more current is delivered to

the output. Similarly, if the error decreases, less current is delivered. Each switcher functions independently but they share the same oscillator and thus the switchers are always in phase. Enabling the part is done by taking either SHDN/SS pin above 1.8V. Disabling the part is done by grounding both SHDN/SS pins. The soft-start feature of the LT3471 allows for clean start-up conditions by limiting the amount of voltage rise at the output of comparator A1 and A2, which in turn limits the peak switching current. The soft-start feature for each switcher is enabled by slowly ramping that switcher's SHDN/SS pin, using an RC network, for example. Typical resistor and capacitor values are 0.33µF and 4.7k, allowing for a start-up time on the order of milliseconds. The LT3471 has a current limit circuit not shown in the Block Diagram. The switch current is constantly monitored and not allowed to exceed the maximum switch current (typically 1.6A). If the switch 3471fb

## OPERATION

current reaches this value, the SR latch is reset regardless of the state of the comparator A2 (A4). Also not shown in the Block Diagram is the thermal shutdown circuit. If the temperature of the part exceeds approximately 160°C, both latches are reset regardless of the state of comparators A2 and A4. The current limit and thermal shutdown circuits protect the power switch as well as the external components connected to the LT3471.

### **APPLICATIONS INFORMATION**

#### **Duty Cycle**

The typical maximum duty cycle of the LT3471 is 94%. The duty cycle for a given application is given by:

$$DC = \frac{|V_{OUT}| + |V_D| - |V_{IN}|}{|V_{OUT}| + |V_D| - |V_{CESAT}|}$$

Where  $V_D$  is the diode forward voltage drop and  $V_{\mbox{CESAT}}$  is in the worst case 330mV (at 1.3A)

The LT3471 can be used at higher duty cycles, but it must be operated in the discontinuous conduction mode so that the actual duty cycle is reduced.

#### Setting Output Voltage

Setting the output voltage depends on the topology used. For normal noninverting boost regulator topologies:

$$V_{OUT} = V_{FBP} \left( 1 + \frac{R1}{R2} \right)$$

where  $V_{\text{FBN}}$  is connected between R1 and R2 (see the Typical Applications section for examples).

Select values of R1 and R2 according to the following equation:

$$R1 = R2 \left[ \left( \frac{V_{OUT}}{V_{REF}} \right) - 1 \right]$$

A good value for R2 is 15k which sets the current in the resistor divider chain to  $1.00V/15k = 67\mu A$ .

$V_{FBP}$  is usually just tied to  $V_{REF} = 1.00V$ , but  $V_{FBP}$  can also be tied to a divided down version of  $V_{REF}$  or some other voltage as long as the absolute maximum ratings for the feedback pins are not exceeded (see Absolute Maximum Ratings). For inverting topologies,  $V_{FBN}$  is tied to ground and  $V_{FBP}$  is connected between R1 and R2. R2 is between  $V_{FBP}$  and  $V_{REF}$  and R1 is between  $V_{FBP}$  and  $V_{OUT}$  (see the Applications section for examples). In this case:

$$V_{OUT} = V_{REF} \left( \frac{R1}{R2} \right)$$

Select values of R1 and R2 according to the following equation:

$$R1 = R2 \left( \frac{V_{OUT}}{V_{REF}} \right)$$

A good value for R2 is 15k, which sets the current in the resistor divider chain to  $1.00V/15k = 67\mu A$ .

#### Switching Frequency and Inductor Selection

The LT3471 switches at 1.2 MHz, allowing for small valued inductors to be used. 4.7 $\mu$ H or 10 $\mu$ H will usually suffice. Choose an inductor that can handle at least 1.4A without saturating, and ensure that the inductor has a low DCR (copper-wire resistance) to minimize I<sup>2</sup>R power losses. Note that in some applications, the current handling requirements of the inductor can be lower, such as in the SEPIC topology where each inductor only carries one half of the total switch current. For better efficiency, use similar valued inductors with a larger volume. Many different sizes and shapes are available from various manufacturers. Choose a core material that has low losses at 1.2 MHz, such as ferrite core.

#### Table 1. Inductor Manufacturers

| Sumida | (847) 956-0666 | www.sumida.com |

|--------|----------------|----------------|

| TDK    | (847) 803-6100 | www.tdk.com    |

| Murata | (714) 852-2001 | www.murata.com |

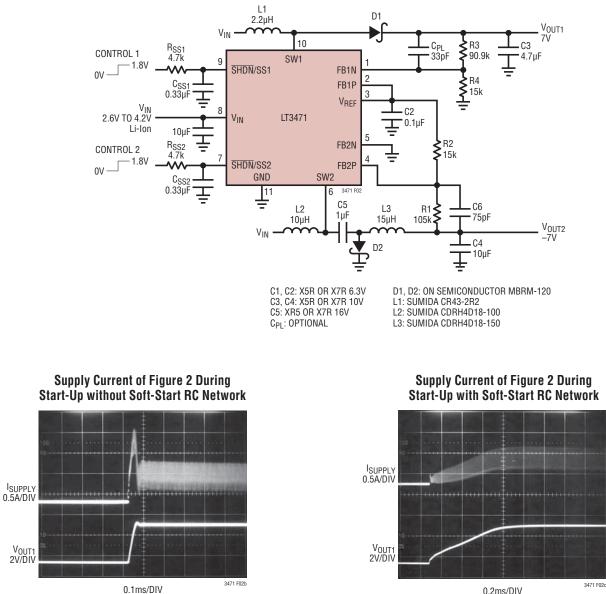

#### Soft-Start and Shutdown Features

To shut down the part, ground both SHDN/SS pins. To shut down one switcher but not the other one, ground that switcher's SHDN/SS pin. The soft-start feature provides a way to limit the inrush current drawn from the supply upon start-up. To use the soft-start feature for either switcher. slowly ramp up that switcher's SHDN/SS pin. The rate of voltage rise at the output of the switcher's comparator (A1 or A3 for switcher 1 or switcher 2 respectively) tracks the rate of voltage rise at the SHDN/SS pin once the SHDN/SS pin has reached about 1.1V. The soft-start function will go away once the voltage at the SHDN/SS pin exceeds 1.8V. See the Peak Switch Current vs SHDN/SS Voltage graph in the Typical Performance Characteristics section. The rate of voltage rise at the SHDN/SS pin can easily be controlled with a simple RC network connected between the control signal and the SHDN/SS pin. Typical values for the RC network are  $4.7k\Omega$  and  $0.33\mu$ F, giving start-up times on the order of milliseconds. This RC time constant can be adjusted to give different start-up times. If different values of resistance are to be used, keep in mind the SHDN/SS Current vs SHDN/SS voltage graph along with the Peak Switch Current vs SHDN/SS Voltage graph, both found in the Typical Performance Characteristics section. The impedance looking into the SHDN/SS pin depends on whether the SHDN/SS is above or below VIN. Normally SHDN/SS will not be driven above VIN, and thus the impedance looks like  $100 k\Omega$  in series with a diode. If the voltage of the SHDN/SS pin is above VIN, the impedance looks more like  $50k\Omega$  in series with a diode. This  $100k\Omega$  or  $50k\Omega$ impedance can have a slight effect on the start-up time if you choose the R in the RC soft-start network too large. Another consideration is selecting the soft-start time so that the soft-start feature is dominated by the RC network and not the capacitor on V<sub>REF</sub>. (See V<sub>REF</sub> voltage reference section of the Applications Information for details.)

The soft-start feature is of particular importance in applications where the switch will see voltage levels of 30V or higher. In these applications, the simultaneous presence of high current and voltage during startup may cause an overstress condition to the switch. Therefore, depending on input and output voltage conditions, higher RC time constant values may be necessary to improve the ruggedness of the design.

#### **CAPACITOR SELECTION**

Low ESR (equivalent series resistance) capacitors should be used at the output to minimize the output ripple voltage. Multi-layer ceramic capacitors are an excellent choice, as they have extremely low ESR and are available in very small packages. X5R dielectrics are preferred, followed by X7R, as these materials retain the capacitance over wide voltage and temperature ranges. A  $4.7\mu$ F to  $15\mu$ F output capacitor is sufficient for most applications, but systems with very low output currents may need only a  $1\mu$ F or  $2.2\mu$ F output capacitor. Solid tantalum or OS-CON capacitors can be used, but they will occupy more board area than a ceramic and will have a higher ESR. Always use a capacitor with a sufficient voltage rating.

Ceramic capacitors also make a good choice for the input decoupling capacitor, which should be placed as close as possible to the LT3471. A  $4.7\mu$ F to  $10\mu$ F input capacitor is sufficient for most applications. Table 2 shows a list of several ceramic capacitor manufacturers. Consult the manufacturers for detailed information on their entire selection of ceramic parts.

#### Table 2. Ceramic Capacitor Manufacturers

| Taiyo Yuden | (408) 573-4150 | www.t-yuden.com |

|-------------|----------------|-----------------|

| AVX         | (803) 448-9411 | www.avxcorp.com |

| Murata      | (714) 852-2001 | www.murata.com  |

The decision to use either low ESR (ceramic) capacitors or the higher ESR (tantalum or OS-CON) capacitors can affect the stability of the overall system. The ESR of any capacitor, along with the capacitance itself, contributes a zero to the system. For the tantalum and OS-CON capacitors, this zero is located at a lower frequency due to the higher value of the ESR, while the zero of a ceramic capacitor is at a much higher frequency and can generally be ignored.

A phase lead zero can be intentionally introduced by placing a capacitor ( $C_{PL}$ ) in parallel with the resistor (R3) between  $V_{OUT}$  and  $V_{FB}$  as shown in Figure 2. The frequency of the zero is determined by the following equation.

$$f_{\rm Z} = \frac{1}{2\pi \bullet \rm R3 \bullet \rm C_{\rm PL}}$$

0.2ms/DIV

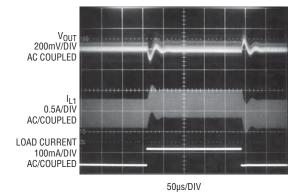

By choosing the appropriate values for the resistor and capacitor, the zero frequency can be designed to improve the phase margin of the overall converter. The typical target value for the zero frequency is between 35kHz to 55kHz. Figure 3 shows the transient response of the step-up converter from Figure 2 without the phase lead capacitor  $C_{PL}$ . Although adequate for many applications, phase margin is not ideal as evidenced by 2-3 "bumps" in both the output voltage and inductor current. A 33pF capacitor for  $C_{PL}$  results in ideal phase margin, which is revealed in Figure 4 as a more damped response and less overshoot.

Figure 3. Transient Response of Figure 2's Step-Up Converter without Phase Lead Capacitor

50µs/DIV

Figure 4. Transient Response of Figure 2's Step-Up Converter with 33pF Phase Lead Capacitor

#### **V<sub>REG</sub> VOLTAGE REFERENCE**

Pin 3 of the LT3471 is a bandgap voltage reference that has been divided down to 1.00V and buffered for external use. This pin must be by passed with at least 0.01 µF and no more than 1µF. This will ensure stability as well as reduce the noise on this pin. The buffer has a built-in current limit of at least 1mA (typically 1.4mA). This not only means that you can use this pin as an external reference for supplemental circuitry, but it also means that it is possible to provide a soft-start feature if this pin is used as one of the feedback pins for the error amplifier. Normally the soft-start time will be dominated by the RC time constant discussed in the soft-start and shutdown section. However, because of the finite current limit of the buffer for the  $V_{REG}$  pin, it will take some time to charge up the bypass capacitor. During this time, the voltage at the  $V_{\mbox{\scriptsize REG}}$  pin will ramp up, and this action provides an alternate means for soft-starting the circuit. If the largest recommended bypass capacitor is used, 1µF, the worst-case (longest) soft-start function that would be provided from the V<sub>RFF</sub> pin is:

$$\frac{1\mu F \bullet 1.00V}{1.0mA} = 1.0ms$$

Choose the RC network such that the soft-start time is longer than this time, or choose a smaller bypass capacitor for the  $V_{REF}$  pin (but always larger than  $0.01\mu$ F) so that the RC network dominates the soft-starting of the LT3471. The voltage at the  $V_{REF}$  pin can also be divided down and used for one of the feedback pins for the error amplifier. This is especially useful in LED driver applications, where the current through the LEDs is set using the voltage reference across a sense resistor in the LED chain. Using a smaller or divided down reference leads to less wasted power in the sense resistor. See the Typical Applications.

#### **DIODE SELECTION**

A Schottky diode is recommended for use with the LT3471. For high efficiency, a diode with good thermal characteristics at high currents should be used such as the On Semiconductor MBRM120. This is a 20V diode. Where the switch voltage exceeds 20V, use the MBRM140, a 40V diode. These diodes are rated to handle an average forward current of 1.0A. In applications where the average forward current of the diode is less than 0.5A, use the Philips PMEG 2005, 3005, or 4005 (a 20V, 30V or 40V diode, respectively).

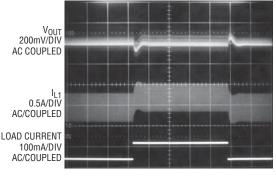

#### LAYOUT HINTS

The high speed operation of the LT3471 demands careful attention to board layout. You will not get advertised performance with careless layout. Figure 5 shows the recommended component placement.

Figure 5. Suggested Layout Showing a Boost on SW1 and an Inverter on SW2. Note the Separate Ground Returns for All High Current Paths (Using a Multilayer Board)

#### Compensation—Theory

Like all other current mode switching regulators, the LT3471 needs to be compensated for stable and efficient operation. Two feedback loops are used in the LT3471: a fast current loop which does not require compensation, and a slower voltage loop which does. Standard Bode plot analysis can be used to understand and adjust the voltage feedback loop.

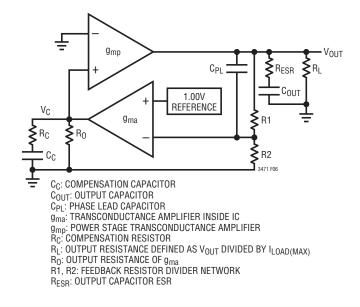

As with any feedback loop, identifying the gain and phase contribution of the various elements in the loop is critical. Figure 6 shows the key equivalent elements of a boost converter. Because of the fast current control loop, the power stage of the IC, inductor and diode have been replaced by the equivalent transconductance amplifier  $g_{mp}$ .  $g_{mp}$  acts as a current source where the output current is proportional to the V<sub>C</sub> voltage. Note that the maximum output current of  $g_{mp}$  is finite due to the current limit in the IC.

Figure 6. Boost Converter Equivalent Model

3471fb

From Figure 6, the DC gain, poles and zeroes can be calculated as follows:

| Output Pole: P1= $\frac{2}{2 \bullet \pi \bullet R_L \bullet C_{OUT}}$                                           |

|------------------------------------------------------------------------------------------------------------------|

| Error Amp Pole: P2= $\frac{1}{2 \bullet \pi \bullet R_0 \bullet C_c}$                                            |

| Error Amp Zero: $Z1 = \frac{1}{2 \bullet \pi \bullet R_{C} \bullet C_{C}}$                                       |

| DC GAIN: $A = \frac{V_{REF}}{V_{OUT}} \bullet g_{ma} \bullet R_0 \bullet g_{mp} \bullet R_L \bullet \frac{1}{2}$ |

| ESR Zero: $Z2 = \frac{1}{2 \cdot \pi \cdot R_{ESR} \cdot C_{OUT}}$                                               |

| RHP Zero: Z3= $\frac{V_{IN}^2 \cdot R_L}{2 \cdot \pi \cdot V_{OUT}^2 \cdot L}$                                   |

| High Frequency Pole: P3> $\frac{f_S}{3}$                                                                         |

| Phase Lead Zero: $Z4 = \frac{1}{2 \bullet \pi \bullet R1 \bullet C_{PL}}$                                        |

| Phase Lead Pole: P4 = $\frac{1}{2 \bullet \pi \bullet C_{PL} \bullet \frac{R1 \bullet R2}{R1 + R2}}$             |

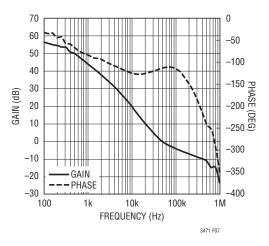

The Current Mode zero is a right half plane zero which can be an issue in feedback control design, but is manageable with proper external component selection. Using the circuit of Figure 2 as an example, Table 3 shows the parameters used to generate the Bode plot shown in Figure 7.

Table 3. Bode Plot Parameters

| Parameter        | Value | Units | Comment              |

|------------------|-------|-------|----------------------|

| RL               | 20    | Ω     | Application Specific |

| C <sub>OUT</sub> | 4.7   | μF    | Application Specific |

| R <sub>ESR</sub> | 10    | mΩ    | Application Specific |

| R <sub>0</sub>   | 0.9   | MΩ    | Not Adjustable       |

| C <sub>C</sub>   | 90    | pF    | Not Adjustable       |

| C <sub>PL</sub>  | 33    | pF    | Adjustable           |

| R <sub>C</sub>   | 55    | kΩ    | Not Adjustable       |

| R1               | 90.9  | kΩ    | Adjustable           |

| R2               | 15    | kΩ    | Adjustable           |

| V <sub>OUT</sub> | 7     | V     | Application Specific |

| VIN              | 3.3   | V     | Application Specific |

| g <sub>ma</sub>  | 50    | µmho  | Not Adjustable       |

| 9 <sub>mp</sub>  | 9.3   | mho   | Not Adjustable       |

| L                | 2.2   | μH    | Application Specific |

| f <sub>S</sub>   | 1.2   | MHz   | Not Adjustable       |

From Figure 7, the phase is  $-115^{\circ}$  when the gain reaches OdB giving a phase margin of 65°. This is more than adequate. The crossover frequency is 50kHz.

Figure 7. Bode Plot of 3.3V to 7V Application

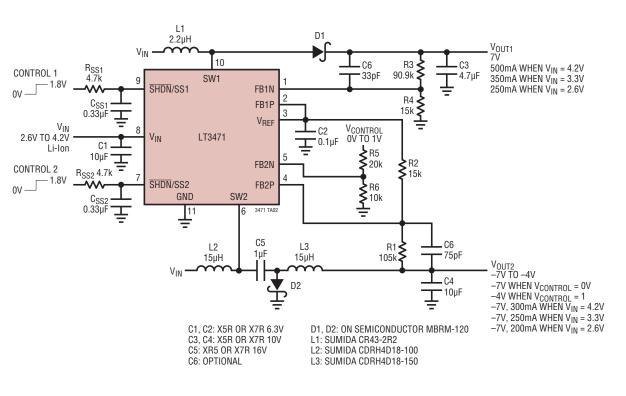

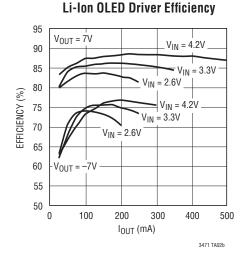

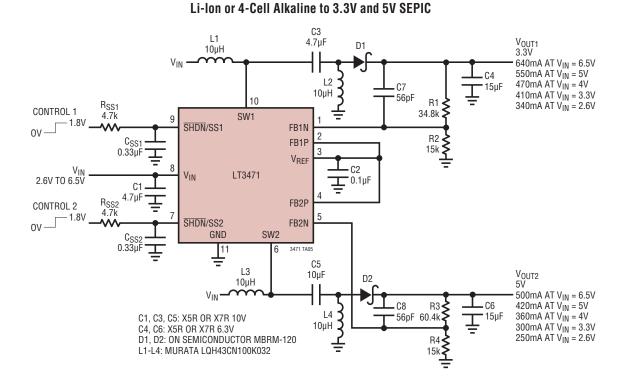

**Li-lon OLED Driver**

12

Downloaded from Arrow.com.

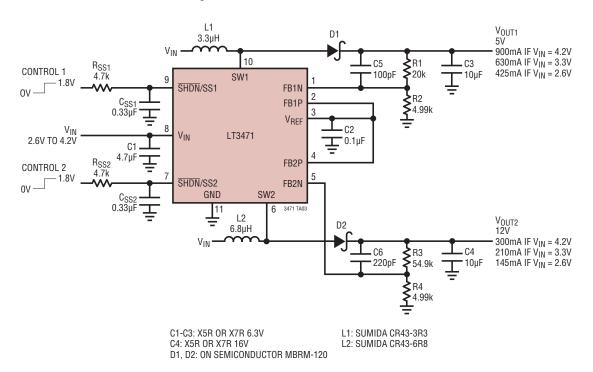

#### Single Li-Ion Cell to 5V, 12V Boost Converter

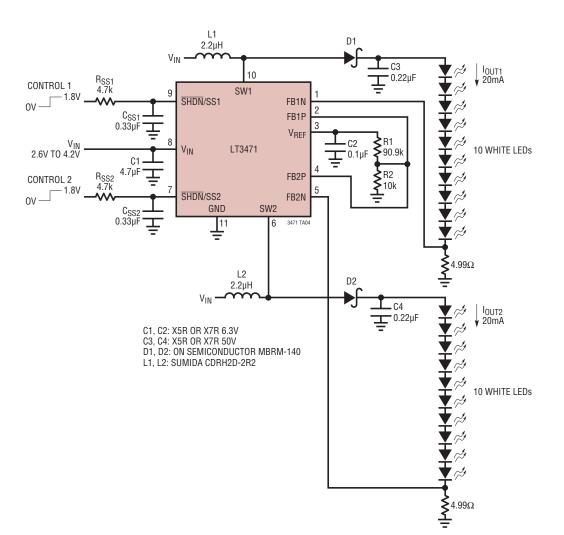

Li-Ion 20 White LED Driver

14 Downloaded from Arrow.com.

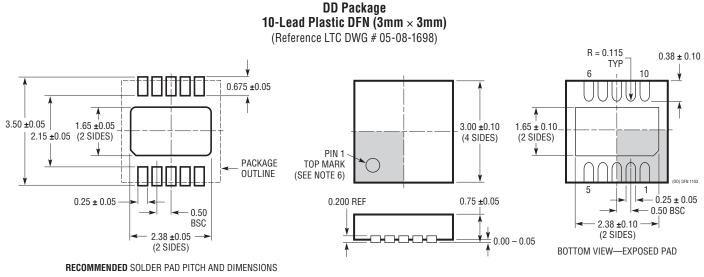

#### PACKAGE DESCRIPTION

NOTE:

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

- MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

TOP AND BOTTOM OF PACKAGE

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

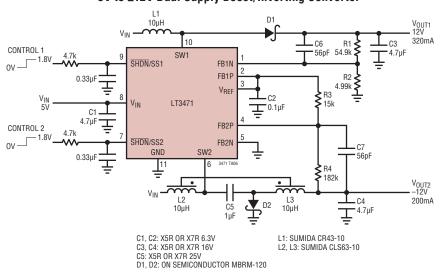

#### 5V to ±12V Dual Supply Boost/Inverting Converter

#### **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                                                                                                                                     | COMMENTS                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| LT1611          | 550mA (I <sub>SW</sub> ), 1.4MHz, High Efficiency Micropower Inverting DC/DC Converter                                                          | $V_{IN}\!\!:$ 1.1V to 10V, $V_{OUT(MAX)}$ = –34V, $I_Q$ = 3mA, $I_{SD}$ < 1µA, ThinSOT Package       |

| LT1613          | 550mA (I <sub>SW</sub> ), 1.4MHz, High Efficiency Step-Up<br>DC/DC Converter                                                                    | $V_{IN}\!\!:\!0.9V$ to 10V, $V_{OUT(MAX)}$ = 34V, $I_Q$ = 3mA, $I_{SD}$ < 1µA, ThinSOT Package       |

| LT1614          | 750mA (I <sub>SW</sub> ), 600kHz, High Efficiency Micropower Inverting DC/DC Converter                                                          | $V_{IN}\!\!:$ 1V to 12V, $V_{OUT(MAX)}$ = -24V, $I_Q$ = 1mA, $I_{SD}$ < 10 $\mu$ A, MS8, S8 Packages |

| LT1615/LT1615-1 | 300mA/80mA (I <sub>SW</sub> ), High Efficiency Step-Up<br>DC/DC Converters                                                                      | $V_{IN}$ = 1V to 15V, $V_{OUT(MAX)}$ = 34V, $I_Q$ = 20µA, $I_{SD}$ < 1µA, ThinSOT Package            |

| LT1617/LT1617-1 | 350mA/100mA (I <sub>SW</sub> ), High Efficiency Micropower Inverting DC/DC Converters                                                           | $V_{IN}$ = 1.2V to 15V, $V_{OUT(MAX)}$ = -34V, $I_Q$ = 20µA, $I_{SD}$ < 1µA, ThinSOT Package         |

| LT1930/LT1930A  | 1A (I <sub>SW</sub> ), 1.2MHz/2.2MHz, High Efficiency Step-Up<br>DC/DC Converters                                                               | $V_{IN}$ : 2.6V to 16V, $V_{OUT(MAX)}$ = 34V, $I_Q$ = 4.2mA/5.5mA, $I_{SD} <$ 1µA, ThinSOT Package   |

| LT1931/LT1931A  | 1A (I <sub>SW</sub> ), 1.2MHz/2.2MHz High Efficiency Micropower Inverting DC/DC Converters                                                      | $V_{IN}$ = 2.6V to 16V, $V_{OUT(MAX)}$ = -34V, $I_Q$ = 5.8mA, $I_{SD}$ < 1µA, ThinSOT Package        |

| LT1943 (Quad)   | Quad Boost, 2.6A Buck, 2.6A Boost, 0.3A Boost, 0.4A Inverter 1.2MHz TFT DC/DC Converter                                                         | $V_{IN}$ = 4.5V to 22V, $V_{OUT(MAX)}$ = 40V, $I_Q$ = 10µA, $I_{SD}$ < 35µA, TSSOP28E Package        |

| LT1945 (Dual)   | Dual Output, Boost/Inverter, 350mA (I <sub>SW</sub> ), Constant Off-Time,<br>High Efficiency Step-Up DC/DC Converter                            | $V_{IN}$ = 1.2V to 15V, $V_{OUT(MAX)}$ = ±34V, $I_Q$ = 40µA, $I_{SD}$ < 1µA, 10-Lead MS Package      |

| LT1946/LT1946A  | 1.5A (I <sub>SW</sub> ), 1.2MHz/2.7MHz, High Efficiency Step-Up<br>DC/DC Converters                                                             | $V_{IN}\!\!:$ 2.45V to 16V, $V_{OUT(MAX)}$ = 34V, $I_Q$ = 3.2mA, $I_{SD}$ < 1 $\mu$ A, MS8 Package   |

| LT3436          | 3A (I <sub>SW</sub> ), 1MHz, 34V Step-Up DC/DC Converter                                                                                        | $V_{IN}\!\!:$ 3V to 25V, $V_{OUT(MAX)}$ = 34V, $I_Q$ = 0.9mA, $I_{SD}$ < 6µA, TSSOP16E Package       |

| LT3462/LT3462A  | 300mA (I <sub>SW</sub> ), 1.2MHz/2.7MHz, High Efficiency Inverting DC/DC Converters with Integrated Schottkys                                   | $V_{IN}$ = 2.5V to 16V, $V_{OUT(MAX)}$ = -38V, $I_Q$ = 2.9mA, $I_{SD}$ < 1 $\mu$ A, ThinSOT Package  |

| LT3463/LT3463A  | Dual Output, Boost/Inverter, 250mA (I <sub>SW</sub> ), Constant Off-Time,<br>High Efficiency Step-Up DC/DC Converters with Integrated Schottkys | $V_{IN}$ = 2.3V to 15V, $V_{OUT(MAX)}$ = ±40V, $I_Q$ = 40µA, $I_{SD}$ < 1µA, DFN Package             |

| LT3464          | 85mA (I <sub>SW</sub> ), High Efficiency Step-Up DC/DC Converter with Integrated Schottky and PNP Disconnect                                    | $V_{IN}$ = 2.3V to 10V, $V_{OUT(MAX)}$ = 34V, $I_Q$ = 25µA, $I_{SD}$ < 1µA, ThinSOT Package          |

3471fb LT 1008 REV B · PRINTED IN USA ECHNOLOGY © LINEAR TECHNOLOGY CORPORATION 2004