#### ■Minimum Bus Cycle Time

- 83.3ns (12MHz) V<sub>DD</sub>=2.8 to 5.5V

- 125ns (8MHz) V<sub>DD</sub>=2.5 to 5.5V

- 500ns (2MHz) V<sub>DD</sub>=2.2 to 5.5V

Note: The bus cycle time here refers to the ROM read speed.

### ■Minimum Instruction Cycle Time (tCYC)

- 250ns (12MHz) V<sub>DD</sub>=2.8 to 5.5V

- 375ns (8MHz) V<sub>DD</sub>=2.5 to 5.5V

- $1.5\mu s (2MHz)$  VDD=2.2 to 5.5V

#### ■Ports

• Normal withstand voltage I/O ports

Ports whose I/O direction can be designated in 1-bit units 46 (P1n, P2n, P3n, P70 to P73, P80 to P86, PCn,

- Ports whose I/O direction can be designated in 4-bit units

- Normal withstand voltage input port

- Dedicated oscillator ports

- Reset pins

- Power pins

#### ■Timers

- Timer 0: 16-bit timer/counter with a capture register

- Mode 0: 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register) ×2 channels

- Mode 1: 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register)

- + 8-bit counter (with an 8-bit capture register)

- Mode 2: 16-bit timer with an 8-bit programmable prescaler (with a 16-bit capture register)

- Mode 3: 16-bit counter (with a 16-bit capture register)

- Timer 1: 16-bit timer/counter that supports PWM/toggle outputs

Mode 0: 8-bit timer with an 8-bit prescaler (with toggle outputs) + 8-bit timer/counter with an 8-bit prescaler (with toggle outputs)

### Mode 1: 8-bit PWM with an 8-bit prescaler $\times$ 2 channels

Mode 2: 16-bit timer/counter with an 8-bit prescaler (with toggle outputs)

(toggle outputs also possible from the lower-order 8-bits)

Mode 3: 16-bit timer with an 8-bit prescaler (with toggle outputs) (The lower-order 8 bits can be used as PWM)

- Timer 4: 8-bit timer with a 6-bit prescaler

- Timer 5: 8-bit timer with a 6-bit prescaler

- Timer 6: 8-bit timer with a 6-bit prescaler (with toggle outputs)

- Timer 7: 8-bit timer with a 6-bit prescaler (with toggle outputs)

- Base timer

- 1) The clock is selectable from the subclock (32.768kHz crystal oscillation), system clock, and timer 0 prescaler output.

- 2) Interrupts programmable in 5 different time schemes.

### ■High-speed Clock Counter

1) Can count clocks with a maximum clock rate of 24MHz (at a main clock of 12MHz)

2) Can generate output real-time.

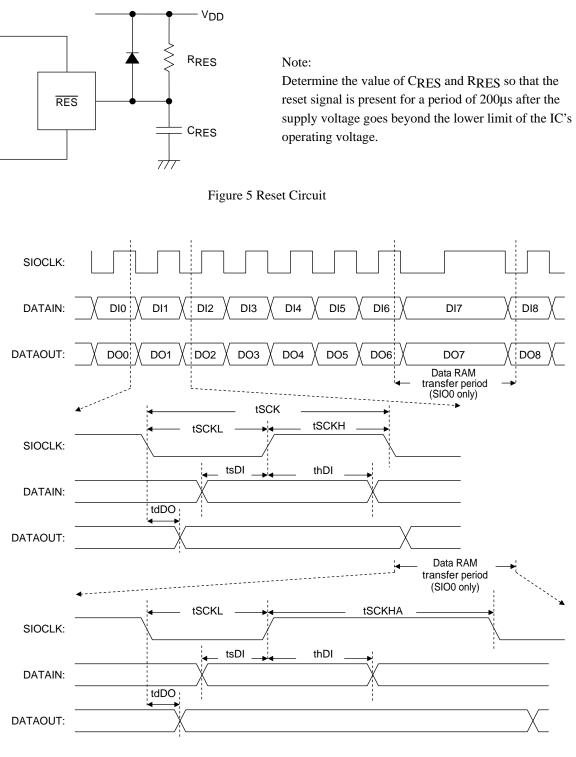

### ■SIO

- SIO0: 8-bit synchronous serial interface

- 1) LSB first/MSB first mode selectable

- 2) Built-in 8-bit baudrate generator (maximum transfer clock cycle = 4/3 tCYC)

- Automatic continuous data transmission (1 to 256 bits, specifiable in 1 bit units, suspension and resumption of data transmission possible in 1 byte units)

- SIO1: 8-bit asynchronous/synchronous serial interface

- Mode 0: Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 tCYC transfer clocks)

- Mode 1: Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 tCYC baudrates)

- Mode 2: Bus mode 1 (start bit, 8 data bits, 2 to 512 tCYC transfer clocks)

- Mode 3: Bus mode 2 (start detect, 8 data bits, stop detect)

PWM2, PWM3, XT2) 8 (P0n) 1 (XT1) 2 (CF1, CF2)

- $2 (\underline{CF1}, \underline{CF2})$ 1 (RES)

- 6 (VSS1 to 3, VDD1 to 3)

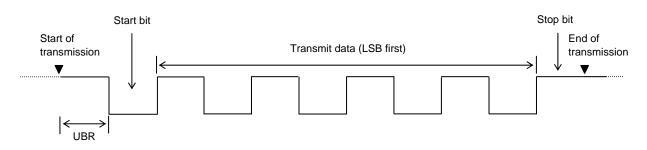

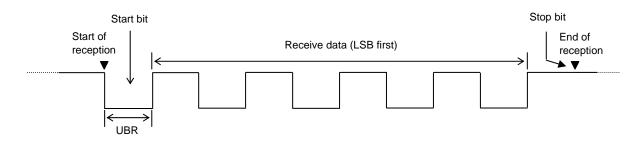

### ■UART: 2 channels

- Full duplex

- 7/8/9 bit data bits selectable

- 1 stop bit (2 bit in continuous data transmission)

- Built-in baudrate generator (with baudrates of 16/3 to 8192/3 tCYC)

■AD Converter: 8 bits × 11 channels

■PWM: Multifrequency 12-bit PWM × 2 channels

Remote Control Receiver Circuit (sharing pins with P73, INT3, and T0IN)

- 1) Noise filtering function (noise filter time constant selectable from 1 tCYC, 32 tCYC, and 128 tCYC)

- 2) The noise filtering function is available for the INT3, T0IN, or T0HCP signal at P73. When P73 is read with an instruction, the signal level at that pin is read regardless of the availability of the noise filtering function.

- ■Watchdog Timer

- External RC watchdog timer

- Interrupt and reset signals selectable

- Clock Output Function

1) Able to output selected oscillation clock 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64 as system clock.

2) Able to output oscillation clock of sub clock.

#### ■Interrupts

- 27 sources, 10 vector addresses

- 1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt requests of the level equal to or lower than the current interrupt are not accepted.

- 2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt into the smallest vector address takes precedence.

| No. | Vector Address | Level  | Interrupt Source                   |  |  |  |

|-----|----------------|--------|------------------------------------|--|--|--|

| 1   | 00003H         | X or L | INTO                               |  |  |  |

| 2   | 0000BH         | X or L | INT1                               |  |  |  |

| 3   | 00013H         | H or L | INT2/T0L/INT4                      |  |  |  |

| 4   | 0001BH         | H or L | INT3/INT5/base timer0/base timer1  |  |  |  |

| 5   | 00023H         | H or L | T0H/INT6                           |  |  |  |

| 6   | 0002BH         | H or L | T1L/T1H/INT7                       |  |  |  |

| 7   | 00033H         | H or L | SIO0/UART1 receive/UART2 receive   |  |  |  |

| 8   | 0003BH         | H or L | SIO1/UART1 transmit/UART2 transmit |  |  |  |

| 9   | 00043H         | H or L | ADC/T6/T7                          |  |  |  |

| 10  | 0004BH         | H or L | Port 0/T4/T5/PWM2, PWM3            |  |  |  |

• Priority levels X > H > L

• Of interrupts of the same level, the one with the smallest vector address takes precedence.

Subroutine Stack Levels: 1024 levels (the stack is allocated in RAM)

■High-speed Multiplication/Division Instructions

- 16-bits  $\times$  8-bits (5 tCYC execution time)

- 24-bits  $\times$  16-bits (12 tCYC execution time)

- 16-bits ÷ 8-bits (8 tCYC execution time)

- 24-bits ÷ 16-bits (12 tCYC execution time)

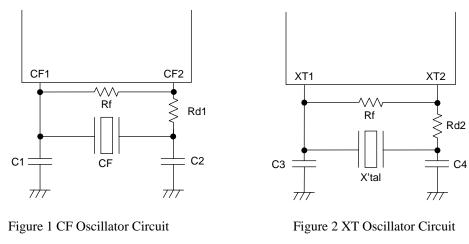

#### ■Oscillation Circuits

- RC oscillation circuit (internal)

- CF oscillation circuit

- Crystal oscillation circuit

- : For system clock

- : For system clock, with internal Rf

- cuit : For low-speed system clock

- Multifrequency RC oscillation circuit (internal) : For system clock

### ■System Clock Divider Function

- Can run on low current.

- The minimum instruction cycle selectable from 250ns, 500ns, 1.0µs, 2.0µs, 4.0µs, 8.0µs, 16.0µs, 32.0µs, and 64.0µs (at a main clock rate of 12MHz).

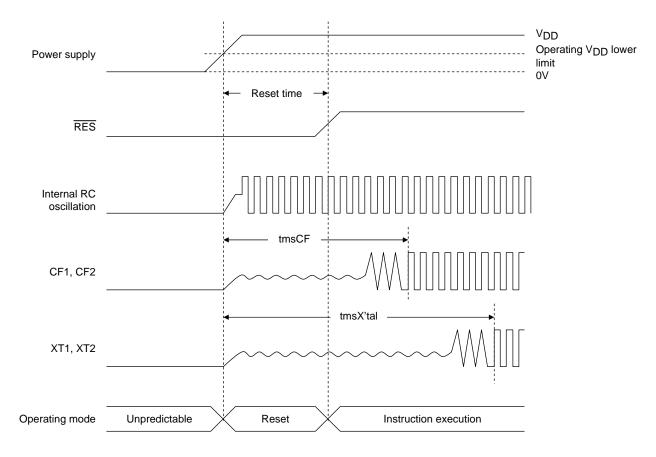

#### ■Standby Function

- HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation.

- 1) Oscillation is not halted automatically.

- 2) Canceled by a system reset or occurrence of an interrupt.

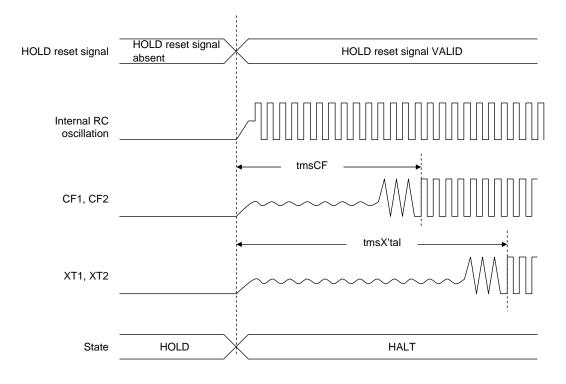

- HOLD mode: Suspends instruction execution and the operation of the peripheral circuits.

- 1) The CF, RC, and crystal oscillators automatically stop operation.

- 2) There are three ways of resetting the HOLD mode.

- (1) Setting the reset pin to the lower level.

- (2) Setting at least one of the INTO, INT1, INT2, INT4, and INT5 pins to the specified level

- (3) Having an interrupt source established at port 0

- X'tal HOLD mode: Suspends instruction execution and the operation of the peripheral circuits except the base timer.

- 1) The CF and RC oscillators automatically stop operation.

- 2) The state of crystal oscillation established when the X'tal HOLD mode is entered is retained.

- 3) There are four ways of resetting the X'tal HOLD mode.

- (1) Setting the reset pin to the low level

- (2) Setting at least one of the INTO, INT1, INT2, INT4, and INT5 pins to the specified level

- (3) Having an interrupt source established at port 0

- (4) Having an interrupt source established in the base timer circuit

#### ■On-chip Debugger Function

• Permits software debugging with the test device installed on the target board.

#### ■Development Tools

- Evaluation (EVA) chip : LC87EV690

- Emulator

- : EVA62S + ECB876600D + SUB875M00 + POD64QFP ICE-B877300 + SUB875M00 + POD64QFP

- On-chip-debugger

: TCB87-TypeB + LC87F5M64A

#### Programming Boards

| Package         | Programming boards |

|-----------------|--------------------|

| QIP64E(14 × 14) | W87F50256Q         |

#### ■Flash ROM Programmer

| Maker                                   | Model                                                             | Support version(Note)                                                 | Device     |  |  |

|-----------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|------------|--|--|

| Flash Support<br>Group,<br>Inc.(Single) | AF9708/09/09B<br>(including product of Ando Electric Co.,Ltd)     | Revision : After Rev.02.73                                            | LC87F6D64A |  |  |

| Flash Support                           | AF9723(Main body)<br>(including product of Ando Electric Co.,Ltd) | Revision : After Rev.02.29                                            | LC87F5M64A |  |  |

| Group, Inc.(Gang)                       | AF9833(Unit)<br>(including product of Ando Electric Co.,Ltd)      | Revision : After Rev.01.88                                            | LC87F5M64A |  |  |

| Our company                             | SKK/SKK Type-B/SKK DBG Type-B<br>(SANYO FWS)                      | Application Version:<br>After 1.04<br>Chip Data Version:<br>After2.10 | LC87F5M64A |  |  |

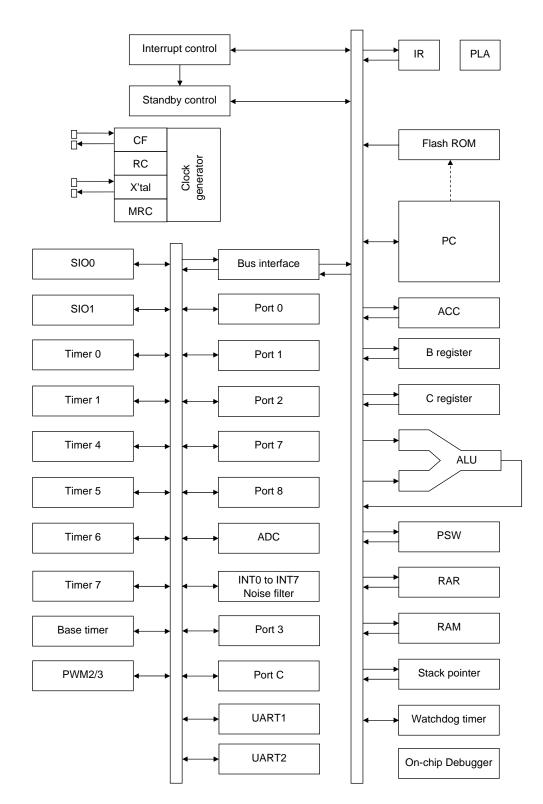

# System Block Diagram

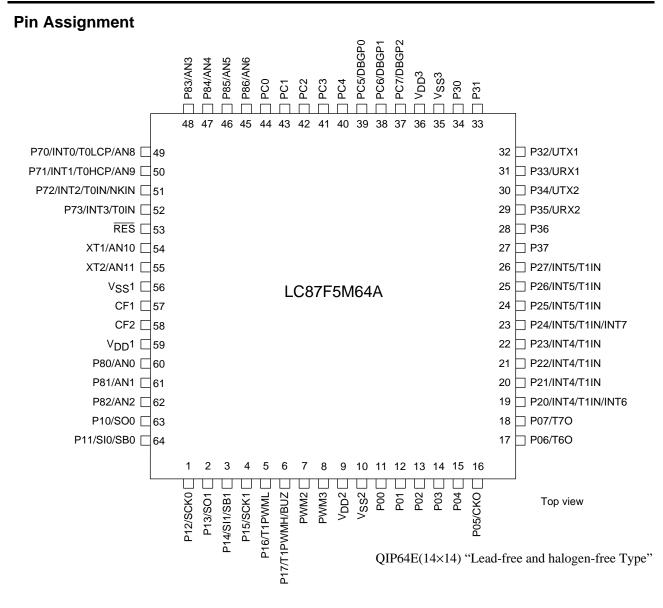

# **Pin Description**

| Pin Name                                                  | I/O                                                          |                                      |                                | Des               | scription          |                   |             | Option |  |

|-----------------------------------------------------------|--------------------------------------------------------------|--------------------------------------|--------------------------------|-------------------|--------------------|-------------------|-------------|--------|--|

| V <sub>SS</sub> 1, V <sub>SS</sub> 2<br>V <sub>SS</sub> 3 | -                                                            | - Power supply p                     | in                             |                   |                    |                   |             | No     |  |

| V <sub>DD</sub> 1, V <sub>DD</sub> 2<br>V <sub>DD</sub> 3 | -                                                            | + Power supply p                     | bin                            |                   |                    |                   |             | No     |  |

| Port 0                                                    | I/O                                                          | • 8-bit I/O port                     |                                |                   |                    |                   |             | Yes    |  |

| P00 to P07                                                |                                                              | • I/O specifiable                    | n 4-bit units                  |                   |                    |                   |             |        |  |

|                                                           |                                                              | <ul> <li>Pull-up resistor</li> </ul> | can be turned                  | on and off in 4-b | it units           |                   |             |        |  |

|                                                           |                                                              | HOLD release                         | nput                           |                   |                    |                   |             |        |  |

|                                                           |                                                              | Port 0 interrupt                     | input                          |                   |                    |                   |             |        |  |

|                                                           | Shared Pins                                                  |                                      |                                |                   |                    |                   |             |        |  |

|                                                           | P05: Clock output (system clock/can selected from sub clock) |                                      |                                |                   |                    |                   |             |        |  |

| P06: Timer 6 toggle output                                |                                                              |                                      |                                |                   |                    |                   |             |        |  |

|                                                           |                                                              | P07: Timer 7 to                      | ggle output                    |                   |                    |                   |             |        |  |

| Port 1                                                    | I/O                                                          | <ul> <li>8-bit I/O port</li> </ul>   |                                |                   |                    |                   |             | Yes    |  |

| P10 to P17 • I/O specifiable in 1-bit units               |                                                              |                                      |                                |                   |                    |                   |             |        |  |

|                                                           |                                                              | <ul> <li>Pull-up resistor</li> </ul> | can be turned                  | on and off in 1-b | it units           |                   |             |        |  |

|                                                           |                                                              | <ul> <li>Pin functions</li> </ul>    |                                |                   |                    |                   |             |        |  |

|                                                           |                                                              | P10: SIO0 data                       | output                         |                   |                    |                   |             |        |  |

|                                                           |                                                              | P11: SIO0 data                       | input/bus I/O                  |                   |                    |                   |             |        |  |

|                                                           |                                                              | P12: SIO0 cloc                       | k I/O                          |                   |                    |                   |             |        |  |

|                                                           |                                                              | P13: SIO1 data                       | output                         |                   |                    |                   |             |        |  |

|                                                           |                                                              | P14: SIO1 data                       | input/bus I/O                  |                   |                    |                   |             |        |  |

|                                                           |                                                              | P15: SIO1 cloc                       | k I/O                          |                   |                    |                   |             |        |  |

|                                                           |                                                              | P16: Timer 1 P                       | WML output                     |                   |                    |                   |             |        |  |

|                                                           |                                                              | P17: Timer 1 P                       | WMH output/be                  | eper output       |                    |                   |             |        |  |

| Port 2                                                    | I/O                                                          | <ul> <li>8-bit I/O port</li> </ul>   |                                |                   |                    |                   |             | Yes    |  |

| P20 to P27                                                |                                                              |                                      | I/O specifiable in 1-bit units |                   |                    |                   |             |        |  |

|                                                           |                                                              | <ul> <li>Pull-up resistor</li> </ul> | can be turned                  | on and off in 1-b | it units           |                   |             |        |  |

|                                                           |                                                              | Other functions                      |                                |                   |                    |                   |             |        |  |

|                                                           |                                                              | P20: INT4 inpu                       | t/HOLD reset in                | put/timer 1 even  | t input/timer 0L o | capture input/    |             |        |  |

|                                                           |                                                              |                                      |                                | -                 | L capture 1 input  |                   |             |        |  |

|                                                           |                                                              |                                      | -                              | reset input/timer | 1 event input/tin  | ner 0L capture ir | nput/       |        |  |

|                                                           |                                                              | timer 0H o                           | capture input                  |                   |                    |                   |             |        |  |

|                                                           |                                                              |                                      |                                | •                 | t input/timer 0L o | • •               |             |        |  |

|                                                           |                                                              |                                      |                                | •                 | H capture 1 inpu   |                   |             |        |  |

|                                                           |                                                              |                                      | -                              | reset input/timer | 1 event input/tin  | ner 0L capture ir | nput/       |        |  |

|                                                           | timer 0H capture input                                       |                                      |                                |                   |                    |                   |             |        |  |

|                                                           |                                                              | <ul> <li>Interrupt ackno</li> </ul>  | wledge type                    |                   | 1                  | 1                 | · · · · · · |        |  |

|                                                           |                                                              |                                      | Rising                         | Falling           | Rising/<br>Falling | H level           | L level     |        |  |

|                                                           |                                                              | INT4                                 | enable                         | enable            | enable             | disable           | disable     |        |  |

|                                                           | 1                                                            | INT5                                 | enable                         | enable            | enable             | disable           | disable     |        |  |

|                                                           |                                                              |                                      |                                |                   |                    |                   |             |        |  |

|                                                           |                                                              | INT6                                 | enable                         | enable            | enable             | disable           | disable     |        |  |

Continued on next page.

| Pin Name   | I/O                        |                                                                                                                                                                                                                          |                             | Des                | cription |         |         | Option |  |

|------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------|---------|---------|--------|--|

| Port 7     | I/O                        | • 4-bit I/O port                                                                                                                                                                                                         |                             |                    |          |         |         | No     |  |

| P70 to P73 |                            | I/O specifiable i                                                                                                                                                                                                        | n 1-bit units               |                    |          |         |         |        |  |

|            |                            | Pull-up resistor can be turned on and off in 1-bit units                                                                                                                                                                 |                             |                    |          |         |         |        |  |

|            |                            | Shared Pins                                                                                                                                                                                                              |                             |                    |          |         |         |        |  |

|            |                            | P70: INT0 input/HOLD reset input/timer 0L capture input/watchdog timer output<br>P71: INT1 input/HOLD reset input/timer 0H capture input<br>P72: INT2 input/HOLD reset input/timer 0 event input/timer 0L capture input/ |                             |                    |          |         |         |        |  |

|            |                            |                                                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            |                                                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            | high speed clock counter input                                                                                                                                                                                           |                             |                    |          |         |         |        |  |

|            |                            | P73: INT3 input (with noise filter)/timer 0 event input/timer 0H capture input                                                                                                                                           |                             |                    |          |         |         |        |  |

|            |                            | AD converter in                                                                                                                                                                                                          | put port: AN8 (I            | P70), AN9 (P71)    |          |         |         |        |  |

|            | Interrupt acknowledge type |                                                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            |                                                                                                                                                                                                                          | Rising                      | Falling            | Rising/  | H level | L level |        |  |

|            |                            |                                                                                                                                                                                                                          | Trising                     | i anng             | Falling  | THEVE   | Elever  |        |  |

|            |                            | INT0                                                                                                                                                                                                                     | enable                      | enable             | disable  | enable  | enable  |        |  |

|            |                            | INT1                                                                                                                                                                                                                     | enable                      | enable             | disable  | enable  | enable  |        |  |

|            |                            | INT2                                                                                                                                                                                                                     | enable                      | enable             | enable   | disable | disable |        |  |

|            |                            | INT3                                                                                                                                                                                                                     | enable                      | enable             | enable   | disable | disable |        |  |

|            |                            |                                                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

| Port 8     | I/O                        | • 7-bit I/O port                                                                                                                                                                                                         |                             |                    |          |         |         | No     |  |

| P80 to P86 |                            | • I/O specifiable in 1-bit units                                                                                                                                                                                         |                             |                    |          |         |         |        |  |

|            |                            | <ul> <li>Shared Pins</li> </ul>                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            | AD converter in                                                                                                                                                                                                          | put port : AN0 (            | (P80) to AN6 (P8   | 6)       |         |         |        |  |

| PWM2       | I/O                        | PWM2 and PW                                                                                                                                                                                                              | M3 output ports             | 5                  |          |         |         | No     |  |

| PWM3       |                            | General-purpos                                                                                                                                                                                                           | e I/O available             |                    |          |         |         |        |  |

| Port 3     | I/O                        | <ul> <li>8-bit I/O port</li> </ul>                                                                                                                                                                                       |                             |                    |          |         |         | Yes    |  |

| P30 to P37 |                            | <ul> <li>I/O specifiable i</li> </ul>                                                                                                                                                                                    | n 1-bit units               |                    |          |         |         |        |  |

|            |                            | Pull-up resistor can be turned on and off in 1-bit units                                                                                                                                                                 |                             |                    |          |         |         |        |  |

|            |                            | Pin functions                                                                                                                                                                                                            |                             |                    |          |         |         |        |  |

|            |                            | P32: UART1 transmit                                                                                                                                                                                                      |                             |                    |          |         |         |        |  |

|            |                            | P33: UART1 receive                                                                                                                                                                                                       |                             |                    |          |         |         |        |  |

|            |                            | P34: UART2 transmit                                                                                                                                                                                                      |                             |                    |          |         |         |        |  |

|            |                            | P35: UART2 red                                                                                                                                                                                                           | ceive                       |                    |          |         |         |        |  |

| Port C     | I/O                        | • 8-bit I/O port                                                                                                                                                                                                         |                             |                    |          |         |         | Yes    |  |

| PC0 to PC7 |                            | I/O specifiable in                                                                                                                                                                                                       |                             |                    |          |         |         |        |  |

|            |                            | Pull-up resistor                                                                                                                                                                                                         | can be turned o             | on and off in 1-bi | tunits   |         |         |        |  |

|            |                            | Pin functions                                                                                                                                                                                                            |                             |                    |          |         |         |        |  |

| <u> </u>   | 1                          |                                                                                                                                                                                                                          | P2(PC5 to PC7               | '): On-chip Debu   | gger     |         |         |        |  |

| RES        | Input                      | Reset pin                                                                                                                                                                                                                |                             |                    |          |         |         | No     |  |

| XT1        | Input                      | • 32.768kHz crys                                                                                                                                                                                                         | tal oscillator inp          | out pin            |          |         |         | No     |  |

|            |                            | <ul> <li>Shared pins</li> </ul>                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            | General-purpos                                                                                                                                                                                                           |                             |                    |          |         |         |        |  |

|            |                            | AD converter in                                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            | Must be connec                                                                                                                                                                                                           | ted to V <sub>DD</sub> 1 if | not to be used.    |          |         |         |        |  |

| XT2        | I/O                        | • 32.768kHz crys                                                                                                                                                                                                         | tal oscillator inp          | out pin            |          |         |         | No     |  |

|            |                            | <ul> <li>Shared pins</li> </ul>                                                                                                                                                                                          |                             |                    |          |         |         |        |  |

|            |                            | General-purpos                                                                                                                                                                                                           |                             |                    |          |         |         |        |  |

|            |                            | AD converter in                                                                                                                                                                                                          | -                           |                    |          |         |         |        |  |

|            |                            | Must be set for oscillation and kept open if not to be used.                                                                                                                                                             |                             |                    |          |         |         |        |  |

| CF1        | Input                      | Ceramic resonate                                                                                                                                                                                                         | or input pin                |                    |          |         |         | No     |  |

| CF2        | Output                     | Ceramic resonate                                                                                                                                                                                                         | or output pin               |                    |          |         |         | No     |  |

## **Port Output Types**

The table below lists the types of port outputs and the presence/absence of a pull-up resistor. Data can be read into any input port even if it is in the output mode.

| Port Name  | Options Selected<br>in Units of | Option Type | Output Type                                                                                     | Pull-up Resistor      |

|------------|---------------------------------|-------------|-------------------------------------------------------------------------------------------------|-----------------------|

| P00 to P07 | 1 bit                           | 1           | CMOS                                                                                            | Programmable (Note 1) |

|            |                                 | 2           | Nch-open drain                                                                                  | No                    |

| P10 to P17 | 1 bit                           | 1           | CMOS                                                                                            | Programmable          |

|            |                                 | 2           | Nch-open drain                                                                                  | Programmable          |

| P20 to P27 | 1 bit                           | 1           | CMOS                                                                                            | Programmable          |

|            |                                 | 2           | Nch-open drain                                                                                  | Programmable          |

| P70        | -                               | No          | Nch-open drain                                                                                  | Programmable          |

| P71 to P73 | -                               | No          | CMOS                                                                                            | Programmable          |

| P80 to P86 | -                               | No          | Nch-open drain                                                                                  | No                    |

| PWM2, PWM3 | -                               | No          | CMOS                                                                                            | No                    |

| P30 to P37 | 1 bit                           | 1           | CMOS                                                                                            | Programmable          |

|            |                                 | 2           | Nch-open drain                                                                                  | Programmable          |

| PC0 to PC7 | 1 bit                           | 1           | CMOS                                                                                            | Programmable          |

|            |                                 | 2           | Nch-open drain                                                                                  | Programmable          |

| XT1        | -                               | No          | Input for 32.768kHz crystal oscillator (Input only)                                             | No                    |

| XT2        | -                               | No          | Output for 32.768kHz crystal oscillator<br>(Nch-open drain when in general-purpose output mode) | No                    |

Note 1: Programmable pull-up resistors for port 0 are controlled in 4-bit units (P00 to 03, P04 to 07).

<sup>(</sup>Example 1) When backup is active in the HOLD mode, the high level of the port outputs is supplied by the backup capacitors.

(Example 2) The high-level output at the ports is unstable when the HOLD mode backup is in effect.

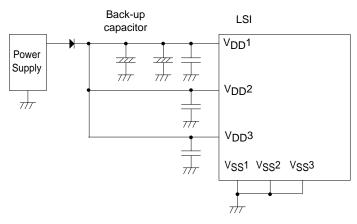

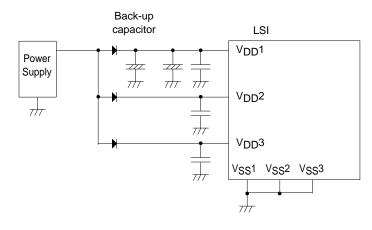

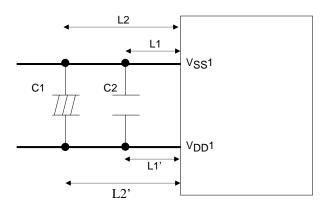

<sup>\*1:</sup> Make the following connection to minimize the noise input to the V<sub>DD</sub>1 pin and prolong the backup time. Be sure to electrically short the V<sub>SS</sub>1, V<sub>SS</sub>2, and V<sub>SS</sub>3 pins.

|                           | Parameter                           | Symbol              | Pins/Remarks                                                 | Conditions                                            |                     | r    | Spec | ification            |     |

|---------------------------|-------------------------------------|---------------------|--------------------------------------------------------------|-------------------------------------------------------|---------------------|------|------|----------------------|-----|

|                           | . aramotor                          |                     |                                                              |                                                       | V <sub>DD</sub> [V] | min  | typ  | max                  | uni |

|                           | ximum supply<br>age                 | V <sub>DD</sub> max | V <sub>DD</sub> 1, V <sub>DD</sub> 2, V <sub>DD</sub> 3      | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3 |                     | -0.3 |      | +6.5                 |     |

| np                        | ut voltage                          | V <sub>I</sub> (1)  | XT1, CF1                                                     |                                                       |                     | -0.3 |      | V <sub>DD</sub> +0.3 |     |

| np                        | ut/Output voltage                   | V <sub>IO</sub> (1) | Ports 0, 1, 2<br>Ports 7, 8<br>Ports 3, C<br>PWM2, PWM3, XT2 |                                                       |                     | -0.3 |      | V <sub>DD</sub> +0.3 | V   |

|                           | Peak output<br>current              | IOPH(1)             | Ports 0, 1, 2<br>Ports 3, C                                  | CMOS output select<br>Per 1 application pin           |                     | -10  |      |                      |     |

|                           |                                     | IOPH(2)             | PWM2, PWM3                                                   | Per 1 application pin.                                |                     | -20  |      |                      |     |

|                           |                                     | IOPH(3)             | P71 to P73                                                   | Per 1 application pin.                                |                     | -5   |      |                      |     |

| ÷                         | Mean output<br>current              | IOMH(1)             | Ports 0, 1, 2<br>Ports 3, C                                  | CMOS output select<br>Per 1 application pin           |                     | -7.5 |      |                      |     |

| rrent                     | (Note1-1)                           | IOMH(2)             | PWM2, PWM3                                                   | Per 1 application pin                                 |                     | -10  |      |                      |     |

| it cui                    | . ,                                 | IOMH(3)             | P71 to P73                                                   | Per 1 application pin                                 |                     | -3   |      |                      |     |

| utpr                      | Total output                        | ΣIOAH(1)            | P71 to P73                                                   | Total of all applicable pins                          |                     | -10  |      |                      |     |

| High level output current | current                             | ΣIOAH(2)            | Ports, 1<br>PWM2, PWM3                                       | Total of all applicable pins                          |                     | -25  |      |                      |     |

| Higt                      |                                     | ΣIOAH(3)            | Ports 0, 2                                                   | Total of all applicable pins                          |                     | -25  |      |                      |     |

|                           |                                     | ΣIOAH(4)            | Ports 0, 1, 2<br>PWM2, PWM3                                  | Total of all applicable pins                          |                     | -45  |      |                      |     |

|                           |                                     | ΣIOAH(5)            | Port 3                                                       | Total of all applicable pins                          |                     | -25  |      |                      |     |

|                           |                                     | ΣIOAH(6)            | Ports C                                                      | Total of all applicable pins                          |                     | -25  |      |                      |     |

|                           |                                     | ΣIOAH(7)            | Ports 3, C                                                   | Total of all applicable pins                          |                     | -45  |      |                      |     |

|                           | Peak output                         | IOPL(1)             | P02 to P07                                                   | Per 1 application pin                                 |                     | -    |      |                      |     |

|                           | current                             |                     | Ports 1, 2<br>Ports 3, C<br>PWM2, PWM3                       |                                                       |                     |      |      | 20                   | m   |

|                           |                                     | IOPL(2)             | P00, P01                                                     | Per 1 application pin                                 |                     |      |      | 30                   |     |

|                           |                                     | IOPL(3)             | Ports 7, 8, XT2                                              | Per 1 application pin                                 |                     |      |      | 10                   |     |

| nt                        | Mean output<br>current<br>(Note1-1) | IOML(1)             | P02 to P07<br>Ports 1, 2<br>Ports 3, C<br>PWM2, PWM3         | Per 1 application pin                                 |                     |      |      | 15                   |     |

| urre                      |                                     | IOML(2)             | P00, P01                                                     | Per 1 application pin                                 |                     |      |      | 20                   |     |

| put c                     |                                     | IOML(3)             | Ports 7, 8, XT2                                              | Per 1 application pin                                 |                     |      |      | 7.5                  |     |

| Low level output current  | Total output<br>current             | ΣIOAL(1)            | Port 7<br>P83 to P86, XT2                                    | Total of all applicable pins                          |                     |      |      | 15                   |     |

| e ve                      |                                     | ΣIOAL(2)            | P80 to P82                                                   | Total of all applicable pins                          |                     |      |      | 15                   |     |

| Ľ                         |                                     | ΣIOAL(3)            | Ports 7, 8, XT2                                              | Total of all applicable pins                          |                     |      |      | 20                   |     |

|                           |                                     | ΣIOAL(4)            | Ports 1<br>PWM2, PWM3                                        | Total of all applicable pins                          |                     |      |      | 45                   |     |

|                           |                                     | ΣIOAL(5)            | Ports 0, 2                                                   | Total of all applicable pins                          |                     |      |      | 45                   |     |

|                           |                                     | ΣIOAL(6)            | Ports 0, 1, 2<br>PWM2, PWM3                                  | Total of all applicable pins                          |                     |      |      | 80                   |     |

|                           |                                     | ΣIOAL(7)            | Port 3                                                       | Total of all applicable pins                          |                     |      |      | 45                   |     |

|                           |                                     | ΣIOAL(8)            | Ports C                                                      | Total of all applicable pins                          |                     |      |      | 45                   |     |

|                           |                                     | ΣIOAL(9)            | Ports 3, C                                                   | Total of all applicable pins                          |                     |      |      | 80                   |     |

|                           | ximum power<br>sipation             | Pd max              | QIP64E(14×14)                                                | Ta=-40 to +85°C                                       |                     |      |      | 300                  | ۳۱  |

|                           | erating ambient<br>nperature        | Topr                |                                                              |                                                       |                     | -40  |      | +85                  | °(  |

| Sto                       | rage ambient                        | Tstg                | 1                                                            |                                                       | 1                   |      |      |                      |     |

### Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS}1 = V_{SS}2 = V_{SS}3 = 0V$

Note 1-1: The mean output current is a mean value measured over 100ms.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

|                               | Ourseland.                          | Dive (Derseeler                                               | Quanditiana                                                                                                                                                                                                                                                      |                                                                    |                            | Specif              | ication                     |      |  |

|-------------------------------|-------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|---------------------|-----------------------------|------|--|

| arameter                      | Symbol                              | Pins/Remarks                                                  | Conditions                                                                                                                                                                                                                                                       | V <sub>DD</sub> [V]                                                | min                        | typ                 | max                         | unit |  |

| rating                        | V <sub>DD</sub> (1)                 | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3         | 0.245µs≤ tCYC≤200µs                                                                                                                                                                                                                                              |                                                                    | 2.8                        |                     | 5.5                         |      |  |

| oly voltage                   |                                     |                                                               | 0.367µs≤ tCYC≤200µs                                                                                                                                                                                                                                              |                                                                    | 2.5                        |                     | 5.5                         |      |  |

| e2-1)                         |                                     |                                                               | 1.47μs≤ tCYC≤200μs                                                                                                                                                                                                                                               |                                                                    | 2.2                        |                     | 5.5                         |      |  |

| nory<br>aining<br>bly voltage | VHD                                 | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3         | RAM and register contents sustained in HOLD mode                                                                                                                                                                                                                 |                                                                    | 2.0                        |                     | 5.5                         |      |  |

| n level input<br>age          | ∨ <sub>IH</sub> (1)                 | Ports 1, 2<br>P71 to P73<br>P70 port input/<br>interrupt side |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | 0.3V <sub>DD</sub><br>+0.7 |                     | V <sub>DD</sub>             |      |  |

|                               | V <sub>IH</sub> (2)                 | Ports 0, 8, 3, C<br>PWM2, PWM3                                |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | 0.3V <sub>DD</sub><br>+0.7 |                     | V <sub>DD</sub>             |      |  |

|                               | V <sub>IH</sub> (3)                 | P70 watchdog timer side                                       |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | 0.9V <sub>DD</sub>         |                     | V <sub>DD</sub>             | V    |  |

|                               | V <sub>IH</sub> (4)                 | XT1, XT2, CF1, RES                                            |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | 0.75V <sub>DD</sub>        |                     | V <sub>DD</sub>             |      |  |

| level input<br>age            | V <sub>IL</sub> (1)                 | Ports 1, 2<br>P71 to P73                                      |                                                                                                                                                                                                                                                                  | 4.0 to 5.5                                                         | V <sub>SS</sub>            |                     | 0.1V <sub>DD</sub><br>+0.4  |      |  |

|                               |                                     | P70 port input/<br>Interrupt side                             |                                                                                                                                                                                                                                                                  | 2.2 to 4.0                                                         | V <sub>SS</sub>            |                     | 0.2V <sub>DD</sub>          |      |  |

|                               | V <sub>IL</sub> (2)                 | Ports 0, 8, 3, C<br>PWM2, PWM3                                |                                                                                                                                                                                                                                                                  | 4.0 to 5.5                                                         | V <sub>SS</sub>            |                     | 0.15V <sub>DD</sub><br>+0.4 |      |  |

|                               |                                     |                                                               |                                                                                                                                                                                                                                                                  | 2.2 to 4.0                                                         | VSS                        |                     | 0.2V <sub>DD</sub>          |      |  |

|                               | V <sub>IL</sub> (3)                 | Port 70 watchdog<br>timer side                                |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | V <sub>SS</sub>            |                     | 0.8V <sub>DD</sub><br>-1.0  |      |  |

|                               | V <sub>IL</sub> (4)                 | XT1, XT2, CF1, RES                                            |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | VSS                        |                     | 0.25V <sub>DD</sub>         |      |  |

| ruction cycle                 | tCYC                                |                                                               |                                                                                                                                                                                                                                                                  | 2.8 to 5.5                                                         | 0.245                      |                     | 200                         |      |  |

|                               |                                     |                                                               |                                                                                                                                                                                                                                                                  | 2.5 to 5.5                                                         | 0.367                      |                     | 200                         | μs   |  |

| e2-2)                         |                                     |                                                               |                                                                                                                                                                                                                                                                  | 2.2 to 5.5                                                         | 1.47                       |                     | 200                         |      |  |

| ernal system                  | FEXCF(1)                            | CF1                                                           | CF2 pin open                                                                                                                                                                                                                                                     | 2.8 to 5.5                                                         | 0.1                        |                     | 12                          |      |  |

| k frequency                   |                                     |                                                               | System clock frequency                                                                                                                                                                                                                                           | 2.5 to 5.5                                                         | 0.1                        |                     | 8                           |      |  |

|                               |                                     |                                                               | <ul> <li>division rate=1/1</li> <li>External system clock<br/>duty=50±5%</li> </ul>                                                                                                                                                                              | 2.2 to 5.5                                                         | 0.1                        |                     | 2                           | MHz  |  |

|                               |                                     |                                                               | CF2 pin open                                                                                                                                                                                                                                                     | 2.8 to 5.5                                                         | 0.2                        |                     | 24.4                        |      |  |

|                               |                                     |                                                               | System clock frequency                                                                                                                                                                                                                                           | 2.5 to 5.5                                                         | 0.1                        |                     | 16                          |      |  |

|                               |                                     |                                                               | division rate=1/2                                                                                                                                                                                                                                                | 2.2 to 5.5                                                         | 0.1                        |                     | 4                           |      |  |

| illation<br>uency             | FmCF(1)                             | CF1, CF2                                                      | 12MHz ceramic oscillation<br>See Fig. 1.                                                                                                                                                                                                                         | 2.8 to 5.5                                                         |                            | 12                  |                             |      |  |

| ie<br>e2-3)                   | FmCF(2)                             | CF1, CF2                                                      | 8MHz ceramic oscillation<br>See Fig. 1.                                                                                                                                                                                                                          | 2.5 to 5.5                                                         |                            | 8                   |                             |      |  |

|                               | FmCF(3)                             | CF1, CF2                                                      | 4MHz ceramic oscillation<br>See Fig. 1.                                                                                                                                                                                                                          | 2.2 to 5.5                                                         |                            | 4                   |                             | MHz  |  |

|                               | FmRC                                |                                                               | Internal RC oscillation                                                                                                                                                                                                                                          | 2.2 to 5.5                                                         | 0.3                        | 1.0                 | 2.0                         |      |  |

|                               | FmMRC                               |                                                               | Frequency variable RC oscillation                                                                                                                                                                                                                                | 2.5 to 5.5                                                         |                            | 16                  |                             |      |  |

| Ē                             | FsX'tal                             | XT1, XT2                                                      | 32.768kHz crystal oscillation<br>See Fig. 2.                                                                                                                                                                                                                     | 2.2 to 5.5                                                         |                            | 32.768              |                             | kHz  |  |

| uency<br>Je                   | FmCF(2)<br>FmCF(3)<br>FmRC<br>FmMRC | CF1, CF2<br>CF1, CF2                                          | See Fig. 1.         8MHz ceramic oscillation         See Fig. 1.         4MHz ceramic oscillation         See Fig. 1.         Internal RC oscillation         Frequency variable RC         oscillation source oscillation         32.768kHz crystal oscillation | 2.8 to 5.5<br>2.5 to 5.5<br>2.2 to 5.5<br>2.2 to 5.5<br>2.5 to 5.5 |                            | 8<br>4<br>1.0<br>16 |                             |      |  |

### Allowable Operating Conditions at $Ta = -40^{\circ}C$ to $+85^{\circ}C$ , $V_{SS}1 = V_{SS}2 = V_{SS}3 = 0V$

Note 2-1: V<sub>DD</sub> must be held greater than or equal to 2.7V in the flash ROM onboard programming mode.

Note 2-2: Relationship between tCYC and oscillation frequency is 3/FmCF at a division ratio of 1/1 and 6/FmCF at a division ratio of 1/2.

Note 2-3: See Tables 1 and 2 for the oscillation constants.

| <b>Electrical Characteristics</b> at $Ta = -40^{\circ}C$ to $+85^{\circ}C$ , V | $V_{SS1} = V_{SS2} = V_{SS3} = 0V$ |

|--------------------------------------------------------------------------------|------------------------------------|

|--------------------------------------------------------------------------------|------------------------------------|

| Parameter                   | Symbol              | Pins/Remarks                                                   | Conditions                                                                                                                     | -                   |                         | Specific           | ation |      |

|-----------------------------|---------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------|--------------------|-------|------|

| Falameter                   | Symbol              | Fills/Itelliaiks                                               | Conditions                                                                                                                     | V <sub>DD</sub> [V] | min                     | typ                | max   | unit |

| High level input<br>current | I <sub>IH</sub> (1) | Ports 0, 1, 2<br>Ports 7, 8<br>Ports 3, C<br>RES<br>PWM2, PWM3 | Output disabled<br>Pull-up resistor off<br>V <sub>IN</sub> =V <sub>DD</sub><br>(Including output Tr's off leakage<br>current)) | 2.2 to 5.5          |                         |                    | 1     |      |

|                             | I <sub>IH</sub> (2) | XT1, XT2                                                       | For input port specification<br>VIN=VDD                                                                                        | 2.2 to 5.5          |                         |                    | 1     |      |

|                             | I <sub>IH</sub> (3) | CF1                                                            | V <sub>IN</sub> =V <sub>DD</sub>                                                                                               | 2.2 to 5.5          |                         |                    | 15    |      |

| Low level input<br>current  | I <sub>IL</sub> (1) | Ports 0, 1, 2<br>Ports 7, 8<br>Ports 3, C<br>RES<br>PWM2, PWM3 | Output disabled<br>Pull-up resistor off<br>VIN=VSS<br>(Including output Tr's off leakage<br>current))                          | 2.2 to 5.5          | -1                      |                    |       | μA   |

|                             | I <sub>IL</sub> (2) | XT1, XT2                                                       | For input port specification<br>VIN=VSS                                                                                        | 2.2 to 5.5          | -1                      |                    |       |      |

|                             | I <sub>IL</sub> (3) | CF1                                                            | V <sub>IN</sub> =V <sub>SS</sub>                                                                                               | 2.2 to 5.5          | -15                     |                    |       |      |

| High level output           | V <sub>OH</sub> (1) | Ports 0, 1, 2                                                  | I <sub>OH</sub> =-1mA                                                                                                          | 4.5 to 5.5          | V <sub>DD</sub> -1      |                    |       |      |

| voltage                     | V <sub>OH</sub> (2) | Ports 3, C                                                     | I <sub>OH</sub> =-0.4mA                                                                                                        | 3.0 to 5.5          | V <sub>DD</sub><br>-0.4 |                    |       |      |