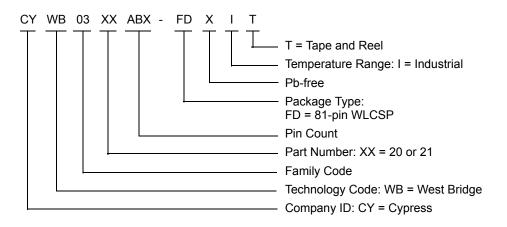

# CYWB0320ABX-FDXI CYWB0321ABX-FDXI

## **Contents**

| Functional Overview                                                                                                     | 3                                |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| The SLIM Architecture                                                                                                   | 3                                |

| 8051 Microprocessor                                                                                                     | 3                                |

| Configuration and Status Registers                                                                                      | 3                                |

| Processor Interface (P-Port)                                                                                            | 3                                |

| USB Interface (U-Port)                                                                                                  |                                  |

| Clocking                                                                                                                |                                  |

| Power Domains                                                                                                           | 4                                |

| Power Modes                                                                                                             | 5                                |

| Pin Assignments                                                                                                         | 6                                |

| Absolute Meximum Detinas                                                                                                |                                  |

| Absolute Maximum Ratings                                                                                                | 13                               |

| Operating Conditions                                                                                                    |                                  |

|                                                                                                                         | 13                               |

| Operating Conditions  DC Characteristics                                                                                | 13<br>14                         |

| Operating Conditions                                                                                                    | 13<br>14<br>16                   |

| Operating Conditions                                                                                                    | 13<br>14<br>16<br>16             |

| Operating Conditions  DC Characteristics  AC Timing Parameters  P Port Interface                                        | 13<br>14<br>16<br>16<br>43       |

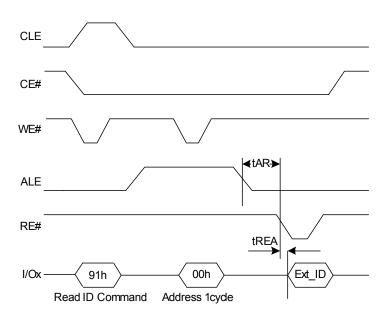

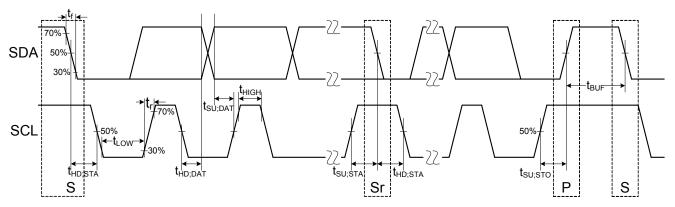

| Operating Conditions  DC Characteristics  AC Timing Parameters  P Port Interface  S Port Interface AC Timing Parameters | 13<br>14<br>16<br>16<br>43<br>45 |

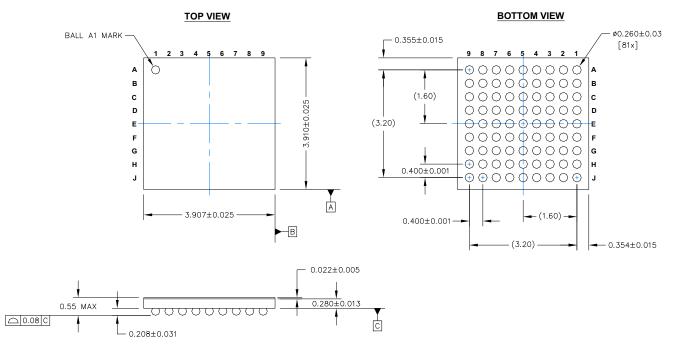

| Package Diagram                         | 48 |

|-----------------------------------------|----|

| Acronyms                                |    |

| Document Conventions                    |    |

| Units of Measure                        | 49 |

| Errata                                  | 50 |

| Part Numbers Affected                   | 50 |

| Arroyo Qualification Status             | 50 |

| Arroyo Errata Summary                   | 50 |

| Errata                                  | 51 |

| Part Numbers Affected                   | 51 |

| Arroyo Qualification Status             | 51 |

| Arroyo Errata Summary                   | 51 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information | 54 |

| Worldwide Sales and Design Support      | 54 |

| Products                                |    |

| PSoC® Solutions                         | 54 |

| Cypress Developer Community             | 54 |

| Technical Support                       | 54 |

## **Functional Overview**

#### The SLIM Architecture

The SLIM architecture enables three different interfaces (P-port, S-port, and U-port) to connect to each other independently.

With this architecture, a device using Arroyo is connected to a PC through a USB, without disturbing any of the device functions. The device can still access mass storage when the PC is synchronizing with the main processor.

The SLIM architecture enables new usage models, in which a PC accesses a mass storage device independent of the main processor, or enumerates access to both the mass storage and the main processor at the same time.

You can do the following in a handset using SLIM architecture:

- Use the phone as a thumb drive.

- Download media files to the phone with all the functionalities still available on the phone.

- Use the same phone as a modem to connect the PC to the internet.

#### 8051 Microprocessor

The 8051 microprocessor embedded in Arroyo does basic transaction management for all transactions between the P-Port, S-Port, and the U-Port. The 8051 does not reside in the data path; it manages the path. The data path is optimized for performance. The 8051 executes firmware that supports SD, SDHC, SDIO, and MMC+ devices at the S-Port.

#### Configuration and Status Registers

The West Bridge<sup>®</sup> Arroyo device includes configuration and status registers that are accessible as memory-mapped registers through the processor interface. The configuration registers enable the system to specify some behaviors of Arroyo. For example, it can mask certain status registers from raising an interrupt. The status registers convey the status of Arroyo, such as the addresses of buffers for read operations.

#### **Processor Interface (P-Port)**

Communication with the external processor is realized through a dedicated processor interface. This interface is configured to support different interface standards. This interface supports multiplexing and nonmultiplexing address or data bus in both synchronous and asynchronous pseudo CRAM-mapped, and nonmultiplexing address or data asynchronous SRAM-mapped memory accesses. The interface also can be configured to a pseudo NAND interface to support the processor's NAND interface. In addition, this interface can be configured to support SPI slave. Asynchronous accesses can reach a bandwidth of up to 66.7 MBps. Synchronous accesses can be performed at 33 MHz across 16 bits for up to 66.7 MBps bandwidth.

The memory address is decoded to access any of the multiple endpoint buffers inside Arroyo. These endpoints serve as buffers for data between each pair of ports; for example, between the processor port and the USB port. The processor writes and reads to these buffers through the memory interface.

Access to these buffers is controlled by using a DMA protocol or using an interrupt to the main processor. These two modes are configured by the external processor.

As a DMA slave, Arroyo generates a DMA request signal to notify the main processor that a specific buffer is ready to be read from or written to. The external processor monitors this signal and polls Arroyo for the specific buffers ready for a read or write operation. It then performs the appropriate read or write operations on the buffer through the processor interface. As a result, the external processor only deals with the buffers to access a storage device connected to Arroyo.

In the Interrupt mode, Arroyo communicates important buffer status changes to the external processor using an interrupt signal. The external processor then polls Arroyo for the specific buffers ready for read or write, and it performs the appropriate read or write operations through the processor interface.

#### **USB Interface (U-Port)**

In accordance with the USB 2.0 specification, Arroyo can operate in both full speed and high speed USB modes. The USB interface consists of the USB transceiver. The USB interface can access and be accessed by both the P-Port and the S-Port.

The Arroyo USB interface supports programmable CONTROL/BULK/INTERRUPT/ISOCHRONOUS endpoints.

#### Mass Storage Support (S-Port)

The S-Port may be configured to support the following:

■ Next-gen SD/SDIO/eMMC+ port

When Arroyo is configured through firmware to support SD/SDIO/MMC+, this interface supports the following:

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 2.0, May 9, 2006.

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 1.10, October 15, 2004.

- SD Specifications Part E1 SDIO specification, Version 1.10, August 18, 2004.

- The Multimedia Card System Specification, MMCA Technical Committee, Version 4.1.

West Bridge Arroyo supports 1-bit and 4-bit SD and SDIO cards; 1-bit, 4-bit, and 8-bit MMC; MMC+ cards. For the SD, SDIO, and MMC/MMC Plus, this block supports one card for one physical bus interface. Arroyo supports SD commands including the multisector program command that is handled by API

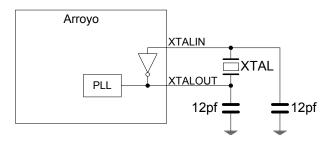

#### Clocking

Arroyo enables connection of an external clock at the XTALIN pin. The power supply level at the crystal supply XVDDQ determines whether a crystal or a clock is provided. If XVDDQ is detected to be 1.8 V, Arroyo assumes that a clock input is provided. For a crystal to be connected, XVDDQ must be 3.3 V.

**Note** Clock inputs at 3.3 V level are not supported.

The 81-pin WLCSP supports 19.2 MHz and 26 MHz external clock input. The crystal or clock frequency selection is shown in Table 1 on page 4.

The XTALIN frequency is independent of the clock and data rate of the 8051 microprocessor or any of the device interfaces (including P-Port and S-Port). The internal PLL applies the proper clock multiply option depending on the input frequency.

For applications that use an external clock source to drive XTALIN, the XTALOUT, pin must be left floating. The external clock source must also stop high or low and not toggle, to achieve the lowest possible current consumption. The requirements for an external clock source are shown in Table 3.

Arroyo has an on-chip oscillator circuit that uses an external 26 MHz (±150 ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 1 mW drive level

- 12 pF (5% tolerance) load capacitors 150 ppm

Note CYWB0321ABX-FDXI does not support crystal.

Figure 1. Crystal Configuration

\* 12 pF capacitor values assumes a trace capacitance of 3 pF per side on a four layer FR4 PCA

Table 1. CYWB0320ABX-FDXI Clock Selection

| XTALSLC | Freq   | Crystal/Clock    |  |  |

|---------|--------|------------------|--|--|

| NA      | 26 MHz | Clock or Crystal |  |  |

Table 2. CYWB0321ABX-FDXI Clock Selection

| XTALSLC | Freq     | Crystal/Clock |  |  |

|---------|----------|---------------|--|--|

| 0       | 19.2 MHz | Clock         |  |  |

| 1       | 26 MHz   | Clock         |  |  |

Table 3. External Clock Requirements

| Parameter  | Description                                  | Specif | Unit        |        |

|------------|----------------------------------------------|--------|-------------|--------|

| Parameter  | Description                                  | Min    | Max         | Oill   |

| Vn (AVDDQ) | Supply Voltage Noise at Frequencies < 50 MHz | _      | 20          | mV p-p |

| PN_100     | Input Phase Noise at 100 Hz                  | _      | <b>–</b> 75 | dBc/Hz |

| PN_1k      | Input Phase Noise at 1 kHz Offset            | -      | -104        | dBc/Hz |

| PN_10k     | Input Phase Noise at 10 kHz Offset           | -      | -120        | dBc/Hz |

| PN_100k    | Input Phase Noise at 100 kHz Offset          | _      | -128        | dBc/Hz |

| PN_1M      | Input Phase Noise at 1 MHz Offset            | -      | -130        | dBc/Hz |

|            | Duty Cycle                                   | 30     | 70          | %      |

|            | Maximum Frequency Deviation                  | _      | 150         | ppm    |

|            | Overshoot                                    | _      | 3           | %      |

|            | Undershoot                                   | _      | -3          | %      |

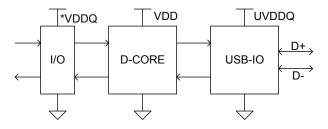

#### **Power Domains**

Arroyo has multiple power domains that serve different purposes within the chip.

VDDQ: This refers to a group of five independent supply domains for the digital I/Os. The nominal voltage level on these

supplies are 1.8 V, 2.5 V, or 3.3 V. Specifically, the four separate I/O power domains are:

- PVDDQ P-Port Processor interface I/O

- SSVDDQ S-Port SD interface I/O

- GVDDQ Other miscellaneous I/O

Document Number: 001-57458 Rev. \*H Page 4 of 54

UVDDQ: This is the 3.3 V nominal supply for the USB I/O and some analog circuits. It also supplies power to the USB transceiver.

VDD: This is the supply voltage for the logic core. The nominal supply voltage level is 1.8 V. This supplies the core logic circuits. The same supply must also be used for AVDDQ.

AVDDQ: This is the 1.8 V supply for PLL and USB serializer analog components. The same supply must also be used for VDD. Maximum permitted noise on AVDDQ is 20 mV p-p.

XVDDQ: This is the clock I/O supply; 3.3 V for XTAL or 1.8 V for an external clock.

Noise guideline for all supplies except AVDDQ is maximum 100 mV p-p. All I/O supplies of Arroyo must be ON when a system is active even if Arroyo is not in use. The core VDD can also be deactivated at any time to preserve power, provided there is a minimum impedance of 1 k $\Omega$  between the VDD pin and ground. All I/Os tristate when the core is disabled.

Figure 2. Arroyo Power Supply Domains

#### Power Supply Sequence

The power supplies are independently sequenced without damaging the part. All power supplies must be up and stable before the device operates. If the supplies are not stable, the remaining domains are in low power (standby) state.

#### **Power Modes**

In addition to the normal operating mode, Arroyo contains several low power states when normal operation is not required.

### Normal Mode

Normal mode is the mode in which Arroyo is fully functional. In this mode data transfer functions described in this document are performed.

## Suspend Mode

This mode is entered internally by 8051 (external processor only initiates entry into this mode through Mailbox commands). This mode is exited by the D+ bus going low, GPIO[0] going to a pre-determined state or by asserting CE# LOW.

In Arroyo's suspend mode:

- The clocks are shut off.

- All I/Os maintain their previous state.

- Core power supply must be retained.

- The states of the configuration registers, endpoint buffers, and the program RAM are maintained. All transactions must be complete before Arroyo enters suspend mode (state of outstanding transactions are not preserved).

- The firmware resumes its operation from where it was suspended, since the program counter is not reset.

- Only inputs that are sensed are RESET#, GPIO[0]/SD\_CD, GPIO[1], SD\_D3, D+, and CE#. The last three are wake up sources (each can be individually enabled or disabled).

- Hard Reset can be performed by asserting the RESET# input, and Arroyo is initialized.

#### Standby Mode

Standby mode is a low power state. This is the lowest power mode of Arroyo while still maintaining external supply levels. This mode is entered through deassertion of the WAKEUP input pin or through internal register settings. To leave this mode, assert WAKEUP, CE#, and RESET#; and change the state of GPIO[0]/SD\_CD, GPIO[1], or SD\_D3.

In this mode all configuration register settings and program RAM contents are preserved. However, data in the buffers or other parts of the data path, if any, is not guaranteed in values. Therefore, the external processor must ensure that the required data is read before putting Arroyo into the standby mode.

In the standby mode:

- The program counter is reset on waking up from standby mode.

- All outputs are tristated and I/O is placed in input only configuration. Values of I/Os in standby mode are listed in the pin assignments table.

- Core power supply must be retained.

- Hard Reset can be performed by asserting the RESET# input, and Arroyo is initialized.

- PLL is disabled.

#### Core Power Down Mode

The core power supply VDD is powered down in this state. AVDDQ is tied to the same supply as VDD and is hence, also powered down. Neither the endpoint buffers, configuration registers nor program RAM maintain state. It is required that all VDDQ power supplies (except AVDDQ) are on and not power downer down in this mode. When UVDDQ is powered down, D+/D- can't be driven by external device.

The core power down mode has two power down options:

- Core only power down VDD power down.

- Core and USB power down VDD and UVDDQ are both powered down.

In these power down options, the endpoint buffers, configuration registers, or the program RAM do not maintain state. It is necessary to reload the firmware on exiting from this mode. It is required that all VDDQ power supplies are on and not powered down in this mode.

# **Pin Assignments**

## Table 4. CYWB0320ABX-FDXI WLCSP Package Pin Assignments

|        |            | Pin Name                 |     |                               |     |                                    |     |                             |       | Pin Description    | Power<br>Domain |

|--------|------------|--------------------------|-----|-------------------------------|-----|------------------------------------|-----|-----------------------------|-------|--------------------|-----------------|

| Ва     | all#       | Pseudo CRAM<br>Interface | I/O | SRAM Interface <sup>[1]</sup> | I/O | ADM (Address/Data<br>Multiplexing) | I/O | PNAND                       | I/O   |                    |                 |

| ,      | J3         | CE#                      | ı   | CE#                           | ı   | CE#                                | ı   | CE#                         | I     | CE#                | PVDDQ           |

|        | E2         | A7                       | ı   | A7                            | I   | External Pull Up                   | I   | A7 => 1:SBD<br>A7 => 0: LBD | I     | A7                 | VGND            |

|        | H1         | A6                       | - 1 | A6                            | I   | SDA                                | I/O | SDA                         | I/O   | A6 or SDA          |                 |

|        | F2         | A5                       | ı   | A5                            | I   | SCL                                | I/O | SCL                         | I/O   | A5 or SCL          |                 |

| (      | G2         | A4                       | I   | A4                            | ı   | External Pull Up                   | ı   | WP#                         | ı     | A4 or WP#          |                 |

| ,      | J1         | A3                       | I   | A3                            | ı   | External Pull Low                  | ı   | External Pull Low           | I     | A3                 |                 |

| I      | H2         | A2                       | ı   | A2                            | ı   | External Pull Up                   | ı   | External Pull Low           | I     | A2                 |                 |

| ,      | J2         | A1                       | - 1 | A1                            | ı   | External Pull Up                   | ı   | R/B#                        | 0     | A1 or R/B#         |                 |

| 1      | H3         | A0                       | I   | A0                            | ı   | External Pull Up                   | ı   | CLE                         | I     | A0 or CLE          |                 |

|        | F3         | DQ[15]                   | I/O | DQ[15]                        | I/O | AD[15]                             | I/O | I/O[15]                     | I/O   | D15, AD15, or IO15 |                 |

| _      | J4         | DQ[14]                   | I/O | DQ[14]                        | I/O | AD[14]                             | I/O | I/O[14]                     | I/O   | D14, AD14, or IO14 |                 |

|        | H4         | DQ[13]                   | I/O | DQ[13]                        | I/O | AD[13]                             | I/O | I/O[13]                     | I/O   | D13, AD13, or IO13 |                 |

| P-Port | G4         | DQ[12]                   | I/O | DQ[12]                        | I/O | AD[12]                             | I/O | I/O[12]                     | I/O   | D12, AD12, or IO12 |                 |

| 급 ㅡ,   | J5         | DQ[11]                   | I/O | DQ[11]                        | I/O | AD[11]                             | I/O | I/O[11]                     | I/O   | D11, AD11, or IO11 |                 |

|        | H5         | DQ[10]                   | I/O | DQ[10]                        | I/O | AD[10]                             | I/O | I/O[10]                     | I/O   | D10, AD10, or IO10 |                 |

| ,      | J6         | DQ[9]                    | I/O | DQ[9]                         | I/O | AD[9]                              | I/O | I/O[9]                      | I/O   | D9, AD9, or IO9    |                 |

| (      | G6         | DQ[8]                    | I/O | DQ[8]                         | I/O | AD[8                               | I/O | I/O[8]                      | I/O   | D8, AD8, or IO8    |                 |

|        | H6         | DQ[7]                    | I/O | DQ[7]                         | I/O | AD[7]                              | I/O | I/O[7]                      | I/O   | D7, AD7, or IO7    |                 |

| ,      | J7         | DQ[6]                    | I/O | DQ[6]                         | I/O | AD[6]                              | I/O | I/O[6]                      | I/O   | D6, AD6, or IO6    |                 |

|        | F6         | DQ[5]                    | I/O | DQ[5]                         | I/O | AD[5]                              | I/O | I/O[5]                      | I/O   | D5, AD5, or IO5    |                 |

| _      | J8         | DQ[4]                    | I/O | DQ[4]                         | I/O | AD[4]                              | I/O | I/O[4]                      | I/O   | D4, AD4, or IO4    |                 |

|        | H7         | DQ[3]                    | I/O | DQ[3]                         | I/O | AD[3]                              | I/O | I/O[3]                      | I/O   | D3, AD3, or IO3    |                 |

| _      | G7         | DQ[2]                    | I/O | DQ[2]                         | I/O | AD[2]                              | I/O | I/O[2]                      | I/O   | D2, AD2, or IO2    |                 |

|        | Н8         | DQ[1]                    | I/O | DQ[1]                         | I/O | AD[1]                              | I/O | I/O[1]                      | I/O   | D1, AD1, or IO1    |                 |

|        | H9         | DQ[0]                    | I/O | DQ[0]                         | I/O | AD[0]                              | I/O | I/O[0]                      | I/O   | D0I, AD0, or IO0   |                 |

| _      | G8         | ADV#                     | ı   |                               | I   | ADV#                               | ı   | ALE                         | I     | Address Valid      |                 |

|        | F8         | OE#                      | ı   | OE#                           | I   | OE#                                | ı   | RE#                         | I     | Output Enable      |                 |

| (      | G9         | WE#                      | - 1 |                               | ı   | WE#                                | I   | WE#                         | ı     | WE#                |                 |

|        | <b>A</b> 7 | INT#                     | 0   |                               | 0   | INT#                               | 0   | INT#                        | 0     | INT Request        | GVDDQ           |

| ᆵ      | D6         | DRQ                      | 0   |                               | 0   | DRQ                                | 0   | DRQ                         | 0     | DMA Request        | VGND            |

|        | C6         | DACK                     | I   |                               | ı   | DACK                               | ı   | DACK                        | I     | DMA ACK            |                 |

|        | D9         | D+                       | 1   | 1                             |     | L                                  |     | 1                           | I/O/Z | USB D+             | UVDDQ           |

| # I    | E9         | D-                       |     |                               |     |                                    |     |                             | I/O/Z | USB D-             | UVSSQ           |

| U-Port | D7         | NC                       |     |                               |     |                                    |     |                             | I/O/Z | Left floating      |                 |

| ⊣ ر    | <b>E</b> 7 | NC                       |     |                               |     |                                    |     |                             | I/O/Z | Left floating      |                 |

## Note

Document Number: 001-57458 Rev. \*H Page 6 of 54

<sup>1.</sup> Errata: When Arroyo is configured to use SRAM for P-port interface, OE should be asserted simultaneously with CE. If this is not possible, OE should be asserted prior to CE. Otherwise, data can be dropped when external processor reads the Arroyo through SRAM interface. For more information, see the "Errata" on page 50 and "Errata" on page 51.

Table 4. CYWB0320ABX-FDXI WLCSP Package Pin Assignments (continued)

|        |                      | Pin Name            |       | Pin Description             | Power<br>Domain |

|--------|----------------------|---------------------|-------|-----------------------------|-----------------|

|        |                      | S-Port Interface    | I/O   |                             |                 |

|        | C4                   | SD_D[7]             | I/O   | SD Data or GPIO             | SSVDDQ          |

|        | A2                   | SD_D[6]             | I/O   | SD Data or GPIO             | VGND            |

|        | В3                   | SD_D[5]             | I/O   | SD Data or GPIO             |                 |

|        | C5                   | SD_D[4]             | I/O   | SD Data or GPIO             |                 |

|        | B4                   | SD_D[3]             | I/O   | SD Data or GPIO             |                 |

|        | A4                   | SD_D[2]             | I/O   | SD Data or GPIO             |                 |

|        | B5                   | SD_D[1]             | I/O   | SD Data or GPIO             |                 |

|        | A5                   | SD_D[0]             | I/O   | SD Data or GPIO             |                 |

|        | A3                   | SD_CLK              | 0     | SD Clock or GPIO            |                 |

| S-Port | A1                   | SD_CMD              | I/O   | SD CMD or GPIO              |                 |

| ų.     | E1                   | <br>PB[7] (GPIO)    | I/O   | GPIOI                       |                 |

| ٠,     | D1                   | PB[6] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | PB[5] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | PB[4] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | PB[3] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | PB[2] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | PB[1] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | PB[0] (GPIO)        | I/O   | GPIOI                       |                 |

|        |                      | TESTTREE            | 0     | Test Mode                   |                 |

|        | F1                   | SCAN (Ext Pull-Low) | I     | Test Mode (Ext<br>Pull-Low) |                 |

| ŗ      | A6                   | SD_CD               | I     | SD CD                       | GVDDQ           |

| ihe    |                      | RESET#              | I     | RESET                       | VGND            |

| Other  | E5                   | WAKEUP              | 1     | Wake Up Signal              |                 |

| Į      | C7                   | TEST[2]             | I     | Test Cfg 2                  | GVDDQ           |

| Conf   | E6                   | TEST[1]             | I     | Test Cfg 1                  | VGND            |

| ပ      | A8                   | TEST[0]             | I     | Test Cfg 0                  |                 |

| ¥      | В9                   | XTALIN              | 1     | Clock IN                    | XVDDQ           |

| CLK    | A9                   | XTALOUT             | 0     | Clock OUT                   | VGND            |

|        |                      | PVDDQ               | Power | Processor I/F VDD           |                 |

|        |                      | UVDDQ               | Power | USBVDD                      |                 |

|        | D5                   | SSVDDQ              | Power | SDIO VDD                    |                 |

|        | B6                   | GVDDQ               |       | Misc I/O VDD                |                 |

|        | C8                   | AVDDQ               | Power | Analog VDD                  |                 |

| 7      | D8                   | XVDDQ               | Power | Crystal VDD                 |                 |

| Power  | E4,<br>G5,<br>F7, F9 | VDD                 | Power | Core VDD                    |                 |

|        |                      | UVSSQ               | Power | USB GND                     | <u> </u>        |

|        |                      | AVSSQ               |       | Analog GND                  | İ               |

|        | C3,<br>D4,<br>E3,    | VGND                |       | Core GND                    |                 |

|        | F5, G3               |                     |       |                             |                 |

Document Number: 001-57458 Rev. \*H Page 7 of 54

## Table 5. CYWB0321ABX-FDXI WLCSP Package Pin Assignments

|        |        |                     | Pin Description | Power<br>Domain     |       |                            |               |

|--------|--------|---------------------|-----------------|---------------------|-------|----------------------------|---------------|

|        | Ball # | PNAND               | I/O             | SPI <sup>[2]</sup>  | I/O   |                            |               |

| ,      | J2     | Ext pull low        | I               | SCK                 | I     | Clock                      | PVDDQ         |

| ,      | J4     | CE#                 | I               | SS#                 | I     | CE# or SPI Slave<br>Select | VGND          |

|        | G5     | SDA                 | I/O             | SDA                 | I/O   | I2C data                   |               |

|        | H2     | SCL                 | I/O             | SCL                 | I/O   | I2C clock                  |               |

| ,      | J1     | WP#                 | I               | Ext pull up         | I     | PNAND WP                   |               |

| Ī      | H3     | A[3] (Ext pull low) | I               | A[3] (Ext pull up)  | I     | A[3]                       |               |

| Ī      | F5     | A[2] (Ext pull low) | I               | A[2] (Ext pull low) | I     | A[2]                       |               |

|        | J3     | RB#                 | 0               | Ext pull up         | I     | PNAND R/B#                 |               |

| r c    | H4     | CLE                 | I               | Ext pull up         | I     | PNAND CLE                  |               |

| P-Port | J6     | I/O[7]              | I/O             | Ext pull up         | I     | IO7                        |               |

| а.     | H6     | I/O[6]              | I/O             | Ext pull up         | I     | IO6                        |               |

| ,      | J7     | I/O[5]              | I/O             | Ext pull up         | I     | IO5                        |               |

| ,      | J8     | I/O[4]              | I/O             | Ext pull up         | I     | IO4                        |               |

| Ī      | H7     | I/O[3]              | I/O             | Ext pull up         | I     | IO3                        |               |

|        | G7     | I/O[2]              | I/O             | Ext pull up         | I     | IO2                        |               |

| Ī      | H8     | I/O[1]              | I/O             | SDO                 | 0     | IO1 or SPI SDO             |               |

| Ī      | H9     | I/O[0]              | I/O             | SDI                 | I     | IO0 or SPI SDI             |               |

|        | G8     | ALE                 | I               | Ext pull up         | I     | Address Valid              |               |

| Ī      | F8     | RE#                 | I               | Ext pull up         | I     | Output Enable              |               |

|        | G9     | WE#                 | I               | Ext pull up         | I     | WE#                        |               |

| Int    | A7     | INT#                | 0               | SINT#               | 0     | INT Request                | GVDDQ<br>VGND |

|        | D9     | D+                  |                 |                     | I/O/Z | USB D+                     | UVDDQ         |

| U-Port | E9     | D-                  |                 |                     | I/O/Z | USB D-                     | UVSSQ         |

| 급      | D7     | NC                  |                 |                     | I/O/Z | Left floating              |               |

| _      | E7     | NC                  |                 |                     | I/O/Z | Left floating              |               |

Document Number: 001-57458 Rev. \*H Page 8 of 54

Errata: When Arroyo is configured to use SPI for Processor-Port (P-Port) interface, transfers from U-Port to P-Port may intermittently fail after wakeup from STANDBY mode. Workaround for this problem is added in SDK version 1.0 or later. For more information, see the "Errata" on page 50 and "Errata" on page 51.

Table 5. CYWB0321ABX-FDXI WLCSP Package Pin Assignments (continued)

|             |                         |          | Pin Description         | Power<br>Domain |                                  |        |

|-------------|-------------------------|----------|-------------------------|-----------------|----------------------------------|--------|

| Ball        | I# SDIO                 | I/O      | GPIO only Configuration | I/O             |                                  |        |

| B2          | SD_D[7]                 | I/O      | PD[7] (GPIO)            | I/O             | SD Data or GPIO                  | SSVDDQ |

| A2          | SD_D[6]                 | I/O      | PD[6] (GPIO)            | I/O             | SD Data or GPIO                  | VGND   |

| C3          | SD_D[5]                 | I/O      | PD[5] (GPIO)            | I/O             | SD Data or GPIO                  |        |

| В3          | SD_D[4]                 | I/O      | PD[4] (GPIO)            | I/O             | SD Data or GPIO                  |        |

| B4          | SD_D[3]                 | I/O      | PD[3] (GPIO)            | I/O             | SD Data or GPIO                  |        |

| C4          | SD_D[2]                 | I/O      | PD[2] (GPIO)            | I/O             | SD Data or GPIO                  |        |

| C5          | SD_D[1]                 | I/O      | PD[1] (GPIO)            | I/O             | SD Data or GPIO                  |        |

| B5          | SD_D[0]                 | I/O      | PD[0] (GPIO)            | I/O             | SD Data or GPIO                  |        |

| A3          | SD_CLK                  | 0        | PC-7 (GPIO)             | I/O             | SD Clock                         |        |

| D4          | SD_CMD                  | I/O      | PC-3 (GPIO)             | I/O             | SD CMD                           |        |

| A1          | SD_POW                  | 0        | PC-6 (GPIO)             | I/O             | SD POW                           |        |

| A5          | SD_WP                   | - 1      | Unused                  | I               | SD WP, GPIO                      |        |

| E2          | SD_RSV                  | I/O      | PB[7] (GPIO)            | I/O             | Connect to                       | SSVDDQ |

| D1 E3       | SD_RSV                  | I/O      | PB[6] (GPIO)            | I/O             | SSVDDQ with 10K pull up resister | VGND   |

| <b>ਨ</b> E3 | SD_RSV                  | I/O      | PB[5] (GPIO)            | I/O             | 1                                |        |

| D2          | SD_RSV                  | I/O      | PB[4] (GPIO)            | I/O             | _                                |        |

| C1          | SD_RSV                  | I/O      | PB[3] (GPIO)            | I/O             | _                                |        |

| D3          | SD_RSV                  | I/O      | PB[2] (GPIO)            | I/O             | _                                |        |

| C2          | SD_RSV                  | I/O      | PB[1] (GPIO)            | I/O             | _                                |        |

| B1          | SD_RSV                  | I/O      | PB[0] (GPIO)            | I/O             | 1                                |        |

| G2          | SD_RSV                  | - 1      | Unused                  | I               | 1                                |        |

| F2          | NC                      | 0        | PA-7 (GPIO)             | I/O             | Left floating                    |        |

| G3          | NC                      | 0        | PC-0 (GPIO)             | I/O             | 1                                |        |

| H1          | NC                      | 0        | N/C                     | 0               | 1                                |        |

| E1          | NC                      | 0        | N/C                     | 0               | 1                                |        |

| F3          | NC                      | 0        | PA-5 (GPIO)             | I/O             | 1                                |        |

| G4          | NC                      | 0        | PA-6 (GPIO)             | I/O             | 1                                |        |

| G1          | NC                      | 0        | PC-2 (GPIO)             | I/O             | 1                                |        |

| B7          | RESETOUT                | 0        | RESETOUT                | 0               | RESETOUT                         | GVDDQ  |

| B6          | PC-5 (GPIO[1])          | I/O      | PC-5 (GPIO[1])          | I/O             | GPIO, SD2 CD4                    | VGND   |

| <u>-</u>    | DO 4 (ODIOM) OD OD      | 0        | DO 4 (ODIOM)            | 1/0             | 0010 004 00                      | _      |

| Other<br>99 | PC-4 (GPIO[0]) or SD_CD | I/O<br>I | PC-4 (GPIO[0])          | I/O             | GPIO, SD1 CD                     |        |

|             |                         | 0        |                         |                 |                                  |        |

| C7          | RESET#                  |          |                         | 1               | RESET                            | 1      |

| D6          | WAKEUP                  |          |                         |                 | Wake Up Signal                   |        |

| A9 XTALSLC  |                         |          | Clock Select            | GVDDQ<br>VGND   |                                  |        |

| A8 F7       | TEST[2]                 |          |                         | I               | Test Cfg 2                       | ]      |

|             | TEST[1]                 |          |                         |                 | Test Cfg 1                       | _      |

| D8          | TEST[0]                 |          |                         |                 | Test Cfg 0                       |        |

| B9          | XTALIN                  |          |                         | I               | Clock IN                         | VGND   |

Document Number: 001-57458 Rev. \*H Page 9 of 54

## Table 5. CYWB0321ABX-FDXI WLCSP Package Pin Assignments (continued)

|       |                             | Pin Name |       | Pin Description   | Power<br>Domain |

|-------|-----------------------------|----------|-------|-------------------|-----------------|

|       | H5, J9                      | PVDDQ    | Power | Processor I/F VDD |                 |

|       | F1                          | SSVDDQ   | Power | SDIO VDD          |                 |

|       | E8                          | UVDDQ    | Power | USB VDD           |                 |

|       | A4                          | SSVDDQ   | Power | SDIO VDD          |                 |

|       | C6                          | GVDDQ    | Power | Misc I/O VDD      |                 |

| -     | C8                          | AVDDQ    | Power | Analog VDD        |                 |

| Power | E5,<br>F4,<br>F6, F9        | VDD      | Power | Core VDD          |                 |

|       | C9                          | UVSSQ    | Power | USB GND           |                 |

|       | B8                          | AVSSQ    | Power | Analog GND        |                 |

|       | D5,<br>E4,<br>E6,<br>G6, J5 | VGND     | Power | Core GND          |                 |

Document Number: 001-57458 Rev. \*H Page 10 of 54

Figure 3. CYWB0320ABX-FDXI WLCSP Ball Map - Top View

|   | 1          | 2          | 3          | 4       | 5       | 6       | 7       | 8       | 9       |   |

|---|------------|------------|------------|---------|---------|---------|---------|---------|---------|---|

| Α | SD_CMD     | SD_D[6]    | SD_CLK     | SD_D[2] | SD_D[0] | GPIO[0] | INT#    | TEST[0] | XTALOUT | Α |

| В | NAND_IO[1] | NAND_IO[0] | SD_D[5]    | SD_D[3] | SD_D[1] | GVDDQ   | RESET#  | AVSSQ   | XTALIN  | В |

| С | NAND_IO[4] | NAND_IO[3] | VGND       | SD_D[7] | SD_D[4] | DACK#   | TEST[2] | AVDDQ   | UVSSQ   | С |

| D | NAND_IO[6] | NAND_IO[5] | NAND_IO[2] | VGND    | SSVDDQ  | DRQ#    | NC      | XVDDQ   | D+      | D |

| E | NAND_IO[7] | A[7]       | VGND       | VDD     | WAKEUP  | TEST[1] | NC      | UVDDQ   | D-      | E |

| F | SCAN       | A[5]       | DQ[15]     | PVDDQ   | VGND    | DQ[5]   | VDD     | OE#     | VDD     | F |

| G | TESTTREE   | A[4]       | VGND       | DQ[12]  | VDD     | DQ[8]   | DQ[2]   | ADV#    | WE#     | G |

| Н | A[6]       | A[2]       | A[0]       | DQ[13]  | DQ[10]  | DQ[7]   | DQ[3]   | DQ[1]   | DQ[0]   | Н |

| J | A[3]       | A[1]       | CE#        | DQ[14]  | DQ[11]  | DQ[9]   | DQ[6]   | DQ[4]   | PVDDQ   | J |

|   | 1          | 2          | 3          | 4       | 5       | 6       | 7       | 8       | 9       | I |

| POWER DOMAIN KEY |            |  |  |  |  |

|------------------|------------|--|--|--|--|

|                  | UVDDQ      |  |  |  |  |

|                  | UVSSQ      |  |  |  |  |

|                  | GVDDQ      |  |  |  |  |

|                  | SSVDDQ     |  |  |  |  |

|                  | VDD/AVDDQ  |  |  |  |  |

|                  | VGND/AVSSQ |  |  |  |  |

|                  | PVDDQ      |  |  |  |  |

|                  | XVDDQ      |  |  |  |  |

Figure 4. CYWB0321ABX-FDXI WLCSP Ball Map – Top View

|   | 1      | 2        | 3       | 4       | 5       | 6       | 7        | 8       | 9       |   |

|---|--------|----------|---------|---------|---------|---------|----------|---------|---------|---|

| Α | SD_POW | SD_D[6]  | SD_CLK  | SSVDDQ  | SD_WP   | GPIO[0] | INT#     | TEST[2] | XTALSLC | Α |

| В | SD_RSV | SD_D[7]  | SD_D[4] | SD_D[3] | SD_D[0] | GPIO[1] | RESETOUT | AVSSQ   | XTALIN  | В |

| С | SD_RSV | SD_RSV   | SD_D[5] | SD_D[2] | SD_D[1] | GVDDQ   | RESET#   | AVDDQ   | UVSSQ   | С |

| D | SD_RSV | SD_RSV   | SD_RSV  | SD_CMD  | VGND    | WAKEUP  | NC       | TEST[0] | D+      | D |

| Е | NC     | SD_RSV   | SD_RSV  | VGND    | VDD     | VGND    | NC       | UVDDQ   | D-      | E |

| F | SSVDDQ | NC       | NC      | VDD     | A[2]    | VDD     | TEST[1]  | RE#     | VDD     | F |

| G | NC     | SD_RSV   | NC      | NC      | SDA     | VGND    | IO[2]    | ALE     | WE#     | G |

| Н | NC     | SCL      | A[3]    | CLE     | PVDDQ   | IO[6]   | IO[3]    | IO[1]   | IO[0]   | Н |

| J | WP#    | Pull-Low | R/B#    | CE#     | VGND    | IO[7]   | IO[5]    | IO[4]   | PVDDQ   | J |

|   | 1      | 2        | 3       | 4       | 5       | 6       | 7        | 8       | 9       |   |

| POWER DOMAIN KEY |            |  |  |  |

|------------------|------------|--|--|--|

|                  | UVDDQ      |  |  |  |

|                  | UVSSQ      |  |  |  |

|                  | GVDDQ      |  |  |  |

|                  | SSVDDQ     |  |  |  |

|                  | VDD/AVDDQ  |  |  |  |

|                  | VGND/AVSSQ |  |  |  |

|                  | PVDDQ      |  |  |  |

## **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested. Storage Temperature ......-65 °C to +150 °C Ambient Temperature with Power Supplied (Industrial) ......-40 °C to +85 °C Supply Voltage to Ground Potential VDD, AVDDQ ......—0.5 V to +2.0 V GVDDQ, PVDDQ, SSVDDQ, UVDDQ, and XVDDQ ......-0.5 V to +4.0 V DC Input Voltage to Any Input Pin ......1.89 V to 3.6 V (Depends on I/O supply voltage. Inputs are not overvoltage tolerant.) DC Voltage applied to Outputs in High Z State ...... -0.5 V to VDDQ + 0.5 V Static Discharge Voltage (ESD) from JESD22-A114 .....> 2000 V Latch up current ......> 200 mA Maximum Output Short Circuit Current for all I/O Configurations. (Vout = 0 V) .....-100 mA

## **Operating Conditions**

| T <sub>A</sub> (Ambient Temperature Under Bias)<br>Industrial | –40 °C to +85 °C |

|---------------------------------------------------------------|------------------|

| VDD, AVDDQ Supply Voltage                                     | 1.7 V to 1.9 V   |

| UVDDQ Supply Voltage                                          | 3.0 V to 3.6 V   |

| PVDDQ, GVDDQ, SSVDDQ                                          |                  |

| Supply Voltage                                                | 1.7 V to 3.6 V   |

| XVDDQ (Crystal I/O) Supply Voltage                            | 3.0 V to 3.6 V   |

| XVDDQ (Ext. Clock I/O) Supply Voltage                         | 1.7 V to 1.9 V   |

Document Number: 001-57458 Rev. \*H Page 13 of 54

## **DC Characteristics**

Table 6. DC Specifications for All Voltage Supplies

| Parameter                       | Description                                                                            | Conditions                                               |         | Min                        | Тур           | Max                    | Unit |

|---------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------|---------|----------------------------|---------------|------------------------|------|

| VDD                             | Core Voltage Supply                                                                    |                                                          |         | 1.7                        | 1.8           | 1.9                    | V    |

| AVDDQ                           | Analog Voltage Supply                                                                  |                                                          |         | 1.7                        | 1.8           | 1.9                    | V    |

| XVDDQ                           | Crystal Voltage Supply                                                                 |                                                          |         | 3.0                        | 3.3           | 3.6                    | V    |

| XVDDQ                           | Clock Voltage Supply                                                                   |                                                          |         | 1.7                        | 1.8           | 1.9                    | V    |

| PVDDQ [3]                       | Processor Interface I/O                                                                |                                                          |         | 1.7                        | 1.8, 2.5, 3.3 | 3.6                    | V    |

| GVDDQ [3]                       | Miscellaneous I/O Voltage<br>Supply                                                    |                                                          |         | 1.7                        | 1.8, 2.5, 3.3 | 3.6                    | V    |

| SSVDDQ [3, 4]                   | S-Port SD I/O Voltage Supply                                                           |                                                          |         | 1.7                        | 1.8, 2.5, 3.3 | 3.6                    | V    |

| UVDDQ <sup>[5]</sup>            | USB Voltage Supply                                                                     |                                                          |         | 3.0                        | 3.3           | 3.6                    | V    |

| V <sub>IH1</sub> <sup>[6]</sup> | Input HIGH Voltage 1                                                                   | All ports except USB,<br>2.0 V ≤ V <sub>CC</sub> ≤ 3.6 V |         | 0.625 ×<br>V <sub>CC</sub> | -             | V <sub>CC</sub> + 0.3  | V    |

| V <sub>IH2</sub> <sup>[6]</sup> | Input HIGH Voltage 2                                                                   | All ports except USB,<br>1.7 V ≤ V <sub>CC</sub> < 2.0 V |         | V <sub>CC</sub> – 0.4      | -             | V <sub>CC</sub> + 0.3  |      |

| V <sub>IL</sub>                 | Input LOW Voltage                                                                      |                                                          |         | -0.3                       | _             | 0.25 × V <sub>CC</sub> | V    |

| V <sub>OH</sub>                 | Output HIGH Voltage                                                                    | $I_{OH}(MAX) = -0.1 \text{ mA}$                          |         | 0.9 × V <sub>CC</sub>      | _             | _                      | V    |

| V <sub>OL</sub>                 | Output LOW Voltage                                                                     | $I_{OL}(MIN) = 0.1 \text{ mA}$                           |         |                            | _             | 0.1 × V <sub>CC</sub>  | V    |

| I <sub>IX</sub>                 | Input Leakage Current                                                                  | All I/O signals held at VDDQ                             | )       | <b>-</b> 1                 | _             | 1                      | μΑ   |

| I <sub>OZ</sub>                 | Output Leakage Current                                                                 | All I/O signals held at VDDQ                             | )       | <b>–</b> 1                 | _             | 1                      | μΑ   |

| I <sub>CC</sub> Core            | Operating Current of Core<br>Voltage Supply (VDD) and<br>Analog Voltage Supply (AVDDQ) | WLCSP package, outputs tri                               | istated | _                          | _             | 115                    | mA   |

| I <sub>CC</sub> Crystal         | Operating Current of Crystal Voltage Supply (XVDDQ) [7]                                | WLCSP package                                            |         | -                          | -             | N/A                    |      |

| I <sub>CC</sub> USB             | Operating Current of USB<br>Voltage Supply (UVDDQ) [7]                                 | Operating and terminated fo<br>speed mode                | r high  | -                          | -             | 25                     | mA   |

| I <sub>SB1</sub>                | Total Standby Current of Arroyo                                                        |                                                          | 25 °C   | TBD                        | TBD           | TBD                    |      |

|                                 | when Device is in Suspend Mode                                                         | , ,                                                      | 85 °C   | TBD                        | TBD           | TBD                    |      |

|                                 |                                                                                        | 2. Outputs and Bidirs high or floating <sup>[7]</sup>    |         |                            |               |                        |      |

|                                 |                                                                                        | 3. XTALOUT floating                                      |         |                            |               |                        |      |

|                                 |                                                                                        | 4. D+ floating, D– grounded                              |         |                            |               |                        |      |

|                                 |                                                                                        | 5. Device in suspend mode                                |         |                            |               |                        |      |

## Notes

- Interfaces with a voltage range are adjustable with respect to the I/O voltage and supports multiple I/O voltages.

The SSVDDQ I/O voltage can be dynamically changed (for example, from high range to low range) as long as the supply voltage undershoot does not surpass the lower minimum voltage limit. SSVDDQ and SNVDDQ levels for SD modes: 2.0 V-3.6 V, MMC modes: 1.7 V-3.6 V.

When U-Port is in a disabled state, UVDDQ can go down to 2.4 V, provided UVDDQ is still the highest supply voltage level.

- V<sub>CC</sub> = pertinent VDDQ value.

The Outputs and Bidirs that are forced low in standby mode can increase I/O supply standby current beyond specified value. -UVDDQ: USB transmitting 50% of the time, receiving 50% of the time.

-PVDDQ/SNVDDQ/SSVDDQ/GVDDQ: Active current depends on I/O activity, bus load and supply level.

## Table 6. DC Specifications for All Voltage Supplies (continued)

| Parameter        | Description                               | Conditions                                                                                      |       | Min | Тур | Max | Unit |

|------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------|-------|-----|-----|-----|------|

| I <sub>SB2</sub> | Total Standby Current of Arroyo           | -,                                                                                              | 25 °C | =   | _   | 52  | μА   |

|                  | when Device is in Standby Mode            | when Device is in Standby Mode (3.0–3.6 V)  2. Outputs and Bidirs High or Floating [7]          | 85 °C | -   | -   | 450 | μА   |

|                  |                                           | XTALOUT Floating     D+ Floating,     D- Grounded                                               |       |     |     |     |      |

| I <sub>SB3</sub> | Total Standby Current of Arroyo           | 3                                                                                               | 25 °C | _   | _   | 28  | μΑ   |

|                  | when Device is in Core Power<br>Down Mode | or Floating <sup>[7]</sup> 2. XTALOUT Floating 3. D+ Floating, D– Grounded 4. Core Powered Down | 85 °C | -   | -   | 139 | μА   |

## Table 7. Capacitance

| Parameter        | Description                         | Conditions                                 | Тур | Max | Unit |

|------------------|-------------------------------------|--------------------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Pin Capacitance, Except D+/D- | TA = 25 °C, f = 1 MHz, $V_{CC} = V_{CCIO}$ | _   | 9   | pF   |

|                  | Input Pin Capacitance, D+/D-        |                                            | _   | 15  |      |

| C <sub>OUT</sub> | Output Pin Capacitance              |                                            | 1   | 10  | pF   |

Document Number: 001-57458 Rev. \*H Page 15 of 54

# **AC Timing Parameters**

## P Port Interface

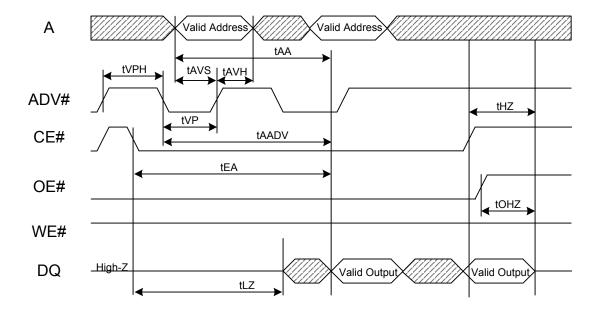

PCRAM Non Multiplexing Asynchronous Mode

**Table 8. Asynchronous Mode Timing Parameters**

| Parameter         | Description                          | Min               | Max  | Unit |

|-------------------|--------------------------------------|-------------------|------|------|

| Read Timing       | Parameters                           | •                 |      | _    |

|                   | Interface Bandwidth (MBPS)           | _                 | 66.7 | MBps |

| t <sub>AA</sub>   | Address to Data Valid                | -                 | 30   | ns   |

| t <sub>OH</sub>   | Data Output Hold from Address Change | 3                 | _    | ns   |

| t <sub>EA</sub>   | Chip Enable to Data Valid            | _                 | 30   | ns   |

| t <sub>AADV</sub> | ADV# to Data Valid Access Time       | _                 | 30   | ns   |

| t <sub>AVS</sub>  | Address Valid to ADV# HIGH           | 5                 | _    | ns   |

| t <sub>AVH</sub>  | ADV# HIGH to Address Hold            | 2 [8]             | -    | ns   |

| t <sub>CVS</sub>  | CE# Low Setup Time to ADV# HIGH      | 5                 | _    | ns   |

| t <sub>VPH</sub>  | ADV# HIGH Time                       | 15 <sup>[9]</sup> | _    | ns   |

| t <sub>VP</sub>   | ADV# Pulse Width LOW                 | 7.5               | -    | ns   |

| t <sub>OE</sub>   | OE# LOW to Data Valid                | -                 | 22.5 | ns   |

| t <sub>OLZ</sub>  | OE# LOW to Low Z                     | 3                 | _    | ns   |

| t <sub>OHZ</sub>  | OE# HIGH to High Z                   | 0                 | 22.5 | ns   |

| $t_{LZ}$          | CE# LOW to Low Z                     | 3                 | _    | ns   |

| $t_{HZ}$          | CE# HIGH to High Z                   | -                 | 22.5 | ns   |

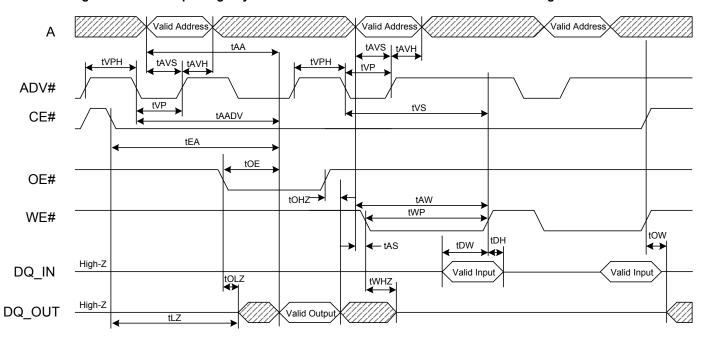

| Write Timing      | Parameters                           | <u>.</u>          |      |      |

| t <sub>CW</sub>   | CE# LOW to Write End                 | 30                | -    | ns   |

| t <sub>AW</sub>   | Address Valid to Write End           | 30                | _    | ns   |

| t <sub>AS</sub>   | Address Setup to Write Start         | 0                 | _    | ns   |

| t <sub>ADVS</sub> | ADV# Setup to Write Start            | 0                 | _    | ns   |

| t <sub>WP</sub>   | WE# Pulse Width                      | 22                | _    | ns   |

| t <sub>WPH</sub>  | WE# HIGH Time                        | 10                | _    | ns   |

| t <sub>CPH</sub>  | CE# HIGH Time                        | 10                | _    | ns   |

| t <sub>AVS</sub>  | Address Valid to ADV# HIGH           | 5                 | _    | ns   |

| t <sub>AVH</sub>  | ADV# HIGH to Address Hold            | 2 [8]             | _    | ns   |

| t <sub>CVS</sub>  | CE# LOW Setup Time to ADV# HIGH      | 5                 | _    | ns   |

| t <sub>VPH</sub>  | ADV# HIGH Time                       | 15 <sup>[9]</sup> | _    | ns   |

| t <sub>VP</sub>   | ADV# Pulse Width LOW                 | 7.5               | _    | ns   |

| t <sub>VS</sub>   | ADV# LOW to End of Write             | 30                | _    | ns   |

| t <sub>DW</sub>   | Data Setup to Write End              | 18                | _    | ns   |

| t <sub>DH</sub>   | Data Hold from Write End             | 0                 | _    | ns   |

| t <sub>WHZ</sub>  | Write to DQ High Z Output            | _                 | 22.5 | ns   |

| t <sub>OW</sub>   | End of Write to Low Z Output         | 3                 | _    | ns   |

#### Notes

8. In applications where back-to-back accesses are not performed on different endpoint addresses, the minimum t<sub>AVH</sub> spec. can be relaxed to 0 ns. 9. In applications where access cycle time is at least 60 ns, t<sub>VPH</sub> can be relaxed to 12 ns.

Valid Address tAA tAVH tAVS tVP tHZ tAADV tCVS CE# tEA tOE OE# tOHZ R/W# tOLZ tLZ DQ High-Z Valid Output

Figure 5. Non Multiplexing Asynchronous Pseudo CRAM mode Single Read Timing Parameters

Figure 6. Non Multiplexing Asynchronous Pseudo CRAM Mode Back to Back Read Timing Parameters

Valid Address Valid Address tAVH tAVS ADV# CE# tCW OE# tAW tWP WE# tOW tDH tDW →I tADVS High-Z DQ\_IN Valid Input Valid Input tWHZ tLZ DQ\_OUT

Figure 7. Non Multiplexing Asynchronous Pseudo CRAM mode Back to Back Write Timing Parameters

Valid Address Valid Address Α tAVS | tAVH tAA tAVS tAVH tVP ADV# tVP tVS CE# tAADV tOE OE# tAW tWP WE# tDH tDW **←** tAS DQ\_IN Valid Input tOLZ tWHZ DQ\_OUT Valid Output

Figure 9. Non Multiplexing Asynchronous Pseudo CRAM Mode Write to Read Timing Parameters

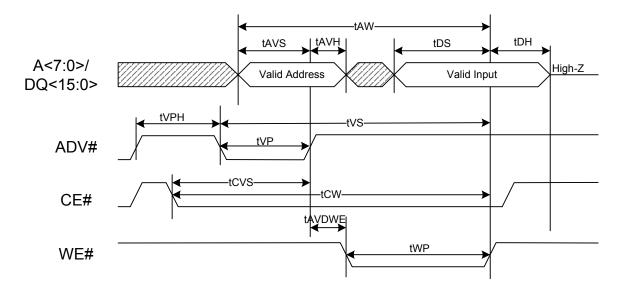

Address Data Multiplexing Asynchronous Mode

# Table 9. Address Data Multiplexing Asynchronous Mode Timing Parameters

| Parameter          | Description                     | Min      | Max  | Unit |

|--------------------|---------------------------------|----------|------|------|

| Read Timing        | Parameters                      | •        | •    | •    |

|                    | Interface Bandwidth             | _        | 50   | MBps |

| t <sub>AA</sub>    | Address to Data Valid           | -        | 30   | ns   |

| t <sub>EA</sub>    | Chip Enable Access Time         | _        | 30   | ns   |

| t <sub>AADV</sub>  | ADV# to Data Valid Access Time  | _        | 30   | ns   |

| t <sub>AVS</sub>   | Address Valid to ADV# HIGH      | 5        | -    | ns   |

| t <sub>AVH</sub>   | ADV# HIGH to Address Hold       | 2        | -    | ns   |

| t <sub>CVS</sub>   | CE# LOW Setup Time to ADV# HIGH | 5        | _    | ns   |

| t <sub>VPH</sub>   | ADV# HIGH Time                  | 15       | _    | ns   |

| $t_{VP}$           | ADV# Pulse Width LOW            | 7.5      | -    | ns   |

| t <sub>AVDOE</sub> | ADV# HIGH to OE# LOW            | 0        | -    | ns   |

| t <sub>OE</sub>    | OE# LOW to Data Valid           | _        | 22.5 | ns   |

| t <sub>OLZ</sub>   | OE# LOW to Low Z                | 3        | _    | ns   |

| t <sub>OHZ</sub>   | OE# HIGH to High Z              | -        | 22.5 | ns   |

| $t_{LZ}$           | CE# LOW to Low Z                | 3        | -    | ns   |

| $t_{HZ}$           | CE# HIGH to High Z              | _        | 22.5 | ns   |

| Write Timing       | Parameters                      | <u>.</u> |      |      |

| t <sub>CW</sub>    | CE# LOW to Write End            | 30       | _    | ns   |

| t <sub>AW</sub>    | Address Valid to Write End      | 30       | -    | ns   |

| t <sub>AVDWE</sub> | ADV# HIGH to Write Start        | 0        | _    | ns   |

| t <sub>WP</sub>    | WE# Pulse Width                 | 22       | -    | ns   |

| t <sub>AVS</sub>   | Address Valid to ADV# HIGH      | 5        | -    | ns   |

| t <sub>AVH</sub>   | ADV# HIGH to Address Hold       | 2        | _    | ns   |

| t <sub>CVS</sub>   | CE# LOW Setup Time to ADV# HIGH | 5        | -    | ns   |

| t <sub>VPH</sub>   | ADV# HIGH Time                  | 15       | -    | ns   |

| $t_{VP}$           | ADV# Pulse Width LOW            | 7.5      | -    | ns   |

| t <sub>VS</sub>    | ADV# LOW to End of Write        | 30       | -    | ns   |

| t <sub>DS</sub>    | Data Setup to Write End         | 18       | -    | ns   |

| t <sub>DH</sub>    | Data Hold from Write End        | 0        | _    | ns   |

Document Number: 001-57458 Rev. \*H Page 20 of 54

tAVS A<7:0>/ High-Z High-Z Valid Address Valid Data DQ<15:0> tAADV ADV# tHZ -tCVS--tEA CE# **▼** tOHZ tAYDOE| tOLZ OE# Logic High WE#

Figure 10. Address Data Multiplexing Asynchronous Single Read Timing Parameters

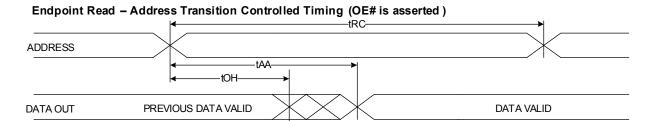

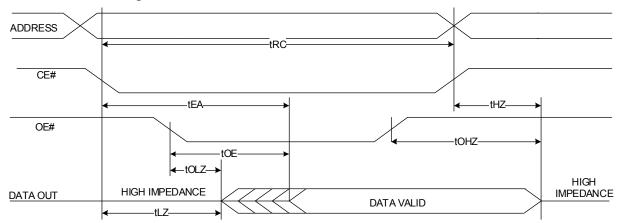

Asynchronous SRAM Mode Timing Parameters

Table 10. Asynchronous SRAM Mode Timing Parameters

| Parameter        | Description                                                                                                                                                                                                                                                 | Min | Max  | Unit |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

|                  | Interface Bandwidth (MBps)                                                                                                                                                                                                                                  | _   | 66.7 | MBps |

| Read Timing I    | Parameters                                                                                                                                                                                                                                                  |     | •    |      |

| t <sub>RC</sub>  | Read Cycle Time                                                                                                                                                                                                                                             | 30  | _    | ns   |

| t <sub>AA</sub>  | Address to Data Valid                                                                                                                                                                                                                                       | -   | 30   | ns   |

| t <sub>OH</sub>  | Data Output Hold from Address Change                                                                                                                                                                                                                        | 3   | _    | ns   |

| t <sub>EA</sub>  | Chip Enable to Data Valid                                                                                                                                                                                                                                   | _   | 30   | ns   |

| t <sub>OE</sub>  | OE# LOW to Data Valid                                                                                                                                                                                                                                       | _   | 22.5 | ns   |

| t <sub>OLZ</sub> | OE# LOW to Low Z                                                                                                                                                                                                                                            | 3   | _    | ns   |

| t <sub>OHZ</sub> | OE# HIGH to High Z                                                                                                                                                                                                                                          | 0   | 22.5 | ns   |

| $t_{LZ}$         | CE# LOW to Low Z                                                                                                                                                                                                                                            | 3   | _    | ns   |

| $t_{HZ}$         | CE# HIGH to High Z                                                                                                                                                                                                                                          | -   | 22.5 | ns   |

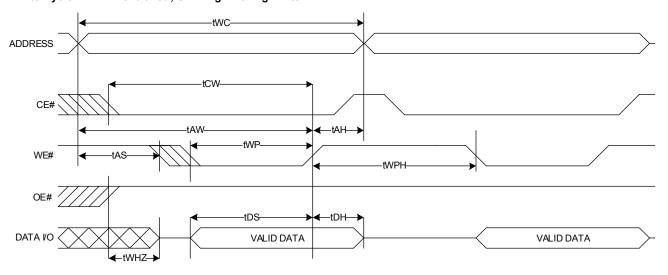

| Write Timing     | Parameters                                                                                                                                                                                                                                                  |     |      | •    |

| t <sub>WC</sub>  | Write Cycle Time                                                                                                                                                                                                                                            | 30  | _    | ns   |

| t <sub>CW</sub>  | CE# LOW to Write End                                                                                                                                                                                                                                        | 30  | _    | ns   |

| t <sub>AW</sub>  | Address Valid to WE# End                                                                                                                                                                                                                                    | 30  | _    | ns   |

| t <sub>AS</sub>  | Address Setup to WE# or CE# Start                                                                                                                                                                                                                           | 0   | _    | ns   |

| t <sub>AH</sub>  | Address Hold Time from WE# or CE# End for PCRAM to SRAM Changes (Astoria is default in PCRAM mode after RESET. This timing is the requirement for the first time to access the P-Port Interface Configuration Register to change the Astoria to PSRAM mode) | 2   | -    | ns   |

|                  | Address Hold Time from WE# or CE# End for PSRAM Mode                                                                                                                                                                                                        | 0   | _    |      |

| t <sub>WP</sub>  | WE# Pulse Width                                                                                                                                                                                                                                             | 22  | -    | ns   |

| t <sub>WPH</sub> | WE# HIGH Time                                                                                                                                                                                                                                               | 10  | _    | ns   |

| t <sub>CPH</sub> | CE# HIGH Time                                                                                                                                                                                                                                               | 10  | -    | ns   |

| t <sub>DS</sub>  | Data Setup to Write End                                                                                                                                                                                                                                     | 18  | -    | ns   |

| t <sub>DH</sub>  | Data Hold from Write End                                                                                                                                                                                                                                    | 0   | _    | ns   |

| t <sub>WHZ</sub> | Write to DQ High Z Output                                                                                                                                                                                                                                   | -   | 22.5 | ns   |

| t <sub>OW</sub>  | End of Write to Low Z Output                                                                                                                                                                                                                                | 3   | _    | ns   |

| t <sub>DPW</sub> | DRQ# Pulse Width                                                                                                                                                                                                                                            | 110 | _    | ns   |

Document Number: 001-57458 Rev. \*H Page 22 of 54

Figure 12. Non Multiplexing Asynchronous SRAM Read Timing Parameters [10]

## **OE# Controlled Timing**

## Note

<sup>10.</sup> Errata: When Arroyo is configured to use SRAM for P-port interface, OE should be asserted simultaneously with CE. If this is not possible, OE should be asserted prior to CE. Otherwise, data can be dropped when external processor reads the Arroyo through SRAM interface. For more information, see the "Errata" on page 50 and "Errata" on page 51.

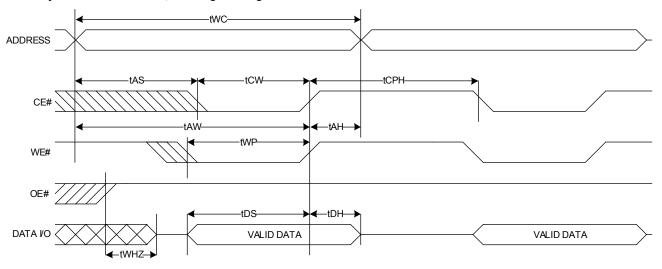

Figure 13. Non Multiplexing Asynchronous SRAM Write Timing (WE# and CE# Controlled)

# Write Cycle 1 WE# Controlled, OE# High During Write

## Write Cycle 2 CE# Controlled, OE# High During Write

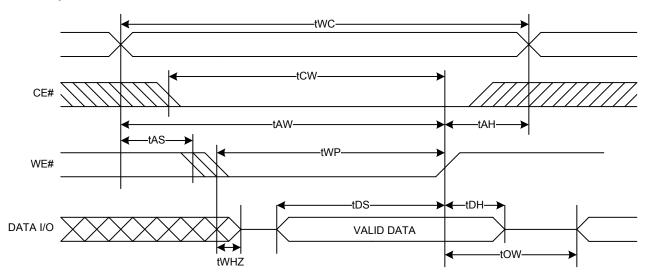

Figure 14. Non Multiplexing Asynchronous SRAM Write Timing (WE# Controlled, OE# LOW)

Write Cycle 3 WE# Controlled. OE# Low

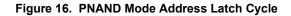

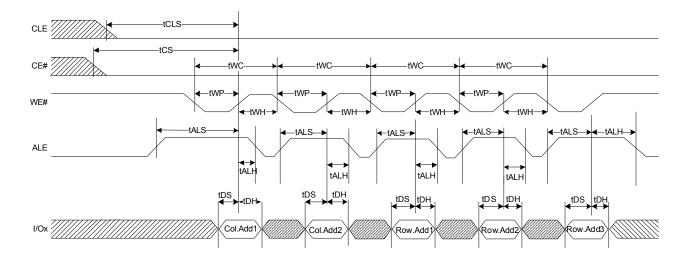

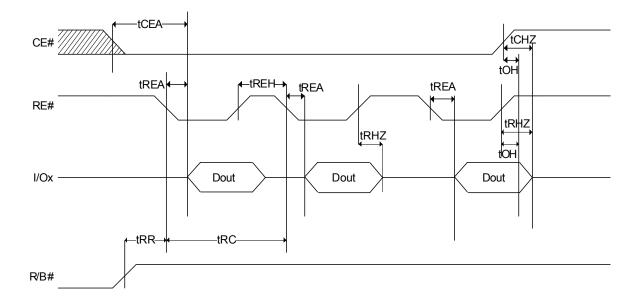

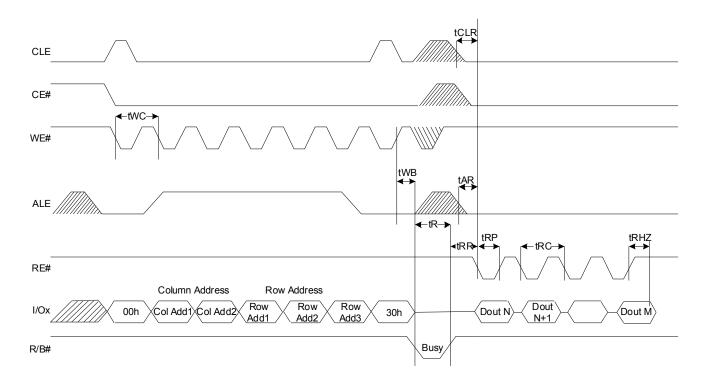

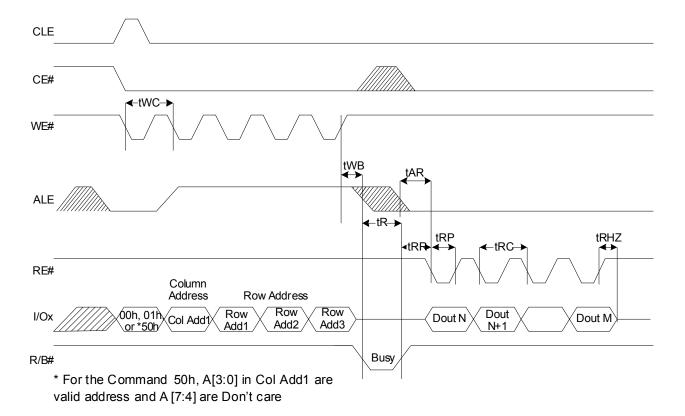

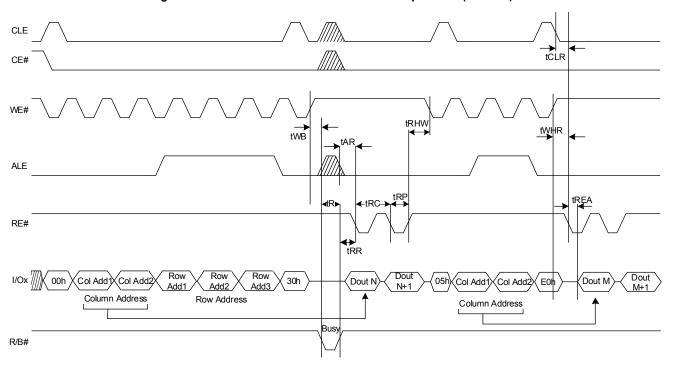

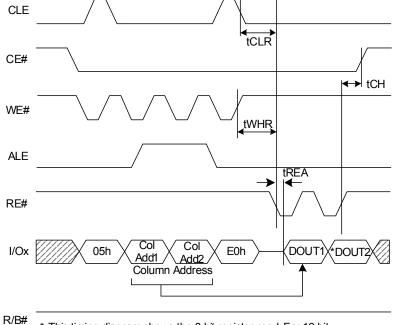

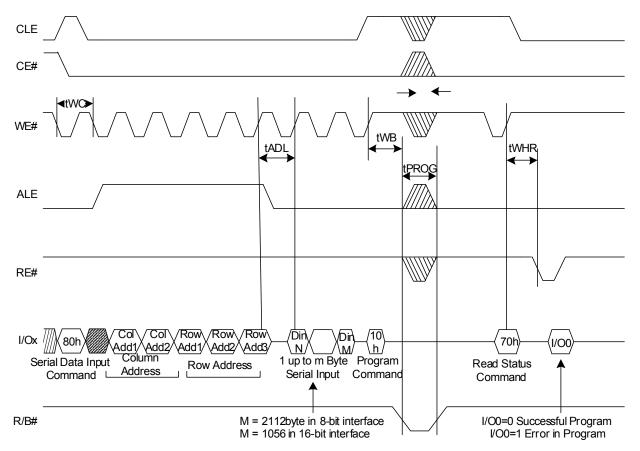

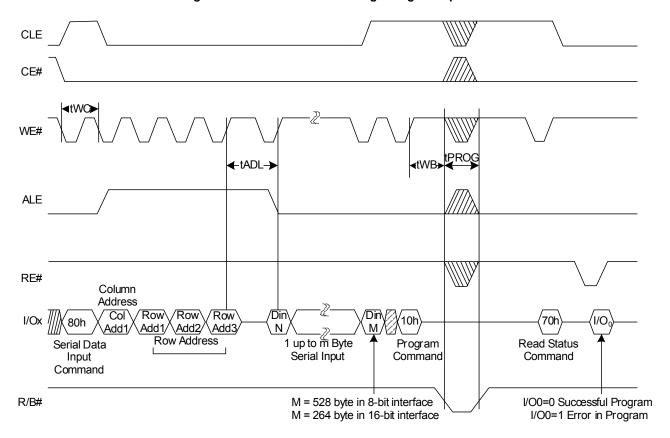

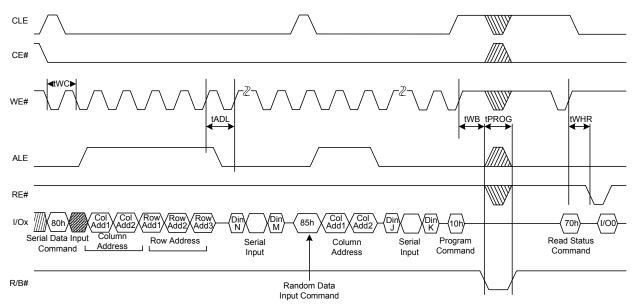

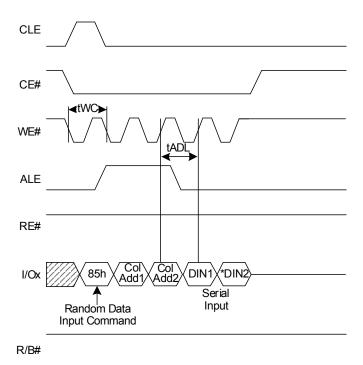

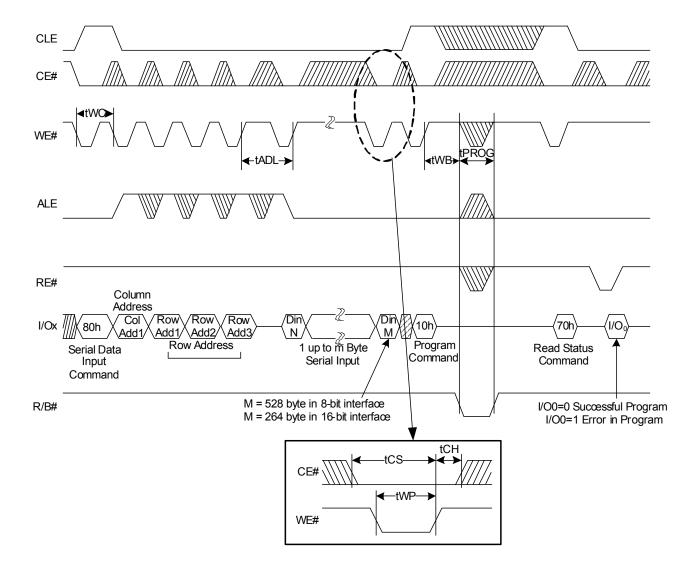

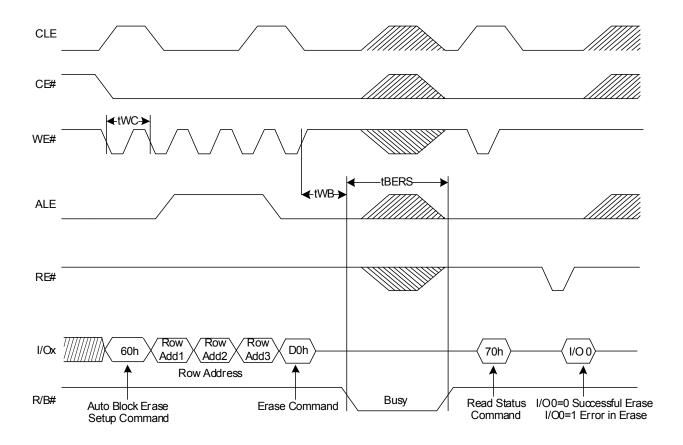

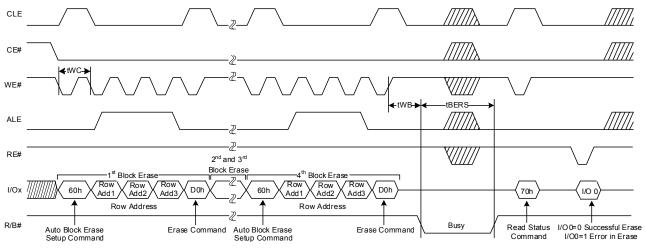

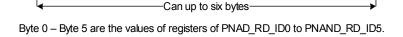

Pseudo NAND (PNAND) Mode

Table 11. PNAND Mode Parameters

| Parameter         | 1                                          | Description                 | Min | Max | Unit |

|-------------------|--------------------------------------------|-----------------------------|-----|-----|------|

|                   |                                            | Non LNA Mode Register Write | 100 | _   | ns   |

| t <sub>ADL</sub>  | Address to Data Loading Time               | Non LNA Mode EP Write       | 100 | _   | ns   |

|                   |                                            | LNA Mode                    | 450 | _   | ns   |

| t <sub>ALH</sub>  | ALE Hold Time                              | •                           | 5   | _   | ns   |

| t <sub>ALS</sub>  | ALE Setup Time                             |                             | 15  | _   | ns   |

| t <sub>AR</sub>   | ALE to RE# Delay                           |                             | 10  | _   | ns   |

| t <sub>BERS</sub> | Block Erase Time MCU/S-Port NAND dependent |                             |     |     |      |

| t <sub>CEA</sub>  | CE# Access Time                            |                             | _   | 35  | ns   |

| t <sub>CH</sub>   | CE# Hold Time                              |                             | 5   | _   | ns   |

| t <sub>CHZ</sub>  | CE# HIGH to O/P HI-Z                       |                             | _   | 40  | ns   |

| t <sub>CLH</sub>  | CLE Hold Time                              |                             | 5   | -   | ns   |

| t <sub>CLR</sub>  | CLE to RE# Time                            |                             | 10  | -   | ns   |

| t <sub>CLS</sub>  | CLE Setup Time                             |                             | 15  | -   | ns   |

| t <sub>CS</sub>   | CE# Setup Time                             |                             | 20  | -   | ns   |

| t <sub>DH</sub>   | Data Hold Time                             |                             | 5   | -   | ns   |

| t <sub>DS</sub>   | Data Setup Time                            |                             | 15  | _   | ns   |

| t <sub>OH</sub>   | Data Output Hold Time                      |                             | 15  | _   | ns   |

**Table 11. PNAND Mode Parameters** (continued)

| Parameter         | Description                                                | Min              | Max                | Unit |