# $\label{eq:continuous} \textbf{AD565A-SPECIFICATIONS} \ \, (\textbf{T}_{A} = 25^{\circ}\text{C}, \, \textbf{V}_{\text{CC}} = 15 \, \text{V}, \, \textbf{V}_{\text{EE}} = 15 \, \text{V}, \, \text{unless otherwise noted.})$

| Parameter                                                                                                                             | Min               | AD565AJ<br>Typ                                    | Max                                | Min               | AD565AK<br>Typ                                  | Max                                  | Unit                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------|------------------------------------|-------------------|-------------------------------------------------|--------------------------------------|-------------------------------------------------------|

| DATA INPUTS <sup>1</sup> (Pins 13 to 24) TTL or 5 V CMOS Input Voltage                                                                |                   |                                                   |                                    |                   |                                                 |                                      |                                                       |

| Bit ON Logic "1" Bit OFF Logic "0" Logic Current (Each Bit)                                                                           | 2.0               |                                                   | 5.5<br>0.8                         | 2.0               |                                                 | 5.5<br>0.8                           | V<br>V                                                |

| Bit ON Logic "1" Bit OFF Logic "0"                                                                                                    |                   | 120<br>35                                         | 300<br>100                         |                   | 120<br>35                                       | 300<br>100                           | μA<br>μA                                              |

| RESOLUTION                                                                                                                            |                   |                                                   | 12                                 |                   |                                                 | 12                                   | Bits                                                  |

| OUTPUT Current Unipolar (All Bits On) Bipolar (All Bits On or Off) Resistance (Exclusive of Span Resistors) Offset Unipolar           | -1.6<br>±0.8<br>6 | -2.0<br>±1.0<br>8                                 | -2.4<br>±1.2<br>10                 | -1.6<br>±0.8<br>6 | -2.0<br>±1.0<br>8                               | -2.4<br>±1.2<br>10                   | mA<br>mA<br>kΩ<br>% of F.S. Range                     |

| Bipolar (Figure 3, R2 = $50 \Omega$ Fixed)<br>Capacitance<br>Compliance Voltage                                                       |                   | 0.01<br>0.05<br>25                                | 0.15                               |                   | 0.01<br>0.05<br>25                              | 0.1                                  | % of F.S. Range<br>pF                                 |

| $T_{ m MIN}$ to $T_{ m MAX}$                                                                                                          | -1.5              |                                                   | +10                                | -1.5              |                                                 | +10                                  | V                                                     |

| ACCURACY (Error Relative to Full Scale) 25°C $T_{\rm MIN} \ {\rm to} \ T_{\rm MAX}$                                                   |                   | $\pm 1/4$ (0.006) $\pm 1/2$ (0.012)               | ±1/2<br>(0.012)<br>±3/4<br>(0.018) |                   | $\pm 1/8$ (0.003) $\pm 1/4$ (0.006)             | ±0.35<br>(0.0084)<br>±1/2<br>(0.012) | LSB<br>% of F.S. Range<br>LSB<br>% of F.S. Range      |

| DIFFERENTIAL NONLINEARITY 25°C                                                                                                        | MONOT             | ±1/2 CONICITY GUA                                 | ±3/4                               | MONOT             | ±1/4<br>FONICITY GUA                            | ±1/2                                 | LSB                                                   |

| T <sub>MIN</sub> to T <sub>MAX</sub> TEMPERATURE COEFFICIENTS                                                                         | MONOI             | ONICITI GUA                                       | RANTEED                            | MONO              | IONICITI GUA                                    | KANTEED                              |                                                       |

| With Internal Reference                                                                                                               |                   |                                                   |                                    |                   |                                                 |                                      |                                                       |

| Unipolar Zero<br>Bipolar Zero<br>Gain (Full Scale)<br>Differential Nonlinearity                                                       |                   | 1<br>5<br>15<br>2                                 | 2<br>10<br>50                      |                   | 1<br>5<br>10<br>2                               | 2<br>10<br>20                        | ppm/°C<br>ppm/°C<br>ppm/°C<br>ppm/°C                  |

| SETTLING TIME TO 1/2 LSB All Bits ON-to-OFF or OFF-to-ON                                                                              |                   | 250                                               | 400                                |                   | 250                                             | 400                                  | ns                                                    |

| FULL-SCALE TRANSITION<br>10% to 90% Delay plus Rise Time<br>90% to 10% Delay plus Fall Time                                           |                   | 15<br>30                                          | 30<br>50                           |                   | 15<br>30                                        | 30<br>50                             | ns<br>ns                                              |

| TEMPERATURE RANGE Operating Storage                                                                                                   | 0<br>-65          |                                                   | +70<br>+150                        | 0<br>-65          |                                                 | +70<br>+150                          | °C<br>°C                                              |

| POWER REQUIREMENTS $V_{CC}$ , +11.4 to +16.5 V dc $V_{EE}$ , -11.4 to -16.5 V dc                                                      |                   | 3<br>-12                                          | 5<br>-18                           |                   | 3<br>-12                                        | 5<br>-18                             | mA<br>mA                                              |

| POWER SUPPLY GAIN SENSITIVITY <sup>2</sup><br>$V_{CC}$ = +11.4 to +16.5 V dc<br>$V_{EE}$ = -11.4 to -16.5 V dc                        |                   | 3<br>15                                           | 10<br>25                           |                   | 3<br>15                                         | 10<br>25                             | ppm of F.S./%<br>ppm of F.S./%                        |

| PROGRAMMABLE OUTPUT RANGES<br>(See Figures 2, 3, 4)                                                                                   |                   | 0 to +5 -2.5 to +2.5 0 to +10 -5 to +5 -10 to +10 | í                                  |                   | 0 to +5 -2.5 to +2 0 to +10 -5 to +5 -10 to +10 |                                      | V<br>V<br>V<br>V                                      |

| EXTERNAL ADJUSTMENTS Gain Error with Fixed 50 Ω Resistor for R2 (Figure 2)                                                            |                   | ±0.1                                              | ±0.25                              |                   | ±0.1                                            | ±0.25                                | % of F.S. Range                                       |

| Bipolar Zero Error with Fixed<br>50 Ω Resistor for R1 (Figure 3)<br>Gain Adjustment Range (Figure 2)<br>Bipolar Zero Adjustment Range | ±0.25<br>±0.15    | ±0.05                                             | ±0.15                              | ±0.25<br>±0.15    | ±0.05                                           | ±0.1                                 | % of F.S. Range<br>% of F.S. Range<br>% of F.S. Range |

| REFERENCE INPUT Input Impedance                                                                                                       | 15                | 20                                                | 25                                 | 15                | 20                                              | 25                                   | kΩ                                                    |

| REFERENCE OUTPUT Voltage Current (Available for External Loads) <sup>3</sup>                                                          | 9.90              | 10.00                                             | 10.10                              | 9.90              | 10.00                                           | 10.10                                | V                                                     |

| POWER DISSIPATION                                                                                                                     | 1.5               | 2.5                                               | 345                                | 1.5               | 2.5                                             | 345                                  | mA<br>mW                                              |

| TOWER DISSIFATION                                                                                                                     |                   | 44)                                               | 343                                |                   | 440                                             | 545                                  | 111 W                                                 |

Specifications subject to change without notice.

NOTES  $^1$ The digital inputs are guaranteed but not tested over the operating temperature range.  $^2$ The power supply gain sensitivity is tested in reference to a  $V_{CC}$ ,  $V_{EE}$  of  $\pm 15$  V dc.  $^3$ For operation at elevated temperatures, the reference cannot supply current for external loads. It, therefore, should be buffered if additional loads are to be supplied.

| Parameter                                                                                          | Min         | AD565AS<br>Typ         | Max             | Min         | AD565AT<br>Typ         | Max                   | Unit                   |

|----------------------------------------------------------------------------------------------------|-------------|------------------------|-----------------|-------------|------------------------|-----------------------|------------------------|

| DATA INPUTS <sup>1</sup> (Pins 13 to 24)<br>TTL or 5 V CMOS                                        |             |                        |                 |             |                        |                       |                        |

| Input Voltage<br>Bit ON Logic "1"                                                                  | 2.0         |                        | 5.5             | 2.0         |                        | 5.5                   | V                      |

| Bit OFF Logic "0"                                                                                  | 2.0         |                        | 0.8             | 2.0         |                        | 0.8                   | V                      |

| Logic Current (Each Bit)                                                                           |             |                        |                 |             |                        |                       |                        |

| Bit ON Logic "1"                                                                                   |             | 120<br>35              | 300<br>100      |             | 120<br>35              | 300                   | μA<br>μA               |

| Bit OFF Logic "0" RESOLUTION                                                                       |             | 33                     | 12              |             | 33                     | 100                   | Bits                   |

| OUTPUT                                                                                             |             |                        | 12              |             |                        | 12                    | DIIS                   |

| Current                                                                                            |             |                        |                 |             |                        |                       |                        |

| Unipolar (All Bits On)                                                                             | -1.6        | -2.0                   | -2.4            | -1.6        | -2.0                   | -2.4                  | mA                     |

| Bipolar (All Bits On or Off)                                                                       | ±0.8        | ±1.0<br>8              | ±1.2            | ±0.8        | $\pm 1.0$              | ±1.2                  | mA                     |

| Resistance (Exclusive of Span Resistors) Offset                                                    | 6           | 8                      | 10              | 6           | 8                      | 10                    | kΩ                     |

| Unipolar                                                                                           |             | 0.01                   | 0.05            |             | 0.01                   | 0.05                  | % of F.S. Range        |

| Bipolar (Figure 3, R2 = 50 $\Omega$ Fixed)                                                         |             | 0.05                   | 0.15            |             | 0.05                   | 0.1                   | % of F.S. Range        |

| Capacitance Compliance Voltage                                                                     |             | 25                     |                 |             | 25                     |                       | pF                     |

| $T_{MIN}$ to $T_{MAX}$                                                                             | -1.5        |                        | +10             | -1.5        |                        | +10                   | V                      |

| ACCURACY (Error Relative to                                                                        |             |                        |                 |             |                        |                       |                        |

| Full Scale) 25°C                                                                                   |             | ±1/4                   | ±1/2            |             | ±1/8                   | ±0.35                 | LSB                    |

| $T_{MIN}$ to $T_{MAX}$                                                                             |             | (0.006)<br>$\pm 1/2$   | (0.012)<br>±3/4 |             | (0.003)<br>$\pm 1/4$   | (0.0084)<br>$\pm 1/2$ | % of F.S. Range<br>LSB |

| 1 MIN to 1 MAX                                                                                     |             | (0.012)                | (0.018)         |             | (0.006)                | (0.012)               | % of F.S. Range        |

| DIFFERENTIAL NONLINEARITY                                                                          |             |                        |                 |             |                        |                       |                        |

| 25°C                                                                                               | MONO        | ±1/2                   | ±3/4            | MONOT       | ±1/4                   | ±1/2                  | LSB                    |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                                               | MONO        | IONICITY G             | UARANTEED       | MONOI       | CONICITY GU            | ARANTEED              |                        |

| TEMPERATURE COEFFICIENTS With Internal Reference                                                   |             |                        |                 |             |                        |                       |                        |

| Unipolar Zero                                                                                      |             | 1                      | 2               |             | 1                      | 2                     | ppm/°C                 |

| Bipolar Zero                                                                                       |             | 5                      | 10              |             | 5                      | 10                    | ppm/°C                 |

| Gain (Full Scale) Differential Nonlinearity                                                        |             | 15<br>2                | 30              |             | 10<br>2                | 15                    | ppm/°C                 |

| SETTLING TIME TO 1/2 LSB                                                                           |             |                        |                 |             |                        |                       | ppm/°C                 |

| All Bits ON-to-OFF or OFF-to-ON                                                                    |             | 250                    | 400             |             | 250                    | 400                   | ns                     |

| FULL-SCALE TRANSITION                                                                              |             |                        |                 |             |                        |                       |                        |

| 10% to 90% Delay plus Rise Time                                                                    |             | 15                     | 30              |             | 15                     | 30                    | ns                     |

| 90% to 10% Delay plus Fall Time                                                                    |             | 30                     | 50              |             | 30                     | 50                    | ns                     |

| TEMPERATURE RANGE Operating                                                                        | -55         |                        | +125            | -55         |                        | +125                  | °C                     |

| Storage                                                                                            | -65         |                        | +150            | -65         |                        | +150                  | °C                     |

| POWER REQUIREMENTS                                                                                 |             |                        |                 |             |                        |                       |                        |

| V <sub>CC</sub> , +11.4 to +16.5 V dc                                                              |             | 3                      | 5               |             | 3                      | 5                     | mA                     |

| V <sub>EE</sub> , -11.4 to -16.5 V dc                                                              |             | -12                    | -18             |             | -12                    | -18                   | mA                     |

| POWER SUPPLY GAIN SENSITIVITY <sup>2</sup>                                                         |             | 3                      | 10              |             | 3                      | 10                    | ppm of F.S./%          |

| $V_{CC} = +11.4 \text{ to } +16.5 \text{ V dc}$<br>$V_{EE} = -11.4 \text{ to } -16.5 \text{ V dc}$ |             | 15                     | 25              |             | 15                     | 25                    | ppm of F.S./%          |

| PROGRAMMABLE OUTPUT RANGES                                                                         |             |                        |                 |             |                        |                       |                        |

| (See Figures 2, 3, 4)                                                                              |             | 0 to +5                |                 |             | 0 to +5                |                       | V                      |

|                                                                                                    |             | -2.5 to $+2$           | .5              |             | -2.5 to $+2.5$         | 5                     | V                      |

|                                                                                                    |             | 0 to +10               |                 |             | 0 to +10               |                       | V                      |

|                                                                                                    |             | −5 to +5<br>−10 to +10 | ,               |             | −5 to +5<br>−10 to +10 |                       | V<br>V                 |

| EXTERNAL ADJUSTMENTS                                                                               |             | -10 to 110             | <u>'</u>        |             | -10 to 110             |                       | v                      |

| Gain Error with Fixed 50 $\Omega$                                                                  |             |                        |                 |             |                        |                       |                        |

| Resistor for R2 (Figure 2)                                                                         |             | $\pm 0.1$              | ±0.25           |             | $\pm 0.1$              | ±0.25                 | % of F.S. Range        |

| Bipolar Zero Error with Fixed<br>50 $\Omega$ Resistor for R1 (Figure 3)                            |             | ±0.05                  | ±0.15           |             | ±0.05                  | ±0.1                  | % of F.S. Range        |

| Gain Adjustment Range (Figure 2)                                                                   | ±0.25       | ±0.03                  | -0.13           | ±0.25       | ±0.09                  | -0.1                  | % of F.S. Range        |

| Bipolar Zero Adjustment Range                                                                      | ±0.15       |                        |                 | ±0.15       |                        |                       | % of F.S. Range        |

|                                                                                                    |             | 20                     | 25              | 1.5         | 20                     | 25                    | 1.0                    |

| REFERENCE INPUT                                                                                    | 1.5         |                        | '15             | 15          | 20                     | 25                    | kΩ                     |

| REFERENCE INPUT<br>Input Impedance                                                                 | 15          | 20                     | 25              | 13          |                        |                       |                        |

| REFERENCE INPUT Input Impedance REFERENCE OUTPUT                                                   |             |                        |                 |             |                        |                       |                        |

| REFERENCE INPUT<br>Input Impedance                                                                 | 9.90<br>1.5 | 10.00<br>2.5           | 10.10           | 9.90<br>1.5 | 10.00<br>2.5           | 10.10                 | V<br>mA                |

Specifications shown in **boldface** are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in **boldface** are tested on all production units.

Specification subject to change without notice.

REV. F -3-

# $\label{eq:AD566A-SPECIFICATIONS} \textbf{(} \textbf{T}_{A} = 25^{\circ}\textbf{C} \textbf{,} \textbf{V}_{EE} = -15 \textbf{ V} \textbf{,} \textbf{ unless otherwise noted} \textbf{)}$

| Parameter                                                                                     | Min            | AD566AJ<br>Typ         | Max               | Min            | AD566AK<br>Typ         | Max               | Unit                               |

|-----------------------------------------------------------------------------------------------|----------------|------------------------|-------------------|----------------|------------------------|-------------------|------------------------------------|

| DATA INPUTS <sup>1</sup> (Pins 13 to 24)                                                      |                |                        |                   |                |                        |                   |                                    |

| TTL or 5 V CMOS Input Voltage                                                                 |                |                        |                   |                |                        |                   |                                    |

| Bit ON Logic "1"                                                                              | 2.0            |                        | 5.5               | 2.0            |                        | 5.5               | V                                  |

| Bit OFF Logic "0"<br>Logic Current (Each Bit)                                                 | 0              |                        | 0.8               | 0              |                        | 0.8               | V                                  |

| Bit ON Logic "1"                                                                              |                | 120                    | 300               |                | 120                    | 300               | μΑ                                 |

| Bit OFF Logic "0" RESOLUTION                                                                  |                | 35                     | 100               |                | 35                     | 100               | μA<br>Bits                         |

| OUTPUT                                                                                        | +              |                        | 12                |                |                        | 12                | DILS                               |

| Current                                                                                       |                |                        |                   |                |                        |                   |                                    |

| Unipolar (All Bits On) Bipolar (All Bits On or Off) Resistance (Exclusive of Span Resistors)  | -1.6<br>±0.8   | -2.0<br>±1.0<br>8      | -2.4<br>±1.2      | -1.6<br>±0.8   | -2.0<br>±1.0<br>8      | -2.4<br>±1.2      | mA<br>mA<br>kΩ                     |

| Offset                                                                                        |                | -                      |                   |                | -                      |                   |                                    |

| Unipolar (Adjustable to Zero per Figure 3)<br>Bipolar (Figure 4, R1 and R2 = 50 Ω Fixed)      |                | 0.01<br>0.05           | 0.05<br>0.15      |                | 0.01<br>0.05           | 0.05<br>0.1       | % of F.S. Range<br>% of F.S. Range |

| Capacitance                                                                                   |                | 25                     |                   |                | 25                     |                   | pF                                 |

| Compliance Voltage $T_{ m MIN}$ to $T_{ m MAX}$                                               | -1.5           |                        | +10               | -1.5           |                        | +10               | V                                  |

| ACCURACY (Error Relative to                                                                   |                |                        | -                 |                |                        |                   | ·                                  |

| Full Scale) 25°C                                                                              |                | $\pm 1/4$ (0.006)      | $\pm 1/2$ (0.012) |                | $\pm 1/8$ (0.003)      | ±0.35<br>(0.0084) | LSB<br>% of F.S. Range             |

| $T_{MIN}$ to $T_{MAX}$                                                                        |                | ±1/2                   | ±3/4              |                | ± 1/4                  | ±1/2              | LSB                                |

|                                                                                               |                | (0.012)                | (0.018)           |                | (0.006)                | (0.012)           | % of F.S. Range                    |

| DIFFERENTIAL NONLINEARITY<br>25°C                                                             |                | ±1/2                   | ±3/4              |                | $\pm1/4$               | ±1/2              | LSB                                |

| $T_{MIN}$ to $T_{MAX}$                                                                        | MONO           | TONICITY G             |                   | MONOT          | ONICITY GUA            |                   |                                    |

| TEMPERATURE COEFFICIENTS                                                                      |                |                        | 2                 |                | 1                      | 2                 | 100                                |

| Unipolar Zero<br>Bipolar Zero                                                                 |                | 1<br>5                 | 2<br>10           |                | 1<br>5                 | 2<br>10           | ppm/°C<br>ppm/°C                   |

| Gain (Full Scale)                                                                             |                | 7                      | 10                |                | 3                      | 5                 | ppm/°C                             |

| Differential Nonlinearity SETTLING TIME TO 1/2 LSB                                            | -              | 2                      |                   |                | 2                      |                   | ppm/°C                             |

| All Bits ON-to-OFF or OFF-to-ON                                                               |                | 250                    | 350               |                | 250                    | 350               | ns                                 |

| FULL-SCALE TRANSITION                                                                         |                |                        |                   |                |                        |                   |                                    |

| 10% to 90% Delay plus Rise Time<br>90% to 10% Delay plus Fall Time                            |                | 15<br>30               | 30<br>50          |                | 15<br>30               | 30<br>50          | ns<br>ns                           |

| POWER REQUIREMENTS                                                                            |                | 30                     |                   |                |                        | 30                | 110                                |

| V <sub>EE</sub> , -11.4 to -16.5 V dc                                                         |                | -12                    | -18               |                | -12                    | -18               | mA                                 |

| POWER SUPPLY GAIN SENSITIVITY <sup>2</sup><br>$V_{EE} = -11.4 \text{ to } -16.5 \text{ V dc}$ |                | 15                     | 25                |                | 15                     | 25                | ppm of F.S./%                      |

| PROGRAMMABLE OUTPUT RANGES                                                                    |                | 13                     | 23                |                | 13                     | 23                | ppin of 1 .5.770                   |

| (see Figures 3, 4, 5)                                                                         |                | 0 to +5                | _                 |                | 0 to +5                | _                 | V                                  |

|                                                                                               |                | -2.5 to +2<br>0 to +10 | .5                |                | -2.5 to +2<br>0 to +10 | .5                | V<br>V                             |

|                                                                                               |                | −5 to +5               |                   |                | -5 to +5               |                   | V                                  |

| EXTERNAL ADJUSTMENTS                                                                          | -              | -10 to +10             | )                 |                | -10 to +10             | )                 | V                                  |

| Gain Error with Fixed 50 $\Omega$                                                             |                |                        |                   |                |                        |                   |                                    |

| Resistor for R2 (Figure 3)                                                                    |                | $\pm 0.1$              | $\pm 0.25$        |                | $\pm 0.1$              | ±0.25             | % of F.S. Range                    |

| Bipolar Zero Error with Fixed<br>50 $\Omega$ Resistor for R1 (Figure 4)                       |                | ±0.05                  | ±0.15             |                | ±0.05                  | ±0.1              | % of F.S. Range                    |

| Gain Adjustment Range (Figure 3)<br>Bipolar Zero Adjustment Range                             | ±0.25<br>±0.15 |                        |                   | ±0.25<br>±0.15 |                        |                   | % of F.S. Range<br>% of F.S. Range |

| REFERENCE INPUT                                                                               | ±0.15          |                        |                   | ±0.15          |                        |                   | % of F.S. Kange                    |

| Input Impedance                                                                               | 15             | 20                     | 25                | 15             | 20                     | 25                | kΩ                                 |

| POWER DISSIPATION                                                                             |                | 180                    | 300               |                | 180                    | 300               | mW                                 |

| MULTIPLYING MODE PERFORMANCE (All Models) Ouadrants                                           |                | Two (2): I             | Bipolar Operatio  | n at Digital   | Innut Only             |                   |                                    |

| Reference Voltage                                                                             |                | 1 V to 10              | V, Unipolar       | Ü              | 1 3                    |                   |                                    |

| Accuracy Reference Feedthrough (Unipolar Mode,                                                |                | 10 Bits (±             | 0.05% of Reduc    | ed F.S.) for   | 1 V dc Reference       | Voltage           |                                    |

| All Bits OFF, and 1 V to 10 V [p-p], Sine Wave                                                |                |                        |                   |                |                        |                   |                                    |

| Frequency for 1/2 LSB [p-p] Feedthrough) Output Slew Rate 10%–90%                             |                | 40<br>5                |                   |                |                        |                   | kHz typ<br>mA/μs                   |

| 90%-10%                                                                                       |                | 1                      |                   |                |                        |                   | mA/μs                              |

| Output Settling Time (All Bits ON and a 0 V–10 V<br>Step Change in Reference Voltage)         |                | 1.5 μs to 0            | 01% F S           |                |                        |                   |                                    |

| CONTROL AMPLIFIER                                                                             | +              | 1.5 μs το 0            | .01/01.0.         |                |                        |                   |                                    |

| Full Power Bandwidth                                                                          |                | 300                    |                   |                |                        |                   | kHz                                |

| Small-Signal Closed-Loop Bandwidth                                                            |                | 1.8                    |                   |                |                        |                   | MHz                                |

REV. F -4-

NOTES  $^1$ The digital input levels are guaranteed but not tested over the temperature range.  $^2$ The power supply gain sensitivity is tested in reference to a  $V_{EE}$  of -1.5 V dc.

Specifications subject to change without notice.

| Parameter                                                                                                                             | Min            | AD566AS<br>Typ                                 | Max                                                 | Min            | AD566AT<br>Typ                                 | Max                                  | Unit                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------|-----------------------------------------------------|----------------|------------------------------------------------|--------------------------------------|-------------------------------------------------------|

| DATA INPUTS <sup>1</sup> (Pins 13 to 24)<br>TTL or 5 V CMOS                                                                           |                |                                                |                                                     |                |                                                |                                      |                                                       |

| Input Voltage Bit ON Logic "1" Bit OFF Logic "0" Logic Current (Bach Bit)                                                             | 2.0            |                                                | 5.5<br>0.8                                          | 2.0<br>0       |                                                | 5.5<br>0.8                           | V<br>V                                                |

| Bit ON Logic "1" Bit OFF Logic "0"                                                                                                    |                | 120<br>35                                      | 300<br>100                                          |                | +120<br>+35                                    | 300<br>100                           | μΑ<br>μΑ                                              |

| RESOLUTION                                                                                                                            |                |                                                | 12                                                  |                |                                                | 12                                   | Bits                                                  |

| OUTPUT Current Unipolar (All Bits On) Bipolar (All Bits On or Off)                                                                    | -1.6<br>±0.8   | -2.0<br>±1.0                                   | -2.4<br>±1.2                                        | -1.6<br>±0.8   | -2.0<br>±1.0                                   | -2.4<br>±1.2                         | mA<br>mA                                              |

| Resistance (Exclusive of Span Resistors) Offset Unipolar (Adjustable to Zero per Figure 3)                                            | 6              | 0.01                                           | 10                                                  | 6              | 8<br>0.01                                      | 10                                   | kΩ<br>% of F.S. Range                                 |

| Bipolar (Figure 4, R1 and R2 = $50 \Omega$ Fixed)<br>Capacitance<br>Compliance Voltage                                                |                | 0.05<br>25                                     | 0.15                                                |                | 0.05<br>25                                     | 0.1                                  | % of F.S. Range<br>pF                                 |

| $T_{MIN}$ to $T_{MAX}$                                                                                                                | -1.5           |                                                | +10                                                 | -1.5           |                                                | +10                                  | V                                                     |

| ACCURACY (Error Relative to Full Scale) 25°C $T_{MIN} \ to \ T_{MAX}$                                                                 |                | $\pm 1/4$ (0.006) $\pm 1/2$ (0.012)            | ±1/2<br>(0.012)<br>±3/4<br>(0.018)                  |                | $\pm 1/8$ (0.003) $\pm 1/4$ (0.006)            | ±0.35<br>(0.0084)<br>±1/2<br>(0.012) | LSB<br>% of F.S. Range<br>LSB<br>% of F.S. Range      |

| DIFFERENTIAL NONLINEARITY 25°C                                                                                                        |                | ±1/2                                           | ±3/4                                                |                | ±1/4                                           | ±1/2                                 | LSB                                                   |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                  | MONO           | CONICITY GU                                    | JARANTEED                                           | MONO           | TONICITY GU                                    | ARANTEED                             |                                                       |

| TEMPERATURE COEFFICIENTS Unipolar Zero Bipolar Zero Gain (Full Scale) Differential Nonlinearity                                       |                | 1<br>5<br>7<br>2                               | 2<br>10<br>10                                       |                | 1<br>5<br>3<br>2                               | 2<br>10<br>5                         | ppm/°C<br>ppm/°C<br>ppm/°C<br>ppm/°C                  |

| SETTLING TIME TO 1/2 LSB<br>All Bits ON-to-OFF or OFF-to-ON                                                                           |                | 250                                            | 350                                                 |                | 250                                            | 350                                  | ns                                                    |

| FULL-SCALE TRANSITION<br>10% to 90% Delay plus Rise Time<br>90% to 10% Delay plus Fall Time                                           |                | 15<br>30                                       | 30<br>50                                            |                | 15<br>30                                       | 30<br>50                             | ns<br>ns                                              |

| POWER REQUIREMENTS $V_{\rm EB}$ , $-11.4$ to $-16.5$ V dc                                                                             |                | -12                                            | -18                                                 |                | -12                                            | -18                                  | mA                                                    |

| POWER SUPPLY GAIN SENSITIVITY <sup>2</sup><br>$V_{EE} = -11.4 \text{ to } -16.5 \text{ V dc}$                                         |                | 15                                             | 25                                                  |                | 15                                             | 25                                   | ppm of F.S./%                                         |

| PROGRAMMABLE OUTPUT RANGES (see Figures 3, 4, 5)                                                                                      |                | 0 to +5 -2.5 to +2 0 to +10 -5 to +5 -10 to +1 |                                                     |                | 0 to +5 -2.5 to +2 0 to +10 -5 to +5 -10 to +1 |                                      | V<br>V<br>V<br>V                                      |

| EXTERNAL ADJUSTMENTS Gain Error with Fixed 50 $\Omega$ Resistor for R2 (Figure 3)                                                     |                | ±0.1                                           | ±0.25                                               |                | ±0.1                                           | ±0.25                                | % of F.S. Range                                       |

| Bipolar Zero Error with Fixed<br>50 Ω Resistor for R1 (Figure 4)<br>Gain Adjustment Range (Figure 3)<br>Bipolar Zero Adjustment Range | ±0.25<br>±0.15 | ±0.05                                          | ±0.15                                               | ±0.25<br>±0.15 | ±0.05                                          | ±0.1                                 | % of F.S. Range<br>% of F.S. Range<br>% of F.S. Range |

| REFERENCE INPUT                                                                                                                       |                |                                                |                                                     |                |                                                |                                      |                                                       |

| Input Impedance POWER DISSIPATION                                                                                                     | 15             | 20                                             | 25                                                  | 15             | 20                                             | 25                                   | kΩ                                                    |

| MULTIPLYING MODE PERFORMANCE (All Models)                                                                                             |                | 180                                            | 300                                                 |                | 180                                            | 300                                  | mW                                                    |

| Quadrants<br>Reference Voltage<br>Accuracy<br>Reference Feedthrough (Unipolar Mode,                                                   |                | 1 V to 10                                      | Bipolar Operation<br>V, Unipolar<br>10.05% of Reduc |                | Input Only 1 V dc Reference                    | e Voltage                            |                                                       |

| All Bits OFF, and 1 V to 10 V [p-p], Sine Wave Frequency for 1/2 LSB [p-p] Feedthrough) Output Slew Rate 10%–90% 90%–10%              |                | 40<br>5<br>1                                   |                                                     |                |                                                |                                      | kHz typ<br>mA/μs<br>mA/μs                             |

| Output Settling Time (All Bits ON and a 0 V–10 V Step Change in Reference Voltage)                                                    |                | 1.5 μs to                                      | 0.01% F.S.                                          |                |                                                |                                      |                                                       |

| CONTROL AMPLIFIER Full Power Bandwidth Small-Signal Closed-Loop Bandwidth                                                             |                | 300<br>1.8                                     |                                                     |                |                                                |                                      | kHz<br>MHz                                            |

Specifications shown in **boldface** are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in **boldface** are tested on all production units.

REV. F \_5\_

Specification subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to Power Ground 0 V to +18 V      |

|---------------------------------------------------|

| $V_{EE}$ to Power Ground (AD565A) 0 V to –18 V    |

| Voltage on DAC Output (Pin 9)3 V to +12 V         |

| Digital Inputs (Pins 13 to 24) to                 |

| Power Ground1.0 V to +7.0 V                       |

| REF IN to Reference Ground ±12 V                  |

| Bipolar Offset to Reference Ground ±12 V          |

| 10 V Span R to Reference Ground ±12 V             |

| 20 V Span R to Reference Ground ±24 V             |

| REF OUT (AD565A) Indefinite Short to Power Ground |

| Momentary Short to V <sub>CC</sub>                |

| Power Dissipation                                 |

#### **GROUNDING RULES**

The AD565A and AD566A use separate reference and power grounds to allow optimum connections for low noise and high speed performance. These grounds should be tied together at one point, usually the device power ground. The separate ground returns minimize current flow in low level signal paths. In this way, logic return currents are not summed into the same return path with analog signals.

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD565A/AD566A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-6- REV.F

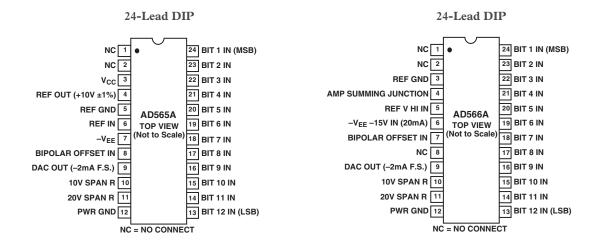

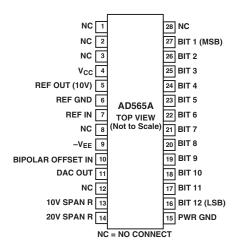

#### **PIN CONFIGURATIONS**

#### 28-Lead SOIC

REV. F -7-

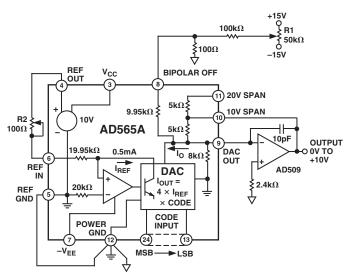

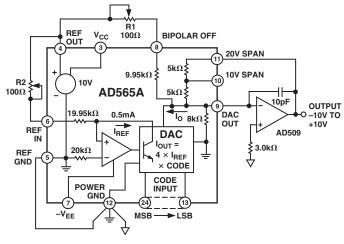

# CONNECTING THE AD565A FOR BUFFERED VOLTAGE OUTPUT

The standard current-to-voltage conversion connections using an operational amplifier are shown in Figures 1, 2, and 3 with the preferred trimming techniques. If a low offset operational amplifier (OP77, AD741L, OP07) is used, excellent performance can be obtained in many situations without trimming (an op amp with less than 0.5 mV max offset voltage should be used to keep offset errors below 1/2 LSB). If a 50  $\Omega$  fixed resistor is substituted for the 100  $\Omega$  trimmer, unipolar zero is typically within  $\pm 1/2$  LSB (plus op amp offset) and full-scale accuracy is within 0.1% (0.25% max). Substituting a 50  $\Omega$  resistor for the 100  $\Omega$  bipolar offset trimmer gives a bipolar zero error typically within  $\pm 2$  LSB (0.05%).

The AD509 is recommended for buffered voltage-output applications that require a settling time to  $\pm 1/2$  LSB of 1  $\mu s$ . The feedback capacitor is shown with the optimum value for each application; this capacitor is required to compensate for the 25 pF DAC output capacitance.

#### FIGURE 1. UNIPOLAR CONFIGURATION

This configuration provides a unipolar 0 V to 10 V output range. In this mode, the bipolar terminal, Pin 8, should be grounded if not used for trimming.

Figure 1. 0 V to 10 V Unipolar Voltage Output

#### STEP I . . . ZERO ADJUST

Turn all bits OFF and adjust zero trimmer R1 until the output reads 0.000 V (1 LSB = 2.44 mV). In most cases, this trim is not needed, but Pin 8 should then be connected to Pin 12.

#### STEP II . . . GAIN ADJUST

Turn all bits ON and adjust  $100~\Omega$  gain trimmer R2 until the output is 9.9976 V. (Full scale is adjusted to 1 LSB less than nominal full scale of 10.000~V.) If a 10.2375~V full scale is desired (exactly 2.5~mV/bit), insert a  $120~\Omega$  resistor in series with the gain resistor at Pin 10 to the op amp output.

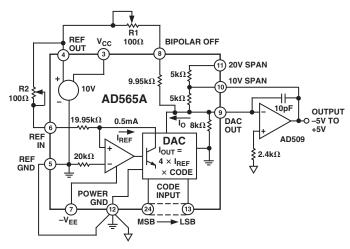

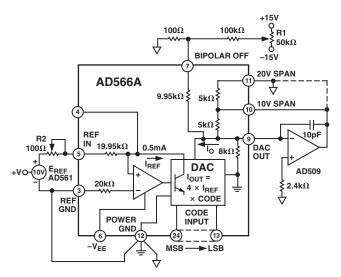

#### FIGURE 2. BIPOLAR CONFIGURATION

This configuration provides a bipolar output voltage from -5.000 V to +4.9976 V, with positive full scale occurring with all bits ON (all 1s).

Figure 2. ±5 V Bipolar Voltage Output

#### STEP I . . . OFFSET ADJUST

Turn OFF all bits. Adjust 100  $\Omega$  trimmer R1 to give –5.000 V output.

#### STEP II . . . GAIN ADJUST

Turn ON all bits. Adjust 100  $\Omega$  gain trimmer R2 to give a reading of +4.9976 V.

Please note that it is not necessary to trim the op amp to obtain full accuracy at room temperature. In most bipolar situations, an op amp trim is unnecessary unless the untrimmed offset drift of the op amp is excessive.

#### FIGURE 3. OTHER VOLTAGE RANGES

The AD565A can also be easily configured for a unipolar 0 V to +5 V range or  $\pm 2.5$  V and  $\pm 10$  V bipolar ranges by using the additional 5 k $\Omega$  application resistor provided at the 20 V span R terminal, Pin 11. For a 5 V span (0 V to +5 V, or  $\pm 2.5$  V), the two 5 k $\Omega$  resistors are used in parallel by shorting Pin 11 to Pin 9 and connecting Pin 10 to the op amp output and the bipolar offset either to ground for unipolar or to REF OUT for the bipolar offset either to ground for unipolar or to REF OUT for the bipolar range. For the  $\pm 10$  V range (20 V span) use the 5 k $\Omega$  resistors in series by connecting only Pin 11 to the op amp output and the bipolar offset connected as shown. The  $\pm 10$  V option is shown in Figure 3.

Figure 3. ±10 V Voltage Output

# CONNECTING THE AD566A FOR BUFFERED VOLTAGE OUTPUT

The standard current-to-voltage conversion connections using an operational amplifier are shown in Figures 4, 5, and 6 with the preferred trimming techniques. If a low offset operational amplifier (OP77, AD741L, OP07) is used, excellent performance can be obtained in many situations without trimming (an op amp with less than 0.5 mV max offset voltage should be used to keep offset errors below 1/2 LSB). If a 50  $\Omega$  fixed resistor is substituted for the 100  $\Omega$  trimmer, unipolar zero typically is within  $\pm 1/2$  LSB (plus op amp offset), and full-scale accuracy is within 0.1% (0.25% max). Substituting a 50  $\Omega$  resistor for the 100  $\Omega$  bipolar offset trimmer gives a bipolar zero error typically within  $\pm 2$  LSB (0.05%).

The AD509 is recommended for buffered voltage-output applications that require a settling time to  $\pm 1/2$  LSB of 1  $\mu$ s. The feedback capacitor is shown with the optimum value for each application; this capacitor is required to compensate for the 25 pF DAC output capacitance.

#### FIGURE 4. UNIPOLAR CONFIGURATION

This configuration provides a unipolar 0 V to 10 V output range. In this mode, the bipolar terminal, Pin 7, should be grounded if not used for trimming.

Figure 4. 0 V to 10 V Unipolar Voltage Output

#### STEP I . . . ZERO ADJUST

Turn all bits OFF and adjust zero trimmer, R1, until the output reads 0.000 V (1 LSB = 2.44 mV). In most cases, this trim is not needed, but Pin 7 should then be connected to Pin 12.

#### STEP II . . . GAIN ADJUST

Turn all bits ON and adjust  $100~\Omega$  gain trimmer, R2, until the output is 9.9976 V. (Full scale is adjusted to 1 LSB less than nominal full scale of 10.000~V.) If a 10.2375~V full scale is desired (exactly 2.5~mV/bit), insert a  $120~\Omega$  resistor in series with the gain resistor at Pin 10 to the op amp output.

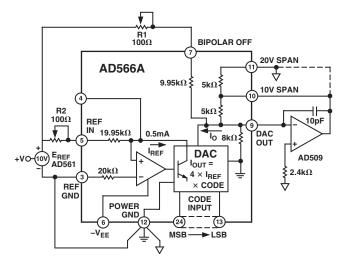

#### FIGURE 5. BIPOLAR CONFIGURATION

This configuration provides a bipolar output voltage from -5.000 V to +4.9976 V, with positive full scale occurring with all bits ON (all 1s).

Figure 5. ±5 V Bipolar Voltage Output

#### STEP I . . . OFFSET ADJUST

Turn OFF all bits. Adjust 100  $\Omega$  trimmer R1 to give –5.000 output V.

#### STEP II . . . GAIN ADJUST

Turn ON all bits. Adjust 100  $\Omega$  gain trimmer R2 to give a reading of +4.9976 V.

Please note that it is not necessary to trim the op amp to obtain full accuracy at room temperature. In most bipolar situations, an op amp trim is unnecessary unless the untrimmed offset drift of the op amp is excessive.

REV. F –9–

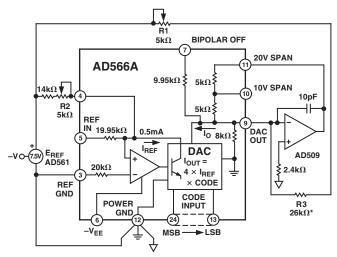

#### FIGURE 6. OTHER VOLTAGE RANGES

The AD566A can also be easily configured for a unipolar 0 V to +5 V range or  $\pm 2.5$  V and  $\pm 10$  V bipolar ranges by using the additional 5 k $\Omega$  application resistor provided at the 20 V span R terminal, Pin 11. For a 5 V span (0 V to +5 V or  $\pm 2.5$  V), the two 5 k $\Omega$  resistors are used in parallel by shorting Pin 11 to Pin 9 and connecting Pin 10 to the op amp output and the bipolar offset resistor either to ground for unipolar or to  $V_{REF}$  for the bipolar range. For the  $\pm 10$  V range (20 V span), use the 5 k $\Omega$  resistors in series by connecting only Pin 11 to the op amp output and the bipolar offset connected as shown. The  $\pm 10$  V option is shown in Figure 6.

<sup>\*</sup> THE PARALLEL COMBINATION OF THE BIPOLAR OFFSET RESISTOR AND R3 ESTABLISHES A CURRENT TO BALANCE THE MSB CURRENT. THE EFFECT OF TEMPERATURE COEFFICIENT MISMATCH BETWEEN THE BIPOLAR RESISTOR COMBINATION AND DAC RESISTORS IS EXPANDED ON PREVIOUS PAGE.

Figure 6. ±10 V Voltage Output

Table I. Digital Input Codes

| DIGITAL INPUT<br>MSB LSB              | Straight Binary   | ANALOG OUTPUT<br>Offset Binary | Twos Complement* |

|---------------------------------------|-------------------|--------------------------------|------------------|

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | Zero              | -FS                            | Zero             |

|                                       | Mid Scale – 1 LSB | Zero – 1 LSB                   | +FS – 1 LSB      |

|                                       | +1/2 FS           | Zero                           | –FS              |

|                                       | +FS – 1 LSB       | +FS – 1 LSB                    | Zero – 1 LSB     |

<sup>\*</sup>Inverts the MSB of the offset binary code with an external inverter to obtain twos complement.

-10- REV.F

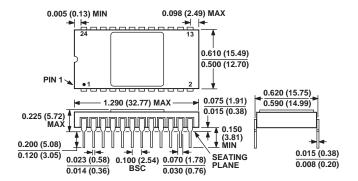

# **OUTLINE DIMENSIONS**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 7. 24-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP] (D-24-2) Dimensions shown in inches and (millimeters)

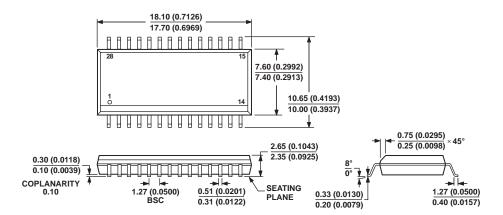

COMPLIANT TO JEDEC STANDARDS MS-013-AE

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 8. 28-Lead Standard Small Outline Package [SOIC\_W]

Wide Body

(RW-28)

Dimensions shown in millimeters and (inches)

-07-2006-A

### **ORDERING GUIDE**

|                       | Max Gain T.C.    |                   | Linearity Error Max @ |                     |                 |

|-----------------------|------------------|-------------------|-----------------------|---------------------|-----------------|

| Model <sup>1, 2</sup> | (ppm of F.S./°C) | Temperature Range | +25°C                 | Package Description | Package Options |

| AD565AJD              | 50               | 0°C to +70°C      | ±1/2 LSB              | 24-Lead SBDIP       | D-24-2          |

| AD565AJR              | 50               | 0°C to +70°C      | ±1/2 LSB              | 28-Lead SOIC_W      | RW-28           |

| AD565AJRZ             | 50               | 0°C to +70°C      | ±1/2 LSB              | 28-Lead SOIC_W      | RW-28           |

| AD565AJRZ-REEL        | 50               | 0°C to +70°C      | ±1/2 LSB              | 28-Lead SOIC_W      | RW-28           |

| AD565AKD              | 20               | 0°C to +70°C      | ±1/4 LSB              | 24-Lead SBDIP       | D-24-2          |

| AD565ASD              | 30               | −55°C to +125°C   | ±1/2 LSB              | 24-Lead SBDIP       | D-24-2          |

| AD565ATD              | 15               | −55°C to +125°C   | ±1/4 LSB              | 24-Lead SBDIP       | D-24-2          |

<sup>&</sup>lt;sup>1</sup> For details on grade and package offerings screened in accordance with MIL-STD-883, refer to the Analog Devices Military Products Databook or current/883B data sheet.

#### **REVISION HISTORY**

#### 3/15—Rev. E to Rev. F

| Added AD566A Obsolete Note | 1  |

|----------------------------|----|

| Updated Outline Dimensions | 11 |

| Changes to Ordering Guide  | 12 |

| 10/02—Rev. D to Rev. E     |    |

| Edits to Specifications    | 2  |

| Outline Dimensions Undated |    |

Rev. F | Page 12

$<sup>^{2}</sup>$  Z = RoHS Copliant Part.